Изобретение относится к радио-электросвязи и может использоваться в проводных, радио-, радиорелейных и космических линиях связи.

В известном способе приема двоичных фазоманипулированных на 0, 90, 180, 270 градусов сигналов с фазорасностной модуляцией [см. Л. 1, стр. 168-171, Рис. 4.4] радиосигнал, принимаемый некогерентным приемником, преобразуется в сигналы (Xn, Yn) с нулевой частотой в двух квадратурных (cosϕ, sinϕ ) каналах, далее низкочастотные отфильтрованные сигналы каждого из каналов (X, Y) задерживаются на один бит и перемножаются с текущими сигналами своего и ортогонального канала. Эти произведения суммируются, вычитаются, квантуются (sgn) по алгоритму:

J1n = sgn[(X(n-1)Yn - XnY(n-1)) + (X(n-1)Xn + Y(n-1)Yn)]

J2n = sgn[(X(n-1)Xn + Y(n-1)Yn) + (X(n-1)Yn - XnY(n-1))]

по значениям сигналов J1n и J2n на выходе приемного устройства принимается решение об изменении фазы сигнала на одно из четырех значений 0,π/2,π,3π/2.

Сущность указанного известного способа состоит в том, что при изменении фазой радиосигнала своего значения на одно из значений 0, 90, 180, 270 градусов между (n-1)-ым и n-ым битами значения низкочастотных отфильтрованных сигналов в обоих квадратурных каналах незначительно изменяются по абсолютной величине (частота гетеродина передатчика незначительно отличается от частоты приемника), на выходе приемного устройства формируется сигнал, соответствующий одному из четырех значений изменения фазы (0, 90, 180, 270 градусов) в зависимости от комбинации выходных квантовых сигналов J1n, J2n. Этот известный способ по своей технической сущности наиболее близок к заявляемому и поэтому выбирается за прототип.

Устройство для его реализации по техническим средствам наиболее близко к заявляемому устройству и также выбирается за прототип заявляемого устройства.

Недостатком указанного известного способа является сложность реализации радиоприемного устройства и относительно низкая помехозащищенность.

Задачей предлагаемого изобретения является повышение помехоустойчивости способа и приемного устройства при общем снижении его сложности.

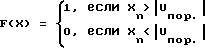

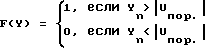

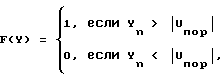

Для выполнения поставленной задачи в предлагаемом способе входные радиосигналы в двух квадратурных (cosϕ,sinϕ) каналах (X, Y) со взаимоортогональными сигналами гетеродина приемника фильтруют полученные таким образом сигналы с последующей задержкой на один бит. По значениям величин отфильтрованных низкочастотных сигналов, посредством сравнения их с заданным пороговым напряжением (Uпор.), формируются два квадратурных оператора F(X) и F(Y) в каналах X и Y по алгоритму:

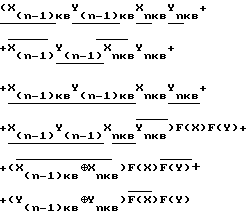

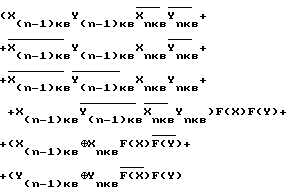

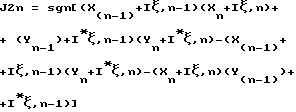

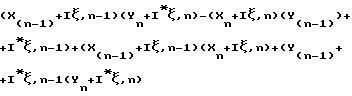

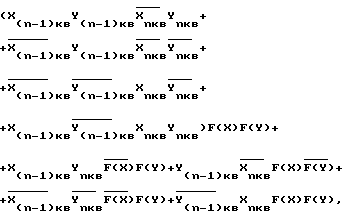

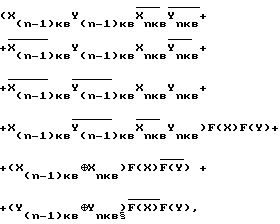

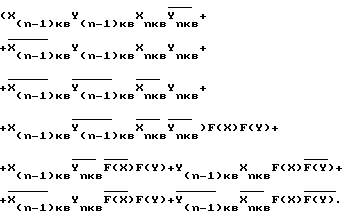

По значениям операторов (F(X), F(Y)), текущего и задержанного на один бит бинарных квантовых сигналов (X(n-1)кв, Y(n-1)кв, Xnкв, Ynкв) в двух квадратурных каналах (X, Y) принимается решение об изменении фазы сигнала на одно из четырех значений 0, 90, 180, 270 градусов по алгоритму:

Δϕ = 0

Δϕ = π/2

Δϕ = π

Δϕ = 3π/2

причем во всех четырех формулах произведения первых четырех слагаемых на F(X)F(Y) соответствуют тому, что F(X)=F(Y)=1 и величины Xn; Yn в обоих каналах больше значения Uпор. по абсолютной величине во всех четырех квадрантах фазовой плоскости (X, Y) (фиг. 1), остальные слагаемые этих формул соответствуют тому, что F(X) ≠ F(Y) (F(X)=1, F(Y)=0) или наоборот) и величина отфильтрованного низкочастотного сигнала канала (Xn или Yn) меньше Uпор. по абсолютной величине во всех четырех квадрантах фазовой плоскости (X, Y) причем значение низкочастотного отфильтрованного сигнала другого канала в данный момент времени близко по абсолютной величине к максимальному значению. (фиг. 1). Значение гистерезиса ( γ ) выбирается с учетом величины шумов в приемном устройстве. (фиг. 1).

В текущий момент времени только слагаемое из всех четырех формул равно 1, что соответствует одному из четырех возможных межбитных изменений фазы 0,π/2,π,3π/2) в одном (при Δϕ = 0) или двух (при Δϕ = π/2, Δϕ = π, Δϕ = 3π/2) из четырех квадрантов фазовой плоскости (X, Y) (фиг. 1) остальные слагаемые в этот момент времени равны 0.

Примером реализации предложенного способа является приемное устройство.

На фиг. 1, 2 представлены векторные диаграммы процессов обработки сигналов в каналах заявляемого приемного устройства, фиг.3 отображает график сравнения помехоусточивости заявляемого и известного приемных устройств, на фиг. 4 представлена функциональная схема приемного устройства, на фиг. 5, 6, 7, 8 представлена функциональная схема процессора обработки сигналов 12.

Приемное устройство содержит: высокочастотные умножители 1, 2, фазовращатель 3, гетеродин, фильтры нижних частот 4, 5, компараторы 6, 7, схемы сравнения 8, 9, линии задержки 10, 11, процессор обработки сигналов 12. При этом процессор обработки сигналов 12 содержит инверторы 13.1...13.N, где N изменяется от 1 до 54, логические блоки 4И 14.1...14.М, где М изменяется от 1 до 24, логические блоки ИСКЛЮЧАЮЩЕЕ ИЛИ 15.1, 15.2, 15.3, 15.4, логические блоки 3И 16.1, 16.2, 16.3, 16.4, 16.5, 16.6, 16.7, 16.8, логические блоки 4ИЛИ 17.1, 17.2, 17.3, 17.4, логические блоки 3ИЛИ 18.1, 18.2, логические блоки 5ИЛИ 19.1, 19.2. Причем первые входы высокочастотных умножителей 1, 2 каналов X и Y объединены и являются входом устройства, выход гетеродина cos(ωt)) соединен со входом фазовращателя 3 и со вторым входом высокочастотного умножителя 1 канала X, выход фазовращателя 3 соединен со вторым входом высокочастотного умножителя 2 канала Y, в каждом канале выходы высокочастотных умножителей 1, 2 последовательно соединены со входами фильтров нижних частот 4, 5, выходы фильтров нижних частот 4, 5 соединены с первыми входами компараторов 6, 7 и первыми входами схем сравнения 8, 9, вторые входы компараторов 6, 7 заземлены, а вторые и третьи входы схем сравнения 8, 9 соединены с разнополярными источниками заданного порогового напряжения (Uпор.), выход компараторов 6, 7 соединены со входами линий задержек 10, 11 и соответствующими входами Xn.кв и Yn.кв процессора обработки сигналов 12, выходы линий задержек 10, 11 соединены с соответствующими входами X(n-1)кв и Y(n-1)кв процессора обработки сигналов 12, выходы схем сравнения 8, 9 соединены соответственно с F(X) и F(Y) входами процессора обработки сигналов 12,

Δϕ = 0, Δϕ = π/2, Δϕ = π, Δϕ = 3π/2 выходы которого являются выходами устройства. Причем выходы первого, второго, третьего и четвертого логических блоков 4И 14.1, 14.2, 14.3, 14.4 подключены соответственно к первому, второму, третьему и четвертому входам первого логического блока 4ИЛИ 17.1, выходы пятого, шестого, седьмого и восьмого логических блоков 4И 14.5, 14.6, 14.7, 14.7 подключены соответственно к первому, второму, третьему и четвертому входам второго логического блока 4ИЛИ 17.2, выходы девятого, десятого, одиннадцатого и двенадцатого логических блоков 4И 14.9, 14.10, 14.11, 14.12 подключены соответственно к первому, второму, третьему и четвертому входам первого логического блока 5ИЛИ 19.1, выходы тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого 14.13, 14.14, 14.15, 14.16 логических блоков 4И подключены соответственно к первому, второму, третьему и четвертому входам третьего логического блока 4ИЛИ 17.3, выходы семнадцатого, восемнадцатого, девятнадцатого и двадцатого логических блоков 4И 14.17, 14.18, 14.19, 14.20 подключены соответственно к первому, второму, третьему и четвертому входам четвертого логического блока 4ИЛИ 17.4, выходы двадцать первого, двадцать второго, двадцать третьего и двадцать четвертого логических блоков 4И 14.21, 14.22, 14.23, 14.24 подключены соответственно к первому, второму, третьему и четвертому входам второго логического блока 5ИЛИ 19.2, первые входы первого и второго логических блоков ИСКЛЮЧАЮЩЕЕ ИЛИ 15.1, 15.2, первые входы первого, четвертого, пятого, восьмого, девятого, тринадцатого, шестнадцатого, семнадцатого, двадцатого и двадцать первого логических блоков 4И 14.1, 14.4, 14.5, 14.8, 14.9, 14.13, 14.16, 14.17, 14.20, 14.21 непосредственно, а второго, третьего, шестого, седьмого, одиннадцатого, четырнадцатого, пятнадцатого, восемнадцатого, девятнадцатого и двадцать третьего логических блоков 4И 14.2, 14.3, 14.6, 14.7, 14.11, 14.14, 14.15, 14.18, 14.19, 14.23 через соответствующие инверторы 13.1, 13.3, 13.12, 13.15, 13.22, 13.29, 13.31, 13.36, 13.37, 13.46 объединены и являются Xn-1.кв входом процессора обработки сигналов 12, первые входы третьего и четвертого логических блоков ИСКЛЮЧАЮЩЕЕ ИЛИ 15.3, 15.4, первые входы десятого и двадцать второго логических блоков 4И 14.10, 14.22, вторые входы первого, второго, пятого, шестого, тринадцатого, четырнадцатого, семнадцатого и восемнадцатого логических блоков 4И 14.1, 14.2, 14.5, 14.6, 14.13, 14.14, 14.17, 14.18 непосредственно, а первые входы двенадцатого и двадцать четвертого логических блоков 4И 14.12, 14.24 и вторые входы третьего, четвертого, седьмого, восьмого, пятнадцатого, шестнадцатого, девятнадцатого и двадцатого логических блоков 4И 14.3, 14.4, 14.7, 14.8, 14.15, 14.16, 14.19, 14.29 через соответствующие инверторы объединены и являются Yn-1.кв входом процессора обработки сигналов 12, вторые входы первого и второго логических блоков ИСКЛЮЧАЮЩЕЕ ИЛИ 15.1, 15.2, вторые входы двенадцатого и двадцать второго логических блоков 4И 14.12, 14.22, третьи входы первого, четвертого, седьмого, восьмого, четырнадцатого, пятнадцатого, семнадцатого, восемнадцатого логических блоков 4И 14.1, 14.4, 14.7, 14.8, 14.14, 14.15, 14.17, 14.18 непосредственно, а вторые входы десятого и двадцать четвертого логических блоков 4И 14.10, 14.24 и третьи входы второго, третьего, пятого, шестого, тринадцатого, шестнадцатого, девятнадцатого и двадцатого логических блоков 4И 14.2, 14.3, 14.5, 14.6, 14.13, 14.16, 14.19, 14.20 через соответствующие инверторы 13.2, 13.5, 13.11, 13.13, 13.20, 13.27, 13.34, 13.39, 13.41, 13.49 объединены и являются Xn.кв входом процессора обработки сигналов 12, вторые входы третьего и четвертого логических блоков ИСКЛЮЧАЮЩЕЕ ИЛИ 15.3, 15.4, вторые входы девятого и двадцать третьего логических блоков 4И 14.9, 14.23, четвертые входы первого, второго, пятого, восьмого, пятнадцатого, шестнадцатого, восемнадцатого и девятнадцатого блоков 4И 14.1, 14.2, 14.5, 14.8, 14.15, 14.16, 14.18, 14.19 непосредственно, а вторые входы одиннадцатого и двадцать первого и четвертые входы третьего, четвертого, шестого, седьмого, тринадцатого, четырнадцатого, семнадцатого и двадцатого логических блоков 4И 14.3, 14.4, 14.6, 14.7, 14.11, 14.13, 14.14, 14.17, 14.20, 14.21 через соответствующие инверторы 13.6, 13.8, 13.14, 13.17, 13.23, 13.28, 13.30, 13.35, 13.42, 13.43 объединены и являются Yn.кв входом процессора обработки сигналов 12, выходы первого, второго и третьего логических блоков 3И 16.1, 16.2, 16.3 подключены соответственно к первому, второму и третьему входам первого логического блока 3ИЛИ 18.1, выход которого является Δϕ = 0 выходом процессора обработки сигналов 12, выход четвертого логического блока 3И 16.4 соединен с пятым входом первого логического блока 5ИЛИ 19.1, выход которого является Δϕ = π/2 выходом процессора обработки сигналов 12, выходы пятого, шестого и седьмого логических блоков 3И 16.5, 16.6, 16.7 подключены соответственно к первому, второму и третьему входам второго логического блока 3ИЛИ 18.3, выход которого является Δϕ = π выходом процессора обработки сигналов 12, выход восьмого логического блока 3И 16.8 соединен с пятым входом второго логического блока 5ИЛИ 19.2, выход которого является Δϕ = 3π/2 выходом процессора обработки сигналов 12, первые входы первого, второго, четвертого, пятого, шестого и восьмого логических блоков 3И 16.1, 16.2, 16.4, 16.5, 16.6, 16.8, третьи входы десятого, двенадцатого, двадцать второго и двадцать четвертого логических блоков 4И 14.10, 14.12, 14.22, 14.24 непосредственно, а первые входы третьего и седьмого логических блоков 3И 16.3, 16.7 и третьи входы девятого, одиннадцатого, двадцать первого и двадцать третьего логических блоков 4И 14.9, 14.11, 14.21, 14.23 через соответствующие инверторы 13.19, 13.24, 13.44, 13.47, 13.52, 14.54 объединены и являются "F(X)" входом процессора обработки сигналов 12, вторые входы первого, третьего, четвертого, пятого, седьмого и восьмого логических блоков 3И 16.1, 16.3, 16.4, 16.5, 16.7, 16.8, четвертые входы девятого, одиннадцатого, двадцать первого и двадцать третьего логических блоков 4И 14.9, 14.11, 14.21, 14.23 непосредственно, а вторые входы второго и шестого логических блоков 3И 16.2, 16.6 и четвертые входы десятого, двенадцатого, двадцать второго и двадцать четвертого логических блоков 4И 14.10, 14.12, 14.22, 14.24 через соответствующие инверторы 13.21, 13.26, 13.45, 13.50, 13.51, 13.53 объединены и являются "F(Y)" входом процессора обработки сигналов 12, выходы первого, второго, третьего и четвертого логических блоков 4ИЛИ 17.1, 17.2, 17.3, 17.4 соединены с третьими входами соответственно первого, четвертого, пятого и восьмого логических блоков 3И 16.1, 16.4, 16.5, 16.8, третьи входы второго и третьего логических блоков 3B 16.2, 16.3 через соответствующие инверторы 13.9, 13.10 подключены к выходам первого и третьего логических блоков ИСКЛЮЧАЮЩЕЕ ИЛИ 15.1, 15.3 соответственно, третьи входы шестого и седьмого логических блоков 3И 16.6, 16.7 соединены с выходами соответственно второго и четвертого логических блоков ИСКЛЮЧАЮЩЕЕ ИЛИ 15.2, 15.4.

Линии задержки 10, 11, элементы процессора обработки 12 сигналов заявленного устройства могут быть реализованы соответственно на D-триггерах, элементах алгебры логики [3] (стр. 5-11), выполненных на типовых микросхемах отечественного производства, например серии: 133, 155, 555, 1533; 561, 564 и т. д. или аналогичные серии зарубежного производства по технологиям ТТЛ, КМОП, ЭСЛ, (TTL, CMOS, ESL). Компараторы 6, 7, схемы сравнения 8, 9 могут быть реализованы на типовых операционных усилителях отечественного производства, например серии: 544,574 и т.д. или аналогичные серии зарубежного производства.

Устройство работает следующим образом: исходный радиосигнал x(t) = acos(ω1t+ϕ) поступает на первые входы высокочастотных умножителей 1, 2, а на вторые входы поступают сигналы гетеродина, смещенные посредством фазовращателя 3 по фазе на π/2(sinω2t; cosω2t), с выходов высокочастотных умножителей 1, 2 двухчастотные сигналы (с частотами ω1+ω2 и ω1-ω2) поступают на входы фильтров нижних частот 4, 5. Фильтры нижних частот 4, 5 выделяют низкочастотные сигналы (Xn, Yn) (aT/2)cosϕ и (aT/2)sinϕ в двух ортогональных каналах X и Y. Разность частот гетеродина радиопередатчика и радиоприемника близка к нулю, поэтому ее значением пренебрегают (за время τ, равное времени одного бита, разность фаз гетеродина радиопередатчика и радиоприемника δϕ = (ω1-ω2)τ ничтожно мала). Компараторы, 6, 7 бинарно квантуют отфильтрованные низкочастотные сигналы (Xnкв, Ynкв, если Xn, Yn>0, то Xnкв, Ynкв присваивается значение логической единицы, если Xn, Yn<0, то Xnкв, Ynкв присваивается значение логического нуля. С выходов компараторов 6, 7 бинарно квантованные сигналы (Xnкв, Ynкв) поступают на соответствующие входы Xnкв и Ynкв процессора обработки сигналов 12 и на соответствующие входы линий задержек 10, 11. В линиях задержек 10, 11 сигналы Xnкв, Ynкв задерживаются на время τ, равное времени одного бита, и подаются на соответствующие входы X(n-1)кв и Y(n-1)кв процессора обработки сигналов 12. На первые входы схем сравнения 8, 9 подаются низкочастотные отфильтрованные сигналы (Xn, Yn) каналов (X, Y), вторые и третьи входы схем сравнения 8, 9 соединены с разнополярными источниками заданного порогового напряжения. Схема сравнения 8, 9 формируют квадратурные операторы F(X) и F(Y) по алгоритму:

и подают их на соответствующие входы процессора обработки сигналов 12. Величины операторов F(X) и F(Y) квантованы бинарно. По значениям сигналов X(n-1)вк, Y(n-1)кв, Xn.кв, Ynкв и операторов F(X) и F(Y) принимается решение об изменении фазы сигнала на одно из четырех значений 0, 90, 180, 270 градусов по алгоритму:

Δϕ = 0

Δϕ = π/2

Δϕ = π

Δϕ = 3π/2

Вышеприведенная формула (Δϕ = 0, Δϕ = π/2, Δϕ = π, Δϕ = 3π/2) по своей структуре представляет собой алгоритм работы процессора обработки сигналов 12.

Оценим величину отношения сигнал/шум на выходе приемника в способе прототипа и в предлагаемом способе.

В способе прототипа:

Пусть на вход приемного устройства поступает сигнал

x(t) = acos(ωt+ϕ) и помеха ξ(t),

где a - амплитуда входного радиосигнала.

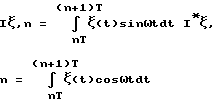

Величины сигналов и помех на выходах фильтров нижних частот каналов X и Y в n-ном и (n-1)-ом битах равны соответственно и приведены в литературе [1] стр. 237.

где T - постоянная времени фильтра частот

где * означает, что сигналы комплексно сопряженные.

Алгоритм

J1n = sgn[(X(n-1)Yn - XnY(n-1)) + (X(n-1)Xn + Y(n-1)Yn)]

J2n = sgn[(X(n-1)Xn + Y(n-1)Yn) + (X(n-1)Yn - XnY(n-1))]

с учетом шумов записывается

sgn - означает операцию бинарного квантования. Отношение сигнал/шум на выходе приемного устройства определяется отношением сигнал/шум на входе квантователя (sgn) каналов X и Y. Возьмем для анализа выход (J1n)

Произведя математические преобразования с учетом того, что значение частоты гетеродина радиопередатчика близко к значению частоты гетеродина радиоприемника и поэтому

получим

где a2T2/4 - полезный сигнал,

aT(I,ξn+Iξ,n-1)eiϕ - шум

Аналогичные значения могут быть получены для выхода J2n.

Отношение сигнал/шум на входе квантователя равно

Модуль отношения сигнал/шум равен

На основании центральной предельной теоремы, приведенной в литературе [2] стр. 73

В предлагаемом способе бинарное квантование осуществляется после фильтров нижних частот в двух квадратурных каналах (X, Y), поэтому возникает необходимость оценить сигнал/шум на входе квантователей в обоих квадратурных каналах.

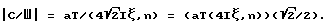

Канал X (C/Ш)x = (aT/(2Iξ,n))cosϕ

Канал Y (C/Ш)y = (aT/(2Iξ*,n))sinϕ

Очевидно, что при определенном ϕ при одновременной работе двух каналов (фиг. 1) отношение сигнал/шум на выходе приемного устройства заявляемого способа будет больше, чем отношение сигнал/шум на выходе приемного устройства способа прототипа в секторах с

или в градусах

20,7°+n90°<ϕ<(90°-20,7°)+n90°, где n = 0, 1, 2, 3, ... n

при

В точках (на плоскости X, Y) со значениями углов π/4,π/4+π/2,π/4+π,π/4+3π/2 отношение отношения сигнал/шум на выходе приемного устройства заявляемого способа будет максимально к отношению сигнал/шум на выходе приемного устройства способа прототипа и равно 2

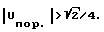

При работе одного из каналов (фиг. 1) отношение сигнал/шум на выходе приемного устройства заявляемого способа всегда будет больше, чем отношение сигнал/шум на выходе приемного устройства способа прототипа, так как в работающем канале величина низкочастотного отфильтрованного сигнала близка к максимальной величине aT(2Iξ,n) и больше, чем

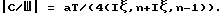

Значение заданного порогового напряжения, при котором отношение сигнал/шум в предлагаемом устройстве будет максимальным, может быть определено.

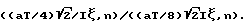

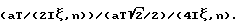

Очевидно, что если Uпор. выбрать равным  то величина зоны одновременной работы двух каналов будет равна нулю (фиг.2), и при любом расположении вектора принимаемого сигнала на плоскостях X, Y отношение отношения сигнал/шум на выходе приемника заявляемого способа к отношению сигнал/шум на выходе приемника в способе, взятом за прототип, будет не меньше 2, причем в точках при значении ϕ на координатной плоскости X, Y π/4,π/4+π/2,π/4+π,π/4+3π/2 это отношение будет равно 2, а во всех других точках выше. Максимальное отношение сигнал/шум на выходе приемника достигается в точках при значении ϕ на координатной плоскости X, Y 0,π/2,π,3π/2. Оно будет выше отношения сигнал/шум способа прототипа в

то величина зоны одновременной работы двух каналов будет равна нулю (фиг.2), и при любом расположении вектора принимаемого сигнала на плоскостях X, Y отношение отношения сигнал/шум на выходе приемника заявляемого способа к отношению сигнал/шум на выходе приемника в способе, взятом за прототип, будет не меньше 2, причем в точках при значении ϕ на координатной плоскости X, Y π/4,π/4+π/2,π/4+π,π/4+3π/2 это отношение будет равно 2, а во всех других точках выше. Максимальное отношение сигнал/шум на выходе приемника достигается в точках при значении ϕ на координатной плоскости X, Y 0,π/2,π,3π/2. Оно будет выше отношения сигнал/шум способа прототипа в  раз (4.5 dB)

раз (4.5 dB)  (фиг. 3). На фиг. 3 отражена зависимость величин отношения сигнал/шум на выходе приемного устройства заявленного способа к отношению сигнал/шум на выходе приемного устройства способа прототипа, в зависимости от расположения вектора принимаемого сигнала на координатной плоскости X,Y(W,ϕ). Кривая (фиг. 3) показывает, что помехоустойчивость приемного устройства заявленного способа выше, чем у приемного устройства способа прототипа, причем при изменении ϕ около точек 0,π/2,π,3π/2 W изменяется незначительно, а при изменении ϕ около точек π/4,π/4+π/2,π/4+π,π/4+3π/2 W изменяется значительно, стремясь к максимуму

(фиг. 3). На фиг. 3 отражена зависимость величин отношения сигнал/шум на выходе приемного устройства заявленного способа к отношению сигнал/шум на выходе приемного устройства способа прототипа, в зависимости от расположения вектора принимаемого сигнала на координатной плоскости X,Y(W,ϕ). Кривая (фиг. 3) показывает, что помехоустойчивость приемного устройства заявленного способа выше, чем у приемного устройства способа прототипа, причем при изменении ϕ около точек 0,π/2,π,3π/2 W изменяется незначительно, а при изменении ϕ около точек π/4,π/4+π/2,π/4+π,π/4+3π/2 W изменяется значительно, стремясь к максимуму  .

.

Заявленное радиоприемное устройство позволяет увеличить отношение сигнал/шум на выходе приемника и реализуется технологически проще радиоприемного устройства прототипа, в котором используются типовые аналоговые или цифровые многоразрядные умножители, по следующим причинам: аналоговые умножители имеют низкую помехозащищенность, цифровые многоразрядные умножители требуют дополнительных сложных дорогостоящих аналого-цифровых преобразователей (АЦП). Кроме того, процесс умножения многоразрядных двоичных чисел производится с использованием ячеек запоминающих устройств (ЗУ), регистров сдвига, многоразрядных сумматоров, что значительно усложняет устройство, снижает его быстродействие.

Заявленное устройство лишено указанных недостатков: во-первых, операции умножителя многоразрядных двоичных чисел или умножения аналоговых сигналов заменены операциями логического умножения и суммирования по модулю два и, во-вторых, сигналы после компараторов не многоразрядны, а квантованы бинарно. Кроме того, современное развитие микроэлектронной элементной базы позволяет реализовать обработку всех бинарно-квантованных сигналов на одной программируемой логической интегральной схеме (ПЛИС), что технологически еще более упрощает устройство, минимизирует монтажные электромагнитные наводки.

Источники информации.

1. Окунев Ю.Б. Цифровые методы передачи информации фазоманипулированными сигналами. Москва. Радио и связь. 1991 г., стр. 168-171, 237, 257-259. (Прототип);

2. Купер Дж., Макгиллем К. Вероятностные методы анализа сигналов и систем. Пер. с англ. Москва. Мир. 1989 г., стр. 73;

3. Пухальский Г.И., Новосельцева Т.Я. Проектирование дискретных устройств на интегральных микросхемах. Справочник. Москва. Радио и связь. 1990 г., стр. 5-11.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПРИЕМА ДВОИЧНЫХ ФАЗОМАНИПУЛИРОВАННЫХ НА 180 ГРАДУСОВ СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ МОДУЛЯЦИЕЙ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1998 |

|

RU2146078C1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ НЕСТАБИЛЬНОСТИ НЕСУЩЕЙ ЧАСТОТЫ ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2336650C2 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ ARCSIN X, ARCCOS X | 1995 |

|

RU2093887C1 |

| ФАЗОМЕТР С ГЕТЕРОДИННЫМ ПРЕОБРАЗОВАНИЕМ ЧАСТОТЫ | 2013 |

|

RU2551837C2 |

| ЦИФРОВАЯ АКТИВНАЯ ФАЗИРОВАННАЯ АНТЕННАЯ РЕШЕТКА | 2015 |

|

RU2608637C1 |

| СПОСОБ УГЛОВОГО РАЗРЕШЕНИЯ ЦЕЛИ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ ПРИ ОБЗОРЕ И РАДИОЛОКАЦИОННАЯ СТАНЦИЯ БОКОВОГО ОБЗОРА | 2000 |

|

RU2182714C2 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФАЗИРОВАННОЙ АНТЕННОЙ РЕШЕТКИ | 1992 |

|

RU2042140C1 |

| СПОСОБ ДЕМОДУЛЯЦИИ СИГНАЛОВ ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2010 |

|

RU2450470C1 |

| УСТРОЙСТВО ДЛЯ АВТОМАТИЧЕСКОЙ БАЛАНСИРОВКИ РОТОРОВ ГИРОСКОПОВ | 2000 |

|

RU2176783C1 |

Предлагаемый новый способ помехоустойчивого приема двоичных фазоманипулированных на 0, 90, 180, 270o с фазоразностной модуляцией радиосигналов может применяться как в радиолиниях, так и в проводных линиях связи. Техническим результатом является повышение помехоустойчивости при уменьшении сложности некогерентного приемника. Указанная цель изобретения достигается тем, что в некогерентном приемнике низкочастотные отфильтрованные сигналы в обоих квадратурных ортогональных (X, Y) каналах квантуются бинарно {0,1}. Так как центральная частота гетеродина в приемнике не равна частоте гетеродина передатчика, то вектор принимаемого сигнала на координатной плоскости (X, У) (Xn, Yn) медленно поворачивается относительно вектора гетеродина приемника. В моменты времени, соответствующие переходу через ноль проекции вектора принимаемого сигнала на ортогональные оси координат, для устранения прохождения на выход приемного устройства несанкционированного срабатывания (из-за шумов) компаратора вблизи нуля в каждом квадратурном канале величина отфильтрованного низкочастотного сигнала сравнивается с заданным пороговым значением Uпор по абсолютной величине. По результатам сравнений формируются два квадратутных оператора F(Х) и F(Y), квантованных бинарно {0,1}. Если величины низкочастотных отфильтрованных сигналов обоих каналов больше Uпор по абсолютной величине, то F(Х) = F(Y) = 1, если величина низкочастотного отфильтрованного сигнала одного из каналов меньше Uпор по абсолютной величине, то F(Х) = F(Y), то есть F(Х) = 1, F(Y) = 0 или F(Х) = 0, F(Y) = 1, причем, если F(Х) = 1, F(Y) = 0, то отфильтрованный низкочастотный сигнал вследствие свойства ортогональности в канале Х в этот момент времени близок к максимальному (по абсолютной величине) значению, если F(Х) = 0, F(Y) = 1, то данное утверждение относится к каналу Y. По значениям бинарно квантованных сигналов обоих каналов в текущем и предшествующем битах (Х(n-1)кв., Y(n-1)кв., Хnкв., Yn.кв.) и квадратурных операторов F(Х) и F(Y) принимается решение об изменении фазы на одно из четырех значений; 0,π/2,3π/2. Устройство, реализующее предложенный способ, представляет собой оптимальный некогерентный приемник фазоманипулированных на 0, 90, 180, 270o сигналов с введенными в него двумя компараторами, двумя схемами сравнения, процессором обработки сигналов при соответствующем их подключении. 2 с.п. ф-лы, 8 ил.

по результатам анализа текущих и задержанных на один бит бинарных квантованных сигналов (X(n-1)кв, Xnкв, Y(n-1)кв, Ynкв) и операторов F(X) и F(Y) принимают решение об изменении фазы сигнала на одно из значений 0, π/2, π, 3π/2 по алгоритму:

Δϕ = 0,

Δϕ = π/2

Δϕ = π

Δϕ = 3π/2,

2. Устройство для осуществления способа по п.1, содержащее гетеродин, фазовращатель и два параллельно включенных канала (X, Y), каждый из которых содержит последовательно соединенные высокочастотный умножитель и фильтр нижних частот, а также линию задержки, причем первые входы высокочастотных умножителей каналов X и Y объединены и являются входом устройства, выход гетеродина подключен к объединенным второму входу высокочастотного умножителя канала X и входу фазовращателя, выход которого соединен со вторым входом высокочастотного умножителя канала Y, отличающееся тем, что введен процессор обработки сигналов, а в каждый канал введены компаратор и схема сравнения, причем в каждом канале первый вход компаратора соединен с выходом фильтра нижних частот, второй вход компаратора заземлен, выходы компараторов X и Y каналов соединены со входами соответствующих линий задержек, объединенными с Xnкв, Ynкв входами процессора обработки сигналов соответственно, выходы линий задержек X и Y каналов подключены соответственно, к X(n-1)кв, Y(n-1)кв входам процессора обработки сигналов, в каждом канале первый вход схемы сравнения соединен с выходом фильтра нижних частот, второй и третий входы схем сравнения подключены к разнополярным источникам порогового напряжения, выходы схем сравнения X и Y каналов соединены соответственно с F(X) и F(Y) входами процессора обработки сигналов, Δϕ = 0, Δϕ = π/2, Δϕ = π, Δϕ = 3π/2 выходы которого являются выходами приемного устройства, причем выходы первого, второго, третьего и четвертого логических блоков 4 И подключены соответственно к первому, второму, третьему и четвертому входам первого логического блока 4 ИЛИ, выходы пятого, шестого, седьмого и восьмого логических блоков 4 И подключены соответственно к первому, второму, третьему и четвертому входам второго логического блока 4 ИЛИ, выходы девятого, десятого, одиннадцатого и двенадцатого логических блоков 4 И подключены соответственно к первому, второму, третьему и четвертому входам первого логического блока 5 ИЛИ, выходы тринадцатого, четырнадцатого, пятнадцатого и шестнадцатого логических блоков 4 И подключены соответственно к первому, второму, третьему и четвертому входам третьего логического блока 4 ИЛИ, выходы семнадцатого, восемнадцатого, девятнадцатого и двадцатого логических блоков 4 И подключены соответственно к первому, второму, третьему и четвертому входам четвертого логического блока 4 ИЛИ, выходы двадцать первого, двадцать второго, двадцать третьего и двадцать четвертого логических блоков 4 И подключены соответственно к первому, второму, третьему и четвертому входам второго логического блока 5 ИЛИ, первые входы первого и второго логических блоков исключающее ИЛИ, первые входы первого, четвертого, пятого, восьмого, девятого, тринадцатого, шестнадцатого, семнадцатого, двадцатого и двадцать первого логических блоков 4 И непосредственно, а второго, третьего, шестого, седьмого, одиннадцатого, четырнадцатого, пятнадцатого, восемнадцатого, девятнадцатого и двадцать третьего логических блоков 4 И через соответствующие инверторы объединены и являются X(n-1)кв входом процессора обработки сигналов, первые входы третьего и четвертого логических блоков исключающее ИЛИ, первые входы десятого и двадцать второго логических блоков 4 И, вторые входы первого, второго, пятого, шестого, тринадцатого, четырнадцатого, семнадцатого и восемнадцатого логических блоков 4 И непосредственно, а первые входы двенадцатого и двадцать четвертого логических блоков 4 И и вторые входы третьего, четвертого, седьмого, восьмого, пятнадцатого, шестнадцатого, девятнадцатого и двадцатого логических блоков 4 И через соответствующие инверторы объединены и являются Ynкв входом процессора обработки сигналов, вторые входы первого и второго логических блоков исключающее ИЛИ, вторые входы двенадцатого и двадцать второго логических блоков 4 И, третьи входы первого, четвертого, седьмого, восьмого, четырнадцатого, пятнадцатого, семнадцатого, восемнадцатого логических блоков 4 И непосредственно, а вторые входы десятого и двадцать четвертого логических блоков 4 И и третьи входы второго, третьего, пятого, шестого, тринадцатого, шестнадцатого, девятнадцатого и двадцатого логических блоков 4 И через соответствующие инверторы объединены и являются Xnкв входом процессора обработки сигналов, вторые входы третьего и четвертого логических блоков исключающее ИЛИ, вторые входы девятого и двадцать третьего логических блоков 4 И, четвертые входы первого, второго, пятого, восьмого, пятнадцатого, шестнадцатого, восемнадцатого и девятнадцатого логических блоков 4 И непосредственно, а вторые входы одиннадцатого и двадцать первого и четвертые входы третьего, четвертого, шестого, седьмого, тринадцатого, четырнадцатого, семнадцатого и двадцатого логических блоков 4 И через соответствующие инверторы объединены и являются Ynкв входом процессора обработки сигналов, выходы первого, второго и третьего логических блоков 3 И подключены соответственно к первому, второму и третьему входам первого логического блока 3 ИЛИ, выход которого является Δϕ = 0 выходом процессора обработки сигналов, выход четвертого логического блока 3 И соединен с пятым входом первого логического блока 5 ИЛИ, выход которого является Δϕ = π/2 выходом процессора обработки сигналов, выходы пятого, шестого и седьмого логических блоков 3 И подключены соответственно к первому, второму и третьему входам второго логического блока 3 ИЛИ, выход которого является Δϕ = π выходом процессора обработки сигналов, выход восьмого логического блока 3 И соединен с пятым входом второго логического блока 5 ИЛИ, выход которого является Δϕ = 3π/2 выходом процессора обработки сигналов, первые входы первого, второго, четвертого, пятого, шестого и восьмого логических блоков 3 И, третьи входы десятого, двенадцатого, двадцать второго и двадцать четвертого логических блоков 4 И непосредственно, а первые входы третьего и седьмого логических блоков 3 И и третьи входы девятого, одиннадцатого, двадцать первого и двадцать третьего логических блоков 4 И через соответствующие инверторы объединены и являются F(X) входом процессора обработки сигналов, вторые входы первого, третьего, четвертого, пятого, седьмого и восьмого логических блоков 3 И, четвертые входы девятого, одиннадцатого, двадцать первого и двадцать третьего логических блоков 4 И непосредственно, а вторые входы второго и шестого логических блоков 3 И и четвертые входы десятого, двенадцатого, двадцать второго и двадцать четвертого логических блоков 4 И через соответствующие инверторы объединены и являются F(Y) входом процессора обработки сигналов, выходы первого, второго, третьего и четвертого логических блоков 4 ИЛИ соединены с третьими входами соответственно первого, четвертого, пятого и восьмого логических блоков 3 И, третьи входы второго и третьего логических блоков 3 И через соответствующие инверторы подключены к выходам первого и третьего логических блоков исключающее ИЛИ соответственно, третьи входы шестого и седьмого логических блоков 3 И соединены с выходами соответственно второго и четвертого логических блоков исключающее ИЛИ.

| Ю.Б.Окунев | |||

| Цифровые методы передачи информации ФМ сигналами | |||

| - М.: Радио и связь, 1991, с.166 - 167 | |||

| Демодулятор фазоманипулированных сигналов | 1977 |

|

SU657655A1 |

| Синхронный детектор | 1984 |

|

SU1272470A1 |

| ОТЖИМНОЙ ВАЛ ДЛЯ ТЕКСТИЛЬНОГО И БУМАЖНОГО | 0 |

|

SU255175A1 |

Авторы

Даты

1999-11-20—Публикация

1998-12-29—Подача