Изобретение относится к телевизионным системам записи, хранения и воспроизведения видеоинформации и может быть использовано в вещательном и специальном телевидении, где необходимо записывать большой объем видеоинформации в виде отдельных кадров изображения для длительного хранения.

Известна система (Пат 2047041 А (Ве- ликобиритания). Цифровой накопитель неподвижных изображений 1980, Н 04 N 5/76), содержащая последовательно соединенные аналого-цифровой преобразователь (АЦП), вход которого Является входом устройства, первую память на кадр, первый блок обработки данных, формирователь форматной записи, носитель з&писи, рас- формирователь форматной зап/си, второй блок обработки данных, вторую память на кадр, цифроаналоговый преобоазователь (ЦАП), выход которого является выходом устройства. В данном устройстве используется суммарно-разностное преобразование,

позволяющее сжать видеоинформацию в два раза. Однако это преобразование не устраняет полностью статистическую связь между соседними элементами изображения, что является недостатком устройства, т.к. сохраняется избыточность, связанная с корреляцией изображения.

Наиболее близка по технической сущности к предложенной система (Пат. 4675750 (США) Система сжатия видеоинформации. 1987. Н 04 N 5/92), содержащая первый АЦП, вход которого является ярко- стным входом системы, второй и третий АЦП, входы которых являются входами Цёе- торазностных сигналов системы, первый Мультиплексор (MX), первый и второй входы которого соединены с выходками второго ги третьего АЦП соответственно, первый и второй блоки преобразования, второй MX, причем входы первого и второго блоков преобразования соединены с выходами первого АЦП и первого MX соответственно, а выходы соединены с первым и вторым

сл

С

VI 00

ы

О СО

сл

входами второго MX, последовательно соединенные блок округления, вход которого соединен с выходом второго MX, линию сравнения, генератор кодов, блок кодирования, формирователь форматной записи, блок записи, носитель записи, блок сопро- изведения, расформирователь форматной записи, блок декодирования, память на строку и первый демультиплексор (ДМХ), первый и второй блоки обратного преобразования, входы которых соединены с первым и вторым выходами первого ДМХ соответственно, второй ДМХ, вход которого соединен с выходом второго блока обратного преобразования, первый ЦАП, вход которого соединен с выходом первого блока обратного преобразования, а выход является яркостным выходом системы, второй и третий ЦАП, входы которых соединены с первым и вторым выходами второго ДМХ соответственно, а выходы являются выходами цветоразностных сигналов системы, Однако в данной системе используется преобразование Адамара, которое при различном характере изображений не является собственным для каждого из них. Это означает, что соседние элементы изображения после преобразования остаются статистически связанными, что является недостатком системы, т.к. сохраняется избыточность, связанная с корреляцией изображения.

Цель изобретения - повышение степени сжатия видеосигнала за счет использова- ния линейного ортонормирующего преобразования, которое позволяет полностью устранить взаимосвязь соседних элементов изображения, что приводит к дополнительному сжатию видеосигнала.

Поставленная цель достигается тем, что в систему записи и воспроизведения видеосигнала, содержащую первый АЦП, вход которого является входом яркостного сигнала системы, второй и третий АЦП, входы которых являются входами цветоразностных сигналов системы, первый MX, первый и второй входы которого соединены с выходами второго и третьего АЦП соответственно, второй MX, последовательно соединенные устройство кодирования, устройство записи, носитель записи, устройство воспроизведения и устройство декодирования, первый ДМХ, второй ДМХ, первый ЦАП, выход которого является выходом яркостного сигнала системы, второй и третий ЦАП, входы которых соединены с первым и вторым выходами второго ДМХ соответственно, а выходы являются выходами цветоразностных сигналов системы, введены первый и второй ортонормирующие преобразователи (ОП), третий, четвертый, пятый, шестой, седьмой и восьмой MX, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый, десятый, одиннадцатый, двенадцатый, тринадцатый и четырнадцатый ДМХ, первый и второй блоки формирования адреса (БФА) и блок управления (БУ). Первые входы третьего и четвертого MX соединены с выходами первого АЦП и первого MX соответственно,

0 а выходы их соединены с информационными входами первого и второго ОП соответственно. Выход нормировки и весовой выход первого ОП соединены с первым и вторым входами пятого MX соответственно,

5 выход которого соединен с первым ьходом седьмого MX. Выход нормировки и весовой выход второго ОП соединены с первым и вторым входами шестого MX соответственно, выход которого соединен с первым вхо0 дом восьмого MX. Информационные выходы первого и второго ОП соединены с выходами третьего и четвертого ДМХ соответственно, первые выходы которых соединены с вторыми входами седьмого и.

5 восьмого MX соответственно. Выходы седьмого и восьмого MX соединены с первым и вторым входами второго MX соответственно, выход которого соединен с входом устройства кодирования. Входы

0 одиннадцатого и двенадцатого ДМХ соединены с первым и вторым выходами первого ДМХ соответственно, вход которого соединен с выходом устройства декодирования. Вторые выходы одиннадцатого и двенадца5 того ДМХ соединены с входами тринадцатого и четырнадцатого ДМХ соответственно, первые их выходы соединены с входами нормировки первого и второго ОП соответственно. Первые выходы тринадцатого и че0 тырнадцатого ДМХ соединены с весовыми входами первого и второго ОП соответственно, вторые выходы их соединены с вторыми входами третьего и четвертого MX соответственно. Вторые выходы третьего и

5 четвертого ДМХ соединены с входами первого ЦАП и второго ДМХ соответственно. Первый и второй выходы БУ соединены с первым и вторым входами первого БФА соответственно, выходы которого с первого по

0 десятый соединены с соответствующими входами БУ с первого по десятый. Первые и вторые адресные входы первого ОП объединены с соответствующими адресными входами второго ОП и подключены к первому и

5 второму адресным выходам первого БФА соответственно. Третий, четвертый, пятый, двадцать пятый, двадцать шестой и двадцать седьмой выходы БУ соединены со входами пятого, шестого, седьмого, восьмого, девятого и десятого ДМХ соответственно

Тактовые входы первого, второго и третьего АЦП соединены с первыми выходами пятого, шестого и седьмого ДМХ соответственно, вторые выходы которых соединены с тактовыми входами первого, второго и третьего ЦАП со- ответственно. Управляющие входы первого MX и второго ДМХ объединены и подключены к шестому выходу БУ. Управляющие входы ДМХ с третьего по десятый, третьего и четвертого MX, первые синхровходы первого и второ- го ОП и третьи входы первого и второго БФА объединены и подключены к седьмому выходу БУ. Синхровходы первого ОП второго по восемнадцатый объединены с соответствующими синхровходами второго ОП и подключены к выходам БУ с восьмого по двадцать четвертый соответственно. Управляющие входы пятого и шестого MX объединены и подключены к первому выходу восьмого ДМХ, управляющие входы седьмого и восьмого MX объедине- ны и подключены к первому выходу девятого ДМХ. Управляющие входы одиннадцатого и двенадцатого ДМХ объединены и подключены ко второму выходу восьмого ДМХ, управляющие входы тринадцатого и четырнадцатого ДМХ объединены и подключены к второму выходу девятого ДМХ, Первый и второй выходы десятого ДМХ соединены с управляющими входами второго MX и первого ДМХ соответственно. Первый и второй входы второго БФА соединены с двадцать восьмым выходом БУ и третьим выходом первого БФА соответственно Выход второго БФА соединен с одиннадцатым входом БУ Третьи и четвертые адресные входы первого ОП объединены с со- ответствующими адресными входами второго ОП и подключены к первому vt второму адресным выходам второго БФА соответственно.

Кроме того, каждый ОП содержит первый и второй элементы задержки (ЭЗ), пер- вый, второй, третий, четвертый, пятый, шестрй, седьмой, восьмой и девятый MX, первое и второе запоминающие устройства (ЗУ), первый, второй и третий шинные формирователи (ШФ), регистр (РГ), первый и второй ДМХ, инвертор, первый, второй, третий и четвертый умножители, регистр опорного сигнала (РОС), первый и второй сумматоры, первый и второй регистры суммы (PC), регистр дисперсии (РД), первый и второй делители, устройство извлечения корня и вычитатель. Первый вход первого MX, а также вторые входы второго и третьего мультиплексоров явтяются информационным входом, весовым входом и входом нормировки ОП соответственно Выход первого MX соединен с входом первого ШФ, вход-выход которого соединен с входом-выходом данных первого ЗУ. Выход второго MX соединен с входом второго ШФ, вход

5 0 5 0 5 0 5

п с

5

выход которого соединен с входом-выходом данных второго ЗУ. Выход третьего MX соединен с входом третьего ШФ, вход-выход которого соединен с входом-выходом данных РГ, Выход первого ШФ соединен с входом первого ДМХ и одновременно является информационным выходом ОП. Первый выход первого ДМХ соединен с входом второго ДМХ Первые выходы . первого умножителя, четвертого и пятого MX и вычи- тателя, а также второй вход четвертого MX объединены и подключены ко второму выходу первого ДМХ. Вторые выходы четвертого и пятого MX, а также второго умножителя и второго делителя объединены и подключены к выходу РОС, вход которого соединен с выходом пятого MX, Выход четвертого MX соединен с вторым входом первого умножителя, выход которого соединен с входом первого сумматора. Входы первого PC, РД и первый вход первого делителя объединены и подключены к выходу первого сумматора, второй вход которого соединен с выходом первого PC. Второй вход первого делителя и вход устройства извлечения корня объединены и подключены к выходу РД. Первые входы второго MX и второго умножителя объединены и подключены к выходу первого делителя. Первые выходы третьего MX и второго делителя объединены и подключены к выходу устройства извлечения корня Выход второго делителя соединен с первым входом шестого MX, Выход второго умножителя соединен с вторым входом вы- читателя, выход которого соединен с вторым входом шестого MX. Выход шестого MX соединен с первым входом седьмого MX, выход которого соединен с вторым входом первого MX. Выход второго ШФ соединен с первым входом третьего умножителя и одновременно является весовым выходом ОП. Выход третьего ШФ соединен с первым входом четвертого умножителя и одновременно является выходом нормировки ОП. Первый выход второго ДМХ соединен с вторым входом четвертого умножителя. Вторые входы третьего умножителя и восьмого MX объединены и подключены к второму выходу второго ДМХ. Выход восьмого MX соединен с первым входом второго сумматора, второй вход которого соединен с выходом второго PC. Выход четвертого умножителя соединен с первым входом девятого MX, выход которого соединен с вторым входом седьмого MX. Второй вход девятого MX и вход второго PC объединены и подключены к выходу второго сумматора. Управляющие входы второго, третьего и седьмого MX, a также первого ДМХ объединены и являются первым синхровходом ОП, вторым синхровходом которого является вход сдвига РГ. Вход реверса РГ и управляющий вход третьего МФ объединены и являются третьим синхровходом ОП. Тактовый вход второго ЗУ является четвертым синхровходом ОП. Вход записи-считывания второго ЗУ и вход второго ЭЗ объединены и являются пятым синхровходом ОП, шестым синхровходом которого является тактовый вход первого ЗУ, вход записи-считывания которого объединен с входом первого ЭЗ и является седьмым синхровходом ОП. Первый и второй адресные входы первого ЗУ и первый и второй адресные входы второго ЗУ являются первым, вторым, третьим и четвертым адресными входами ОП, восьмым синхровходом которого является управляющий вход первого MX. Управляющий вход четвертого MX и вход инвертора объединены и являются девятым синхровходом ОП, десятым синхровходом которого является входом сдвига РД, причем выход инвертора соединен с управляющим входом пятого MX. Управляющий вход восьмого MX, входы записи и установки нуля первого PC являются одиннадцатым, двенадцатым и тринадцатым синхровходами ОП соответственно, четырнадцатым и пятнадцатым синхровходами которого являются вход сдвига РОС и управляющий вход шестого MX соответственно, Входы записи и установки нуля второго PC, а также управляющий вход девятого MX являются шестнадцатым, семнадцатым и восемнадцатым синхровходами ОП соответственно.

Кроме того, первый БФА содержит с первого по восьмой элементы И, первый и второй ДМХ, первый, второй и третий элементы ИЛИ, с первого по десятый счетчики (СЧ), регистр, первый и второй сумматоры, первый, второй и третий ЭЗ, инкрементор, с первого по шестой дешифраторы (ДШ), с первого по седьмой MX, схему сравнения и инвертор. Вторые входы первого и второго элементов И и вход первого ДМХ объединены и являются первым входом первого БФА. Первый вход шестого элемента И является вторым входом первого БФА Управляющие входы первого ДМХ, четвертого и пятого MX, вторые входы третьего элемента ИЛИ и четвертого элемента И объединены и являются третьим входом первого БФА. Выход первого элемента И и первый выход первого ДМХ соответственно соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен со входом первого СЧ. Первый выход первого СЧ соединен с первым входом первого сумматора, а второй выход соединен с входом второго СЧ, второй выход которого соединен с первым

выходом регистра, выход которого соединен со вторым входом первого сумматора. Вход первого ЭЗ, первые входы первого ДШ и седьмого MX объединены и подключены к

выходу первого сумматора. Выход первого ЭЗ соединен со входом инкрементора, выход которого соединен со вторым входом регистра. Второй вход первого ДШ и первый вход шестого мультиплексора объеди0 нены и подключены к первому выходу второго СЧ. Второй вход второго элемента И и первый вход четвертого MX объединены и подключены к выходу первого ДШ и одновременно являются вторым выходом перво5 го БФА. Второй выход первого ДМХ и выход второго элемента И соединены соответственно с первым, и вторым входами второго элемента ИЛИ, выход которого соединен со входом третьего счетчика. Вход второго ДШ

0 и второй вход шестого MX объединены и подключены к первому выходу третьего СЧ и одновременно являются первым выходом первого БФА. Второй выход третьего СЧ соединен с входом четвертого СЧ Первые

5 входы первого MX и второго сумматора объединены и подключены к первому выходу четвертого СЧ, второй выход которого соединен с входом пятого. СЧ и одновременно является девятым выходом первого БФА.

0 Второй вход второго сумматора и вход четвертого ДШ объединены и подключены к выходу пятого СЧ, выход второго сумматора соединен с вторым входом первого MX. Вход третьего ДШ и второй вход седьмого

5 MX объединены и подключены к выходу первого MX. Выходы второго и третьего ДШ соединены с первым и вторым входами пятого элемента И соответственно, причем выход второго ДШ одновременно является

0 десятым выходом первого БФА, Первый вход третьего элемента И соединен с выходом четвертого ДШ. Вторые входы третьего и шестого элементов И и первый вход седьмого элемента И объединены и подключены

5 к выходу пятого элемента И и одновременно являются третьим выходом первого БФА. Первые входы третьего элемента ИЛИ и четвертого элемента И объединены и подключены к выходу третьего элемента И. Выход

0 третьего элемента ИЛИ соединен с управляющим входом первого MX и одновременно является седьмым выходом первого БФА. Выход четвертого элемента И соединен с первым входом пятого MX. Выход шестого

5 элемента И соединен с входом второго ДМХ, первый и второй выходы которого соединены с входом шестого СЧ и первым входом восьмого СЧ соответственно. Первые входы второго MX и шестого ДШ объединены и подключены к первому выходу шестого

N

СЧ, второй еыход которого соединен со входом седьмого СЧ. Первый вход третьего MX и второй вход шестого ДШ объединены и соединены с первым выходом седьмого MX соответственно. Управляющие входы второго и третьего MX и второго ДМХ объединены и подключены к второму выходу седьмого СЧ и одновременно являются пятым выходом первого БФА. Выход шестого ДШ соединен с входом третьего ЭЗ, выход которого является четвертым выходом первого Б-ФА, Второй вход третьего MX, первые входы пятого ДШ и схемы сравнению объединены и подключены к выходу восьмого СЧ. Вторые входы второго MX и пятого ДШ объединены и подключены к первому выходу девятого СЧ, второй выход которого соединен с первым входом восьмого элемента И, выход которого соединен с входом десятого СЧ и одновременно является пятым выходом первого БФА. Выход десятого СЧ соединен с вторым выходом схемы сравнения, выход которой соединен с входом второго ЭЗ. Вторые входы восьмого СЧ и восьмого элемента И, а также вход девятого СЧ объединены и подключены к выходу второго ЭЗ Первый вход первого элемента И и вход инвертора объединены и подключены к выходу пятого ДШ и одновременно являются шестым выходом первого БФА. Вторые входы четвертого MX и седьмого элемента И объединены и подключены к выходу инвертора. Выход седьмого элемента И соединен со вторым входом пятого MX. Первые управляющие входы шестого и седьмого MX объединены и подключены к выходу четвертого MX, a вторые управляющие входы их объединены и подключены к выходу пятого MX, Выходы шестого и седьмого MX являются первым и вторым адресными выходами первого БФА соответственно.

Кроме того, второй БФА содержит с первого по пятый СЧ, с первого по четвертый элементы И, первый, второй и третий MX, триггер, формирователь импульсов, ДШ и схему сравнения (СС). Второй вход первого СЧ и первый вход второго элемента И объединены и являются первым входом второго БФА, вторым входом которого является управляющий вход первого MX. Первые входы первого и третьего элементов И объединены и являются третьим входом второго БФА. Первые входы ДШ и третьего MX объединены и подключены к первому выходу первого СЧ. Вход триггера и второй вход первого MX объединены и подключены ко второму выходу первого СЧ. Вход формирователя импульсов и первый вход первого MX объединены и подключены к выходу триггера. Выход формирователя импульсов соединен с первым входом первого счетчика. Выход первого MX соединен с входом второго СЧ. Третий вход первого СЧ, второй вход ДШ и первый вход второго MX объединены 5 и подключены к выходу второго СЧ. Вторые входы первого и третьего элементов И объединены и подключены к выходу ДШ и одновременно являются выходом второго БФА. Выход первого элемента И соединен

0 со вторым входом второго элемента И, выход которого соединен со вторым входом третьего СЧ, первый вход СС и второй вход третьего MX объединены и подключены к выходу третьего СЧ. Вторые выходы второго

5 MX и СС объединены и подключены к выходу четвертого СЧ. Первые входы третьего СЧ и четвертого элемента И, а также вход пятого СЧ объединены и подключены к выходу СС. Выход пятого СЧ соединен со вторым вхо0 дом четвертого элемента И, выход которого соединен со входом четвертого СЧ. Управляющие входы второго и третьего MX объединены и подключены к выходу третьего элемента И. Выходы их являются первым и

5 вторым адресными выходами второго БФА. Кроме того, блок управления содержит тактовый генератор, датчик логического нуля, датчик логической единицы, с первого по четырнадцатый элементы ИЛ И, с первого по

о двадцать шестой элементы И, с первого по девятый триггеры (ТР), с первого по восьмой инверторы, элемент исключающее ИЛИ, с первого по восьмой ЭЗ, первую и вторую дифференцирующие цепочки (ДЦ), с перво5 го по пятый СЧ, элемент И-НЕ, ДШ, с первого по девятый MX, с первой по четвертую СС и ключ. Пергые входы первого, второго, двенадцатого, f вадцать первого и двадцать третьего элементов И, вторые входы пятого,

Q девятого, двадцатого элементов И и девятого MX, а также входы первого, восьмого, девятого ТР и первого ЭЗ объединены и подключены к выходу тактового генератора, который одновременно является третьим

с выходом БУ. Первый выход первого ТР соединен со вторым входом первого элемента И и одновременно является шестым выходом БУ. Второй выход первого ТР соединен со вторым входом второго элемента И, выходы первого и второго элементов И являются четвертым и пятым выходами БУ соответственно. Выходы датчиков логической 1 и логического 0 соединены с первым и вторым входами ключа. Управляющие входы третьего, четвертого, пятого, шестого, восьмого и девятого MX объединены и подключены к третьему выходу ключа и одновременно являются седьмым выходом БУ. Первый вход первого элемента ИЛИ является первым входом БУ, выход его соединен

0

5

со входом первой ДЦ, и одновременно - пятнадцатым выходом БУ, вторым входом которого является первый вход второго элемента ИЛИ. Первые входы десятого элемента И, третьего ТР и девятого элемента ИЛИ, а также вторые входы второго элемента ИЛИ, третьего и восьмого элементов И объединены и являются третьим входом БУ. flepsfcte входы третьих элементов И и ИЛИ, а также вход первого инвертора объединены и являются девятым вхоДом БУ, десятым входом БУ является вход второго ЭЗ, выход которого соединен с третьим входом седьмого элемента И, Первые входы седьмого элемента ИЛИ, тринадцатого элемента И, элемента ИЛИ-НЕ и четвертого MX, а также вторые входы третьего элемента ИЛИ, элемента исключающее ИЛИ и двенадцатого элемента И объединены и являются седьмым входом БУ. Выход третьего элемента ИЛИ соединен с первым входом шестого MX. Первые входы одиннадцатого элемента И и элемента исключающее ИЛИ, а также вторые входы четвертого и шестого MX объединены и подключены к выходу второго элемента ИЛИ, который одновременно является четырнадцатым выходом БУ, девятым и одиннадцатым выходами которого являются выходы четвертого и шестого MX соответственно. Первые входы четвертого, шестого, седьмого, восьмого элементов И, вторые входы двенадцатого и четырнадцатого элементов ИЛИ, двадцать второго и двадцать шестого элементов И и пятого MX, а также третьи входы двадцать четвертого и двадцать пятого элементов И объединены и подключены к выходу первого ЭЗ. Первые входы пятого элемента И и шестого элемента ИЛИ, вторые входы седьмого элемента И и пятого элемента ИЛИ, а также третьи входы четвертого и восьмого элементов И объединены и подключены к выходу первого инвертора. Вторые входы четвертого и шестого элементов И и третий вход первого элемента ИЛИ объединены и подключены к выходу элемента исключающее ИЛИ. Первые входы девятого элемента И и пятого элемента ИЛИ объединены и подключены к выходу второго ТР, первый вход которого соединен с выходом третьего элемента И, а второй вход соединен с выходом пятого элемента И. Выход девятого элемента И соединен с вторым входом третьего ТР, выход которого соединен с вторым входом шестого элемента ИЛИ. Вторые входы десятого и одиннадцатого элементов И объединены и подключены к выходу шестого элемента ИЛИ, выходы их соединены с вторыми входами четвертого и седьмого элемента ИЛИ соответственно. Первый вход четвертого

элемента ИЛИ соединен с выходом восьмого элемента И. Первый вход восьмого MX и второй вход первого элемента ИЛИ объединены и подключены к выходу седьмого элемента ИЛИ, причем выход восьмого MX является тринадцатым выходом БУ. Выход четвертого элемента ИЛИ соединен с первым входом тринадцатого элемента ИЛИ, выход которого соединен с входом пятого

0 ЭЗ и одновременно является двадцать восьмым выходом БУ, восемнадцатым выходом которого является выход четвертого элемента И. Вторые входы двадцать четвертого и двадцать пятого элементов И и третий вход

5 двадцатого элемента И объединены и являются четвертым входом БУ, а также его двадцать четвертым выходом. Вход пятого инвертора и управляющий вход седьмого MX объединены и являются пятым входом

0 БУ, одиннадцатым входом которого являет ся первый вход восьмого элемента ИЛИ, а шестым входом - вход шестого ЭЗ, выход которого соединен с входом четвертого СЧ. Восьмым входом БУ является вход второго

5 СЧ, выход которого соединен с первым входом первой СС. Выходы шестого и седьмого элементов И являются двадцатым и девятнадцатым выходами БУ, двадцать первым выходом которого является выход пятого

о элемента ИЛИ. Выход первой ДЦ соединен со входом четвертого ТР, выход которого соединен со входом третьего ЭЗ и одновременно является шестнадцатым выходом БУ. Первые входы четырнадцатого и пятнадца5 того элементов И и второго MX, а также второй вход первого MX объединены и подключены к выходу двенадцатого элемента И. Выходы восьмого и девятого элементов ИЛИ соединены с входами пятого и шестого

Q ТР соответственно, выходы которых соединены со вторыми входами тринадцатого элемента И и элемента И-НЕ соответственно, Вход второго инвертора и первый вход семнадцатого элемента И объединены и

5 подключены к выходу тринадцатого элемента И. Выход второго инвертора соединен с первым входом шестнадцатого элемента И, выход которого соединен с первым входом первого MX и одновременно является двад,. цать шестым выходом БУ. Входы четвертого инвертора и второй ДЦ, а также вторые входы шестнадцатого и восемнадцатого элементов И объединены и подключены к выходу элемента И-НЕ, который одновременно является двадцать седьмым выходом БУ. Вторые входы восьмого и девятого элементов ИЛИ и первого СЧ объединены и подключены к выходу седьмого ТР, вход которого соединен с выходом второй ДЦ. Выход первого СЧ соединен со входом ДШ.

выход которого соединен со входом третьего инвертора и вторым входом семнадцатого элемента И и одновременно является двадцать пятым выходом БУ. Первые выходы восемнадцатого и девятнадцатого элементов И, а также вторые входы первого и второго MX объединены и подключены к выходу третьего инвертора. Выход четвертого инвертора соединен со вторым входом девятнадцатого элемента И. Выходы девятнадцатого и восемнадцатого элементов И соединены со вторыми входами четырнадцатого и пятнадцатого элементов И соответственно, выходы которых соединены с первым и вторым входами десятого элемента ИЛ И соответственно. Первый вход первого СЧ и второй вход одиннадцатого элемента ИЛИ объединены и подключены к выходу десятого элемента ИЛИ. Выход семнадцатого элемента И соединен с первым входом второго MX, выход которого соединен со входом тринадцатого элемента ИЛИ. Выход первого MX соединен с первым входом двенадцатого элемента ИЛИ, выход которого соединен со входом четвертого ЭЗ и одновременно является первым выходом БУ. Выход четвертого ЭЗ соединен с первым входом пятого MX, выход которого является двенадцатым выходом БУ. Выход третьего ЭЗ соединен с первым входом одиннадцатого элемента ИЛИ, выход которого соединен с первым входом девятого MX, выход которого является восьмым выходом БУ. Выход восьмого ТР соединен с первым входом двадцатого элемента И, выход которого соединен с первым входом третьего СЧ. Выходы второй СС и седьмого ЭЗ объединены и подключены к выходу третьего СЧ, второй вход которого соединен с выходом первой СС, второй вход которой соединен с выходом седьмого ЭЗ. Выход второй СС соединен со входом шестого инвертора и одновременно является семнадцатым выходом БУ, десятым выходом которого является выход третьего MX. Первый вход двадцать второго элемента И соединен с первым входом четырнадцатого элемента ИЛИ, выход которого соединен со вторым выходом третьего MX. Выход девятого ТР соединен с первым входом седьмого MX, выход которого соединен со вторым входом двадцать третьего элемента И, выход пятого инвертора соединен со вторым входом двадцать первого элемента И, выход которого соединен с первым входом пятого счетчика. Входы третьей СС и восьмого ЭЗ объединены и подключены к выходу пятого СЧ, Первый и второй входы четвертой СС соединены с выходами четвертого СЧ и восьмого ЭЗ, а выход ее соединен со вторым входом пятого СЧ. Выход третьей СС соединен с входом седьмого инвертора, выход которого соединен с вторым входом седьмого MX. Первые входы двадцать чет- 5 вертого и двадцать шестого элементов И, второй вход восьмого MX и вход восьмого инвертора объединены и подключены к выходу двадцать третьего элемента И. Выход восьмого инвертора соединение первым вхо0 дом двадцать пятого элемента И. Выходы двадцать четвертого, двадцать пятого и двадцать шестого элементов И являются двадцать вторым, двадцать третьим и вторым выходами БУ соответственно.

5 По отношению к известным системам сжатия и обработки видеоинформации в предлагаемой системе используется сжатие видеоинформации путем применения адаптивного ортонормирующего преобразова0 ния, позволяющего формировать характеристики преобразующего устройства непосредственно по отсчетам входного изображения. В известных системах такое преобразование не используется, они осно5 ваны на других типах преобразования, таких, как преобразование Адамара, Фурье, Хаара и ряде других. Использование ортонормирующего преобразования позволило увеличить степень сжатия видеоинформао ции, т.е. увеличить объем записываемой на носитель записи информации. Кроме того, реализация ОП предусматривает выполнение в одном блоке как прямого преобразования в режиме записи видеоинформации,

5 так и обратного - в режиме воспроизведения. Существующие системы основаны на использовании двух отдельных блоков для прямого и обратного преобразования. Таким образом введенная в предлагаемое изо0 бретение совокупность существенных признаков в изве тН1ЬГ ё хнйческих решениях отсутствует, что позволяет сделать вывод о наличии у предлагаемой системы существенных отличий.

5 u ж .

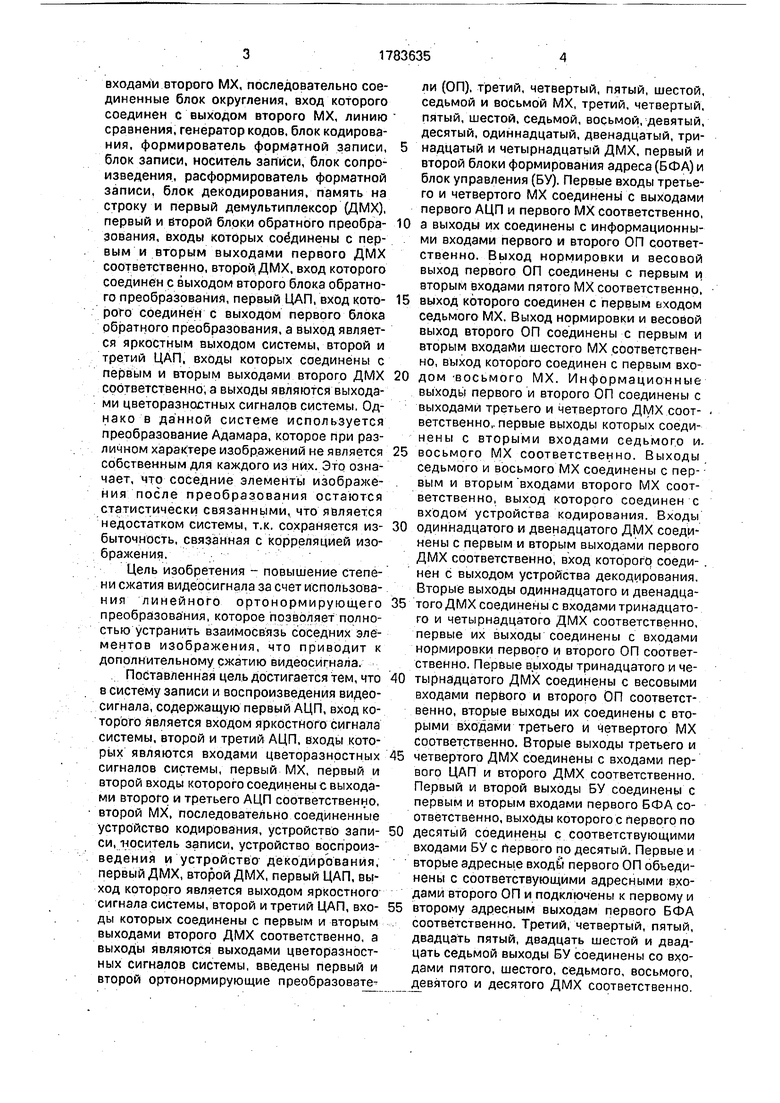

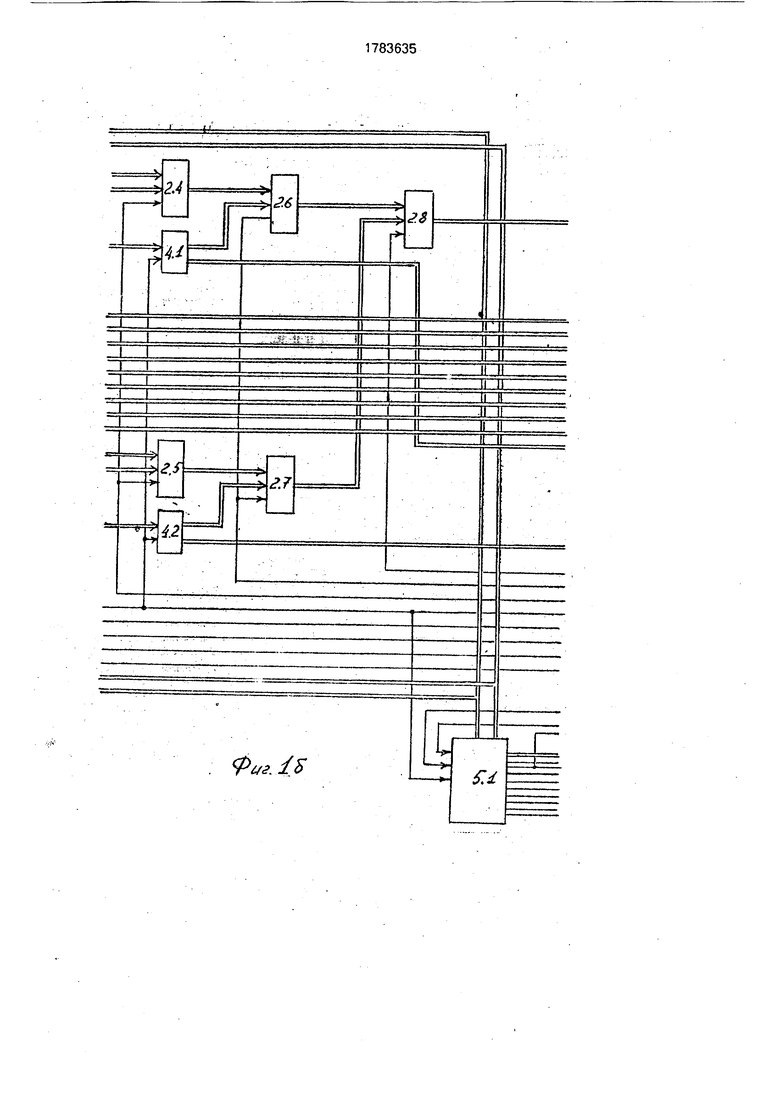

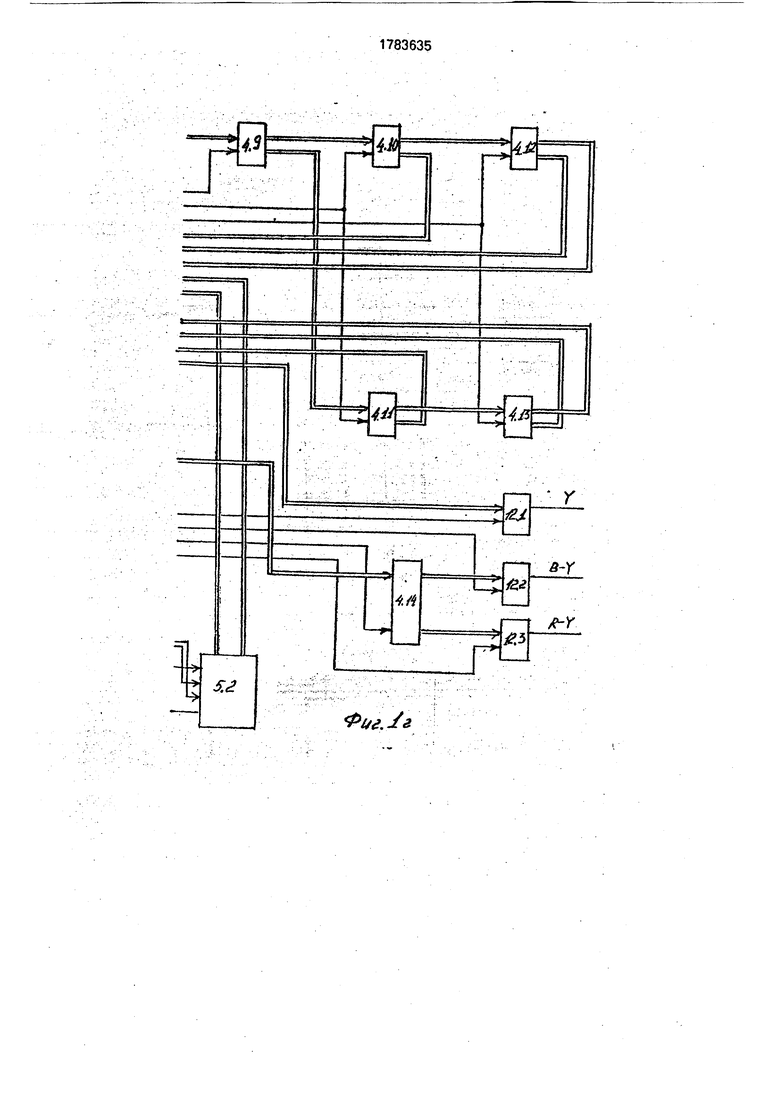

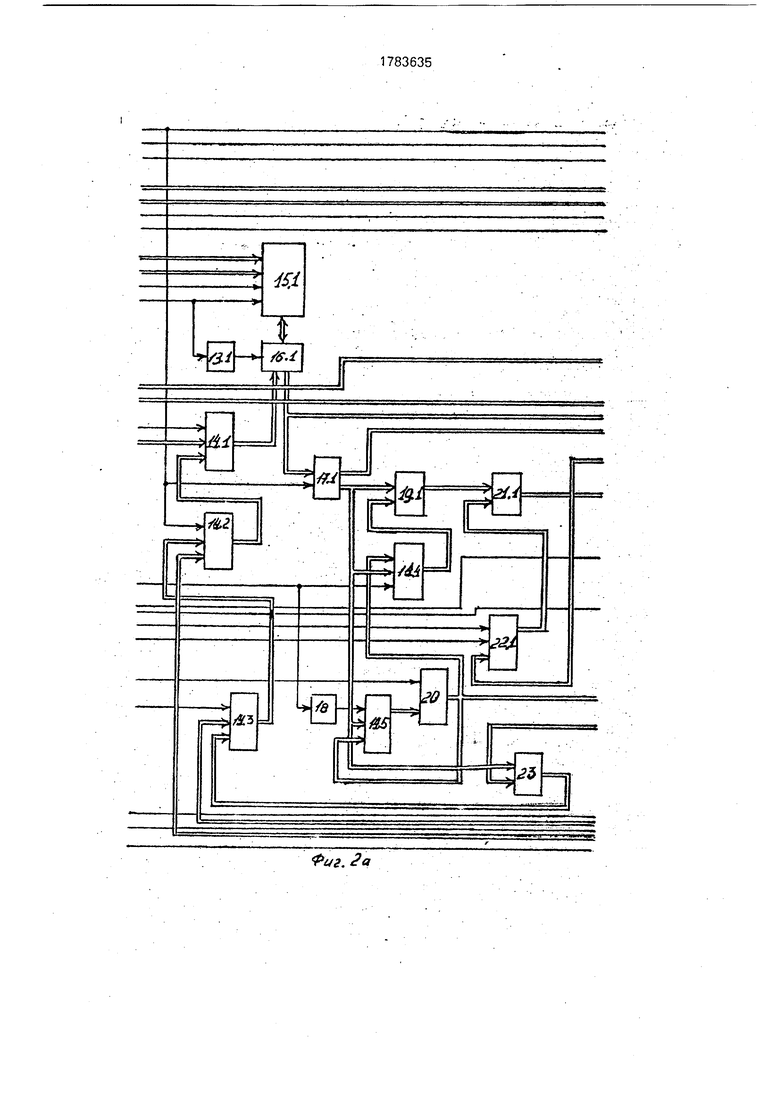

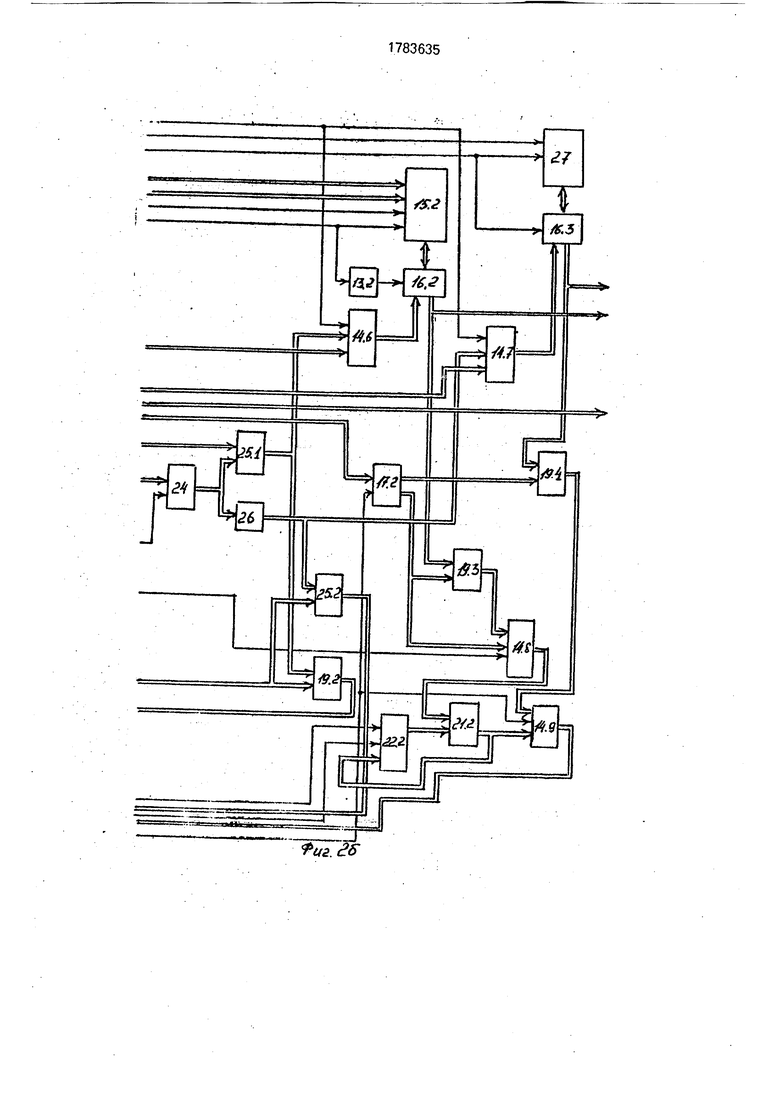

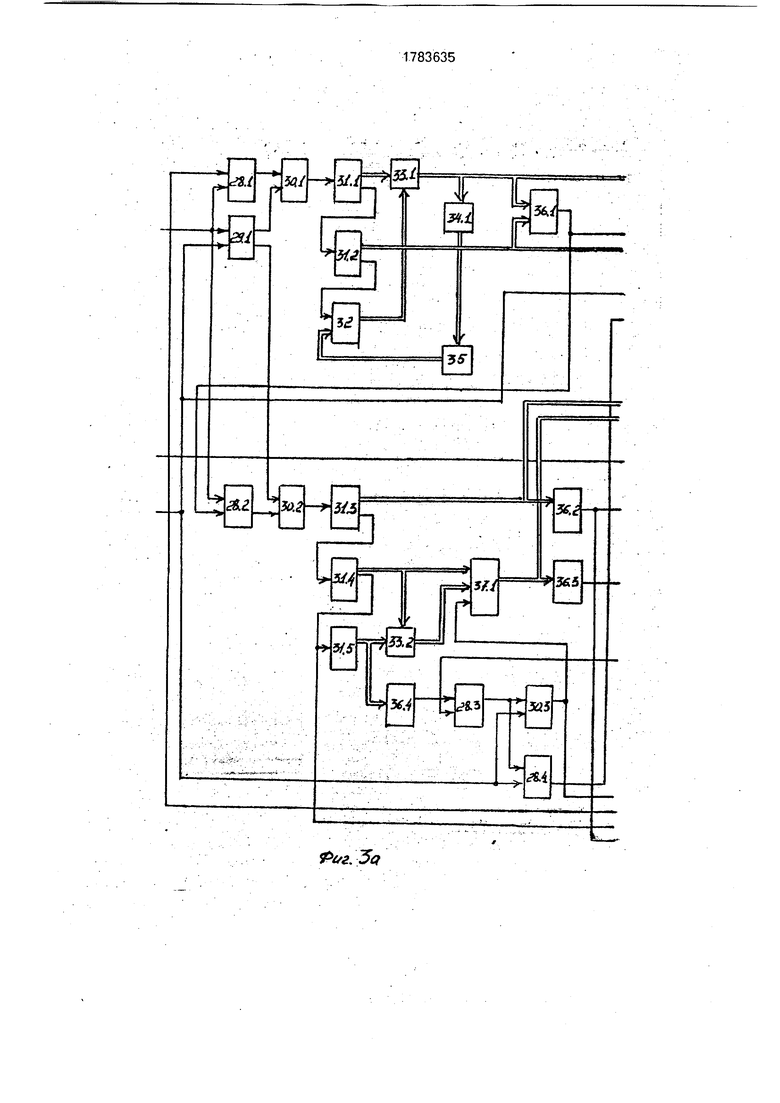

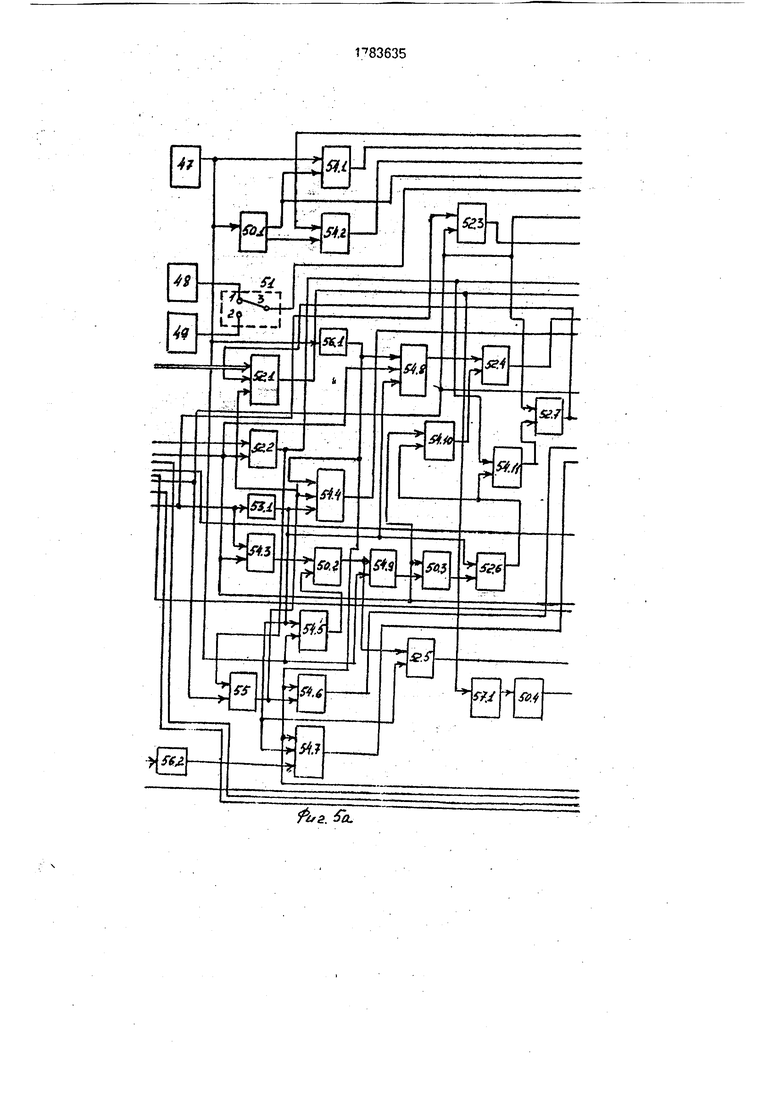

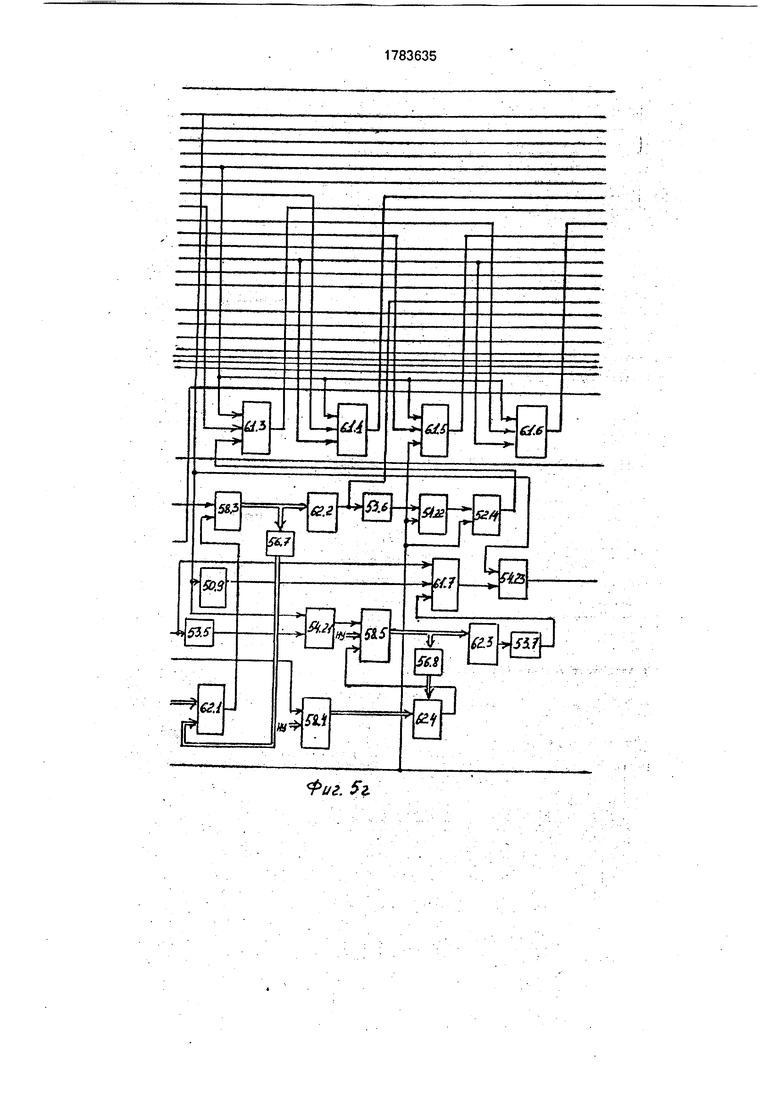

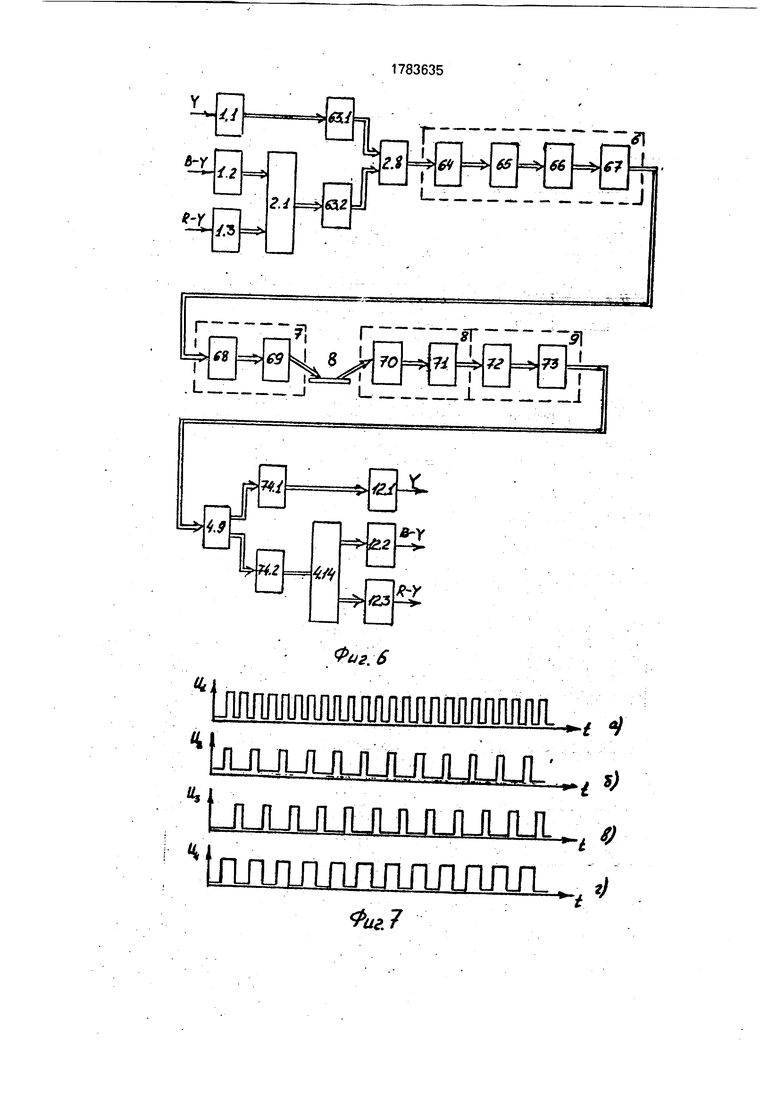

На фиг.1 приведена структурная схема

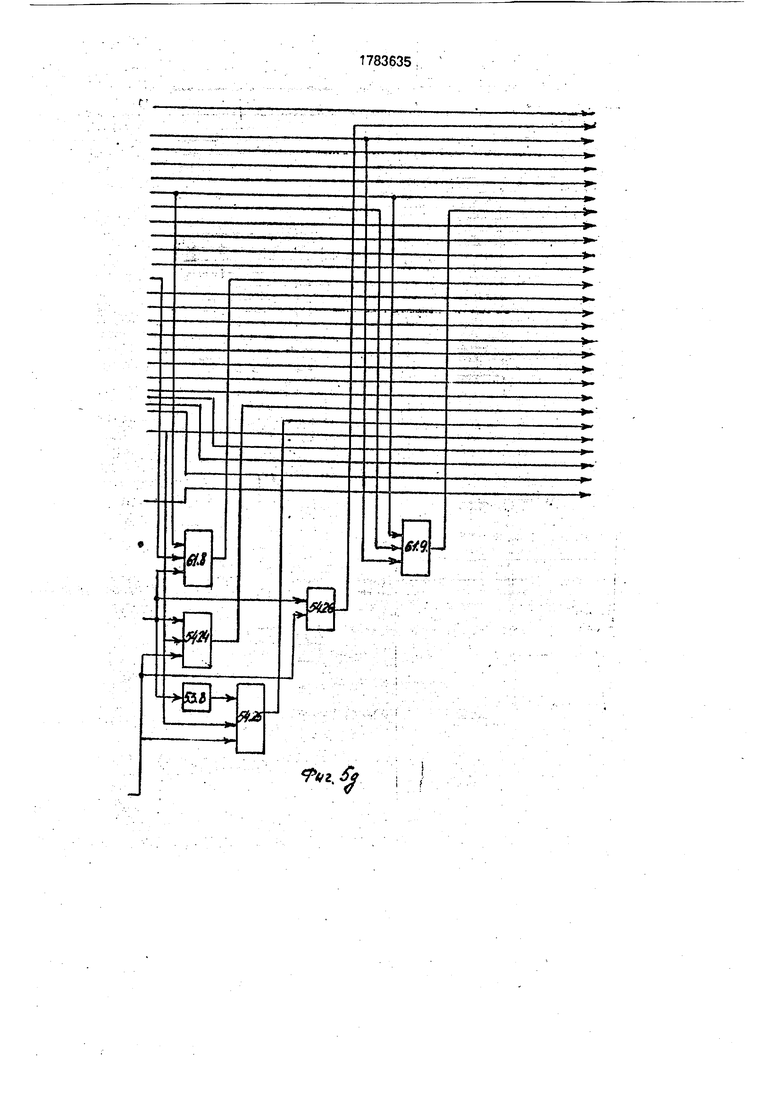

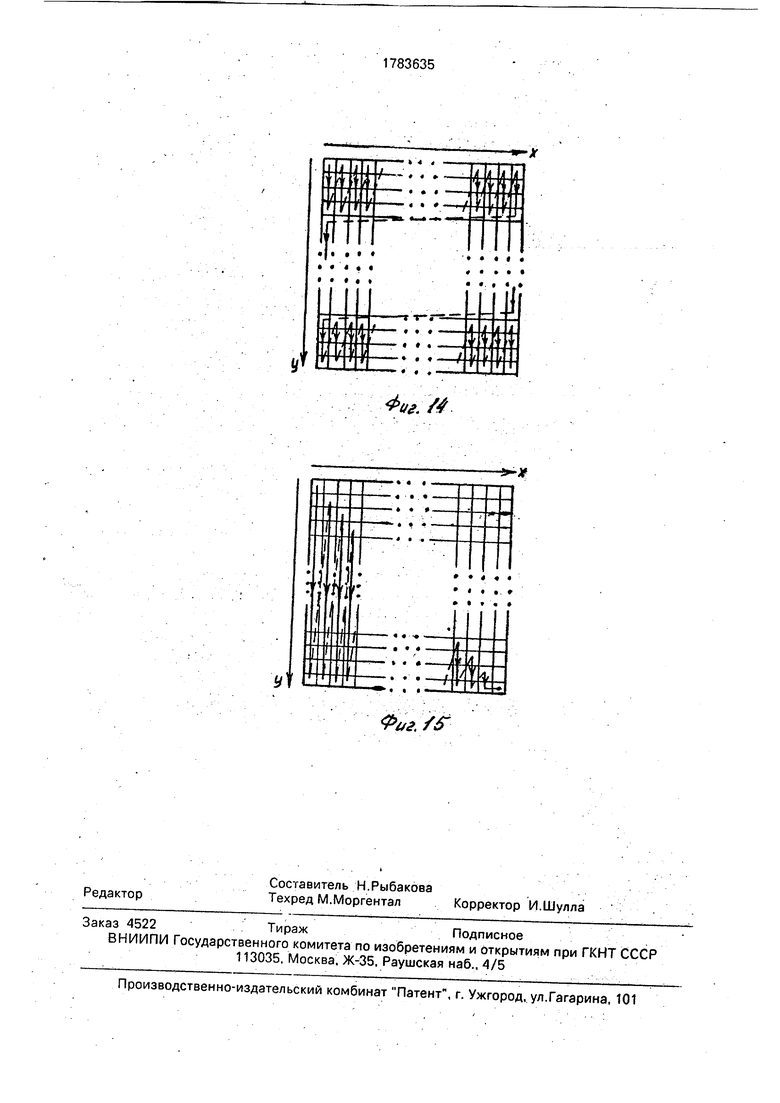

системы записи и воспроизведения видеосигнала; на фиг.2 - функциональная схема ОП; на фиг.З - функциональная схема пер- вого БФА; на фиг.4 - функциональная схема второго БФА; на фиг.5 - функциональная схема БУ; на фиг.б - структурная схема прототипа; на фиг.7 - диаграммы работы АЦП и ЦАП; на фиг.8 - диаграммы работы системы в третьем цикле режима записи и первом цикле режима воспроизведения; на фиг.9 - принцип записи исходного изображения в память ОП; на фиг. 10 - диаграммы работы ОП в первом цикле режима записи; на фиг. 11 - диаграммы работы ОП во втором

цикле режима записи; на фиг.12 - диаграммы работы ОП в третьем цикле режима записи и первом цикле режима воспроизведения; на фиг.13- диаграммы работы ОП во втором цикле режима воспроизведения; на фиг.14 - принцип адресации первого ЗУ; на фиг. 15 - принцип адресации второго ЗУ.

На фиг.1 цифрами обозначены:

1.1-1.3 - первый, второй и третий АЦП;

2.1 - первый MX;

2.2-2.7 - третий, четвертый, пятый, шестой, седьмой и восьмой MX;

2.8- второй MX;

3.1, 3.2 - первый и второй ОП;

4.1-4.8 - третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый ДМХ;

4.9- первый ДМХ:

4.10-4.13 - одиннадцатый, двенадцатый, тринадцатый, четырнадцатый ДМХ; 4.14-второй ДМХ; 5.1, 5.2 - первый и второй БФА;

6- устройство кодирования;

7- устройство записи;

8- носитель записи;

9- устройство воспроизведения;

10- устройство декодирования;

11- БУ;

12.1-12.3 - первый, второй и третий ЦАП.

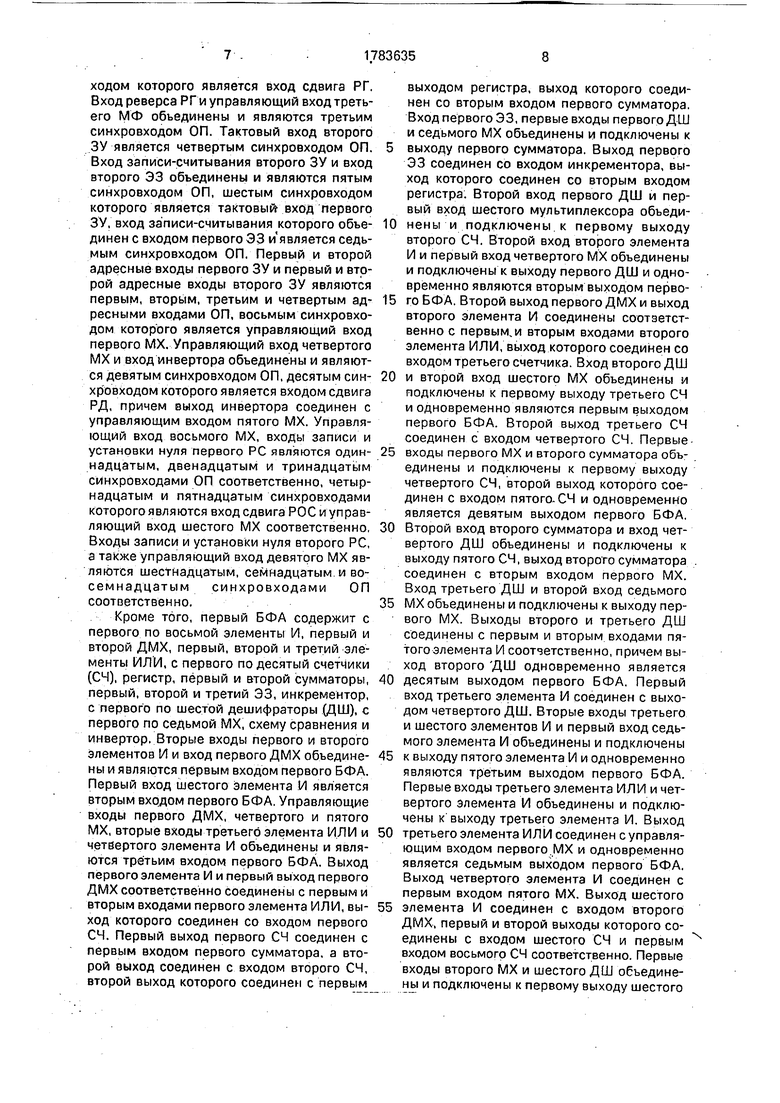

На фиг.2 цифрами обозначены: 13.1. 13.2 - первый и второй ЭЗ;

14.1- первый MX;

14.2-седьмой MX; 14.3- шестой MX;

14.4, 14.5 -четвертый и пятый MX;

14.6, 14.7 - второй и третий MX;

14.8, 14.9 - восьмой и девятый MX;

15.1, 15.2 - первое и второе ЗУ;

16.1-16.3 - первый, второй и третий ШФ;

17.1, 17.2 - первый и второй ДМХ;

18- инвертор;

19.1-19.4 - первый, второй, третий и четвертый умножители;

20 - РОС;

21.1,21.2 - первый и второй сумматоры;

22.1, 22.2 - первый и второй PC:

23- вычитатель;

24- РД;

25.1, 25.2 - первый и второй делители;

26- устройство извлечения корня;

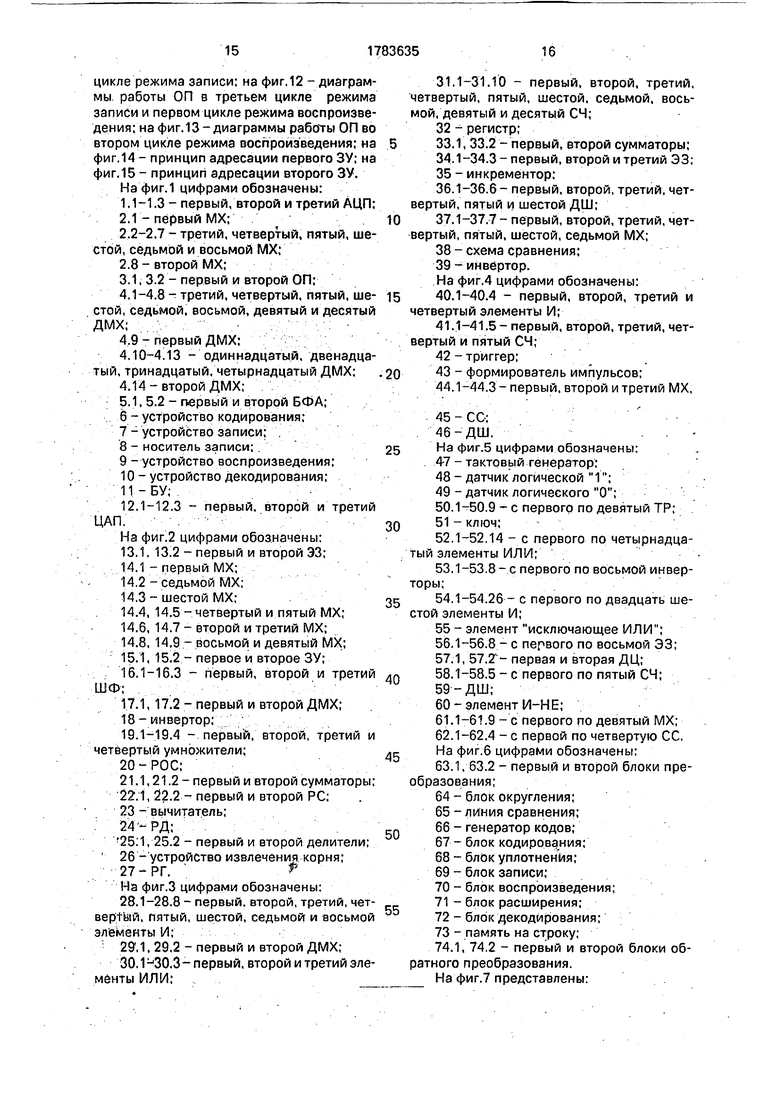

27- РГ. На фиг.З цифрами обозначены: 28.1-28.8 - первый, второй, третий, четBeptku, пятый, шестой, седьмой и восьмой элементы И;

29.1, 29.2 - первый и второй ДМХ;

30,1 30.3- первый, второй и третий элементы ИЛИ;

31.1-31.10 - первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой, девятый и десятый СЧ;

32 - регистр; 33.1, 33.2 - первый, второй сумматоры;

34.1-34.3-первый, второй и третий ЭЗ;

35 - инкрементор:

36.1-36.6 - первый, второй, третий, четвертый, пятый и шестой ДШ; 37.1-37.7- первый, второй, третий, четвертый, пятый, шестой, седьмой MX;

38- схема сравнения;

39- инвертор.

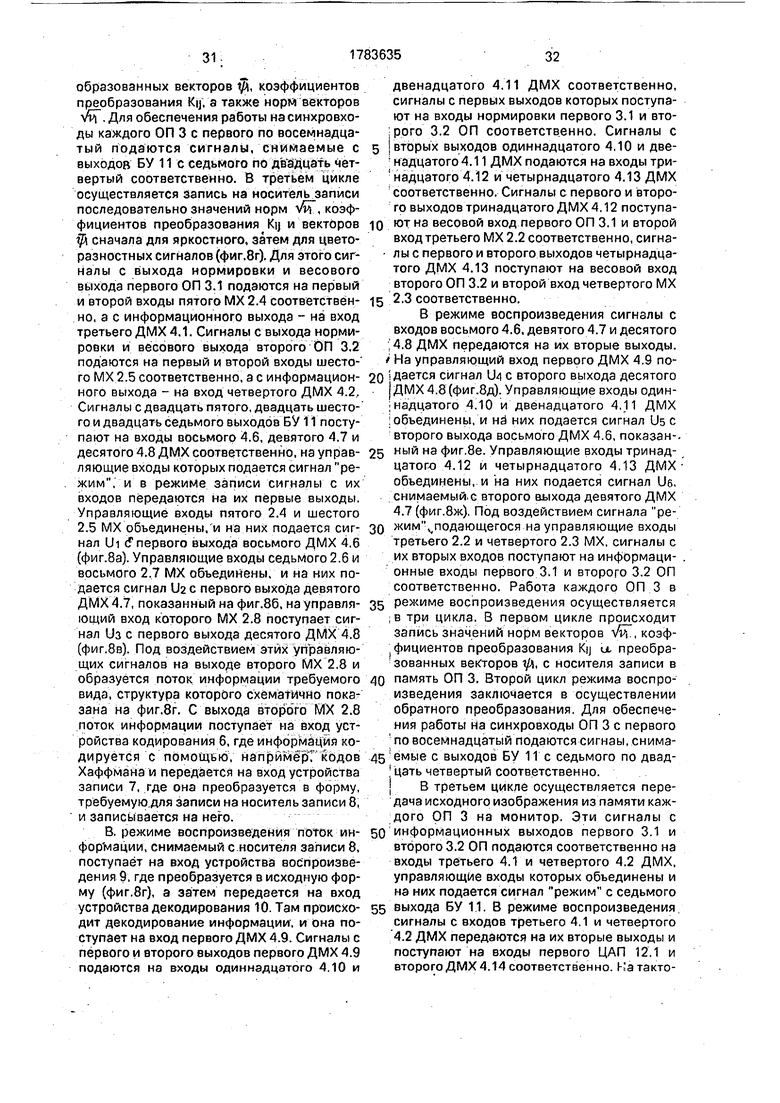

На фиг.4 цифрами обозначены: 40.1-40.4 - первый, второй, третий и четвертый элементы И;

41.1-41.5- первый, второй, третий, четвертый и пятый СЧ;

42 - триггер; 43 - формирователь импульсов;

44.1-44.3-первый, второй и третий MX,

5

45 - СС:

46-ДШ.

На фиг.5 цифрами обозначены:

47- тактовый генератор;

48- датчик логической

49- датчик логического 50.1-50.9 - с первого по девятый ТР;

о 51 - ключ;

52.1-52.14 - с первого по четырнадцатый элементы ИЛИ;

53.1-53 8 - с первого по восьмой инверторы;

5 54.1-54.26 - с первого по двадцать шестой элементы И;

55 - элемент исключающее 56.1-56.8 - с первого по восьмой ЭЗ; 57.1, 57.2- первая и вторая ДЦ; л 58.1-58.5 - с первого по пятый СЧ; 59-ДШ;

60-элемент И-Н Е; 61.1-64.9 - с первого по девятый MX; 62.1-62.4 - с первой по четвертую СС. g На фиг.6 цифрами обозначены:

63.1, 63.2 - первый и второй блоки преобразования;

64- блок округления;

65- линия сравнения;

66- генератор кодов;

67- блок кодирования;

68- блок уплотнения;

69- блок записи;

70- блок воспроизведения;

71- блок расширения;

72- блок декодирования;

73- память на строку;

74.1, 74.2 - первый и второй блоки обратного преобразования. На фиг.7 представлены:

0

5

а)- тактовые импульсы Ui первых АЦП и ЦАП;

б)- тактовые импульсы U2 вторых АЦП и ЦАП;

в)- тактовые импульсы Us третьих АЦП и ЦАП;

г)- управляющий сигнал 1М первого MX и второго ДМХ.

На фиг.8 представлены:

а)- управляющий сигнал Ui пятого и шестого MX;

б)- управляющий сигнал U2 седьмого и восьмого MX;

в)- управляющий сигнал Us второго MX;

г)- структура потока информации;

д) управляющий сигнал 1)4 первого MX;

е)- управляющий сигнал Us одиннадцатого и двенадцатого MX;

ж)- управляющий сигнал Ue тринадцатого и четырнадцатого MX.

На фиг.9 представлены:

а)- вид исходного изображения;

б)- вид записанного в память изображения.

На фиг.10 представлены: а)-управляющий сигнал Ui первого MX ОП;

б)- сигнал U2 записи-считывания первого ЗУ ОП;

в)- тактовые импульсы Уз первого ЗУ ОП.

Нафиг.11 представлены:

а)- управляющий сигнал U1 первого MX ОП;

б)- сигнал U2 записи-считывания первого ЗУ;

в)- управляющий сигнал Us четвертого MX ОП;

г)- сигнал сдвига Us РОС;

д)- сигнал записи Ue первого PC;

е)- сигнал обнуления U первого PC;

ж)- сигнал записи Us РД;

з)- сигнал сдвига Ug регистра;

и) - сигнал записи-считывания Uio второго ЗУ;

к) - тактовые импульсы Un второго ЗУ;

л) - управляющий сигнал Ui2 шестого МХОП.

На фиг. 12 представлены:

а)- импульсы сдвига Ui регистра;

б)- тактовые импульсы U2 второго ЗУ;

в)- тактовые импульсы из первого ЗУ. На фиг. 13 представлены:

а)-сигнал Ui записи-считывания первого ЗУ;

б)- управляющий сигнал U2 девятого MX ОП и второго ДМХ ОП;

в)- сигнал Ua реверса регистра:

г)- тактовые импульсы U4 первого ЗУ;

д) - тактовые импульсы Us второго ЗУ; е)-сигнал Ueзаписи-считывания второго ЗУ;

ж)- управляющий сигнал U восьмого 5 MX ОП;

з)сигнал Us записи второго PC.

Система сжатия видеоинформации содержит первый АЦП 1.1, вход которого является входом яркостного сигнала системы.

0 второй 1.2 и третий 1.3 АЦП, входы которых являются входами цветоразностных 6 игна- лов системы, первый 2.1, второй 2.8, третий 2.2, четвертый 2.3, пятый 2.4, шестой 2.5, седьмой 2.6, восьмой 2.7 MX, первый 3.1 и

5 второй 3.2 ОП, первый 4.9, второй 4.14, третий 4.1, четвертый 4.2, пятый 4.3, шестой 4.4, седьмой 4.5, восьмой 4.6, девятый 4.7, десятый 4.8, одиннадцатый 4.10, двенадцатый 4.11, тринадцатый 4.12, четырнадцатый 4.13

0 ДШХ, первый 5.1 и второй 5.2 БФА, последовательно соединенные устройство кодирования 6, устройство записи 7, носитель записи 8, устройство вопроизведения 9 и устройство декодирования 10, БУ 11, пер5 вый ЦАП 12.1, выход которого является выходом яркостного сигнала системы, второй 12.2 и третий 1.2.3 ЦАП, выходы которых являются выходами цветоразностных сигналов системы. Первый и второй входы перо вого MX 2,1 соединены с выходами второго 1.2 и третьего 1.3 АЦП соответственно. Первые входы третьего 2.2 и четвертого 2.3 MX соединены с выходами первого АЦП 1.1 и первого MX 2.1 соответственно, а выходы их

5 соединены с информационными входами первого 3.1 и второго 3.2 ОП соответственно. Выход нормировки и весовой выход первого ОП 3.1 соединены с первым и вторым входами пятого MX 2.4 соответственно, вы0 ход которого соединен с первым входом седьмого MX 2.6. Выход нормировки и весовой выход второго ОП 3.2 соединены с первым и вторы входами шестого MX 2 5 соответственно, выход которого соединен с

5 первым входом восьмого MX 2.7. Информационные выходы первого 3.1 и второго 3.2 ОП соединены с входами третьего 4.1 и четвертого 4.2 ДМХ соответственно, первые выходы которых соединены со вторыми входами седьмрго 2.6 и восьмого 2.7 MX соответственно. Выходы седьмого 2.6 и восьмого 2.7 MX соединены соответственно с первым и вторым входа м и Шестого MX 2.5, выход которого соединен с первым входом восьмого MX 2.7. Информационные выходы первого 3.1 и второго 3.2 ОП соединены с входами третьего 4.1 и четвертого 4.2 ДМХ соответственно, первые выходы которых соединены с вторыми входами седьмого 2.6 и восьмого 2.7 MX соответственно. Выходы

0

5

седьмого 2.6 и восьмого 2.7 MX соединены с первым и вторым входами второго MX 2.8 соответственно, вход которого соединен с входом устройства кодирования 6. Входы одиннадцатого 4.10 и двенадцатого 4.11 соединены с первым и вторым выходами первого ДМХ 4.9 соответственно, вход которого соединен с выходом устройства декодирования 10. Вторые выходы одиннадцатого 4.10 и двенадцатого 4.11 ДМХ соединены с входами тринадцатого 4.12 и четырнадцатого 4.13 ДМХ соответственно, первые их выходы соединены с входами нормировки первого 3.1 и второго 3.2 ОП соответственно. Первые выходы тринадцатого 4.12 и четырнадцатого 4.13 ДМХ соединены с весовыми входами первого 3.1 и второго 3.2 ОП соответственно, вторые выходы их соединены со вторыми входами третьего 2.2 и четвертого 2.3 MX соответственно. Вторые выходы третьего 4.1 и четвертого 4.2 ДМХ соединены с входами первого ЦАП 12.1 и второго ДМХ 4.14 соответственно. Первый и второй выходы второго ДМХ 4.14соединены со входами второго 12.2 и третьего 12.3 ЦАП соответственно. Первый и второй выходы БУ 11 соединены с первым и вторым входами первого БФА 5.1 соответственно, выходы которого с первого по десятый соединены с соответствующими входами БУ 11 с первого по десятый. Первые и вторые адресные входы первого ОП 3.1 объединены с соответствующими адресными входами второго ОП 3.2 и подключены к первому и второму адресным выходам первого БФА 5.1 соответственно. Третий, четвертый, пятый, двадцать пятый, двадцать шестой и двадцать седьмой выходы БУ 11 соединены со входами пятого 4.3, шестого 4.4, седьмого 4.5, восьмого 4.6, девятого 4.7 и десятого 4,8 ДМХ соответственно. Тактовые входы первого 1.1, второго 1.2 и третьего 1.3 АЦП соединены с первыми выходами пятого 4.3, шестого 4.4 и седьмого 4.5 ДМХ соответственно, вторые выходы которых соединены с тактовыми входами первого 12.1, второго 12.2 и третьего 12.3 ЦАП соответственно. Управляющие входы первого MX 2.1 и второго ДМХ 4.14 объединены и подключены к шестому выходу БУ 11. Управляющие входы третьего 2.2 и четвертого 2.3 MX, ДМХ с третьего 4.1 по десятый 4.8, первые синх- ровходы первого 3.1 и второго 3.2 ОП и третьи входы первого 5.1 и второго 5.2 БФА объединены и подключены к седьмому выходу БУ 11. Синхровходы первого ОП 3.1 со второго по восемнадцатый объединены с соответствующими синхровходами второго ОП 3.2 и подключены к выходам БУ 11 с восьмого по двадцать четвертый соответственно. Управляющие входы пятого 2.4 и шестого 2.5 MX объединены и подключены к первому выходу восьмого ДМХ 4.6, управляющие входы седьмого 2.6 и восьмого 2.7 MX объединены и подключены к первому выходу девятого ДМХ 4.7. Управляющие входы одиннадцатого 4,10 и двенадцатого 4.11 ДМХ объединены и подключены ко второму выходу восьмого ДМХ 4.6, управляющие входы тринадцатого 4.12 и четырнадцатого 4.13 ДМХ объединены и подключены ко второму выходу девятого ДМХ 4.7. Первый и второй выходы десятого ДМХ 4.8 соединены с управляющими входами второго MX 2.8 и первого ДМХ 4,9 соответственно. Первый и второй входы второго БФА 5.2 соединены с двадцать восьмым выходом БУ 11 и третьим выходом первого БФА 5.1 соответственно. Выход второго БФА 5.2 соединен с одиннадцатым входом БУ 11. Третьи и четвертые адресные входы первого ОП 3.1 объединены с соответствующими адресными входами второго ОП 3.2 и подключены к первому и второму адресным выходам второго БФА 5.2 соответственно.

Кроме того, каждый ОП 3 содержит первый 13.1 и второй 13.2 элементы задержки (ЭЗ), первый 14.1, второй 14.6, третий 14.7, четвертый 14.4, пятый 14.5, шестой 14.3. Седьмой 14.2, восьмой 14.8 и девятый 14.9 MX, первое 15.1 и второе 15.2 запоминающие устройства (ЗУ), первый 16.1, второй 16.2 и третий 16.3 шинные формирователи (ШФ), регистр (РГ)27, первый 17.1 и второй

5 17.2 ДМХ, инвертор 18, первый 19.1, второй 19.2, третий 19.3 и четвертый 19.4 умножители, регистр опорного сигнала (РОС) 20, первый 21.1 и второй 21.2 сумматоры, пер- |вый 22.1 и второй 22.2 регистры суммы (PC),

Q | регистр дисперсии (РД) 24, первый 25.1 и второй 25.2 делители, устройство извлечения корня и вычитатель 23. Первый вход первого MX 14.1, а также вторые входы вто- Фого 14.6 и третьего 14.7 мультиплексоров

5 являются информационным входом, весо- вым входом и входом нормировки ОП 3 соответственно. Выход первого MX 14.1 соединен с входом первого ШФ 16.1, вход- выход которого соединен с входом-выходом

Q данных первого ЗУ 15.1. Выход второго MX 14.6 соединен с входом второго ШФ 16.2, вход-выход которого соединен с входом-выходом данных второго ЗУ 15.2. Выход третьего MX 14.7 соединен с входом третьего ШФ

5 16.3, вход-выход которого соединен с входом-выходом данных РГ 27. Выход первого ШФ 16.1 соединен со входом первого ДМХ 17.1 и одновременно является информационным выходом ОП 3. Первый выход первого ДМХ 17.1 соединен с входом второго ДМХ

0

5

0

5

0

17.2. Первые выходы первого умножителя 19,1, пятого MX 14.5 и вычитателя 23, а также второй вход четвертого MX 14.4 объединены и подключены к второму выходу первого ДМХ 17.1. Вторые выходы четвертого 14.4 и пятого 14.5 MX, а также второго умножителя 19.2 и второго делителя 25.2 объединены и подключены к выходу РОС 20, вход которого соединен с выходом пятого MX 14.5. Выход четвертого MX 14.4 соединен со вторым входом первого умножителя 19.1, выход которого соединен со входом первого сумматора 21.1. Входы первого PC

22.1,РД 24 и первый вход первого делителя 25.1 объединены и подключены к выходу первого сумматора 21.1. второй вход которого соединен с выходом первого PC 22.1. Второй вход первого делителя 25.1 и вход устройства извлечения корня 26 объединены и подключены к выходу РД 24. Первый вход второго MX 14,6 и первый вход второго умножителя 19.2 объединены и подключены к выходу первого делителя 25.1. Первый выход третьего MX 14.7 и первый вход второго делителя 25.2 объединены и подключены к выходу устройства извлечения корня 26. Выход второго делителя 25.2 соединен с первым входом шестого MX 143. Выход второго умножителя 19.2 соединен с вторым входом вычитателя 23, выход которого соединен со вторым входом шестого MX 14.3. Выход шестого MX 14.3 соединен с первым входом седьмого MX 14.2, выход которого соединен со вторым входом первого MX 14 1. Выход второго ШФ 16.2 соединен с первым входом третьего умножителя 19.3 и одновременно является весовым выходом ОП 3. Выход третьего ШФ 16.3 соединен с первым входом четвертого умножителя 19.5 и одновре- MQHHO является выходом нормировки ОП 3. Первый выход второго ДМХ 17.2 соединен со вторым входом четвертого умножителя 19.4. Вторые входы третьего умножителя

19.3и восьмого MX 14.8 объединены и подключены к второму выходу второго ДМХ

17.2.Выход восьмого MX 14.8 соединен с первым входом второго сумматора 21.2, второй вход которого соединен с выходом второго PC 22.2. Выход четвертого умножителя

19.4соединен с первым входом девятого MX 14.9, выход которого соединен с вторым входом седьмого MX 14.2. Второй вход девятого MX 14.9 и вход второго PC 22 2 объединены и подключены к выходу второго сумматора 21.2. Управляющие входы второго 14.6, третьего 14.7 и седьмого 14.2 MX, а также первого ДМХ 17.2 объединены и являются первым синхровходом ОП 3, вторым синх- ровходом которого является вход сдвига РГ 27. Вход реверса РГ27 и управляющий вход

третьего ШФ 16.3 объединены и являются третьим синхровходом ОП 3. Тактовый вход второго ЗУ 15.2 является четвертым синхровходом ОП 3. Вход записи-считывания

5 второго ЗУ 15.2 и вход второго ЭЗ 13.2 объединены и являются пятым синхровходом ОП 3, шестым синхровходом которого является тактовый вход первого ЗУ 15.1, вход записи-считывания которого объединен с

Q входом первого ЭЗ 13.1 и является седьмым синхровходом ОП 3. Первый и второй адресные входы первого ЗУ 15.1, первый и второй адресные входы второго ЗУ 15.2 являются первым, вторым, третьим и четвертым ад5 ресными входами ОП 3 соответственно, восьмым синхровходом которого является управляющий вход первого MX 14.1. Управляющий вход четвертого MX 14.4 и вход инвертора 18 объединены и являются девятым

Q синхровходом ОП 3, десятым синхровходом которого является вход сдвига РД 24. причем выход инвертора 18 соединен с управляющим входом пятого MX 14,5. Управляющий вход восьмого MX 14.8, входы

5 записи и установки нуля первого PC 22.1 являются одиннадцатым, двенадцатым и тринадцатым синхровходамй ОП 3 соответственно, четырнадцатым и пятнадцатым синхровходами которого являются вход

n сдвига РОС 20 и управляющий вход шестого MX 14.3 соответственно. Входы записи и установки нуля второго PC 22.2, а также управляющий вход девятого MX 14.9 являются шестнадцатым, семнадцатым и восем5 надцатым синхровходами ОП 3 соответственно.

Кроме того, первый БФА 5.1 содержит с первого 28.1 по восьмой 28.8 элементы И, первый 29.1 и второй 29.2 ДМХ, первый 30.1,

л второй 30.2 и третий 30.3 элементы ИЛИ, с первого 31.1 по десятый 31.10 счетчики (СЧ), регистр 32, первый 33.1 и второй 33.2 сумматоры, первый 34.1, второй 34.2 и третий

34.3ЭЗ, инкрементор 35, с первого 36.1 по 5 шестой 36.6 дешифраторы (ДШ), с первого

37.1 по седьмой 37.7 MX, схему сравнения 38 и инвертор 39. Вторые входы первого 28.1 и второго 28.2 элементов И и вход первого ДМХ 29.1 объединены и являются пер- л вым входом первого БФА 5.1. Первый вход шестого элемента И 28.6 является вторым входом первого БФА 5.1. Управляющие входы первого ДМХ 29.1, четвертого 37.4 и пя- того 37.5 MX, вторые входы третьего 5 элемента ИЛИ 30 3 и четвертого элемента И

28.4объединены и являются третьим входом первого БФА 5.1. Выход первого эле. мента И 28.1 и первый выход первого ДМХ 29.1 соединены с первым и вторым входами первого элемента ИЛИ 30 1 соответственно.

выход которого соединен с входом первого СЧ 31.1. Первый выход первого СЧ 31.1 соединен с первым входом первого сумматора 33.1, а второй выход соединен с входом второго СЧ 31.2, второй выход которого соединен с первым выходом регистра 32, выход которого соединен с вторым уходом первого сумматора 33.1. Вход первого ЭЗ 34.1, первые входы первого ДШ 29.1 и седьмого MX 37.7 объединены и подключены к выходу первого сумматора 33.1. Выход первого ЭЗ

34.1соединен со входом инкрементора 35, выход которого соединен с вторым входом регистра 32. Второй вход первого ДШ 36.1 и первый вход шестого мультиплексора 37.6 объединены и подключены к первому выходу второго СЧ 31.2. Второй вход второго элемента И 28.2 и первый вход четвертого MX 37.4 объединены и подключены к выходу первого ДШ 35.1 и одновременно являются вторым выходом первого БФА 5.1. Второй выход первого ДМХ 29.1 и выход второго элемента И 28.2 соединены с первым и вторым входами второго элемента ИЛИ 30.2 соответственно, выход которого соединен с входом третьего счетчика 31.3. Вход второго ДШ 35.2 и второй вход шестого MX 37.6 объединены и подключены к первому выходу третьего СЧ 31.3 и одновременно являются первым выходом первого БФА 5.1. Второй выход третьего СЧ 31.3 соединен с входом четвертого СЧ 31.4. Первые входы первого MX 37.1 и второго сумматора 33.2 объединены и подключены к первому выходу четвертого СЧ 31.4, второй выход которого соединен с входом пятого СЧ 31.5 и одновременно является девятым выходом первого БФА 5.1. Второй вход второго сумматора 33.2 и вход четвертого ДШ 36.4 объединены и подключены к выходу пятого СЧ 31.5, выход второго сумматора 33.2 соединен с вторым входом первого MX 37.1 Вход третьего ДШ 36.3 и второй вход седьмого MX 37.7 объединены и подключены к выходу первого MX 37.1. Выходы второго 35.2 и третьего 36.3 ДШ соединены с первым и вторым входами пятого элемента И 28.5 соответственно, причем выход второго ДШ

36.2одновременно является десятым выходом первого БФА 5.1. Первый выход третьего элемента И 28.3 соединен с выходом четвертого ДШ 36.4. Вторые входы третьего

28.3и шестого 28.6 элементов И и первый вход седьмого элемента И 28.7 объединены и подключены к выходу пятого элемента И 28.5 и одновременно являются третьим выходом первого БФА 5.1. Первые входы третьего элемента ИЛИ 30.1 и четвертого элемента И 28.4 объединены и подключены, к выходу третьего элемента И 28.3. Выход

третьего элемента ИЛИ 30.3 соединен с управляющим входом первого MX 37,1 и одновременно является седьмым первого БФА 5.1. Выход четвертого элемента И 28.4 сое5 Динен с первым входом пятого MX 37.5. Выход шестого элемента И 28.6 соединен с входом второго ДМХ 29.2, первый и второй выходы которого соединены с входом шестого СЧ 31.6 и первым входом восьмого СЧ

0 31.8 соответственно. Первые входы второго MX 37.2 и шестого ДШ 36.6 объединены и подключены к первому выходу шестого СЧ 31.6, второй выход которого соединен с входом седьмого СЧ31.7. Первый вход третьего

15 MX 37.3 и второй вход шестого ДШ 36.6 | объединены и соединены с первым выходом седьмого СЧ 31.7. Выходывторого 37.2 и третьего 37.3 MX соединены с третьими входами шестого 37.6 и седьмого 37.7 MX соот0 ветственно. Управляющие входы второго 37.2 и третьего 37.3 MX и второго ДМХ 29.2 объединены и подключены к второму выходу седьмого СЧ и одновременно являются пятым выходом первого БФА5.1. Выход ше-5 стого ДШ 36.6 соединен с входом третьего ЭЗ 34.3, выход которого являются четвертым выходом первого БФА 5.1. Второй вход третьего MX 37.3, первые входы пятого ДШ 36.5 и схемы сравнения 38 объединены и

0 подключены к выходу восьмого СЧ 31.8. Вторые входы второго MX 37.2 и пятого ДШ 36.5 объединены и подключены к первому 1 выходу девятого СЧ 31.9, второй выход которого соединен с первым входом восьмого

5 элемента И 28.8, выход которого соединен с входом десятого СЧ 31.10 и одновременно является пятым в ыходом первого БФА 5.1. Выход десятого СЧ 31.10 соединен со вторым выходом схемы сравнения 38, выход

0 которой соединен со входом второго ЭЗ 34.2. Вторые входы восьмого СЧ 31.8 и восьмого элемента И 28.8, а также вход девятого СЧ 31.9 объединены и подключены к выходу второго ЭЗ 34.2. Первый вход первого эле5 мента И 28.1 и вход инвертора 39 объединены и подключены к выходу пятого ДШ 36.5 и одновременно являются шестым выходом первого БФА 5.1. Вторые входы четвертого MX 37.4 и седьмого элемента И 28.7 объеди0 нены и подключены к выходу инвертора 39. Выход седьмого элемента И 28.7 соединен с вторым входом пятого MX 37.5. Первые управляющие входы шестого 37.6 и седьмого 37.7 MX объединены и подключены к вы- 5 ходу четвертого MX 37.4, а вторые управляющие входы их объединены и подключены к выходу пятого MX 37.5. Выходы шестого 37.6 и седьмого 37.7 MX являются первым и вторым адресными выходами первого БФА 5.1 соответственно.

Кроме того, второй БФА 5.2 содержит с первого 41.1 по пятый 41.5 СЧ, с первого 40.1 по четвертый 40.4 элементы И, первый 44.1, второй 44.2 и третий 44.3 MX, триггер 42, формирователь импульсов 43, ДШ 46 и схему сравнения (СС) 45. Второй вход первого СЧ 41.1 и первый вход второго элемента И 40.2 объединены и являются первым входом второго БФА 5.2, вторым входом которого является управляющий вход первого MX 44.1. Первые входы первого 40.1 и третьего 40.3 элементов И объединены и являются третьим-входом второго БФА 5.2. Первые входы ДШ 46 и третьего MX 44.3 объединены и подключены к первому выходу первого СЧ 41.1. Вход триггера 42 и второй вход первого MX 44.1 объединены и подключены к второму выходу первого СЧ 41.1. Вход формирователя импульсов 43 и первый вход первого MX 44.1 объединены и подключены к выходу триггера 42. Выход формирователя импульсов 43 соединен с первым входом первого счетчика 41.1. Выход первого MX 44.1 соединен со входом второго СЧ 41.2. Третий вход первого СЧ 41.1, второй вход ДШ 46 и первый вход второго MX 44.2 объединены и подключены к выходу второго СЧ 41.2. Вторые входы первого 40.1 и третьего 40.3 элементов И объединены и подключены к выходу ДШ 46 и одновременно являются выходом второго БФА 5.2, Выход первого элемента И 40.1 соединен с вторым входом второго элемента И 40.2, выход которого соединен с вторым входом третьего СЧ 41.3, первый вход СС45 и второй вход третьего MX 44,3 объединены и подключены к выходу третьего СЧ 41.3, Вторые выходы второго MX 44.2 и СС 45 объединены и подключены к выходу четвертого СЧ 41,4. Первые входы третьего СЧ 41.3 и четвертого элемента И 40.4, а также вход пятого СЧ 41.5 объединены и подключены к выходу СС 45. Выход пятого СЧ 41.5 соединен с вторым входом четвертого элемента И 40.4, выход которого соединен с входом четвертого СЧ 41.4. Управляющие входы второго 44,2 и третьего 44.3 MX объединены и подключены к выходу третьего элемента И 40.3. Выходы их являются первым и вторым адресными выходами второго БФА 5.2 соот- -ветственно.

Кроме того, блок управления 11 содержит тактовый генератор 47, датчик логического нуля 49, датчик логической единицы 48, с первого 52.1 по четырнадцатый 52.14 элементы ИЛИ, с первого 54.1 по двадцать шестой 54.26 - элементы И, с первого 50.1 по девятый 50.9 - триггеры (ТР), с первого 53.1 по восьмой 53.8 - инверторы, элемент исключающее ИЛИ 55, с первого 56,1 по

восьмой 56.8 ЭЗ, первую 57.1 и вторую 57.2 - дифференцирующие цепочки (ДЦ), с первого 58.1 по пятый 58.5 СЧ - элемент И-НЕ 60, ДШ 59, с первого 61,1 по девятый 61.9MX, с первой 62.1 по четвертую 62.4 - СС и ключ 51. Первые входы первого 54.1, второ- го54.2, двенадцатого 54.12, двадцать первого 54.21 и двадцать третьего 54.23 элементов И, вторые входы пятого 54.5, деQ вятого 54.9, двадцатого 54.20 элементов И и девятого MX 61.9, а также входы первого 50.1, восьмого 50.8. девятого 50.9 ТР и первого ЭЗ 57.1 объединены и подключены к выходу тактового генератора 47, который

g одновременно является третьим выходом БУ 11. Первый выход первого ТР 50.1 соединен с вторым входом первого элемента И

54.1и одновременно является шестым выходом БУ 11. Второй выход первого ТР 50.1

Q соединен с вторым входом второго элемента И 54.2, выходы первого 54.1 и второгр

54.2элементов И являются четвертым и пятым выходами БУ 11 соответственно. Выходы датчиков логической 1 48 и логического

J- О, выходы третьего 61.3, четвертого 61.4, пятого 61.5, шестого 61.6, восьмого 61.8 и девятого 61.9 MX объединены и подключены к третьему входу ключа 51 и одновременно являются седьмым выходом БУ 11. Первый

Q вход первого элемента ИЛИ 52.1 является первым входом БУ 11, выход его соединен с входом первой ДЦ 57.1 и одновременно является пятнадцатым выходом БУ 11, вторым входом которого является первый вход вто2 рого элемента ИЛИ 52.2. Первые входы десятого элемента И 54.10, третьего ТР 50.3 и девятого элемента ИЛ И 52.9, а также вторые входы второго элемента ИЛИ 52.2, третьего

54.3и восьмого 54.8 элементов И объедине- Q ны и являются третьим входом БУ 11. Первые входы третьих элементов И 54.3 и ИЛИ 52.3, а также вход первого инвертора 53.1 объединены и являются девятым входом БУ 11, десятым входом которого является вход

5 второго ЭЗ 56.2, выход которого соединен с третьим входом седьмого элемента И 54.7. Первые входы седьмого элемента ИЛИ 52.7, тринадцатого элемента И 54.13, элемента И-НЕ 60 и четвертого MX 61.4, а также втоQ рые входы третьего элемента ИЛИ 52.3, элемента исключающее ИЛИ 55 и двенадцатого элемента И 54.12 объединены и являются седьмым входом БУ 11. Выход третьего элемента ИЛИ 54.3 соединен с перt- вым входом шестого MX 61.9. Первые входы одиннадцатого элемента И 54.11 и элемента исключающее ИЛИ 55, а также вторые входы четвертого 61.4 и шестого 61.6 MX объединены и подключены к выходу второго элемента ИЛИ 52.2, который одновременно

является четырнадцатым выходом БУ11, девятым и одиннадцатым выходами которого являются выходы четвертого 61.4 и шестого

61.6MX соответственно. Первые входы четвертого 54.4, шестого 54.6, седьмого 54.7. восьмого 54.8 элементов И, вторые входы двенадцатого 52.12 и четырнадцатого 52.14 элементов ИЛИ,двадцать второго 54.22 и двадцать шестого 54.6 элементов И и пятого MX 61.5,а также третье вхбйьГДВЗАДЦ ать четвертого 54.24, и двадцать пятого 54.25 элементов И объединены и подключены к выходу первого ЭЗ 56.1. Первые входы пятого элемента И 54.5 и шестого элемента ИЛИ 52.6, вторые входы седьмого элемента И

54.7и пятого элемента ИЛИ 52.5, а также третьи входы четвертого 54.4 и восьмого

54.8элементов И объединены и подключены к выходу первого инвертора 53.1. Вторые входы четвертого 54.4 и шестого 44.6 элементов И и третий вход первого элемента ИЛИ 52.1 объединены и подключены к выходу элемента исключающее ИЛИ 55. Первые входы девятого элемента И 54.9 и пятого элемента ИЛИ 52.5 объединены и подключены к выходу второго ТР 50.2, первый вход которого соединен б выходом третьего элемента И 54.3. а второй вход соединен с выходом пятого элемента И 54.5. Выход девятого элемента И 54.9 соединен с вторым входом третьего ТР, выход которого соединен с вторым входом шестого элемента ИЛИ 52.6. Вторые входы десятого 54.10 и одиннадцатого 54.22 элементов И объединены и подключены к выходу шестого элемента ИЛИ 52.6, выходы их соединены с вторыми входами четвертого 52.4 и седьмого 52.7 элементов ИЛИ соответственно. Первый вход четвертого элемента ИЛИ 52.4 соединен с выходом восьмого элемента И 54.8. Первый вход восьмого MX 61.8 и второй вход первого элемента ИЛИ 52.1 объединены и подключены к выходу седьмого элемента ИЛИ 52.7, причем выход восьмого MX 61.8 является тринадцатым выходом БУ 11. Выход четвертого элемента ИЛИ 52.4 соединен с первым входом тринадцатого элемента ИЛИ 52.13, выход которого соединен с входом пятого ЭЗ 56.5 и одновременно является двадцать восьмым выходом БУ 11,-восемнадцатым выходом которого является выход четвертого элемента И 54.4. Вторые входы двадцать четвертого 54.24 и двадцать пятого 54.25 элементов И и третий вход двадцатого элемента И 54.20 объединены и являются четвертым входом БУ 11, а также его двадцать четвертым выходом. Вход пятого инвертора 53.5 и управляющий вход седьмого MX 61.7 объединены и являются пятым входом БУ 11, одиннадцатым

5

0

5

0

5

0

5

0

5

входом которого является первый вход восьмого элемента ИЛИ 52.8, а шестым входом - вход шестого ЭЗ 56.6, выход которого соединен с входом четвертого СЧ 58.4. Восьмым входом БУ 11 является вход второго СЧ

58.2,выход которого соединен с первым входом первой СС 62.2. Выходы шестого 54.6 и седьмого 54,7 элементов И являются двадцатым и девятнадцатым выходами БУ 11, двадцать первым выходом которого является выход пятого элемента ИЛИ 52.5. Выход первой ДЦ 57.1 соединен с входом четвертого ТР 50.4, выход которого соединен с входом третьего ЭЗ 56.3 м одновременно является шестнадцатым выходом БУ 11. Первые входы четырнадцатого 54.14 и пятнадцатого 54.15 элементов И и второго второго MX 61.2, а также второй вход первого MX 61.1 объединены и подключены к выходу двенадцатого элемента И 54.12. Выходы восьмого 52.8 и девятого 52.9 элементов ИЛИ соединены с входами пятого 50.5 и шестого 50,6 ТР соответственно, выходы которых соединены с вторыми входами тринадцатого элемента И 54.13 и элемента И-НЕ 60 соответственно. Вход второго инвертора 53.2 и первый вход семнадцатого элемента И 54.17 объединены и подключены к выходу тринадцатого элемента И 54.13. Выход второго инвертора 53.2 соединен с первым входом шестнадцатого элемента И 54.16, выход которого соединен с первым входом первого MX 61.1 и одно- временно является двадцать шестым выходом БУ 11. Входы четвертого инвертора 53.4 и второй ДЦ 57.2. а также вторые входы шестнадцатого 54.16 восемнадцатого

54.18элементов И объединены и подключены к выходу элемента И-НЕ 60, который одновременно является двадцать седьмумч выходом БУ 11. Втдрые входы восьмого 52,8 и девятого 52.9 элементов-ИЛИ и первого СЧ 58.1 объединены и подключены к выходу седьмого ТР 50.7, вход которого соединен с выходом второй ДЦ 57.2. Выход первого СЧ 58.1 соединен с входом ДШ 59, выход которого соединен с входом третьего инвертора 53,3 и вторым входом семнадцатого элемента И 54.17 и одновременно является двадцать пятым выходом БУ 11. Первые входы восемнадцатого 54.18 и девятнадцатого

54.19элементов И, а также вторые входы первого 61.1 и второго 61.2 MX объединены и подключены к выходу третьего инвертора

53.3.Выход четвертого инвертора 53.4 соединен с вторым входом девятнадцатого элемента И 54.19. Выходы девятнадцатого 54.19 и восемнадцатого 54.18 элементов И соединены с вторыми входами четырнадцатого 54.14 и пятнадцатого 54,15 элементов

И соответственно, выходы которых соединены с первым и вторым входами десятого элемента ИЛИ 52.10 соответственно. Пер-, вый вход первого СЧ 58.1 и второй вход одиннадцатого элемента ИЛ И 52.11 объединены и подключены к выходу десятого элемента ИЛИ 52.10. Выход семнадцатого элемента И 54.17 соединен с первым входом второго MX 61.2, выход которого соединен с вторым входом тринадцатого элемента ИЛИ 52.13. Выход первого MX 61.1 соединен с первым входом двенадцатого элемента ИЛИ 52.12, выход которого соединен с входом четвертого ЭЗ 56.4 и одновременно является первым выходом БУ 11. Выход четвертого ЭЗ 56.4 соединен с первым входом пятого MX 61.5, выход которого является двенадцатым выходом БУ 11. Выход третьего ЭЗ 56.3 соединен с первым входом одиннадцатого элемента ИЛИ 52.11, выход которого соединен с первым входом девятого MX 61.9, выход которого является восьмым выходом БУ 11, Выход восьмого ТР 50.8 соединен с первым входом двадцатого элемента И 54.20, выход которого соединен с первым входом третьего СЧ 58.3. Входы второй СС 62.2 и седьмого ЭЗ 56.7 объединены и подключены к выходу третьего СЧ 58.3, второй вход которого соединен с выходом первой СС 62,1, второй вход которой соединен с выходом седьмого ЭЗ 56.7. Выход второй СС 62.2 соединен с входом шестого инвертора 53.6 и одновременно является семнадцатым выходом БУ 11, десятым выходом которого является выход третьего MX 61.3. Первый вход двадцать второго элемента И 54.22 соединен с первым входом четырнадцатого элемента ИЛИ 52.14, выход которого соединен с вторым выходом третьего MX 61.3. Выход девятого ТР 50.9 соединен с первым входом седьмого MX 61.7, выход которого соединен с вторым входом двадцать третьего элемента И 54.23, выход пятого инвертора 53.5 соединен с вторым входом двадцать первого элемента И 54.21, выход которого соединен с первым входом пятого счетчика 58.5. Входы третьей СС 62.3 и восьмого ЭЗ 56.8 объединены и подключены к выходу пятого СЧ 58.5. Первый и второй входы четвертый СС 62.4 соединены с выходами четвертого СЧ 58.4 и восьмого ЭЗ 56.8 соответственно, а выход ее соединен с вторым входом пятого СЧ 58,5. Выход третьей СС 62.3 соединен с входом седьмого инвертора 53.7, выход которого соединен с вторым входом седьмого MX 61.7. Первые входы двадцать четвертого 54.24 и двадцать шестого 54.26 элементов И, второй вход восьмого MX 61.8 и вход восьмого инвертора 53.8 объединены и подключены к выходу

двадцать третьего элемента И 54.23. Выход восьмого инвертора 53.8 соединен с первым входом двадцать пятого элемента И 54.25. Выходы двадцать четвертого 54.24, двад- 5 цать пятого 54.25 и двадцать шестого 54.26 элементов И являются двадцать вторым, двадцать третьим и вторым выходами БУ 11 соответственно.

0 Система сжатия видеоинформации работает следующим образом. В режиме записи на вход первого АЦП 1.1 подается яркостный сигнал, а на входы второго 1.2 и третьего 1.3 АЦП подаются цветоразност5 ные сигналы. Тактовые импульсы с третьего, четвертого и пятого выходов БУ 11 подаются на входы пятого 4.3, шестого 4,4 и седьмого 4.5 ДМХ соответственно. Под воздействием сигнала режим, снимаемого с седьмого

0 выхода БУ 11 и подающегося на управляющие входы ДМХ 4.3-4.8, тактовые импульсь с их первых выходов подаются на тактовые входы первого 1.1, второго 1.2 и третьего 1.3 АЦП соответственно. С выхода первого АЦП

5 1.1 яркостный сигнал, преобразованный в цифровую форму, подается на первый вход третьего MX 2.2. Преобразованные в цифровую форму цветоразностные сигналы с выходов второго 1,2 и третьего 1.3 АЦП

0 подаются на первый и второй входы первого MX 2.1 соответственно. Как показано на фиг.7, тактовые импульсы первого АЦП 1.1 (фиг.7а) имеют в два раза большую частоту следования по сравнению с тактовыми им5 пульсами второго 1.2 (фиг.7б) и третьего 1.3 (фиг.7в) АЦП, причем тактовые сигналы второго 1.2 и третьего 1.3 АЦП сдвинуты по фазе на половину периода. Это позволяет объединить информацию с выходов второго

0 1 -2 и третьего 1.3 АЦП в один поток на выходе первого MX 2.1, на управляющий вход которого подается сигнал с шестого выхода БУ 11 (фиг.7г). Сигнал с выхода первого MX 2.1 подается на первый вход четвертого MX

5 2.3. Управляющие входы третьего 2.2 и четвертого 2.3 MX объединены и на них подается сигнал режим с шестого выхода БУ 11. Сигналы с выходов третьего 2.2 и четвертого 2.3 MX поступают на информационные вхо0 ды первого 3.1 и второго 3.2 ОП соответственно. В режиме записи на эти входы поступают сигналы с первых входов третьего 2.2 и четвертого 2.3 MX соответственно. Работа каждого ОП 3 в режиме записи осу5 ществляется в три цикла. В первом цикле происходит запись сигнала изображения в память ОП 3. Второй цикл режима записи заключается в осуществлении прямого ор- тонормирующего преобразования сигнала изображения с вычислением значений преобразованных векторов $, коэффициентов преобразования Кц. а также норм векторов wT. Для обеспечения работы насинхровхо- ды каждого ОП 3 с первого по восемнадцатый подаются сигналы, снимаемые с выходов БУ 11 с седьмого по дйадца-ть четвертый соответственно. В третьем цикле осуществляется запись на носитель записи последовательно значений норм , коэффициентов преобразования KIJ и векторов $ сначала для яркостного, затем для цвето- разностных сигналов (фиг.Вг). Для этого сигналы с выхода нормировки и весового выхода первого ОП 3.1 подаются на первый и второй входы пятого MX 2.4 соответственно, а с информационного выхода - на вход третьего ДМХ 4.1. Сигналы с выхода нормировки и весового выхода второго ОП 3.2 подаются на первый и второй входы шесто- го MX 2.5 соответственно, а с информационного выхода - на вход четвертого ДМХ 4.2. Сигналы с двадцать пятого, двадцать шестого и двадцать седьмого выходов БУ 11 поступают на входы восьмого 4.6, девятого 4.7 и десятого 4.8 ДМХ соответственно, на управляющие входы которых подается сигнал режим, и в режиме записи сигналы с их входов передаются на их первые выходы. Управляющие входы пятого 2.4 и шестого 2.5 MX объединены, и на них подается сигнал Ui f первого выхода восьмого ДМХ 4.6 (фиг.8а). Управляющие входы седьмого 2.6 и восьмого 2.7 MX объединены, и на них подается сигнал IJ2 с первого выхода девятого ДМХ 4.7, показанный на фиг.86. на управляющий вход которого MX 2.8 поступает сигнал Уз с первого выхода десятого ДМХ 4.8 (фиг.бв). Под воздействием этих управляющих сигналов на выходе второго MX 2.8 и образуется поток информации требуемого вида, структура которого схематично показана на фиг.8г. С выхода второго MX 2.8 поток информации поступает на вход устройства кодирования 6, где информация кодируется с помощью, например кодов Хаффмана и передается на вход устройства записи 7, где она преобразуется в форму, требуемую для записи на носитель записи 8, и записывается на него.

В. режиме воспроизведения поток информации, снимаемый с носителя записи 8, поступает на вход устройства воспроизведения 9, где преобразуется в исходную форму (фиг.8г), а затем передается на вход устройства декодирования 10. Там происходит декодирование информации, и она поступает на вход первого ДМХ 4.9. Сигналы с первого и второго выходов первого ДМХ 4.9 подаются на входы одиннадцатого 4.10 и

двенадцатого 4.11 ДМХ соответственно, сигналы с первых выходов которых поступают на входы нормировки первого 3.1 и второго 3.2 ОП соответственно. Сигналы с (вторых выходов одиннадцатого 4.10 и две- надцатого 4.11 ДМХ подаются на входы три- надцатого 4.12 и четырнадцатого 4.13 ДМХ соответственно. Сигналы с первого и второго выходов тринадцатого ДМХ 4.12 поступа- ют на весовой вход первого ОП 3.1 и второй вход третьего MX 2.2 соответственно, сигна- лы с первого и второго выходов четырнадцатого ДМХ 4.13 поступают на весовой вход второго ОП 3.2 и второй вход четвертого MX 2.3 соответственно.

В режиме воспроизведения сигналы с входов восьмого 4.6, девятого 4.7 и десятого 4.8 ДМХ передаются на их вторые выходы. t На управляющий вход первого ДМХ 4.9 по- i дается сигнал 1)4 с второго выхода десятого | ДМХ 4.8 (фиг.8д). Управляющие входы один- ; надцатого 4.10 и двенадцатого 4.11 ДМХ объединены, и не них подается сигнал Us с второго выхода восьмого ДМХ 4.6, показан-. ный на фиг.Зе. Управляющие входы тринадцатого 4.12 и четырнадцатого 4.13 ДМХ объединены, и на них подается сигнал Us, снимаемый, с второго выхода девятого ДМХ 4.7 (фиг.8ж). Под воздействием сигнала ре- жим подзющегося на управляющие входы третьего 2.2 и четвертого 2.3 MX, сигналы с их вторых входов поступают на информационные входы первого 3.1 и второго 3.2 ОП соответственно. Работа каждого ОП 3 в режиме воспроизведения осуществляется ,в три цикла. В первом цикле происходит запись значений норм векторов fv , коэффициентов преобразования KIJ UL преобразованных векторов $, с носителя записи в память ОП 3, Второй цикл режима воспроизведения заключается в осуществлении обратного преобразования. Для обеспечения работы на синхровходы ОП 3 с первого по восемнадцатый подаются сигнаы, снима- емые с выходов БУ 11 с седьмого по двад- цать четвертый соответственно. { В третьем цикле осуществляется передача исходного изображения из памяти каждого ОП 3 на монитор. Эти сигналы с информационных выходов первого 3.1 и второго 3.2 ОП подаются соответственно на входы третьего 4.1 и четвертого 4.2 ДМХ, управляющие входы которых объединены и на них подается сигнал режим с седьмого выхода БУ 11. В режиме воспроизведения сигналы с входов третьего 4.1 и четвертого 4.2 ДМХ передаются на их вторые выходы и поступают на входы первого ЦАП 12.1 и второго ДМХ 4.14 соответственно. Катакто33

вые входы первого 12.1, второго 12.2 и третьего 12.3 ЦАП подаются тактовые сигналы с вторых выходов пятого 4.3, шестого 4.4 и седьмого 4.5 ДМХ соответственно (фиг.7а,б,в). На управляющий вход второго ДМХ 4.14 подается сигнал с шестого выхода БУ 11 (фиг.7г). Сигналы с первого и второго выходов второго ДМХ 4.14 поступают на входы второго 12,2 и третьего 12.3 ЦАП соответственно. На выходе первого ЦАП 12.1 образуются яркостные сигналы, преобразованные в аналоговую форму, а на выходах второго 12.2 и третьего 12.3 ЦАП -аналоговые цветоразностные сигналы.

Рассмотрим работу системы сжатия видеоинформации в целом и ОП 3 более подробно. В первом цикле режима записи происходит запись сигнала изображения в ячейки первого матричного ЗУ 15.1. При этом изображение представляется в виде последовательного набора фрагментов одинаковой размерности(фиг.Эа). Информация, поступающая на информационный вход ОП 3, подается на первый вход первого MX 14,1. Под воздействием сигнала Ui (фиг. 10), снимаемого с четырнадцатого выхода БУ 11 и подающегося на управляющий вход первого MX 14.1, являющийся восьмым синхров- ходом ОП 3, эта информация поступает на вход первого ШФ 16.1. Входы записи-считывания первого ЗУ 15.1 и вход первого элемента задержки 13.1 объединены, и на них подается сигнал U2 (фиг. 106), снимаемый с тринадцатого выхода БУ 11. С выхода первого ЭЗ 13.1 сигнал поступает на управляющий вход первого ШФ 16.1 и под его воздействием информация с входа первого ШФ 16.1 поступает на вход-выход данных первого ЗУ 15.1. На тактовый вход первого ЗУ 15.1 поступают тактовые импульсы 11з (фиг. 10в) с двенадцатого выхода БУ 11, а на первый и второй адресные входы его поступают сигналы с первого и второго адресных выходов первого БФА 5.1. После записи информация в первом ЗУ 15.1 имеет ви/j после- довательных столбцов, содержащих построчно считываемые элементы фрагментов изображения (фиг.96). Каждый из фрагментов представляется в виде вектора и заносится в соответствующий стол бец ЗУ 15.1 каждого ОП 3. Обозначим первые элементы полученных таким образом векторов как Јi, вторые элементы - Ј и т.д. (фиг.9б), до ЈNI , N1 - число элементов фрагмента.

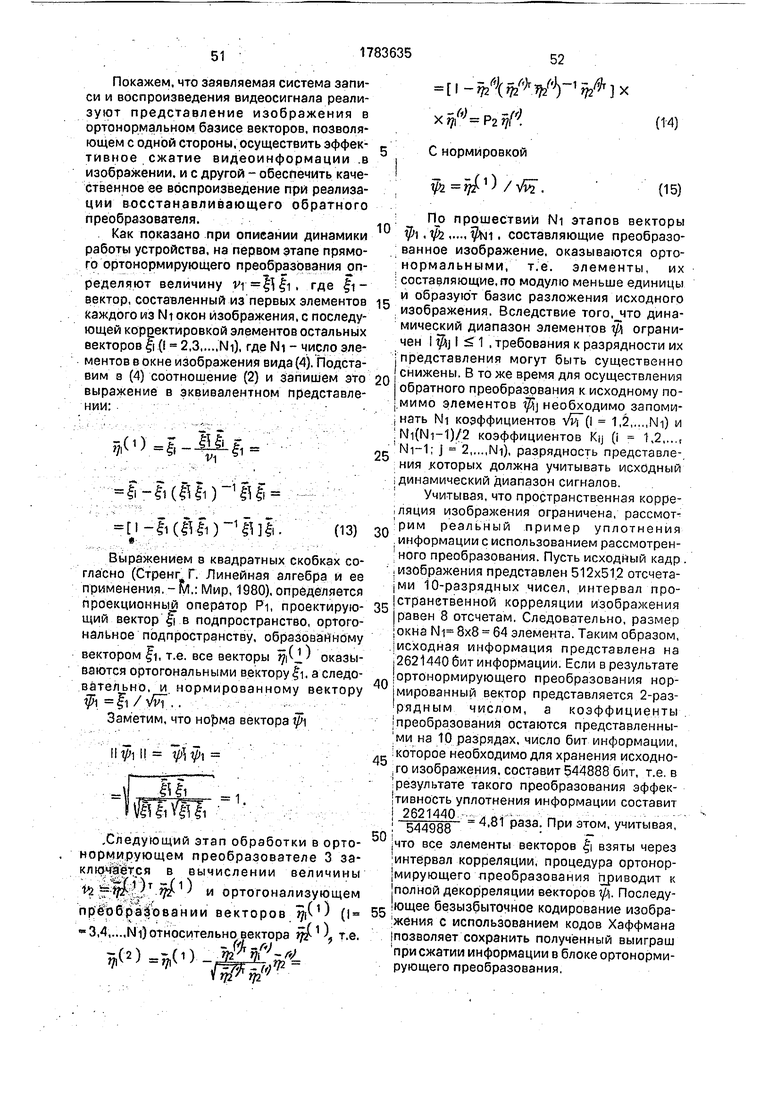

Второй цикл режима записи заключается в осуществлении NI этапов прямого орто- нирующего преобразования векторов §. На первом этапе сначала осуществляется вы3635 34

числение квадрата нормы вектора fi по формуле

vi |i |i.

О)

0

5

0

5

0

5

0

5

0

5

Для этого на соответствующие входы первого ЗУ 15.1 подаются тактовые импульсы и сигналы записи-считывания 1)2 (фиг. 11 б). На интервале времени ti-t2 происходит поэлементное считывание вектора ft из памяти первого ЗУ 15.1. Эта информация через первый ШФ 16.1 передается на вход первого ДМХ 17.1, на управляющий вход которого подается сигнал режим, В режиме записи сигнал с входа первого ДМХ 17.1 передается на его второй выход и поступает на первые входы первого умножителя 19.1, пятого MX 14.5 и вычитателя 23, а также на второй вход четвертого MX 14.4. Под воздействием управляющего сигнала Ua (фиг. 11 в), снимаемого с пятнадцатого выхода БУ 11 и подающегося на управляющий вход четвертого MX 14.4, сигнал с него поступает на второй вход первого умножителя 19.1, где происходит поэлементное умножение вектора Јi на fi . Одновременно элементы вектора fi ЈnЈi2 ,Ј13Јiw с

выхода пятого MX 14.5, на управляющий вход которого подается инверсный сигнал Уз, поступают на вход РОС 20 и под воздействием сигнала сдвига U/j (фиг. 11 г) записываются в него. В момент времени ti первый PC 22.1 обнулен. Произведение ЈпЈп с выхода первого умножителя 19.1 поступает на первый вход первого сумматора 21.1, с выхода которого оно поступает в первый PC 22.1 и под воздействием сигнала записи Us записывается в него. В дальнейшем при осуществлении поэлементного умножения

ЈijЈij 0 1-2N) произведение ЈijЈij в

первом сумматоре 21.1 складывается с

предыдущими 0 1.21-1), находящимися

в первом PC 22.1, где таким образом к моменту времени t2 накапливается скалярное произведение

.

В момент времени t2 по сигналу U (фиг.11ж) это произведение записывается в РД 24 и задержкой на т.з по сигналу Us (фиг.11з) заносится в регистр 27 через устройство извлечения корня 26, где определяется величина vЈT, третий MX 14.7 и третий ШФ 16.3.

Затем определяются коэффициенты ор- тононализирую щего преобразования

Kn jftS/Vi.

(2)

Рассмотрим процессы, происходящие в схеме ОП 3 на интервале времени t2-ta (фиг.11). Первый умножитель 19.1 осуществляет поэлементное умножение векторов

1J2|NI .учитываемых из первого ЗУ 15.1,

на вектор |i, элементы которого находятся в РОС 20. По мере вычисления каждого из

произведения Ј2fi INI, они накапливаются в первом сумматоре 21.1 и первом PC 22.1 ив соответствующие моменты времени происходит деление Јi|i назначение . находящееся в РД 24, а также обнуление первого PC 22.1 для накопления следующего произведения Ј1 ft-n (фиг.11е). С выхода первого делителя 25.1 значения Кц поступают на первый вход второго MX 14,6 и через второй ШФ 16.2 записываются во второе ЗУ 15.2. На тактовый вход его подается сигнал Uю. на вход записи-считывания сигнал Ug (фиг.11к,и).

Затем находится нормированный вектор

т/л fi / vvT.

(3)

Для этого сигнал с выхода РОС 20 подается на второй вход второго делителя 25.2, на первый вход которого подается сигнал с выхода устройства извлечения корня 26, С выходу второго делителя 25.2 значения вектора ty поступают на первый вход шестого MX 14.3, на управляющий вход которого подается сигнал DH (фиг.11л), снимаемый с двадцать первого выхода БУ 11. Далее по цепи второй MX 14.2, первый MX 14.1 эта информация через первый ШФ 16,1 записывается в первое ЗУ 15.1.

В заключение производится корректировка значений векторов г, |зЈш по

формуле

(о f,-Kitii.

И

ванных векторов rj ЗУ 15.1.

й(0

где 2,3.....М1.

Сигнал с выхода РОС 20 поступает на второй вход второго умножителя 19.2, на первый вход которого поступает сигнал с выхода первого делителя 25.1. С выхода второго умножителя образующиеся там произ- ведения поступают на второй вход вычитателя 23, на первый вход которого поступают значения Ј|. Значения скорректирозаносятся в первое

0

На втором этапе находится норма

Vis вектора vjk1 , затем рассчитываются коэффициенты Ki2, находится нормированный вектор $2 и производится корректировка значений векторов

, J7N11 по формулам

),

)/,, (1 ),

15

(2)(0-К|2 0

(5)

0

где 1 3,4NI,

и т.д.

Осуществление этого и последующих этапов аналогично пр оизведению рассмотренного выше первого этапа.

На NI-.J-M этапе производите расчет

I .)

| нормы VVN 1 - 1 вектора г1м-- .

определяется коэффициент KNI.NI-ч .

нормированный вектор $N1 - 1 и произ- |водится корректировка значений векторов ум по формулам

(М-4 т (//-;)

VNI -1 }w -i J/N1 -1 , „-&+ т -w-л).

KN1.N1-1 J/N1- 1 rjW /VN1-1 ,

ftff-Л)

N1-1 N1-1 / VVN1 -1 ,

-ftffij -01-4-M-4

ум ;NI KNI.NI- ;NI - 1 (6)

Последний Nt-й этап заключатся в про- 40 стом нормировании вектора ум к норме i по формулам

/M-I)I )

VM1 7N1 ,

т -flrtt}. ,-

N1 N1 / VVN1 .

(7)

В результате проведения всех NI этапов в ячейках первого ЗУ 15.1 содержатся орто- нормированные значения векторов $, во

.втором ЗУ 15.2 - значения коэффициентов Kij, значения норм v находятся в РГ 27.

В третьем цикле режима записи на вход сдвига РГ 27 поступает сигнал Ui (фиг.12а). а тактовый вход второго ЗУ 15.2 подается