Устройство предназначено для применения в качестве элемента в системах стабилизации, наведения и навигации. Изобретение может найти применение в приборах измерения механических величин компенсационного типа.

Известно устройство для измерения ускорений (патент РФ №2098833, МПК6 G 01 P 15/13, опубл. 10.12.97), содержащее чувствительный элемент, включающий в себя два неподвижных электрода и подвижную пластину, три усилителя, два резистора, при этом выход первого усилителя подключен к первому резистору, а вход второго усилителя соединен со вторым резистором и является выходом устройства. Для повышения помехоустойчивости при воздействии электрических помех в него введен источник опорного напряжения, генератор электрического сигнала, две транзисторные пары, три резистора, два конденсатора, позволяющих за счет охвата усилителей отрицательной обратной связью, осуществить компенсацию электрических помех.

Недостатком данного устройства является низкая точность измерения, так как выбор коэффициента усиления в жесткой отрицательной обратной связи ограничен условием устойчивости системы.

Наиболее близким по техническому решению является устройство (RU 2189046 С1, МПК7 G 01 P 15/13, опубл. 10.09.2002, Бюл. N 25), содержащее чувствительный элемент, датчик угла, усилитель и датчик моментов, включенный в обратную связь, два параллельных канала, один аналоговый, с выхода усилителя на один из входов датчика моментов через последовательно включенные первый логический элемент, схему исключающее "ИЛИ", первый прецизионный релейный элемент, сглаживающий фильтр, суммирующий элемент, сопряженный фильтр верхних частот, первый преобразователь напряжение - ток, другой, цифровой, с выхода усилителя на другой вход датчика моментов через последовательно включенные первый логический элемент, схему исключающее "ИЛИ", первый прецизионный релейный элемент, сглаживающий фильтр, суммирующий элемент, сопряженный фильтр нижних частот, релейный элемент, ждущие синхронные генераторы, RS-триггер, прецизионный релейный элемент, преобразователь напряжение - ток, итоговый регистр, схемы совпадения, реверсивный двоичный счетчик.

Существенным недостатком подобного устройства является невысокая точность измерения, вызванная дискретным характером выдачи информации о действующем ускорении в виде цифрового кода с итогового регистра.

Задачей предложенного технического решения является повышение точности измерения ускорения.

Поставленная цель достигается тем, что в устройство, содержащее чувствительный элемент, датчик угла, усилитель и датчик моментов, включенное в отрицательную обратную связь, введены два канала в цепь отрицательной обратной связи, один аналоговый канал введен с выхода усилителя на один из входов датчика моментов через последовательно соединенные первый логический элемент, первую схему исключающее "ИЛИ", другой вход который соединен с генератором опорного напряжения через второй логический элемент, первый прецизионный релейный элемент, сглаживающий фильтр, сопряженный фильтр верхних частот, первый преобразователь напряжение - ток, первый суммирующий элемент. Другой канал, цифровой, введен с выхода усилителя на другой вход датчика моментов через последовательно соединенные первый логический элемент, первую схему исключающее "ИЛИ", первый прецизионный релейный элемент, сглаживающий фильтр, сопряженный фильтр нижних частот, второй суммирующий элемент, второй релейный элемент, два выхода которого соединены с входами двух ждущих синхронных генераторов, триггер знака отклонения, первую пару схем исключающее "ИЛИ", первую пару схем логического умножения "И", первый реверсивный двоичный счетчик, один из выходов которого соединен с итоговым регистром, другой выход первого реверсивного двоичного счетчика через первый элемент задержки и схему собирания соединен с входом R “сброс нуля” первого реверсивного двоичного счетчика и выход первого реверсивного двоичного счетчика через вторую пару схем логического умножения "И" и триггер соединен с входами первой пары схем исключающее "ИЛИ", другой выход триггера соединен с другим входом итогового регистра, выход триггера знака отклонения соединен с входами второй пары схем логического умножения "И", выход итогового регистра соединен последовательно по информационным входам: с первым двоичным умножителем, пятой парой схем логического умножения "И", первой парой схем собирания, вторым реверсивным двоичным счетчиком, счетчиком текущей информации, триггером обратной связи, второй схемой исключающее "ИЛИ", вторым прецизионным релейным элементом, вторым преобразователем напряжение - ток, выход которого соединен с одним из входов датчика моментов, причем один из выходов второго реверсивного двоичного счетчика соединен с входом “R” второго реверсивного двоичного счетчика через второй элемент задержки, другой выход второго реверсивного двоичного счетчика соединен со вторыми входами первой пары схемы собирания, через третью пару схем логического умножения "И", триггер знака второго реверсивного двоичного счетчика, четвертую пару схем логического умножения "И", вторые входы третьей пары схем логического умножения "И" соединены с выходом итогового регистра, вторые входы пятой пары схем логического умножения "И" соединены с выходами второй пары схем исключающее "ИЛИ", входы которой соединены с выходами итогового регистра и триггера знака второго реверсивного двоичного счетчика, другие входы четвертой пары схем логического умножения "И" соединены с выходом второго двоичного умножителя, вход которого соединен с выходом второго реверсивного двоичного счетчика, вход второй схемы исключающее "ИЛИ" соединен с выходом триггера знака второго реверсивного двоичного счетчика, выход счетчика интервала преобразования соединен с входом счетчика текущей информации и триггером обратной связи, входы второго суммирующего элемента, ждущих синхронных генераторов, первой пары схем логического умножения "И", итогового регистра, первого и второго двоичного умножителя, счетчика текущей информации и счетчика интервала преобразования, схемы собирания соединены с устройством распределения синхроимпульсов, вход которого соединен с генератором пилообразного напряжения, а выход генератора несущей частоты соединен с входом датчика угла, выход которого соединен с усилителем, причем выход со второго реверсивного двоичного счетчика является выходом устройства с непрерывным цифровым кодом, пропорциональным действующему ускорению.

Введение двух каналов в отрицательную обратную связь - аналогового для стабилизации переходного процесса и цифрового канала съема цифрового кода с непрерывной цифровой фильтрацией выходной информации позволило создать устройство с выдачей текущей информации не в дискретные промежутки времени (как для прототипа), а непрерывно, тем самым повысив точность.

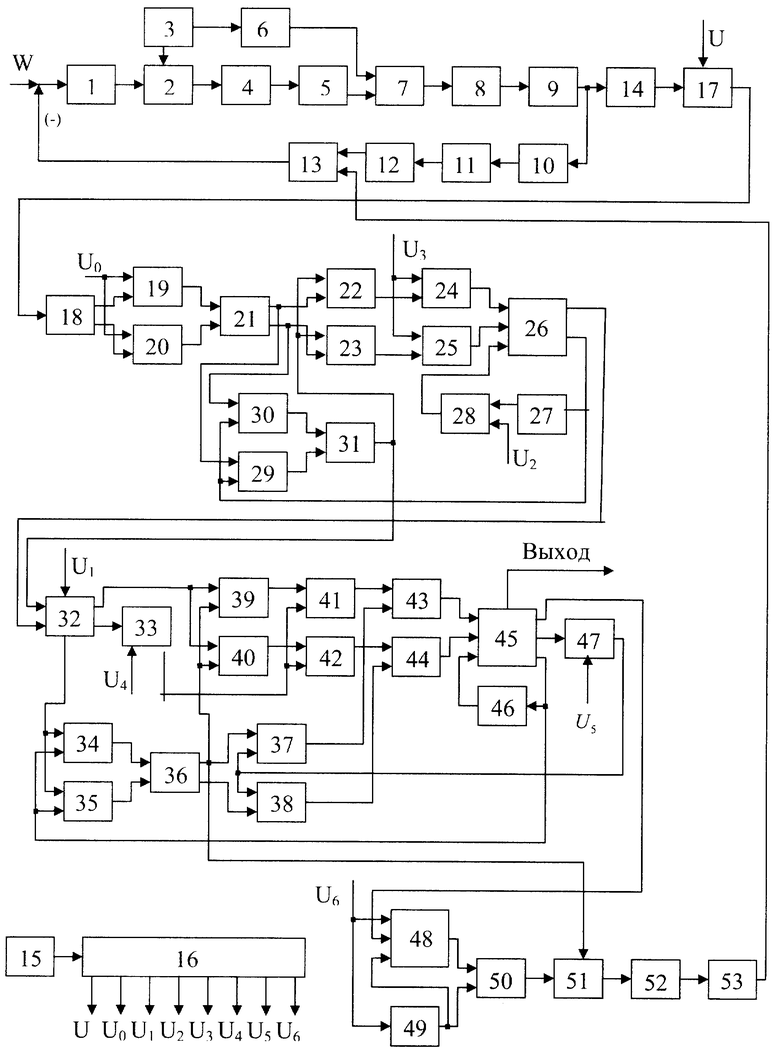

На чертеже изображена функциональная схема предлагаемого устройства.

Устройство для измерения ускорений содержит чувствительный элемент 1, угловое положение которого фиксирует датчик угла 2. Обмотка возбуждения датчика угла 2 соединена с выходом генератора опорного напряжения 3. Выходная обмотка датчика угла 2 соединена с усилителем переменного тока со стабильным коэффициентом передачи 4, выход которого соединен с входом первого логического элемента 5. Вход второго логического элемента 6 соединен с выходом генератора опорного напряжения 3, а выход 6 соединен с одним из входов первой схемы исключающее "ИЛИ" 7, другой вход схемы исключающее "ИЛИ" 7 соединен с выходом первого логического элемента 5. Вход первого прецизионного релейного элемента 8 соединен с выходом схемы исключающее "ИЛИ" 7, а выход первого прецизионного релейного элемента 8 соединен с входом сглаживающего фильтра 9. Один из выходов сглаживающего фильтра 9 соединен с входом сопряженного фильтра верхних частот 10, выход которого через первый преобразователь напряжение - ток 11 соединен с входом первого суммирующего элемента 12. Выход первого суммирующего элемента 12 соединен с одним из входов (токовой обмоткой) датчика моментов 13. Другой выход сглаживающего фильтра 9 соединен с входом сопряженного фильтра нижних частот 14. Генератор пилообразного напряжения 15 через устройство распределения синхроимпульсов 16 соединен с одним из входов второго суммирующего элемента 17(U), второй вход которого соединен с выходом сопряженного фильтра нижних частот 14, а выход второго суммирующего элемента 17 соединен с входом релейного элемента 18. Выходы релейного элемента 18 соединены с входами ждущих синхронных генераторов 19 и 20, другие входы 19 и 20 соединены с выходами устройства распределения синхроимпульсов 16(U0). Ждущие синхронные генераторы 19 и 20 соединены с входами триггера знака отклонения 21, выходы которого соединены с входами первой пары схем исключающее "ИЛИ" 22 и 23. Выходы схем 22 и 23 соединены с входами первой пары схем логического умножения "И" 24, 25. Выходы 24 и 25 соединены с суммирующим и вычитающим входами первого реверсивного двоичного счетчика 26, один из выходов которого через первый элемент задержки 27 и схему собирания 28 соединен с входом R - “сброс нуля” первого реверсивного двоичного счетчика 26. Выход первого реверсивного двоичного счетчика 26 соединен с входами второй пары схем логического умножения "И" 29 и 30, выходы которых через триггер 31 соединены с одним из входов итогового регистра 32 и с входами первой пары схем исключающее "ИЛИ" 22 и 23. Выход триггера знака отклонения 21 соединен с входами второй пары схем логического схем умножения "И" 29 и 30. Другие входы первой пары схем логического умножения "И" 24, 25 и схемы собирания 28 соединены с выходами устройства распределения синхроимпульсов 16 (U3, U2). Выход первого двоичного реверсивного счетчика 26 соединен с входом итогового регистра 32, другой вход 32 соединен с устройством распределения синхроимпульсов 16(U1). Выход итогового регистра 32 соединен с входом первого двоичного умножителя 33 и с входами третьей пары схем логического умножения схем "И" 34 и 35, выходы которых соединены с входами R и S триггера знака второго реверсивного счетчика 36. Выход 36 соединен с входами четвертой пары схем логического умножения "И" 37 и 38. Выход триггера знака второго реверсивного счетчика 36 соединен также с одними из входов второй пары схем исключающее "ИЛИ" 39 и 40. Входы 39 и 40 соединены также с одним из выходов итогового регистра 32. Входы пятой пары схем логического умножения "И" 41 и 42 соединены с выходами второй пары схем исключающее "ИЛИ" 39 и 40 и с выходом первого двоичного умножителя 33, один из входов первого двоичного умножителя 33 соединен с устройством распределения синхроимпульсов 16(U4). Выходы триггера знака второго реверсивного счетчика 36 через схемы четвертой пары схем логического умножения "И" 37 и 38 соединены с одними из входов первой пары схем собирания 43 и 44, другие входы 43 и 44 соединены с выходами пятой пары схем "И" 41 и 42. Выходы первой пары схем собирания 43 и 44 соединены с суммирующим и вычитающим входами второго реверсивного двоичного счетчика 45, один из выходов которого через второй элемент задержки 46 соединен с входом “сброс нуля” второго реверсивного двоичного счетчика 45. Один из выходов 45 соединен с входами четвертой пары схем "И" 34 и 35.

Выход второго реверсивного двоичного счетчика 45 соединен с входами второго элемента задержки 46, второго двоичного умножителя 47, так и с входом счетчика текущей информации 48. Выход второго элемента задержки 46 соединен с одним из входов второго реверсивного двоичного счетчика 45, а выход второго двоичного умножителя 47 соединен с входами четвертой пары схем "И" 37 и 38. Выход устройства распределения синхроимпульсов 16 соединен с входами 47(U5), 48(U6) и счетчиком интервала преобразования 49(U6). Выход счетчика интервала преобразования 49 соединен с S входом триггера обратной связи 50 и с входом 48. Вход триггера 50 “R” соединен с выходом счетчика текущей информации 48. Выходы 50 и 36 соединены с входом второй схемы исключающее "ИЛИ" 51, выход которой соединен с входом второго прецизионного релейного элемента 52. Датчик моментов 13 соединен с выходом прецизионного релейного элемента 52 через второй преобразователь напряжение - ток 53.

Внутреннее содержание блоков, реализующих устройство для измерения ускорения, описаны в книгах: Майоров С.А., Новиков Г.И. Принцип организации цифровых машин. Л.: Машиностроение, 1974, 432 с.; Хоровиц П., Хилл У. Искусство схемотехники. М.: Мир, т.1-3, 1993.

Работа предлагаемого устройства осуществляется следующим образом. Отклонение чувствительного элемента 1, вызванное действием ускорения (W), фиксируется датчиком угла 2, обмотка возбуждения которого соединена с генератором опорного напряжения 3. Выходной сигнал с датчика угла 2 усиливается усилителем переменного тока со стабильным коэффициентом передачи 4. С выхода первого логического элемента 5 сигнал с усилителя 4 представляется в виде сигнала прямоугольной формы с частотой генератора опорного напряжения 3. Для выделения фазы отклонения чувствительного элемента 1 в схеме предусмотрен второй логический элемент 6, на вход которого подается сигнал с генератора опорного напряжения 3. На выходе второго логического элемента 6 будет сигнал, аналогичный по форме сигналу с первого логического элемента 5. Выходные сигналы с 5 и 6, сдвинутые по фазе, поступают на соответствующие входы первой схемы исключающее "ИЛИ" 7 (схема сложения по модулю “2”), осуществляющей операцию логического сложения. Если сигналы с логических элементов 5 и 6 имеют нулевой фазовый сдвиг, то на выходе схемы 7 имеем логический “0”, если же сигналы с 5 и 6 имеют фазовый сдвиг, отличный от нуля, то на выходе 7 имеем логическую единицу “1”. По форме сигнал с выхода схемы 7 имеет аналогичную форму сигналов с выходов 5 и 6. Сигнал с выхода 7 поступает на вход первого прецизионного релейного элемента 8, переключение которого происходит на несущей частоте генератора 3, и осуществляется фиксация сигнала с выхода 7. Сглаживающий фильтр 9 выделяет уровень сигнала с выхода 8 в соответствии с фазой отклонения чувствительного элемента 1. Сопряженный фильтр верхних частот 10, включенный в аналоговый канал для формирования заданного переходного процесса, соединен с сглаживающим фильтром 9. Так как входом для датчика моментов 13 является ток, то с выхода сопряженного фильтра верхних частот 10 на вход 13 включены последовательно первый преобразователь напряжение - ток 11 и первый суммирующий элемент 12. Элементы 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13 образуют аналоговый канал в цепи отрицательной обратной связи, осуществляющей стабилизацию переходного процесса в устройстве для измерения ускорений. Сглаженный сигнал в виде уровня с выхода 9 поступает на вход сопряженного фильтра нижних частот 14. На вход второго суммирующего элемента 17 поступают сигналы с выхода сопряженного фильтра нижних частот 14 и с генератора пилообразного напряжения 15 через устройство распределения синхроимпульсов 16 (U). На выходе второго суммирующего элемента 17 имеем сигнал в виде пилообразного напряжения, смещенного по уровню в зависимости от фазы отклонения чувствительного элемента 1. Второй прецизионный релейный элемент 18, включенный на выход 17, срабатывает по знаку сигнала с выхода второго суммирующего элемента 17 и сигнал в виде ШИМ (широтно-импульсная модуляция) поступает на входы ждущих синхронных генераторов 19 и 20, которые взводятся от прецизионного релейного элемента 18 и вырабатывают короткие, длительностью, определяемой частотой привязки U0 схемы распределения синхроимпульсов 16, импульсы, частота которых определяется частотой переключения 18. В зависимости от фазы отклонения чувствительного элемента 1 на RS-триггер (триггер знака отклонения) 21 подается импульс с ждущего синхронного генератора 19 либо с ждущего синхронного генератора 20. Если фаза отклонения чувствительного элемента 1 - “0”, то на одном из выходов триггера знака 21 имеем логический “0”, а на инверсном выходе триггера знака 21 логическую “1”. Сигналы с выхода 21 поступают как на входы первой пары схем логического "ИЛИ" 22 и 23, так и на входы второй пары схем логического умножения "И" 29 и 30. Если информация на выходе первого реверсивного двоичного счетчика 26 (равная разности числа “положительных” и “отрицательных” импульсов) отрицательна, то с одного из выходов 26 импульсы поступают на соответствующие входы второй пары схем "И" 29 и 30 и на вход “R” счетчика 26 через первый элемент задержки 27 и первую схему собирания 28. При этом на входе “R” счетчика 26 будет происходить “сброс нуля” по сигналу (U2) со схемы синхронизации 16, поданному на один из входов первой схемы собирания 28. На выходах второй пары схем логического умножения 29 и 30 при логическом перемножении сигналов с 21 и 26, имеем при нулевой фазе отклонения чувствительного элемента 1 логическую “1” со схемы 30 и логический “0” со схемы 29. Выходные сигналы со схем 30 и 29 поступают соответственно на S и R входы триггера 31, выходной сигнал (знак разряда) которого поступает на входы первой пары схем исключающее "ИЛИ" 22 и 23, а также на вход итогового регистра 32. В результате логического сложения по модулю “2” схемами исключающее "ИЛИ" 22 и 23 сигналов со схем 21 и 31 на выходе будем иметь в зависимости от фазы отклонения чувствительного элемента 1 логический “0” либо логическую “1”. Выходные сигналы с 22 и 23 подаются на входы первой пары схем "И" 24 и 25, на другие входы 24 и 25 подаются импульсы U3 (импульсы счета) от устройства распределения синхроимпульсов 16. В зависимости от состояния схем 22 и 23 эти импульсы будут подаваться либо на суммирующий, либо на вычитающий входы первого реверсивного двоичного счетчика 26. По окончании периода колебаний чувствительного элемента 1 информация из счетчика 26 (равная разности “положительных” и “отрицательных” импульсов) по сигналу импульса записи U1 со схемы синхронизации 16 переписывается в итоговый регистр 32 в соответствии со знаком разряда с триггера 31. Цифровой код с итогового регистра 32 поступает на вход первого двоичного умножителя 33 с тактовой частотой U1 со схемы синхронизации 16. На другой вход первого двоичного умножителя 33 поступают импульсы счета U4 со схемы 16. Импульс “0”, характеризующий знаковый разряд цифрового кода, с выхода 32 и импульс “1”, характеризующий инверсное значение знакового разряда цифрового кода, с выхода 32 подаются на выходы третьей пары схем "И" 34 и 35, на другие входы которой подаются импульсы с выхода второго реверсивного счетчика 45, и схемы 34 и 35 осуществляют операцию логического умножения над сигналами с выходов 45 и 32. На входы R или S триггера знака второго реверсивного двоичного счетчика 36 подаются импульсы либо с 34, либо с 35 в зависимости от фазы отклонения чувствительного элемента 1. С прямого выхода триггера знака 36 сигнал подается на схемы второй пары исключающее "ИЛИ" 39 и 40 и на один из входов третьей пары схемы логического умножения 37. Инверсный выход 36 соединен с входом третьей пары схемы логического умножения 38. На другие входы второй пары схемы исключающее "ИЛИ" 39 и 40 подаются сигналы, характеризующие знак разряда (“0” либо “1”) цифрового кода, с итогового регистра 32. Код знака с 32 подается на вход 39 и инверсный код на вход 40. В зависимости от состояния триггера знака 36 импульсы подаются на вход схем умножения 41 либо 42, на другие выходы схем 41 и 42 подаются импульсы с выхода первого двоичного умножителя 33. Импульс с 41 либо с 42 в зависимости от состояния первого двоичного умножителя 33 подается на входы пары схем собирания 43 либо 44. На другие входы пары схем собирания 43 и 44 подаются импульсы со схем 37 и 38, управление которыми осуществляется триггером 36 и вторым реверсивным двоичным умножителем 47. В зависимости от состояния схем собирания 43 и 44 импульсы будут подаваться либо на суммирующий, либо на вычитающий вход второго реверсивного счетчика 45, один из выходов которого через второй элемент задержки 46 подается на вход “сброс нуля” счетчика 45. Цифровой код с выхода второго реверсивного двоичного 45 поступает на входы второго двоичного реверсивного умножителя 47 (на другой вход 47 поступает импульс U5 счета цепи обратной связи) и на вход счетчика текущей информации 48. Элементы 45 и 46 реализуют цифровой фильтр с передаточной функцией W(S)=1/(TцS+1). На другие входы счетчика текущей информации 48 поступают сигналы с выхода счетчика интервала преобразования 49 и с устройства распределения синхроимпульсов 16 (U6). На вход счетчика 49 поступает также импульс счета счетчика преобразования интервала в ШИМ с устройства 16 (U6). Текущая информация с 48 и 49 поступает либо на вход R, либо на вход S триггера обратной связи 50, и в зависимости от его состояния (“0” либо “1”) импульсы подаются на один из входов второй схемы исключающее "ИЛИ" 51, которая осуществляет операцию логического сложения по модулю “2” сигналов с выхода триггера знака 36 и триггера обратной связи 50. Если сигналы с выходов триггера знака 36 и триггера обратной связи 50 в фазе, то на выходе второй схемы исключающее "ИЛИ" 51 имеем логический “0”, в противном случае “1”. Второй прецизионный релейный элемент 52, включенный на выход 51, переключается на частоте U6 с устройства 16, и сигнал в виде ШИМ поступает на вход второго преобразователя напряжение - ток 53. Непрерывная цифровая информация, пропорциональная действующему ускорению, снимается со второго реверсивного двоичного счетчика 45 (выход устройства). Сигнал с выхода первого суммирующего элемента 12 и выхода 53 поступает на вход датчика моментов 13, который возвращает чувствительный элемент 1 в исходное положение.

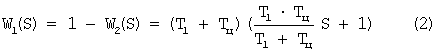

Передаточная функция сопряженного фильтра верхних частей W1(S) 10, осуществляющая стабилизацию переходного процесса, выбирается из условия, что

где W2(S) - произведение передаточных функций сопряженного фильтра нижних частот 14  и цифрового фильтра с передаточной функцией

и цифрового фильтра с передаточной функцией

После подстановки передаточных функций получим:

Введение в устройство двух каналов в цепи отрицательной обратной связи один, аналоговый с W1(S) для стабилизации переходного процесса, другой, цифровой с непрерывной фильтрацией, позволяет создать устройство повышенной точности, т.к. в предлагаемом устройстве осуществляется одновременно аналоговая фильтрация и цифровая.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2004 |

|

RU2255341C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2001 |

|

RU2190226C1 |

| КОМПЕНСАЦИОННЫЙ АКСЕЛЕРОМЕТР | 2010 |

|

RU2447451C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2004 |

|

RU2276372C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2003 |

|

RU2231075C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2002 |

|

RU2227920C1 |

| Акселерометр | 2017 |

|

RU2653140C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2005 |

|

RU2279093C1 |

| АКСЕЛЕРОМЕТР | 2011 |

|

RU2481588C1 |

| КОМПЕНСАЦИОННЫЙ АКСЕЛЕРОМЕТР | 2011 |

|

RU2478212C1 |

Изобретение предназначено для применения в качестве чувствительного элемента в системах стабилизации, наведения и навигации и может найти применение в приборах измерения механических величин компенсационного типа. Сущность изобретения заключается в том, что в устройство введены два канала в цепи отрицательной обратной связи, один аналоговый канал с выхода усилителя на один из входов датчика моментов через последовательно соединенные первый логический элемент, первую схему исключающее "ИЛИ", другой вход которой соединен с генератором опорного напряжения через второй логический элемент, первый прецизионный релейный элемент, сглаживающий фильтр, сопряженный фильтр верхних частот, первый преобразователь напряжение - ток, первый суммирующий элемент. Другой канал, цифровой, введен с выхода усилителя на другой вход датчика моментов через последовательно соединенные первый логический элемент, первую схему исключающее "ИЛИ", первый прецизионный релейный элемент, сглаживающий фильтр, сопряженный фильтр нижних частот, второй суммирующий элемент, второй релейный элемент, два выхода которого соединены с входами двух ждущих синхронных генераторов, триггер знака отклонения, первую пару схем исключающее "ИЛИ", первую пару схем логического умножения "И", первый реверсивный двоичный счетчик, один выход которого соединен с итоговым регистром. Введение двух каналов в отрицательную обратную связь - аналогового для стабилизации переходного процесса и цифрового канала съема цифрового кода с непрерывной цифровой фильтрацией выходной информации позволило создать устройство с выдачей текущей информации не в дискретные промежутки времени, а непрерывно, т.е. повысить точность измерения. 1 ил.

Устройство для измерения ускорений, содержащее чувствительный элемент, датчик угла, усилитель и датчик моментов, включенный в отрицательную обратную связь, отличающееся тем, что в цепь отрицательной обратной связи введены два канала, один аналоговый канал введен с выхода усилителя на один из входов датчика моментов через последовательно соединенные первый логический элемент, первую схему исключающее ИЛИ, другой вход которой соединен с генератором опорного напряжения через второй логический элемент, первый прецизионный релейный элемент, сглаживающий фильтр, сопряженный фильтр верхних частот, первый преобразователь напряжение - ток, первый суммирующий элемент, другой канал, цифровой, введен с выхода усилителя на другой вход датчика моментов через последовательно соединенные первый логический элемент, первую схему исключающее ИЛИ, первый прецизионный релейный элемент, сглаживающий фильтр, сопряженный фильтр нижних частот, второй суммирующий элемент, второй релейный элемент, два выхода которого соединены с входами двух ждущих синхронных генераторов, триггер знака отклонения, первую пару схем исключающее ИЛИ, первую пару схем логического умножения И, первый реверсивный двоичный счетчик, один из выходов которого соединен с итоговым регистром, другой выход первого реверсивного двоичного счетчика через первый элемент задержки и схему собирания соединен с входом R "сброс нуля" первого реверсивного двоичного счетчика и выход первого реверсивного двоичного счетчика через вторую пару схем логического умножения И и триггер соединен с входами первой пары схем исключающее ИЛИ, другой выход триггера соединен с другим входом итогового регистра, выход триггера знака отклонения соединен с входами второй пары схем логического умножения И, выход итогового регистра соединен последовательно по информационным входам: с первым двоичным умножителем, пятой парой схем логического умножения И, первой парой схем собирания, вторым реверсивным двоичным счетчиком, счетчиком текущей информации, триггером обратной связи, второй схемой исключающее ИЛИ, вторым прецизионным релейным элементом, вторым преобразователем напряжение - ток, выход которого соединен с одним из входов датчика моментов, причем один из выходов второго реверсивного двоичного счетчика соединен с входом R второго реверсивного двоичного счетчика через второй элемент задержки, другой выход второго реверсивного двоичного счетчика соединен со вторыми входами первой пары схемы собирания, через третью пару схем логического умножения "И", триггер знака второго реверсивного двоичного счетчика, четвертую пару схем логического умножения "И", вторые входы третьей пары схем логического умножения И соединены с выходом итогового регистра, вторые входы пятой пары схем логического умножения И соединены с выходами второй пары схем исключающее ИЛИ, входы которой соединены с выходами итогового регистра и триггера знака второго реверсивного двоичного счетчика, другие входы четвертой пары схем логического умножения И соединены с выходом второго двоичного умножителя, вход которого соединен с выходом второго реверсивного двоичного счетчика, вход второй схемы исключающее ИЛИ соединен с выходом триггера знака второго реверсивного двоичного счетчика, выход счетчика интервала преобразования соединен с входом счетчика текущей информации и триггером обратной связи, входы второго суммирующего элемента, ждущих синхронных генераторов, первой пары схем логического умножения И, итогового регистра, первого и второго двоичного умножителя, счетчика текущей информации и счетчика интервала преобразования, схемы собирания соединены с устройством распределения синхроимпульсов, вход которого соединен с генератором пилообразного напряжения, а выход генератора несущей частоты соединен с входом датчика угла, выход которого соединен с усилителем, и выход со второго реверсивного двоичного счетчика является выходом устройства с непрерывным цифровым кодом, пропорциональным действующему ускорению.

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2001 |

|

RU2189046C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 1999 |

|

RU2163380C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ УСКОРЕНИЙ | 2001 |

|

RU2190226C1 |

| КОМПЕНСАЦИОННЫЙ АКСЕЛЕРОМЕТР | 1996 |

|

RU2098833C1 |

| US 4336718 A, 29.06.1982 | |||

| US 4932261 А, 12.06.1990. | |||

Авторы

Даты

2005-06-27—Публикация

2004-03-02—Подача