Изобретение относится к технике электрической связи, в частности к системам передачи информации по двухпроводным линиям связи и может также быть использовано в вычислительной технике в каналах обмена информации ЭВМ с абонентами.

Известно устройство для приема и передачи информации (см. описание к авторскому св-ву СССР №1510095, опубл. 23.09.89 г., МПК Н 03 М 7/00, Н 03 В 3/00), содержащее блок пороговых детекторов, инжекторы токов, усилители. Сложность конструктивного выполнения данного устройства не позволяет реализовать его в виде микросборки.

Известен приемопередатчик, предназначенный для мультиплексного канала обмена информацией и реализованный в виде микросборки ВА996 ПИЖМ.431287.004. Известный приемопередатчик выполняется в виде микросборки с использованием бескорпусных радиоэлементов. Однако вариант реализации этого приемопередатчика на основе активных элементов, таких как операционный усилитель, частотный фильтр и интегральные компараторы, оказывается сложным в изготовлении и недостаточно надежным в работе.

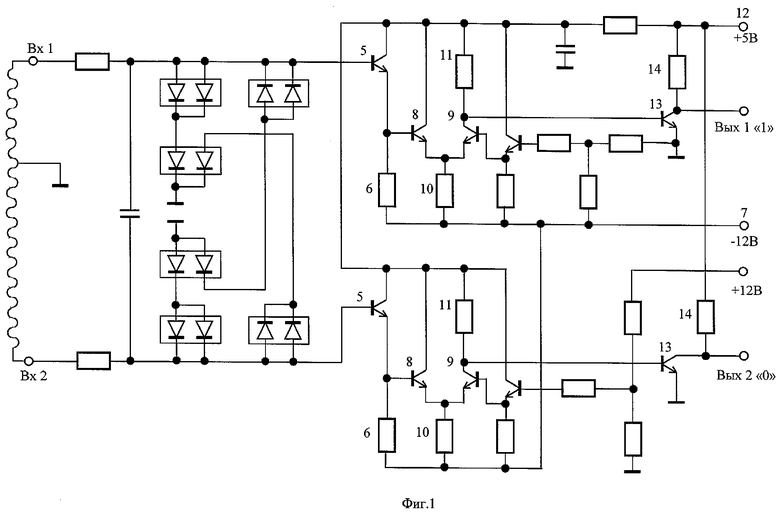

Наиболее близким из известных аналогов (прототипом) (см. фиг.1) является устройство для приема информации с линии связи, содержащее частотный фильтр с двумя входами и с двумя выходами, соединенными с соответствующими входами ограничителя амплитуды напряжения входного сигнала, два выхода которого соединены с первыми входами двух компараторов, построенных по схеме дифференциального каскада на двух транзисторах с эмиттерными повторителями, расположенными на первых и вторых входах дифференциальных каскадов обоих компараторов, резистивным делителем и выходным каскадом, выполненным на одном транзисторе, расположенными на выходе каждого компаратора (см. микросборку ВА 998А ПИЖМ.431287.005).

Известное устройство достаточно сложно в исполнении и обладает низкой точностью срабатывания из-за малого коэффициента усиления дифференциальных каскадов компараторов и зависимости пороговых напряжений на вторых входах компараторов от разбаланса положительного и отрицательного источников питания.

Целью изобретения является упрощение конструкции устройства, повышение точности и надежности его работы.

Кроме того, предлагаемое устройство для приема кодированной информации в линии связи расширяет арсенал известных технических средств того же назначения.

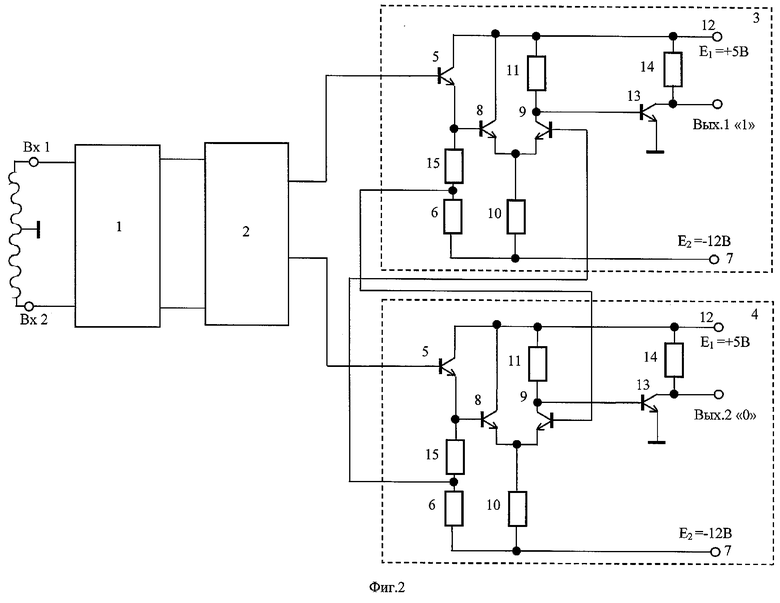

Поставленная цель достигается тем, что в устройство приема кодированной информации в линии связи, содержащее частотный фильтр с двумя входами, являющимися входами устройства, причем два выхода фильтра соединены с соответствующими входами ограничителя амплитуды напряжения, два выхода которого соединены соответственно с первыми входами двух компараторов, выходы которых являются выходами устройства, при этом каждый компаратор содержит первый транзистор, база которого является входом компаратора, первый резистор, одним выводом соединенный с отрицательным полюсом первого источника питания, дифференциальный каскад, выполненный на втором и третьем транзисторах, втором и третьем резисторах, причем база второго транзистора соединена с эмиттером первого транзистора, а общая точка соединения эмиттеров обоих транзисторов каскада соединена с одним из выводов второго резистора, другой вывод которого подсоединен к отрицательному полюсу первого источника питания, а третий резистор включен между коллектором третьего транзистора и положительным полюсом второго источника питания, выходной каскад на четвертом транзисторе, база которого соединена с коллектором третьего транзистора, эмиттер заземлен, а коллектор соединен с одним из выводов четвертого резистора, при этом второй вывод четвертого транзистора, коллекторы первого и второго транзисторов подсоединены к положительному полюсу второго источника питания, а общая точка соединения коллектора четвертого транзистора и вывода четвертого резистора является выходом компаратора, вторым входом которого является база третьего транзистора, в каждый компаратор дополнительно введен пятый резистор, включенный между эмиттером первого транзистора и вторым выводом первого резистора, общая точка соединения первого и пятого резисторов первого компаратора соединена с базой третьего транзистора второго компаратора, а общая точка соединения первого и пятого резисторов второго компаратора соединена с базой третьего транзистора первого компаратора.

Введение отличительных признаков, а именно пятого резистора в цепь эмиттерного повторителя на первом входе каждого компаратора, а также связи общей точки соединения пятого и первого резисторов одного компаратора с базой третьего транзистора другого компаратора позволило в качестве эмиттерного повторителя, размещаемого на втором входе дифференциального каскада одного компаратора, использовать эмиттерный повторитель, расположенный на первом входе другого компаратора, и конструктивно организовать делители напряжения, запитываемые от одного источника питания, при этом управляющее каждым компаратором напряжение увеличилось почти вдвое, а пороговое напряжение, вырабатываемое делителями обоих компараторов, стало иметь одну и ту же величину, что, в свою очередь, обеспечило повышение точности работы устройства, существенно упростило его конструкцию и повысило его надежность.

По мнению авторов, данная совокупность признаков заявляемого изобретения является новой, а из уровня техники неизвестна причинно-следственная связь между отличительными признаками и достигаемым техническим результатом (целью).

Заявляемое изобретение поясняется чертежом, где:

- на фиг.1 приведена функциональная схема устройства и принципиальные схемы компараторов прототипа,

- на фиг.2 приведена функциональная схема устройства и принципиальные схемы компараторов заявляемого устройства.

Устройство для приема кодированной информации в линии связи содержит частотный фильтр 1 с двумя входами, являющимися входами устройства. Два выхода фильтра 1 соединены с соответствующими входами ограничителя амплитуды напряжения 2, два выхода которого соединены соответственно с первыми входами двух компараторов 3 и 4, выходы которых являются выходами устройства. Каждый компаратор 3, 4 содержит первый транзистор 5, база которого является входом компаратора, первый (являющийся одновременно нагрузочным и токозадающим) резистор 6, одним выводом соединенный с отрицательным полюсом первого источника питания 7, дифференциальный каскад, выполненный на втором и третьем транзисторах 8, 9, втором и третьем (соответственно токозадающем и нагрузочном) резисторах 10, 11. Общая точка соединения эмиттеров обоих транзисторов 8, 9 каскада соединена с одним из выводов второго резистора 10, другой вывод которого подсоединен к отрицательному полюсу первого источника питания 7, а третий резистор 11 включен между коллектором третьего транзистора 9 и положительным полюсом второго источника питания 12. Выходной каскад компараторов 3, 4 выполнен на четвертом транзисторе 13, база которого соединена с коллектором третьего транзистора 10, эмиттер заземлен, а коллектор соединен с одним из выводов четвертого (нагрузочного) резистора 14, второй вывод которого подсоединен к положительному полюсу второго источника питания 12. К этому же полюсу второго источника питания 12 подсоединены коллекторы первого 5 и второго 8 транзисторов. В цепь между эмиттером первого транзистора 5 и вторым выводом первого резистора 6 введен пятый (токозадающий и одновременно нагрузочный) резистор 15. Общая точка соединения первого 6 и пятого 15 резисторов компаратора 3 соединена с базой третьего транзистора 9 компаратора 4, а общая точка соединения первого 6 и пятого 15 резисторов компаратора 4 соединена с базой третьего транзистора 9 компаратора 3. База второго транзистора 8 соединена с эмиттером первого транзистора 5. Вторым входом каждого из компараторов 3, 4 является база третьего транзистора 9, а выходом - общая точка соединения коллектора четвертого транзистора 13 и вывода четвертого резистора 14 каждого компаратора 3, 4.

Заявляемое устройство работает следующим образом. При отсутствии сигнала на линии связи - входе устройства дифференциальный каскад каждого компаратора 3, 4 находится в переключенном состоянии, а именно второй транзистор 8 находится в проводящем состоянии, а третий транзистор 9 - в обесточенном, так что весь ток третьего резистора 11 поступает в базу четвертого транзистора 13, приводя его в состояние насыщения и формируя на его выходе напряжение, близкое к нулю ("логический нуль"). В этом режиме потенциалы баз второго 8 и третьего 9 транзисторов неодинаковы по величине и отличаются на величину падения напряжения на пятом резисторе 15, т.е. на величину так называемого порогового напряжения, достаточного для переключения дифференциального каскада. Следует отметить, что пороговые напряжения в обоих компараторах 3, 4 имеют практически одинаковую величину в силу следующих причин: идентичность параметров первых транзисторов 5, использование для образования пороговых напряжений одного и того же источника питания 7. При появлении входного сигнала, превышающего величину порогового напряжения происходит переключение дифференциальных каскадов. В этом случае в проводящем (открытом) состоянии на время действия отрицательной полуволны сигнала оказывается третий транзистор 9, а в непроводящем (закрытом) состоянии - второй транзистор 8. Параметры третьего (нагрузочного) резистора 11, третьего транзистора 9 выбираются из условия, чтобы потенциал его коллектора был "слегка" отрицательным, т.е. в диапазоне (-0,5 - -0,8 В), что является достаточным для запирания четвертого транзистора и образования на его выходе высокого состояния ("логической единицы"). А так как входной сигнал представляет собой чередование отрицательных и положительных уровней, то напряжения логических уровней на выходах компараторов будут чередоваться.

Следует еще раз отметить, что в заявляемом устройстве в отличие от прототипа каждый компаратор работает с почти удвоенной величиной входного сигнала, получая дополнительно к его собственному сигналу противоположный по знаку сигнал по второму входу от первого транзистора соседнего компаратора. Это приводит к улучшению качества работы компаратора (уменьшению длительности фронтов его выходных импульсов, увеличению запаса по обеспечению надежности переключения в условиях, отличных от нормальных климатических условий, а также при старении элементов устройства и т.д.).

Кроме того, в заявляемом устройстве уменьшено количество транзисторов (за счет исключения эмиттерных повторителей по второму входу компараторов), что также повышает надежность устройства и снижает его энергопотребление.

Заявляемое устройство может быть технически реализовано по известным правилам из стандартных элементов, выпускаемых промышленностью, что позволяет сделать вывод о его промышленной применимости.

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2157048C2 |

| Широкополосный операционный усилитель | 1983 |

|

SU1223338A1 |

| Аналоговый коммутатор | 1990 |

|

SU1798911A1 |

| УСТРОЙСТВО РЕГУЛИРОВАНИЯ СИНХРОННОГО ГЕНЕРАТОРА С ПРЕЦИЗИОННОЙ СИСТЕМОЙ УПРАВЛЕНИЯ | 2006 |

|

RU2312453C1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU815902A1 |

| Усилитель переменного тока с регулируемым коэффициентом усиления | 1989 |

|

SU1658375A1 |

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| Повторитель напряжения | 1981 |

|

SU1012420A1 |

| Аналоговый компаратор | 1982 |

|

SU1157521A1 |

| Операционный усилитель | 1973 |

|

SU470815A1 |

Изобретение относится к технике электрической связи, в частности к системам передачи информации по двухпроводным линиям связи. Технический результат заключается в упрощении конструкции устройства, а также в повышении точности и надежности его работы. Сущность изобретения заключается в том, что устройство для приема кодированной информации в линии связи содержит частотный фильтр (ЧФ), ограничитель амплитуды напряжения и два компаратора, каждый из которых включает в себя дифференциальный каскад, два источника питания, эмиттерный повторитель и делитель напряжения. 2 ил.

Устройство для приема кодированной информации в линии связи, содержащее частотный фильтр с двумя входами, являющимися входами устройства, причем два выхода фильтра соединены с соответствующими входами ограничителя амплитуды напряжения, два выхода которого соединены соответственно с первыми входами двух компараторов, выходы которых являются выходами устройства, при этом каждый компаратор содержит первый транзистор, база которого является входом компаратора, первый резистор, одним выводом соединенный с отрицательным полюсом первого источника питания, дифференциальный каскад, выполненный на втором и третьем транзисторах, втором и третьем резисторах, причем база второго транзистора соединена с эмиттером первого транзистора, а общая точка соединения эмиттеров обоих транзисторов каскада соединена одним из выводов второго резистора, другой вывод которого подсоединен к отрицательному полюсу первого источника питания, а третий резистор включен между коллектором третьего транзистора и положительным полюсом второго источника питания, выходной каскад на четвертом транзисторе, база которого соединена с коллектором третьего транзистора, эмиттер заземлен, а коллектор соединен с одним из выводов четвертого резистора, при этом второй вывод четвертого транзистора, коллекторы первого и второго транзисторов подсоединены к положительному полюсу второго источника питания, а общая точка соединения коллектора четвертого транзистора и вывода четвертого резистора является выходом компаратора, вторым входом которого является база третьего транзистора, отличающееся тем, что в каждый компаратор дополнительно введен пятый резистор, включенный между эмиттером первого транзистора и вторым выводом первого резистора, общая точка соединения первого и пятого резисторов первого компаратора соединена с базой третьего транзистора второго компаратора, а общая точка соединения первого и пятого резисторов второго компаратора соединена с базой третьего транзистора первого компаратора.

| Устройство для приема и передачи информации | 1988 |

|

SU1510095A1 |

| US 3838393, 24.09.1974 | |||

| US 4101734, 18.07.1978 | |||

| Устройство для передачи и приема информации с многозначным кодированием | 1984 |

|

SU1206830A1 |

Авторы

Даты

2005-09-27—Публикация

2004-03-09—Подача