1

(21)4364534/24-24

(22)13.01.88

(46) 23.09.89. Бюл. № 35

(72) 3.Д.Коноплянке

(53) 681.325(088.8)

(56) Патент США № 3838393,

кл. Н 04 В 1/00, опублик. 1975.

Патент США № 4101734, кл. Н 04 В 1/00, опублик. 1978.

(54) УСТРОЙСТВО ДЛЯ ПРИЕМА И ПЕРЕДАЧИ ИНФОРМАЦИИ

(57) Изобретение относится к вычислительной технике и может быть использовано в цифровых устрогйствах и системах обработки данных при организации интерфейса.. Цель изобретения - повьшение надежности устройства. Устройство содержит входной суммирующий блок 1, блок 2 пороговых детекторов, линию 3 связи, инжекторы 4-9 тока, ключевые элементы 10-12, элементы НЕ 13-16 и элементы И 17-24. 4 ил., 4 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Четырехзначный умножитель элементов поля Галуа GF(2 @ ) | 1990 |

|

SU1737443A1 |

| Устройство для обмена информацией | 1978 |

|

SU824186A1 |

| ВОСЬМИЗНАЧНОЕ УСТРОЙСТВО ПРИЕМА И ПЕРЕДАЧИ ДАННЫХ | 1992 |

|

RU2012061C1 |

| Устройство для передачи и приема информации с многозначным кодированием | 1984 |

|

SU1206830A1 |

| Одноразрядный сумматор на инжекционных элементах | 1985 |

|

SU1275430A1 |

| Устройство для передачи и приема многоуровневых сигналов | 1983 |

|

SU1203565A1 |

| Универсальный многозначный логический элемент инжекционного типа /его варианты/ | 1980 |

|

SU890558A1 |

| Многофункциональное логическое устройство | 1982 |

|

SU1026314A1 |

| Четверичный сумматор инжекционного типа | 1980 |

|

SU959280A1 |

| Устройство для контроля перемещения подвижных объектов | 1989 |

|

SU1652965A1 |

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах и системах обработки данных при организации интерфейса. Цель изобретения - повышение надежности устройства. Устройство содержит входной суммирующий блок 1, блок 2 пороговых детекторов, линию 3 связи, инжекторы 4-9 тока, ключевые элементы 10-12, элементы НЕ 13 - 16 и элементы И 17-24. 4 ил.

Изобретение относится к вычислительной технике и может быть использовано в цифровых устройствах и системах обработки данных при организа- ции интерфейса.

Цель изобретения - повьшение надежности устройства.

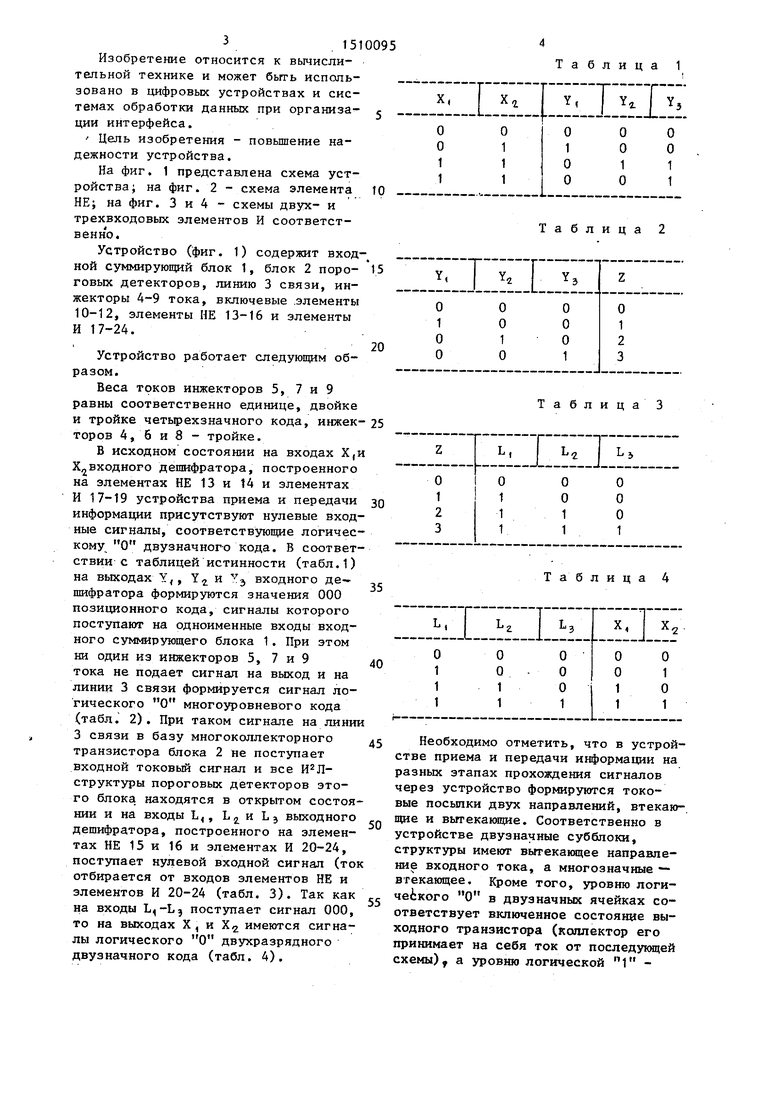

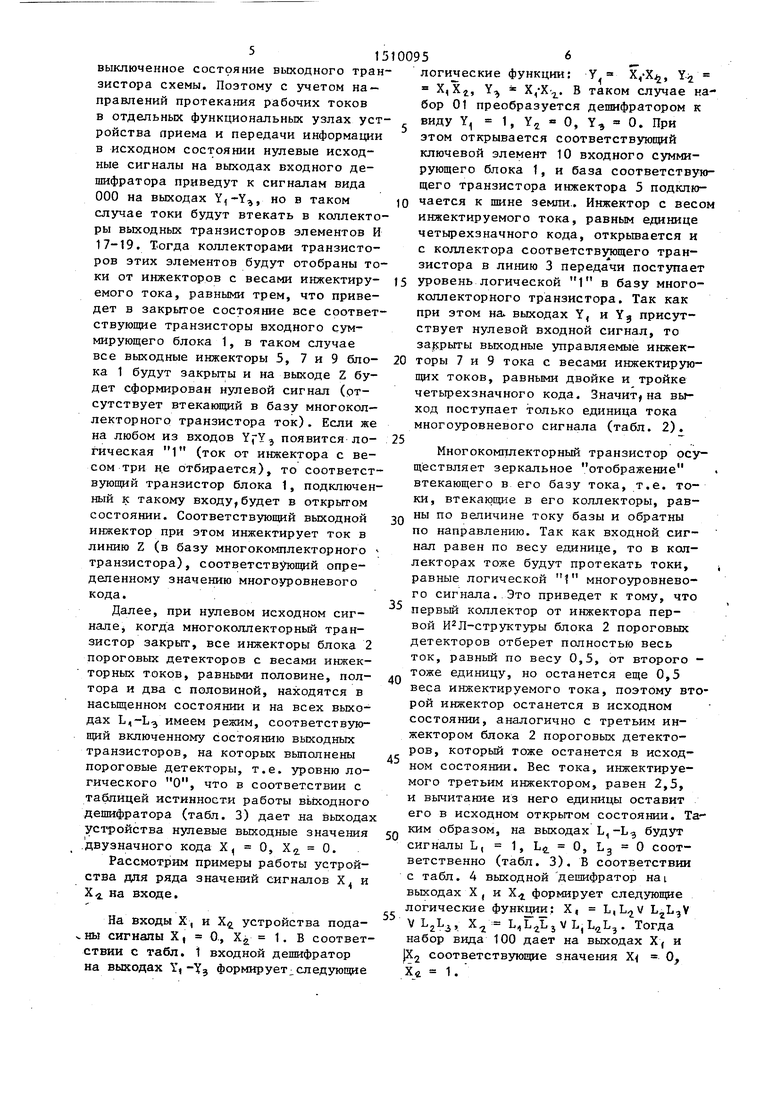

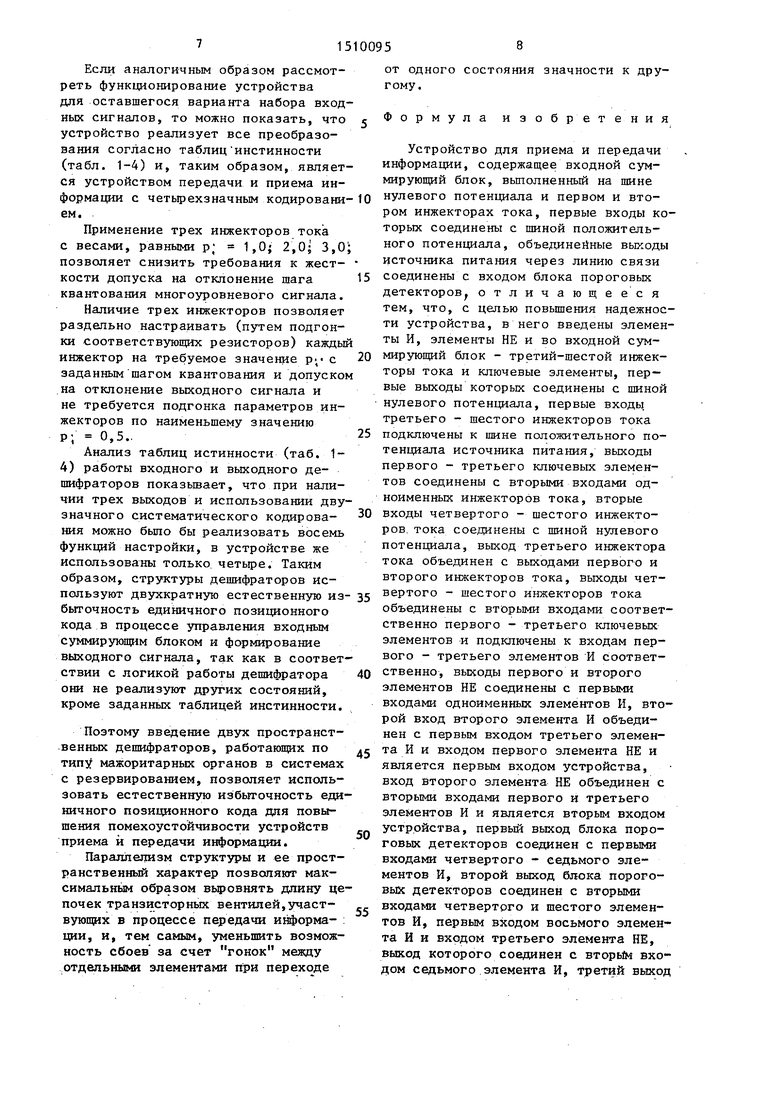

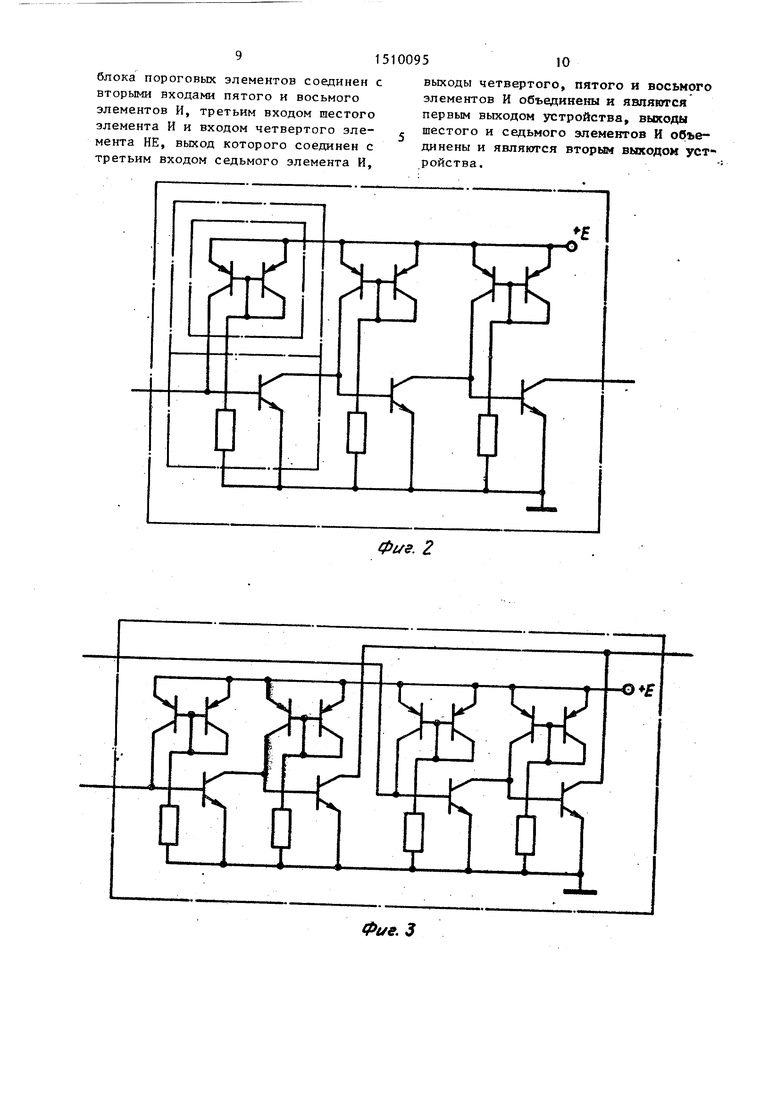

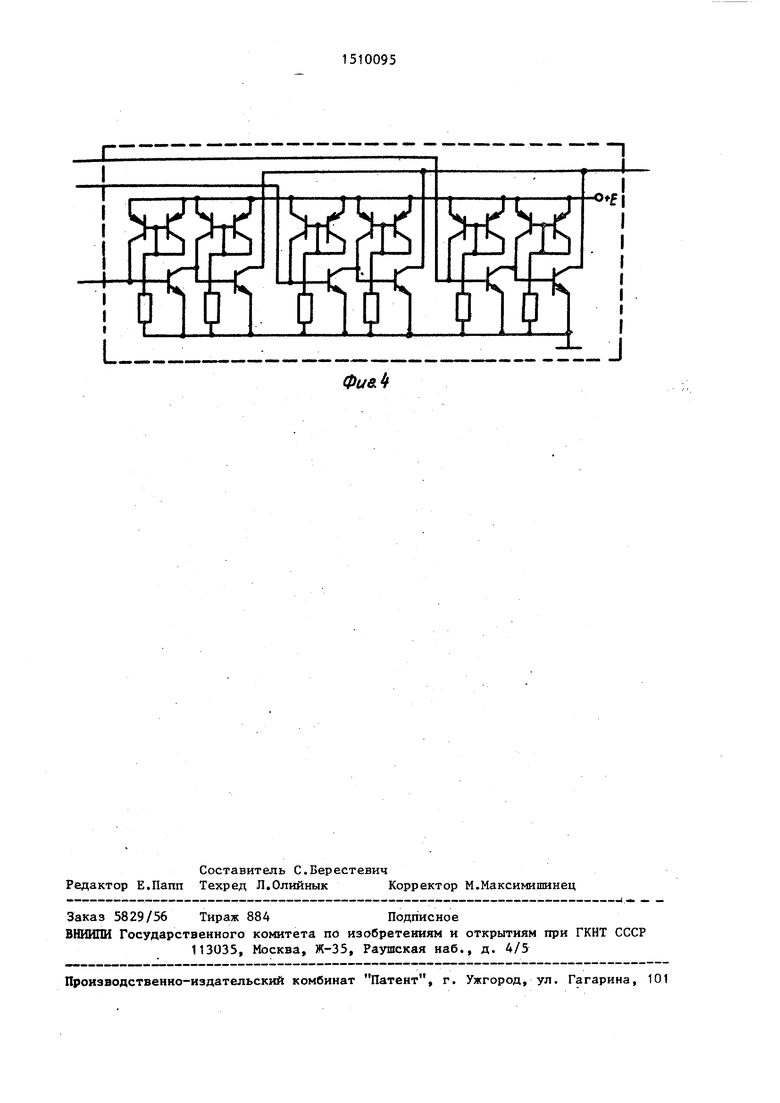

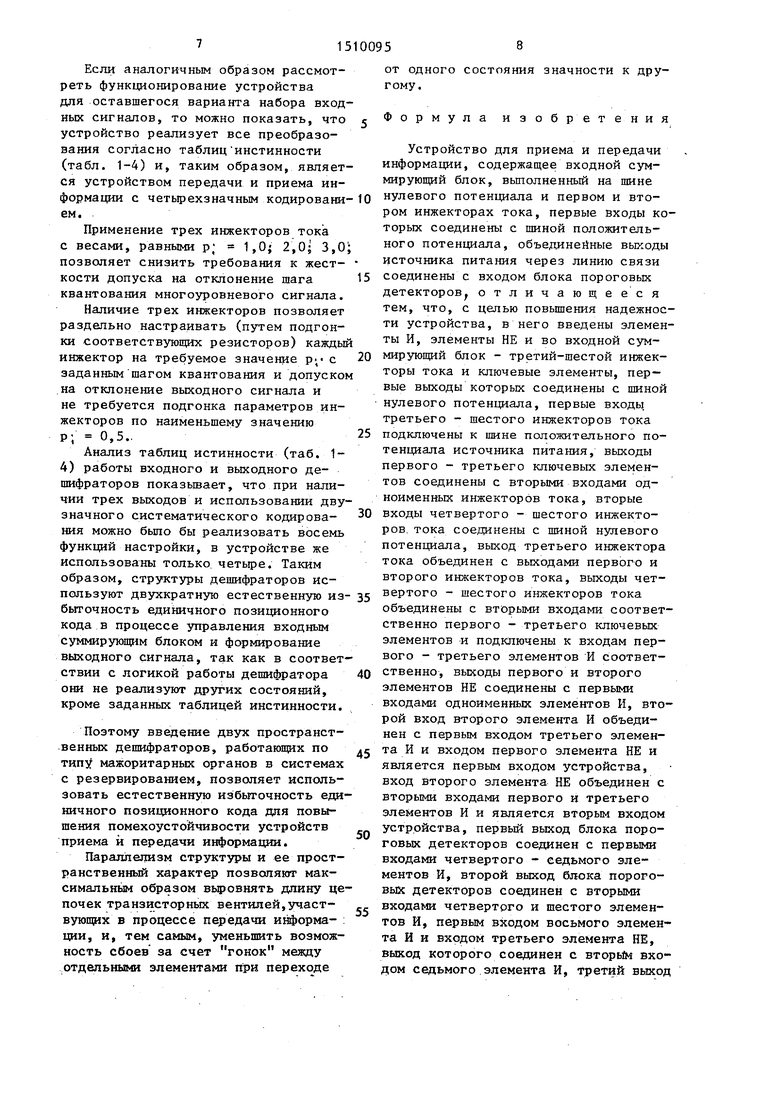

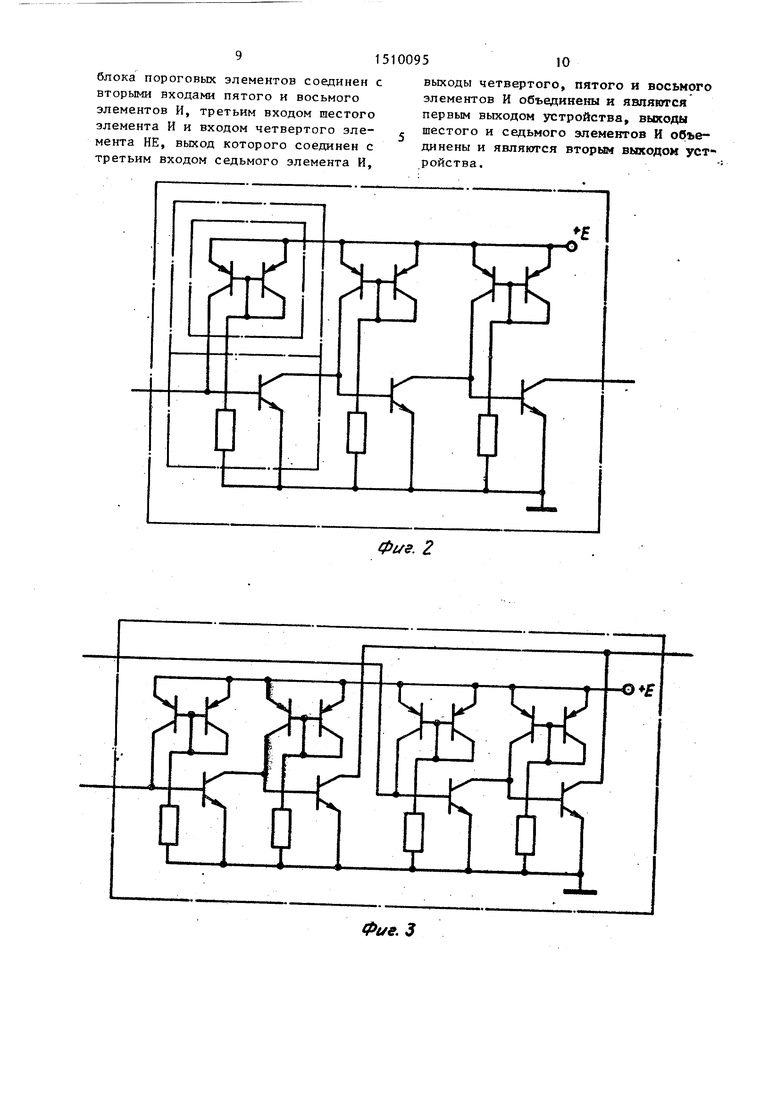

На фиг. 1 представлена схема устройства; на фиг. 2 - схема элемента НЕ; на фиг. 3 и 4 - схемы двух- и трехвкодовых элементов И соответст- венн о.

Устройство (фиг. 1) содержит входной суммирующий блок 1, блок 2 поро- говых детекторов, линию 3 связи, инжекторы 4-9 тока, включевые .элементы 10-12, элементы НЕ 13-16 и элементы И 17-24.

Устройство работает следующим образом.

Веса токов инжекторов 5, 7 и 9 равны соответственно единице, двойке и тройке четырехзначного кода, инжек- торов 4, 6 и 8 - тройке.

В исходном состоянии на входах Х,и Х-входного дешифратора, построенного на элементах НЕ 13 и t4 и элементах И 17-19 устройства приема и передачи информации присутствуют нулевые входные сигналы, соответствующие логическому О двузначного кода. В соответствии с таблицей истинности (табл.1) на выходах Y,, Y и входного дешифратора формируются значения 000 позиционного кода, сигналы которого поступают на одноименные входы входного суммирующего блока 1. При этом ни один из инжекторов 5, 7 и 9

тока не подает сигнал на выход и на линии 3 связи формируется сигнал логического О многоуровневого кода (табл. 2). При таком сигнале на линии 3 связи в базу многоколлекторного

транзистора блока 2 не поступает входной токовый сигнал и все структуры пороговых детекторов этого блока находятся в открытом состоянии и на входы L,, Lj и Lj выходного дешифратора, построенного на элементах НЕ 15 и 16 и элементах И 20-24, поступает нулевой входной сигнап (то отбирается от входов элементов НЕ и элементов И 20-24 (табл. 3). Так как на входы Ь,-Ьз поступает сигнал 000, то на выходах X, и Х имеются сигналы логического О двухразрядного двузначного кода (табл. 4).

Таблица 1

Необходимо отметить, что в устройстве приема и передачи информации на разных этапах прохождения сигналов через устройство формируются токовые посьшки двух направлений, втекающие и вытекакнцие. Соответственно в устройстве двузначные субблоки, структуры имеют вытеканмцее направление входного тока, а многозначные - втекаклцее. Кроме того, уровню логи- О в двузначных ячейках соответствует включенное состояние выходного транзистора (коллектор его принимает на себя ток от последукщей схемы)у а уровню логической 1 выключенное состояние вьпсодного транзистора схемы. Поэтому с учетом направлений протекания рабочих токов в отдельных функциональных узлах устройства приема и передачи информации в исходном состоянии нулевые исходные сигналы на выходах входного дешифратора приведут к сигналам вида 000 на выходах Y,-Y,, но в таком случае токи будут втекать в коллекторы выходных транзисторов элементов И 17-19. Тогда коллекторами транзисторов этих элементов будут отобраны токи от инжекторов с весами инжектируемого тока, равными трем, что приведет в закрытое состояние все соответствующие транзисторы входного суммирующего блока 1, в таком случае все выходные инжекторы 5, 7 и 9 блока 1 будут закрыты и на выходе Z будет сформирован нулевой сигнал (отсутствует втекающий в базу многокол- лекторного транзистора ток). Если же на любом из входов , появится логическая 1 (ток от инжектора с весом три не отбирается), то соответствующий транзистор блока 1, подключенный к такому входу,будет в открытом состоянии. Соответствующий выходной инжектор при этом инжектирует ток в линию Z (в базу многоког лекторного транзистора), соответствующий определенному значению многоуровневого кода.

Далее, при нулевом исходном сиг- напе когда многоколлекторный транзистор закрыт, все инжекторы блока 2 пороговых детекторов с весами инжекторных токов, равными половине, полтора и два с половиной, находятся в насьпценном состоянии и на всех выходах Ь,-Ьз имеем режим, соответствующий включенному состоянию выходньпс транзисторов, на которых выполнены пороговые детекторы, т.е. уровню логического О, что в соответствии с таблицей истинности работы вьгходного дешифратора (табл. 3) дает на выходах устройства нулевые выходные значения . двузначного кода X, О, Х2. 0.

Рассмотрим примеры работы устройства для ряда значений сигналов Х и Х на входе.

На входы X, и Х устройства пода- . ны сигналы X, 0., Xj, 1. В соответствии с табл. 1 входной дешифратор на выходах Y,-у, формирует;.еледзтощие

логические функции: У

0

Х,Х

г

Y .у

А,Л.

X, Xij, Y; В таком случае набор 01 преобразуется дешифратором к

1

виду Y, 1, Y О, Y, « 0. При

0

этом открывается соответствующий ключевой элемент 10 входного суммирующего блока 1, и база соответствующего транзистора инжектора 5 подключается к шине земли.. Инжектор с весом инжектируемого тока, равным единице четырехзначного кода, открьтается и с коллектора соответствующего транзистора в линию 3 передачи поступает 5 уровень логической 1 в базу многоколлекторного транзистора. Так как при этом на выходах Y, и Y присутствует нулевой входной сигнал, то закрыты выходные управляемые инжекторы 7 и 9 тока с весами инжектирующих токов, равными двойке и тройке четырехзначного кода. Значит на вьг- ход поступает только единица тока многоуровневого сигнала (табл. 2).

0

5

0

5

0

5

5

Многокомплекторный транзистор осуществляет зеркальное отображение втекающего в его базу тока, т.е. токи, втекающие в его коллекторы, равны по величине току базы и обратны по направлению. Так как входной сигнал равен по весу единице, то в коллекторах тоже будут протекать токи, равные логической 1 многоуровневого сигнала. Это приведет к тому, что первый коллектор от инжектора первой И Л-структуры блока 2 пороговых детекторов отберет полностью весь ток, равный по весу 0,5, от второго - тоже единицу, но останется еще 0,5 веса инжектируемого тока, поэтому второй инжектор останется в исходном состоянии, аналогично с третьим инжектором блока 2 пороговых детекторов, который тоже останется в исходном состоянии. Вес тока, инжектируемого третьим инжектором, равен 2,5, и вычитание из него единицы оставит его в исходном открытом состоянии. Таким образом, на выходах L,-L будут сигналы L, 1, Lg О, Lg О соответственно (табл. 3). В соответ.ствии с табл. 4 выходной дешифратор Hai выходах X, и Х формирует следующие логические функции: X, L, , Х V , . Тогда набор вида 100 дает на выходах X, и jXj соответствуюЕ(не значения Х О, Хг 1.

Если аналогичным образом рассмотреть функционирование устройства для оставшегося варианта набора входных сигналов, то можно показать, что устройство реализует все преобразования согласно таблиц инстинности (табл. 1-4) и, таким образом, является устройством передачи и приема информации с четырехзначным кодировани- ем.

Применение трех инжекторов тока с весами, равными р; 1,0; 2,0; 3,0 позволяет снизить требования к жест- кости допуска на отклонение шага квантования многоуровневого сигнала.

Наличие трех инжекторов позволяет раздельно настраивать (путем подгонки соответствующих резисторов) каждый инжектор на требуемое значение р-/ с заданным шагом квантования и допуском .на отклонение выходного сигнала и не требуется подгонка параметров инжекторов по наименьшему значению р; 0,5..

Анализ таблиц истинности (таб. 1- 4) работы входного и выходного дешифраторов показьшает, что при наличии трех выходов и использовании двузначного систематического кодирова- ния можно было бы реализовать восемь функций настройки, в устройстве же использовань: только, четьфе. Таким образом, структуры дешифраторов используют двухкратную естественную из быточность единичного позиционного кода в процессе управления входным суммирующим блоком и формирование выходного сигнала, так как в соответствии с логикой работы дешифратора они не реализуют других состояний, кроме заданных таблицей инстинности.

Поэтому введение двух пространственных дешифраторов, работающих по типу мажоритарных органов в системах с резервированием, позволяет использовать естественную избыточность единичного позиционного кода для повышения помехоустойчивости устройств приема и передачи информации.

Параллелизм структуры и ее пространственный характер позволяют максимальным образом вьфовнять длину цепочек транзисторных вентш1ей,згчаст- вующих в процессе передачи информации, и, тем самым, уменьшить возможность сбоев за счет гонок между отдельными элементами при переходе

5

5

0

5 0

0

от одного состояния значности к другому.

Формула изобретения

Устройство для приема и передачи информации, содержащее входной суммирующий блок, выполненный на шине нулевого потенциала и первом и втором инжекторах тока, первые входы которых соединены с шиной положительного потенциала, обьединейные выходы источника питания через линию связи соединены с входом блока пороговых детекторовJ отличающееся тем, что, с целью повьш1ения надежности устройства, в него введены элементы И, элементы НЕ и во входной суммирующий блок - третий-шестой инжекторы тока и ключевые элементы, первые выходы которых соединены с шиной нулевого потенциала, первые входы, третьего - шестого инжекторов тока подключены к шине положительного потенциала источника питания, выходы первого - третьего ключевых элементов соединены с вторыми входами одноименных инжекторов тока, вторые входы четвертого - шестого инжекторов, тока соединены с шиной нулевого потенциала, выход третьего инжектора тока обьединен с выходами первого и второго инжекторов тока, выходы четвертого - шестого инжекторов тока объединены с вторыми входами соответственно первого - третьего ключевых элементов и подключены к входам первого - третьего элементов И соответственно, выходы первого и второго элементов НЕ соединены с первыми входами одноименшзк элементов И, второй вход второго элемента И объединен с первым входом третьего элемента И и входом первого элемента НЕ и является первым входом устройства, вход второго элемента НЕ объединен с вторыми входами первого и третьего элементов И и является вторым входом устройства, первый выход блока пороговых детекторов соединен с первыми входами четвертого - седьмого элементов И, второй выход блока пороговых детекторов соединен с вторыми входами четвертого и шестого элементов И, первым входом восьмого элемента И и входоь третьего элемента НЕ, выход которого соединен с вторым входом седьмого элемента И, третий выход

блока пороговых элементов соединен с вторыми вxoдa и пятого и восьмого элементов И, третьим входом шестого элемента И и входом четвертого элемента НЕ, выход которого соединен с третьим входом седьмого элемента И,

выходы четвертого, пятого и восьмого элементов И объединены и являются первым выходом устройства, выходы шестого и седьмого элементов И объединены и являются вторым выходом згст- ройства.

Фие. 2

Фие. 3

Фие.

Авторы

Даты

1989-09-23—Публикация

1988-01-13—Подача