.

Изобретение относится к электросвязи и может быть использовано для передачи информации в цифровых вы- числительных системах при организации интерфейса

Целью изобретения является повышение быстродействия устройства.

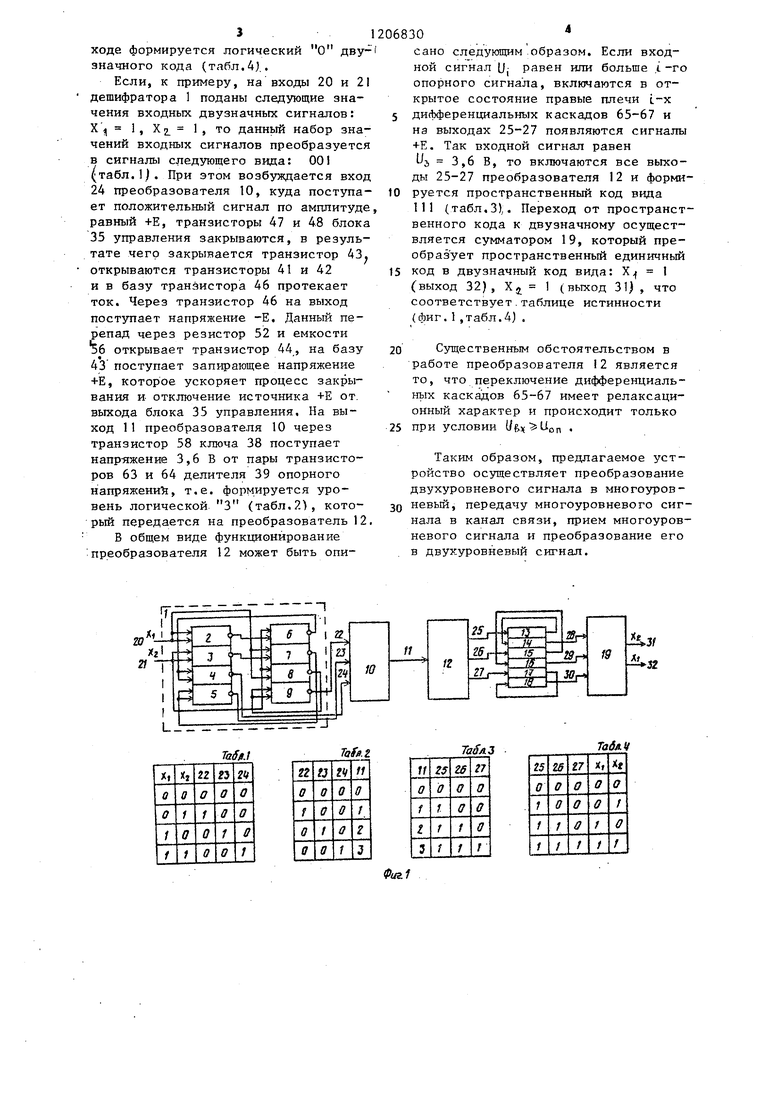

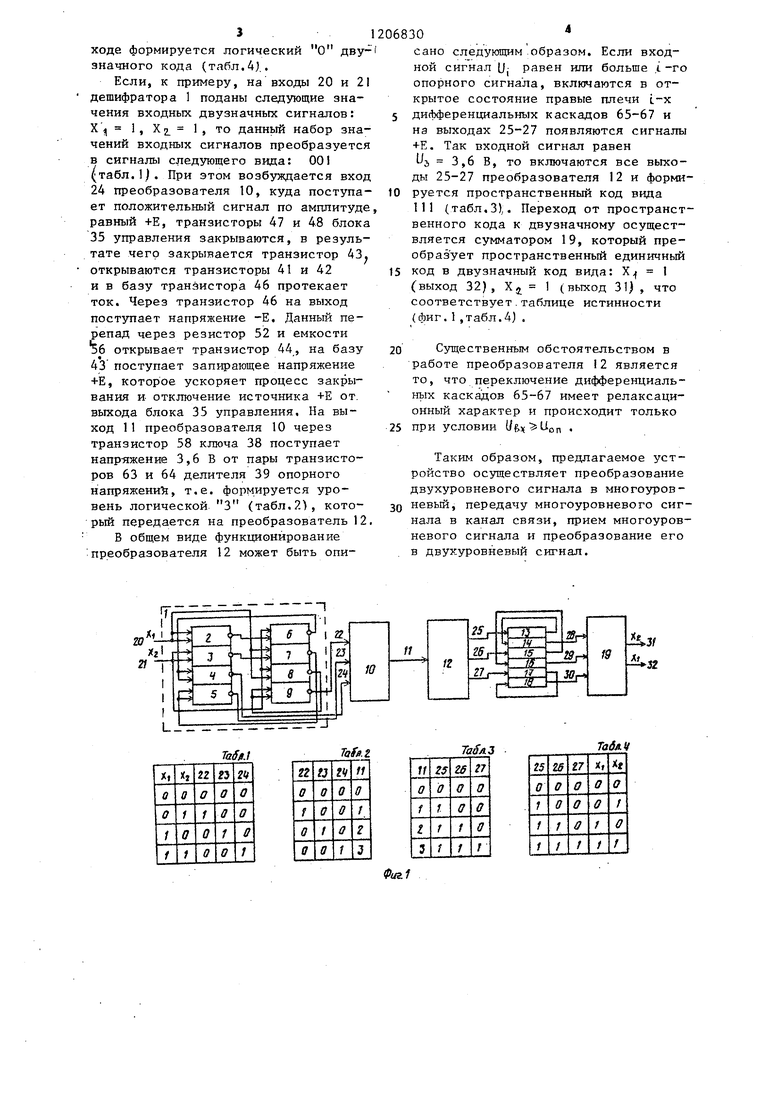

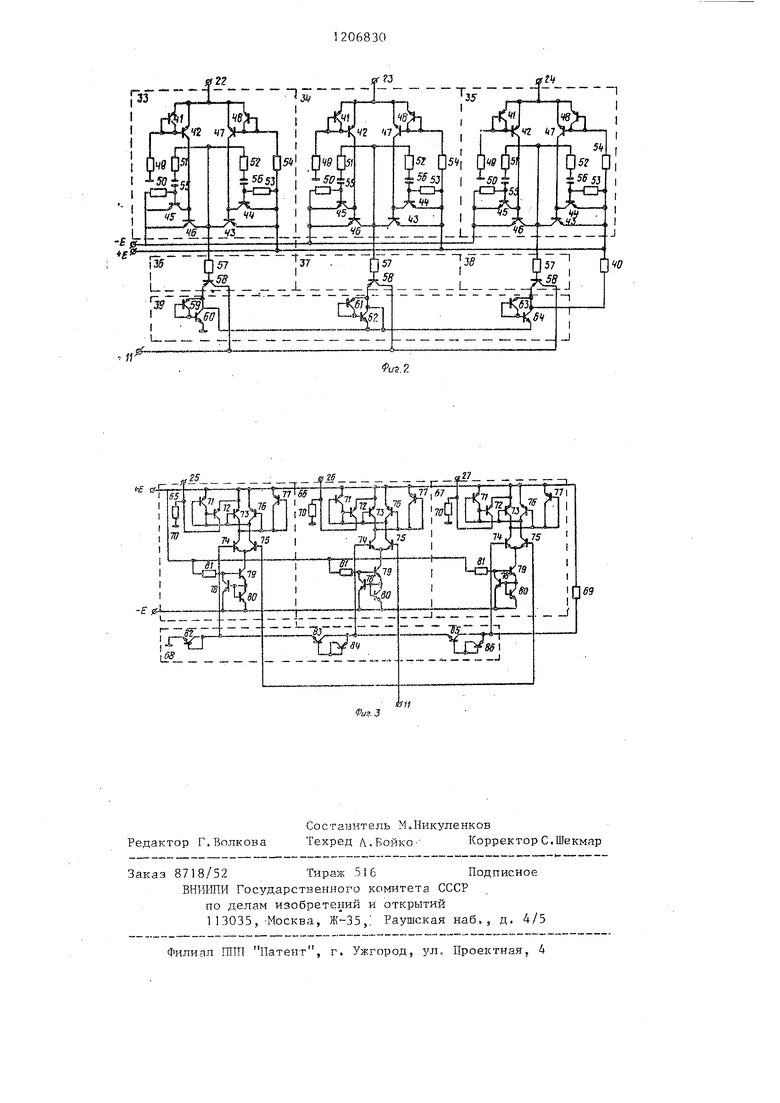

На.фиг. 1 показана ф ункциональная схема устройства для передачи и приема информации с многозначным кодированием и его таблицы истинности; на фиг.2 - принципиальная схема цифро-аналогового преобразователя; на фиг.3 - принципиальная схема аналого-цифрового преобразователя.

Устройство для передачи и приема информации с многозначнь м кодированием СФИГ.1) содержит дешифратор 1. выполненный на элементах НЕ 2-5, элементах И-НЕ 6-8, элементе НЕ 9, цифроаналоговьш преобразователь 0j канал 11 связи, аналого-цифровой преобразователь 12, триггеры 13 - 18 1Ш-1идта, сумматор 19, входы 20 и 21 дешифратора 1, входы 22-24 цифро аналогового преобразователя 10, выходы 25-27 аналого-цифрового преобразователя 12, входы 28-30 и выходы 31-32 сумматора 19. Цифроаналого вый преобразователь 10 (фиг.2) содержит блоки 33-35 управления, ключи 36-38, делитель 39 опорного напряжения, резистор 40, транзисторы 41-48, резисторы 49-50, конденсаторы 55 и 56, резисторы 57 и транзисторы 58-64. Аналого-цифровой преобразователь 12 (фиг.З) содержит компараторы 65-67 на дифференциальных каскадах, формирователь 68 опорного напряжения, резисторы 69 и 70, транзисторы 71-80, резисторы 81 и транзисторы 82-86.

Устройство работает следующим образом.

Для конкретности рассмотрим работу на примере устройства с четырехзначным кодированием. В исходном состоянии на входах 20 и 21 дешифратора 1 присутствуют нулевые входные сигналы, соответствующие логическому О двузначного кода. Согласно фиг,1 (табл.1) , на выходах 22-24 дешифратора 1 Нормируется унитарный пространственный код 000, сигналы которого поступают на соответствующие входы преобразователя 10. В это случае от +Е источника питания {фиг.2) подается положительный по0683q

тенциал в базы транзисторов 47, 48 и, в зависимости от величины резис-. тора 54, ток протекает в корректор транзистора 47 так, что транзистор

5 43 открыт и положительный потенциал подается в базу транзистора 58 и запирает его.

Транзистор 59 работает при малом токе эмиттера, поэтому U5э транзисто10 ра 59 и U(.транзистора 60 равны, т.е. Ц&Э1 8-,, тогда выходное напряжение на паре транзисторов 59 и 60 будет равным 2tJg3(. Напряжение tJSj US-,,j 0,6 В, тогда на выходе имеем

15 2 1,2 В.

Следовательно, эмиттер транзистора 58 ключа 36 подключен к паре транзисторов 59 и 60, где падение напряжения равно Ui 1,2 В, а эмиттер

20 транзистора 58 ключа 37 подключен к паре транзисторов 61 и 62, где падение напряжения равно U 2,4 В и эмиттер транзистора 58 ключа 38 подключен, соответственно, к паре тран - зисторов 63 и 64, где падение напряжения равно и 3,6 В. Так как транзистор 58 закрыт на выход 11 преобразователя 10 напряжение не поступает от делителя 39 опорного напряже30 ния. На выходе 11 формируется уровень логического О, который передается по каналу 11 связи на вход преобразователя 12. Входной сигнал о поступает одновременно на все

35 правые плечи (транзистор 75) трех дифференциальных каскадов 65-67. Левые плечи (транзистор 74) в каждом дифс})еренциальном каскаде подключены к соответствуюшим точкам формирова40 теля 68 опорных напряжений, где падение напряжения на транзисторе 82 равно 0,6 В, в точке, образуемой транзисторами 83 и 84 - 1,8 В, а в точке, образуемой транзисторами 85,

45 86 - 3,0 В.

Как ввдно, по сравнению с напряжением делителя 39 напряжение формирователя 68 сдвинуто вниз на 0,6 В. За счет этого обеспечивается быстрое

50 и точное срабатывание соответствующих каскадов преобразователя 12.

В исходном состоянии левые плечи Стрензистор 74)1 дифференциальных кас- кадов 65-67 находятся в открытом сос- 55 тоянии и на выходах 25-27 преобразователя 12 исходное нулевое состояние. Так как на входы сумматора 19 сигналы не поступают, то на его вы5

ходе формируется логический О двузиачного кода (табл.4Ь

Если, к примеру, на входы 20 и 21 дешифратора 1 поданы следующие значения входных двузначных сигналов: X 1 , X z 1 , то данный набор значений входных сигналов преобразуется в сигналы следующего вида: 001 (табл.;. При этом возбуждается вход 24 преобразователя 10, куда поступает положительный сигнал по амплитуде равный +Е, транзисторы 47 и 48 блока 35 управления закрываются, в результате чего закрывается транзистор 43. открываются транзисторы 41 и 42 и в базу транзистора 46 протекает ток. Через транзистор 46 на выход поступает напряжение -Е. Данный перепад через резистор 52 и емкости 36 открывает транзистор 44, на базу 43 поступает запирающее напряжение +Е, которое ускоряет процесс закрывания и отключение источника +Е от. выхода блока 35 управления. На выход 11 преобразователя 10 через транзистор 58 ключа 38 поступает напряжение 3,6 В от пары транзисторов 63 и 64 делителя 39 опорного напряжений, т.е. формируется уровень логической 3 (табл.2), который передается на преобразователь 12.

В общем виде функционирование преобразователя 12 может быть опи10

06830Л

сано следующим .образом. Если входной сигнал Uj равен или больше i-го опорного сигнала, включаются в открытое состояние правые плечи L-X 5 дифференциальных каскадов 65-67 и на выходах 25-27 появляются сигналы +Е. Так входной сигнал равен iJj 3,6 В, то включаются все выходы 25-27 преобразователя 12 и формируется пространственный код вида 111 (табл.3),. Переход от пространственного кода к двузначному осуществляется сумматором 19, который пре- образ ует пространственный единичный 5 код в двузначный код вида: Х I (выход 32), Xj, (выход 31), что соответствует.таблице истинности (фиг. 1 ,табл.4) .

0 Существенным обстоятельством в работе преобразователя 12 является то, что переключение дифференциальных каскадов 65-67 имеет релаксационный характер и происходит только

5 при условии l/ : 5:Uon .

Таким образом, предлагаемое устройство осуществляет преобразование двухуровневого сигнала в многоуроп- 0 невый, передачу многоуровневого сигнала в канал связи, прием многоуровневого сигнала и преобразование его . в двухуровневый сигнал.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| УСТРОЙСТВО КОНТРОЛЯ ПАРАМЕТРОВ | 1996 |

|

RU2106679C1 |

| Программный генератор | 1983 |

|

SU1190484A1 |

| Устройство для контроля положения стационарных плужковых сбрасывателей | 1990 |

|

SU1813686A1 |

| Широкодиапазонный логарифмический аналого-цифровой преобразователь | 1988 |

|

SU1580557A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ И СПОСОБ ЕГО КАЛИБРОВКИ | 2006 |

|

RU2341017C2 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1985 |

|

SU1356233A1 |

| Аналого-цифровой преобразователь интегральных характеристик электрических величин | 1981 |

|

SU1035790A1 |

| Программный генератор | 1982 |

|

SU1062858A2 |

LJ-rrrr

Taff.l

Га fa. 2

TafAS

ТаблЧ

ZV

fC 0-E

Редактор Г.Волкова

Составитель М.Никуленков

Техред А. Бойко Корректор С.Шекмар

Заказ 8718/52 Тираж 5 бПодписное

ВНИШИ Государственного комитета СССР по делам изобретений и открытий 1 13035, -Москва, ж -ЗЗ, Раушская наб. , д. 4/5

Филиал ШШ Патент, г. Ужгород, ул Проектная, 4

t u.. 3

ifll

| Патент США № 4101734, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Росс | |||

| Уменьшение числа системных связей благодаря многоуровневой логике | |||

| - Электроника, 1977, т | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Приспособление для автоматической односторонней разгрузки железнодорожных платформ | 1921 |

|

SU48A1 |

Авторы

Даты

1986-01-23—Публикация

1984-06-26—Подача