Изобретение относится к цифровой вычислительной технике, в частности к средствам к средствам контроля и поиска неисправностей в устройствах с дискретным характером функционирования.

Известна система диагностирования цифровых устройств, содержащая вычислительное устройство с центральным процессорным блоком, мультиплексор и шины связи с объектом диагностирования (RU №2127447, G 06 F 11/26, 1999 г.).

Недостатком технического решения известной системы является неэффективное использование ресурсов вычислительного устройства по причине заимствования ее значительной части на второстепенные функции.

Более совершенным и наиболее близким аналогом заявляемому изобретению является устройство проверки работоспособности сегментов локальной сети, содержащее программируемый контроллер с интегрированным в оперативной и постоянной памяти программным обеспечением функций сбора и обработки информации о периферийных устройствах сегмента, буферную память, выходной регистр, входной регистр, генератор тактовой частоты и блок питания (US №5919250, G 06 F 15/17, 1999 г.).

Указанное устройство обеспечивает эффективное использование ресурсов локальной сети за счет преобразования умеренных количеств информации в местах ее возникновения. Однако достижение этого результата обусловлено усложнением схемотехнических решений узлов локальной сети, что в конечном итоге увеличивает затраты и исключает применение неспециализированных для этого аппаратных средств.

Задачей, на решение которой направлено заявляемое изобретение, является создание надежного и сравнительно дешевого средства для тестирования работоспособности сегментов локальных сетей (например, Ethernet) и для удаленного управления подключенным к нему оборудованием посредством выдачи цифровых дискретных сигналов, а также сбора первичной информации от датчиков, подключенных к цифровым дискретным входам устройства.

Технический результат, который может быть получен при осуществлении изобретения, заключается в обеспечении возможности применять устройство в различных случаях, где требуется взаимодействие неспециализированных устройств, датчиков, и исполнительных механизмов с дискретными интерфейсами управления с локальными вычислительными сетями, например, на основе технологии Ethernet и группы протоколов TCP/IP.

Указанный технический результат достигается устройством проверки работоспособности сегментов локальной сети, содержащим программируемый контроллер с интегрированным в оперативной и постоянной памяти программным обеспечением функций сбора и обработки информации о периферийных устройствах сегмента, буферную память, выходной регистр, входной регистр, генератор тактовой частоты и блок питания, за счет того, что оно оно снабжено буферным выходным каскадом силовых выходов для подключения внешнего оборудования к локальной сети и буферным входным каскадом ввода для подключения внешнего оборудования к локальной сети, при этом генератор тактовой частоты подключен к программируемому контроллеру, буферная память подключена к программируемому контроллеру, блок питания соединен с программируемым контроллером, тактовым генератором и внешней энергонезависимой памятью, программируемый контроллер через выходной регистр соединен с буферным выходным каскадом, а посредством входного регистра соединен с буферным входным каскадом, причем входной регистр выполнен в виде сдвигового регистра с возможностью параллельной записи информации, а выходной регистр выполнен в виде сдвигового регистра с возможностью последовательной записи информации.

А также за счет того, что дополнительно содержит сетевой контроллер, предназначенный для проверки корректности и идентификации пакетов.

А также за счет того, что буферная память выполнена в виде внешней энергонезависимой памяти, подключенной по последовательному интерфейсу к программируемому контроллеру.

А также за счет того, что блок питания выполнен в виде интегрального параметрического стабилизатора питания с выпрямителем на основе диодного моста с варистером на входе и сглаживающим конденсатором на выходе.

Данное техническое решение обеспечивает подключение к стандартной локальной вычислительной компьютерной сети на основе технологии Ethernet, поддержку стандартных протоколов работы в сетях на основе технологии TCP/IP и за счет этого использование устройства в огромном количестве уже существующих сетей, работающих на основе этой технологии, в том числе и в составе глобальной компьютерной сети Internet. Поддержка ICMP-протокола и статический IP-адрес, позволяют использовать устройство для тестирования факта работоспособности сегмента локальной сети, в которой оно установлено, и сканировать внешние датчики дискретных сигналов. А если при сетевом контроллере, соответствующем стандарту Ethernet, в качестве управляющего протокола устройства применяется стандартный протокол SNMP, то это позволяет управлять устройством при помощи стандартных SNMP-клиентов, входящих в состав всех наиболее популярных ОС и выдержать все стандарты на подключение к локальным компьютерным сетям на основе технологии Ethernet.

Возможность собственной программной реализации всех основных протоколов работы в сетях на основе группы протоколов TCP/IP, и всех функций устройства по управлению дискретными входами/выходами на контроллере с минимальными затратами ресурсов позволила максимально снизить цену устройства без ущерба для его функциональности, при этом внешняя энергонезависимая память позволяет выполнять процесс удаленного обновления программного обеспечения устройства без угрозы привести устройство в неработоспособное состояние из-за искажения информации в процессе передачи и без каких-либо физических действий над устройством.

Применение программируемого контроллера с интегрированным в оперативной и постоянной памяти программным обеспечением функций сбора и обработки информации о периферийных устройствах сегмента максимально уменьшило количество внешних элементов и, как следствие, удешевило устройство и сделало его более компактным.

Сочетанием буферного выходного каскада силовых выходов для подключения внешнего оборудования к локальной сети с выходным регистром в виде сдвигового регистра на основе микросхемы с возможностью последовательной записи информации создаются условия для управления независимыми дискретными выходными каналами, когда каждый из каналов имеет выходной усилитель тока и выход типа открытый коллектор, что позволяет использовать выходные сигналы в широком диапазоне напряжений и выходных токов.

Сочетанием буферного входного каскада ввода для подключения внешнего оборудования к локальной сети с входным регистром в виде сдвигового регистра на основе микросхемы с возможностью параллельной записи информации создаются условия для приема сигналов с независимых дискретных входов, когда каждый из входов имеет защиту от перенапряжения, ограничитель тока, и пассивную защиту от внешних помех.

Наличие источника питания в виде интегрального параметрического стабилизатора питания с выпрямителем на основе диодного моста с варистером на входе и сглаживающим конденсатором на выходе позволили максимально расширить диапазон входных напряжений устройства и обеспечить возможность питания устройства от источников электроэнергии с выходным как переменным, так и постоянным напряжением, а также нечувствительность к переполюсовкам входного напряжения.

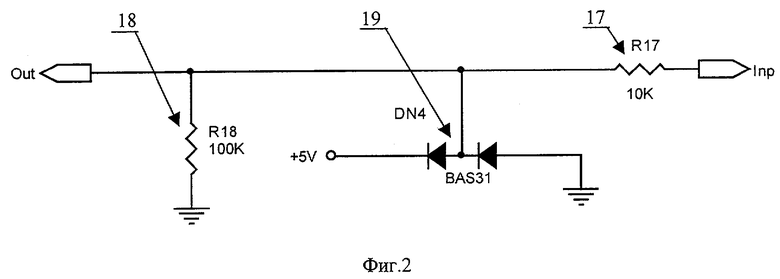

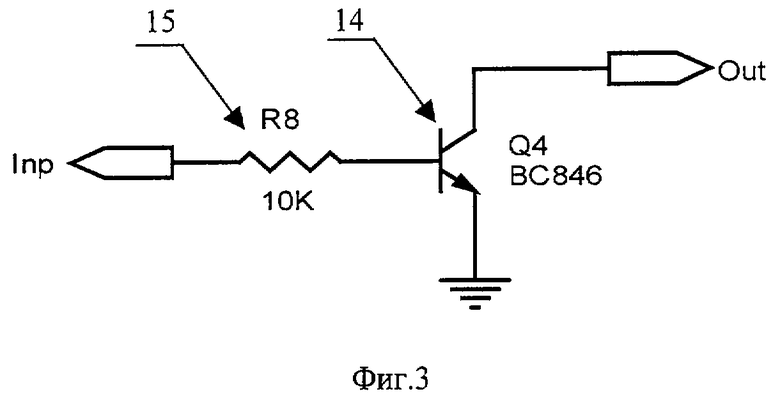

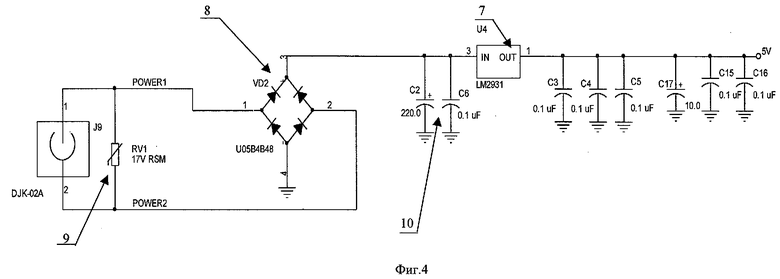

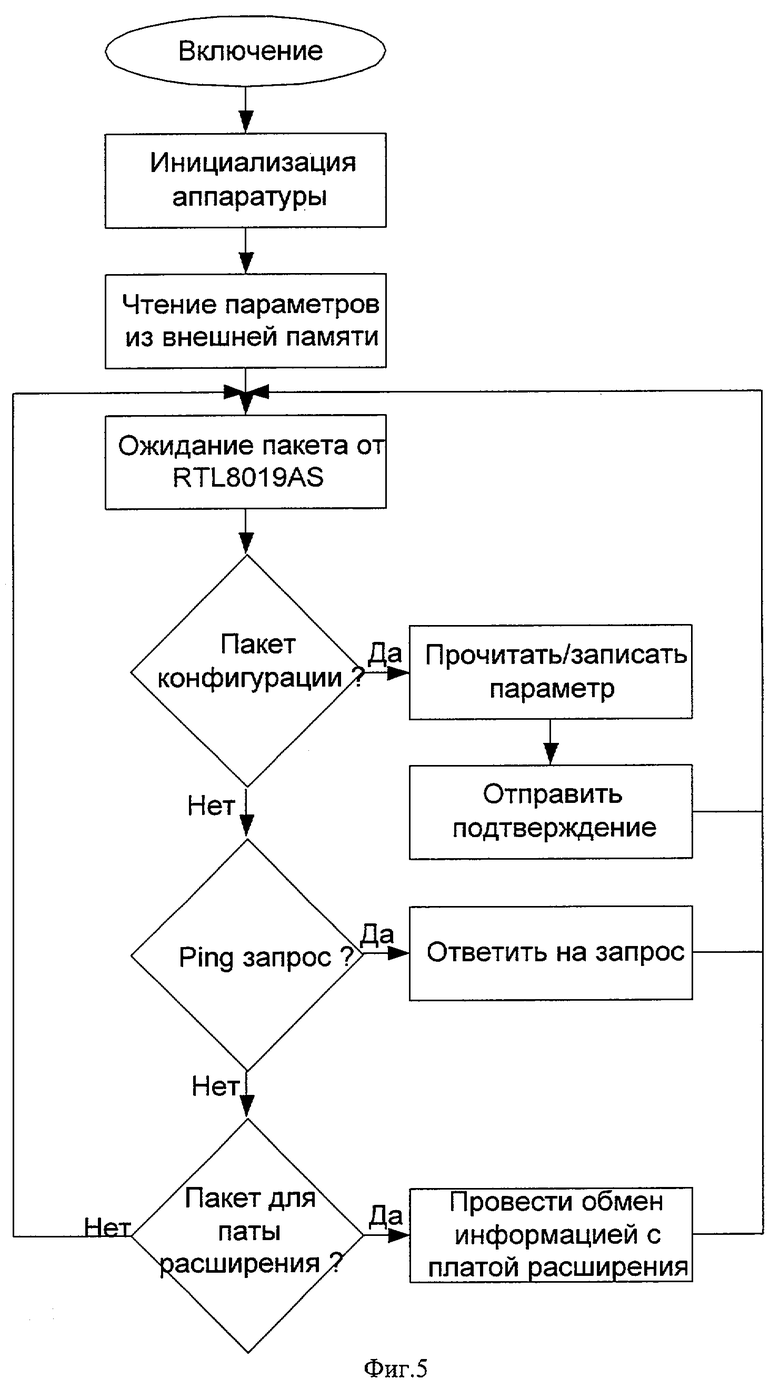

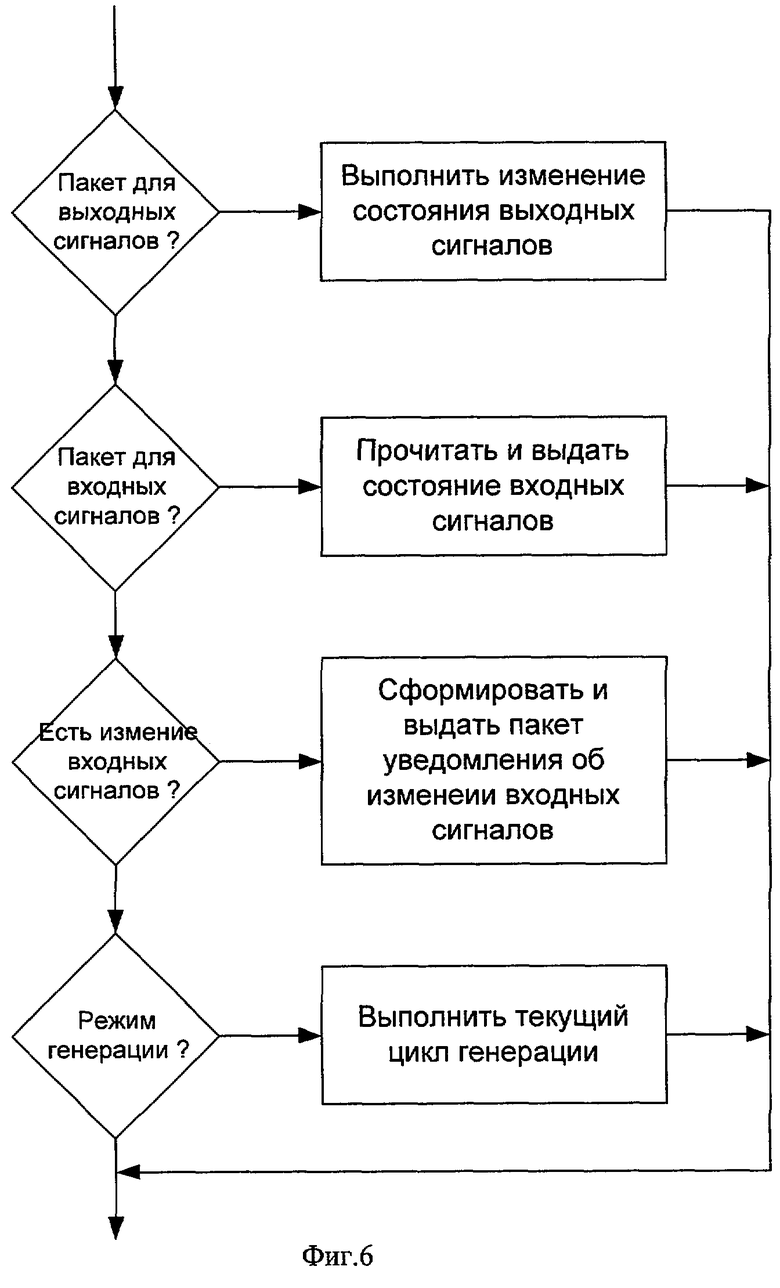

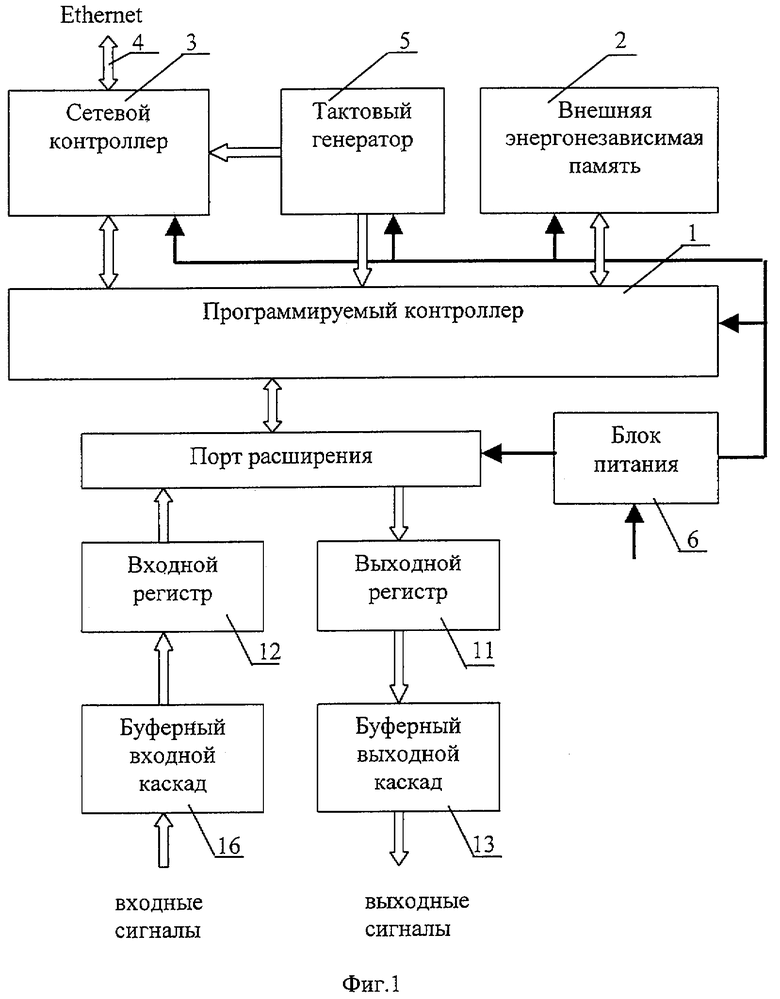

Сущность заявляемого изобретения поясняется чертежами, где на фиг.1 показана блок-схема устройства, на фиг.2 - возможный вариант принципиальной электрической схемы буферного входного каскада, на фиг.3 - возможный вариант принципиальной электрической схемы буферного выходного каскада, на фиг.4 - возможный вариант принципиальной электрической схемы блока питания, на фиг. 5 - алгоритм работы программируемого контроллера, а на фиг.6 - алгоритм процесса "провести обмен информацией с платой расширения".

Устройство проверки работоспособности сегментов локальной сети содержит программируемый контроллер 1 с интегрированным в его оперативной и постоянной памяти программным обеспечением функций сбора и обработки информации о периферийных устройствах сегмента. В таком качестве может быть применен микроконтроллер PIC16F876 фирмы Microchip с программным обеспечением, поддерживающим стек протоколов IP, ARQ, ICMP и SNMP. Все эти протоколы являются стандартными и описаны в документах RFC (серия документов IETF, начатая в 1969 году и содержащая описания набора протоколов Internet и связанную с ними информацию).

Для хранения таблиц настроек, а также временного хранения прошивок в процессе апгрейта версии программного обеспечения устройство содержит буферную память, выполненную в виде внешней энергонезависимой памяти 2 (например, на основе микросхемы 24LC128 фирмы Microchip), подключенной по последовательному интерфейсу (например, I2C) к программируемому контроллеру 1.

Устройство содержит сетевой контроллер 3 с интерфейсом 4 (например, соответствующий стандарту IEEE 802.3 и физической среде передачи 10Base-T) локальной сети (например, Ethernet, на черт. не показана). Сетевой контроллер 3 выполняет функции проверки корректности пакетов (сверяет контрольные суммы пакетов) и идентификации пакетов, поступающих в устройство, выделяя предназначенные устройству и отбрасывая все остальные. Сетевой контроллер может быть выполнен на основе стандартной микросхемы RTL8019AS фирмы фирмы Realtek.

Синхронизацию работы контроллеров в устройстве обеспечивает генератор 5 тактовой частоты (например, выполненный на кварцевом кристалле SS2 фирмы Jauch), подключенный как внешний генератор и к программируемому 1 и к сетевому 3 контроллерам.

Электроэнергия для работы устройства подается посредством блока 6 питания, выполненного в виде интегрального параметрического стабилизатора 7 питания (например, LM78L05 Series 3-Terminal Positive Regulators фирмы National) с выпрямителем на основе диодного моста 8 с варистером 9 на входе и сглаживающим конденсатором 10 на выходе.

Управляющую информацию для выходов программируемый контроллер 1 передает через выходной регистр 11, выполненный в виде сдвигового регистра на основе микросхемы с возможностью последовательной записи информации, а информацию с входов читает из входного регистра 12, выполненного в виде сдвигового регистра на основе микросхемы с возможностью параллельной записи информации. В указанном качестве выходным регистром могут быть регистры фирмы Philips 74HC595; 74НСТ595; 8-bit serial-in, serial or parallel-out shift register with output latches; 3-state, а входным регистром - регистр фирмы Philips 74HC/HCT597; 8-bit shift register with input flip-flops.

Устройство снабжено буферным выходным каскадом 13 силовых выходов для подключения внешнего оборудования к локальной сети, выходной ключ которого собран по схеме включения транзистора 14 с «общим эмиттером» и токоограничивающим резистором 15. Управляющая информация поступает в каскад 13 от выходного регистра 11, при этом все выходные сигналы с целью уменьшения стоимости и габаритов не являются гальванически развязанными.

Устройство снабжено буферным входным каскадом 16 ввода для подключения внешнего оборудования к локальной сети. Схемотехническое решение входного каскада с токоограничивающим резистором 17, нагрузочным резистором 18 и диодной сборкой 19 позволяет максимально расширить диапазон входных сигналов, защитить вход входного регистра и подавить помехи, наводимые на неподключенный вход устройства. Управляющая информация поступает из каскада 16 во входной регистр 12, при этом все выходные сигналы с целью уменьшения стоимости и габаритов также не являются гальванически развязанными.

Конструктивно входной 12 и выходной 11 регистры могут состоять из 8-ми идентичных блоков (по одному блоку на каждый дискретный вход-выход). Данная особенность в сочетании со схемотехническим решением буферных входных 16 и выходных 13 каскадов обеспечивает возможность наращивания количества дискретных входов-выходов простым увеличением количества входных 12 и выходных 11 регистров, включая их каскадно друг за другом, без каких-либо других изменений в структуре устройства.

Устройство поддерживает различные режимы управления цифровыми входами/выходами, что позволяет строить различные конфигурации систем управления и сканирования входных сигналов. Для того чтобы не привязываться к конкретному логическому уровню ключа буферного выходного каскада 13 вводится понятие активного и неактивного состояния. Неактивным считается состояние ключа при включении устройства. Если нужно проинвертировать выходной сигнал, достаточно просто изменить состояние сигнала при включении.

В частности, для перевода выходного сигнала в требуемое состояние по кадру управления по SNMP протоколу любой из выходных сигналов устройства может быть установлен или сброшен соответствующим битом в байте состояния выходов. Установленное состояние будет запоминаться в энергонезависимой памяти 2 устройства и восстанавливаться при включении устройства. Перевод любого из выходных сигналов в активное состояние осуществляется вне зависимости от предыдущего состояния сигнала и режима работы выхода каскада 13. Эта операция не влияет на состояние выходов при включении устройства. Перевод любого из выходных сигналов в неактивное состояние также осуществляется вне зависимости от предыдущего состояния сигнала и режима работы выхода каскада 11 и не влияет на состояние выходов при включении устройства. Для перевода любого из выходных сигналов в режим генерации можно задать различные частоты и скважности прямоугольных импульсов при помощи регистров значения времени активности и регистра значения времени неактивности выходного сигнала программируемого контроллера 1. Аналогичным образом осуществляется перевод любого из выходных сигналов в режим выдачи одиночного импульса с устанавливаемой длительностью.

Входные сигналы помимо отображения текущего состояния могут быть переведены в режим выдачи TRAP сообщения при изменении состояния. С этой целью вход через входной регистр 12 может быть запрограммирован для посылки TRAP сообщения как при переходе с активного состояния в неактивное, так и наоборот, а также для обоих случаев. Передача TRAP-сообщения будет происходить до тех пор, пока удаленный хост не подтвердить прием данного TRAP-сообщения, путем записи соответствующей маски в входной регистр 12. При необходимости управления исполнительным оборудованием выходы устройства через буферный выходной каскад 13 устанавливаются в неактивное состояние при включении устройства, а для включения оборудования сигнал удаленно переводится в активное состояние. В этом случае чтение входного регистра 12 дает информацию об успешности/неуспешности выполнения команды.

Для сброса оборудования выход устройства конфигурируется как выход с активным уровнем сигнала сброса и режимом работы с выдачей одиночного импульса. При необходимости выдачи сигнала сброса, выдается кадр управления, по приходу которого устройство формирует сигнал сброса установленной длительности. Таким образом, можно сбрасывать сетевое оборудование, от которого зависит связь с самим устройством.

Если подключить вход устройства к сигналу сброса (либо к другому цифровому выходу внутри сбрасываемого оборудования), то запрограммировав вход для выдачи TRAP-сообщения при переходе в активное состояние устройство будет автоматически высылать уведомление об окончании сброса оборудования. Если необходим множественный сброс оборудования, выход можно перевести в режим генерации (сигнала сброса), а по приходу TRAP-сообщения об окончании сброса выключать этот режим кадром, а до тех пор, пока TRAP-сообщение не подтверждено и режим генерации не выключен, устройство будет выдавать периодические сигналы сброса оборудованию.

Устройство автоматически формирует сигналы сброса, когда связь с хостом потеряна. Выход устройства переводится в режим генерации с длительностью активного уровня, равной желаемой длительности сигнала сброса, и длительностью неактивного уровня, равной времени для проверки наличия связи. После чего при включении устройство выдаст сигнал сброса хабу, затем если в течение времени неактивности сигнала сброса придет команда очистки внутреннего таймера, сброс не будет выполнен, если такая команда не придет, это означает, что связь потеряна и устройство выполнит сброс хаба и будет повторять операцию сброса один раз за время неактивности сигнала до тех пор пока связь не будет восстановлена.

При необходимости можно подключить входной сигнал к сигналу сброса и настроить его на автоматическую пересылку TRAP-сообщения про сигнал сброса. К устройству можно подключить несколько независимых шлейфов сигнализации, настроив каждый из них на посылку TRAP-сообщения в случае обрыва, а также при необходимости и в случае восстановления шлейфа. Также возможен режим автоматической передачи TRAP-сообщений о целостности шлейфа. Для этого необходимо перевести выходной сигнал в режим генерации, при каждом изменении состояния будет посылаться TRAP-сообщение о том, что шлейф не поврежден.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА АВТОМАТИЧЕСКОГО КОНТРОЛЯ КОТЕЛЬНОЙ | 2017 |

|

RU2656670C1 |

| УПРАВЛЯЮЩАЯ ЭВМ | 2005 |

|

RU2316807C2 |

| УДАЛЕННАЯ СИСТЕМА СБОРА И ОБРАБОТКИ ДАННЫХ ДЛЯ БОРТОВОЙ РЕГИСТРИРУЮЩЕЙ АППАРАТУРЫ | 2012 |

|

RU2493592C1 |

| БЛОК ИНТЕРФЕЙСНЫЙ | 2007 |

|

RU2363980C2 |

| УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ И ДОСТУПА К КАНАЛУ ДЛЯ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ | 1992 |

|

RU2060539C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ СОПРЯЖЕНИЕМ АБОНЕНТОВ | 1993 |

|

RU2037196C1 |

| Реконфигурируемый вычислительный модуль | 2018 |

|

RU2686017C1 |

| УПРАВЛЕНИЕ ЦИФРОВОЙ И АНАЛОГОВОЙ МОЩНОСТЬЮ ТЕРМИНАЛА ДОСТУПА OFDMA/CDMA | 2008 |

|

RU2433533C2 |

| АРХИТЕКТУРА ПРОЦЕССОРА ВВОДА-ВЫВОДА, КОТОРЫЙ ОБЪЕДИНЯЕТ МОСТ МЕЖСОЕДИНЕНИЯ ПЕРВИЧНЫХ КОМПОНЕНТ | 1996 |

|

RU2157000C2 |

| КОМПЛЕКС ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ АВТОМАТИЗАЦИИ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2004 |

|

RU2279117C2 |

Изобретение относится к цифровой вычислительной технике, в частности к средствам контроля и поиска неисправностей в устройствах с дискретным характером функционирования. Техническим результатом является обеспечение возможности применения устройства в случаях, когда требуется взаимодействие неспециализированных устройств, датчиков и исполнительных механизмов с дискретными интерфейсами управления. Для этого устройство содержит программируемый контроллер с интегрированным в оперативной и постоянной памяти программным обеспечением функций сбора и обработки информации о периферийных устройствах сегмента, буферную память, выходной регистр, входной регистр, генератор тактовой частоты, блок питания, буферный выходной каскад силовых выходов и буферный входной каскад ввода. 3 з.п. ф-лы, 6 ил.

| US 5919250 A, 06.07.1999.RU 2060539 C1, 20.05.1995.RU 2127447 C1, 10.03.1999.US 6192422 B1, 20.02.2001.WO 99/14902 A1, 25.03.1999. |

Авторы

Даты

2005-10-27—Публикация

2003-11-04—Подача