Изобретение относится к области вычислительной техники и предназначено для использования в составе автотранспортных средств (АТС) с электронными системами управления двигателями (ЭСУД) уровня Евро-4, и может быть установлено в магистральных автопоездах и автобусах производства Республиканского унитарного предприятия (РУП) «МАЗ», автозаводов России и республики Беларусь.

Известен программируемый логический контроллер (см. пат. РФ №2101757, МПК 6 G06F 9/00, опубл. 10.01.1998 г., по заявке №95120422/09 от 01.12.1995 г., патентообладатель Научно-исследовательский институт системных исследований РАН), содержащий микропроцессор, локальную шину, двухпортовое статическое ОЗУ, интерфейс шины VME, интерфейс шины ISA, ПЗУ, электрически программируемую постоянную память EEPROM, часы реального времени, контроллер клавиатуры, системный контроллер, универсальный программируемый сторожевой таймер, интерфейсы последовательных каналов RS232 и RS485, периферийную шину, интерфейс шины субмодулей, буферные усилители адреса и приемники/передатчики данных шины субмодулей, буферные усилители и приемники/передатчики данных ОЗУ, приемники/передатчики адреса и приемники/передатчики данных интерфейса шины VME, буферные усилители адреса и приемники/передатчики данных интерфейса шины ISA, буферные усилители адреса и приемники/передатчики данных периферийной шины.

Признаки аналога, совпадающие с признаками заявляемого изобретения, следующие: ПЗУ, локальная шина, электрически программируемая постоянная память EEPROM, часы реального времени.

Причиной, препятствующей достижению заявляемого технического результата, является то, что данный программируемый логический контроллер не предназначен для работы в составе АТС, так как не поддерживает цифровой мультиплексный информационный канал (ЦМИК) CAN2.0, что не позволяет обеспечить взаимодействие ЭСУД с органами управления, датчиками и электронными системами автомобиля.

Известен программируемый логический контроллер с интерфейсом последовательной передачи данных в двух стандартах (см. заявку РФ №2003115922/09 от 27.05.2003 г., МПК 7 G06F 9/00, G06F 13/00, опубл. 27.11.2004 г., заявитель Бабанин В.Б.), содержащий набор буферных элементов с преобразователем постоянного напряжения в двухполярное, микроконтроллер и коммутатор выводов микроконтроллера, имеющих альтернативные функции внутрисхемного программирования, схему распознавания протокола передачи на основе интегратора с двумя постоянными времени интегрирования, вход которой соединен с линией принимаемых микроконтроллером данных, а выход подключен к входу управления коммутатором и входу RESET микроконтроллера, дополнительно содержит супервизор питания, причем в режиме программирования коммутатор подключает выводы микроконтроллера к сигналам интерфейса последовательной передачи данных, а в режиме обмена данными (автономном) - к устройствам контроля и/или управления.

Признак аналога, совпадающий с признаком заявляемого изобретения, следующий: супервизор питания.

Причиной, препятствующей достижению заявляемого технического результата, является то, что программируемый логический контроллер не предназначен для работы в АТС, так как не поддерживает ЦМИК CAN2.0, что не может обеспечить взаимодействие работы ЭСУЭД с органами управления, датчиками и электронными системами автомобиля.

Наиболее близким аналогом к заявляемому изобретению является блок формирования управляющих сигналов (БФУС) (см. патент на полезную модель №53030 РФ, МПК G06F 9/00 (2006.01), опубл. 27.04.2006 г., по заявке №2006102082/22, патентообладатель Научно-исследовательский институт многопроцессорных вычислительных систем Таганрогского государственного радиотехнического университета (НИИ МВС ТРТУ) (RU)), содержащий микроконтроллер, соединенный с мультиплексированной шиной адрес/данные, с блоком оперативного запоминающего устройства (ОЗУ), сетевыми контроллерами, блоком временного хранения адреса и данных, который демультиплексирует ее и соединен с блоком ОЗУ и блоками сетевых контроллеров шиной адреса и по линиям управляющих сигналов и адрес/данные образует интерфейс подключения модулей ввода/вывода, а блок анализа ошибок связан с микроконтроллером посредством линий диагностики микроконтроллера, а также линиями диагностики дополнительных БФУС, подключенными через блок гальванической развязки сигналов БФУС, и линией сигнала ошибки модулей ввода/вывода, кроме того, микроконтроллер подключен к интерфейсу CAN №1 через блок гальваноразвязки CAN №1 и блок приемопередатчика CAN №2, к интерфейсу SSI через блок гальваноразвязки RS-485 №1, блок приемника CLK RS-485 №1 по линиям приема/передачи данных интерфейсов CAN №1, CAN №2 и SSI соответственно, а сетевые контроллеры соединены через блоки гальваноразвязок Ethernet №1 и Ethernet №2 по линиям приема/передачи с соответствующими интерфейсами Ethernet, причем блок временного хранения адреса и данных по линиям адрес/данные модулей ввода/вывода, а также по линиям управляющих сигналов и по линиям диагностики модулей ввода/вывода образует интерфейс для подключения модулей ввода/вывода.

Признаки аналога, совпадающие с признаками заявляемого изобретения, следующие: два приемопередатчика интерфейса CAN.

Причиной, препятствующей достижению заявляемого технического результата, является то, что блок формирования управляющих сигналов не предназначен для работы в составе АТС, так как не имеет входов для подключения дискретных и аналоговых датчиков, выходов для управления контрольными лампами и стрелочными указателями панели приборов АТС, что не обеспечивает взаимодействия ЭСУД с органами управления, датчиками и электронными системами автомобиля.

Задача, на решение которой направлено заявляемое техническое решение, заключается в создании блока интерфейсного для использования его в составе АТС и предназначенного для обеспечения взаимодействия электронных блоков управления двигателями уровня Евро-4 с органами управления, датчиками, устройствами индикации и другими электронными системами АТС.

Технический результат, обеспечиваемый при реализации заявляемого технического решения, заключается в следующем:

- контроль состояния датчиков и органов управления двигателем за счет буферных каскадов дискретных входов для подключения дискретных датчиков с коммутацией на массу, буферных каскадов дискретных входов для подключения дискретных датчиков с коммутацией на питание, буферных каскадов входов для подключения частотных датчиков, буферных каскадов входов для подключения аналоговых датчиков и буферных каскадов входов для подключения резистивных датчиков;

- управление приборами и контрольными лампами, отображающими параметры работы двигателя в соответствии с информацией, полученной от ЭСУД, осуществляется через электронные интеллектуальные ключи дискретных выходов с коммутацией на массу и с коммутацией на питание, от электронных интеллектуальных ключей дискретных выходов с коммутацией на массу и с коммутацией на питание в блок вычислительный передается диагностическая информация о состоянии подключенных нагрузок (обрыв, короткое замыкание);

- обмен данными с электронными системами по ЦМИК CAN 2.0 (в соответствии с протоколом SAE J 1939) и J 1708.

Указанный технический результат при осуществлении изобретения достигается тем, что в блок интерфейсный, содержащий два приемопередатчика интерфейса CAN, дополнительно введены часы реального времени, супервизор питания, энергонезависимое перепрограммируемое постоянное запоминающее устройство (ЭНППЗУ), р буферных каскадов с входами для подключения дискретных датчиков с коммутацией на питание, q буферных каскадов с входами для подключения дискретных датчиков с коммутацией на массу, г буферных каскадов с входами для подключения частотных датчиков, генератор, k приемопередатчиков интерфейса CAN, технологический канал, n приемопередатчиков интерфейса J1708, w приемопередатчиков диагностического интерфейса ISO 9141, t буферных каскадов с входами для подключения аналоговых датчиков, s буферных каскадов с входами для подключения резистивных датчиков, d электронных интеллектуальных ключей с дискретными выходами с коммутацией на массу, m электронных интеллектуальных ключей с дискретными выходами с коммутацией на питание, формирователь питающего напряжения с выходом ошибки, выходом для питания аналоговых датчиков и входом включения, схема защиты, промежуточный преобразователь напряжения, линейный стабилизатор напряжения, блок вычислительный, содержащий соединенные через локальную шину арифметико-логическое устройство (АЛУ), постоянно-запоминающее устройство (ПЗУ), устройство ввода-вывода, контроллеры CAN, UART 1, UART 0, UART 2, аналого-цифровой преобразователь (АЦП) и оперативное запоминающее устройство (ОЗУ), причем входы устройства ввода-вывода блока вычислительного соединены с соответствующими выходами q буферных каскадов с входами для подключения дискретных датчиков с коммутацией на массу, r буферных каскадов с входами для подключения частотных датчиков, р буферных каскадов с входами для подключения дискретных датчиков с коммутацией на питание и с выходом ошибки формирователя питающего напряжения, выходы устройства ввода-вывода блока вычислительного соединены с соответствующими входами m электронных интеллектуальных ключей с дискретными выходами с коммутацией на питание, входом формирователя питающего напряжения с выходом для питания аналоговых датчиков и входом промежуточного преобразователя напряжения, входы-выходы устройства ввода-вывода блока вычислительного через последовательный интерфейс I2C соединены с часами реального времени, супервизором питания, ЭНППЗУ и через последовательный интерфейс SPI с соответствующими входами-выходами d электронных интеллектуальных ключей с дискретными выходами с коммутацией на массу, входы АЦП блока вычислительного соединены с соответствующими выходами t буферных каскадов с входами для подключения аналоговых датчиков, s буферных каскадов с входами для подключения резистивных датчиков, входы-выходы контроллеров CAN, UART 0, UART 2 блока вычислительного соединены с соответствующими входами-выходами k приемопередатчиков интерфейса CAN, n приемопередатчиков интерфейса J 1708 и w приемопередатчиков диагностического интерфейса ISO 9141, вход-выход контроллера UART 1 блока вычислительного соединен с технологическим каналом, входы АЛУ блока вычислительного соединены соответственно с выходом супервизора питания и выходом генератора, вход промежуточного преобразователя напряжения соединен со схемой защиты, выход - с линейным стабилизатором напряжения, один из входов для подключения дискретных датчиков с коммутацией на питание соединен с промежуточным преобразователем напряжения, схема защиты соединена с шиной питания.

Предельные значения k, d, m, n, w, p, q, r, s, t находятся в следующем диапазоне: k=(1, 2,…4), d=(1, 2…12),m=(1, 2…35), n=(0, 1), w=(0, 1), p=(1, 2…40), q=(1, 2…16), r=(1, 2…4), s=(1, 2, 3), t=(1, 2, 3).

В блоке вычислительном входы АЛУ и входы АЦП являются соответственно входами блока вычислительного, входы устройства ввода-вывода и выходы устройства ввода-вывода являются соответственно входами и выходами блока вычислительного, входы-выходы устройства ввода-вывода и входы-выходы контроллеров CAN, UART I, UART 0, UART 2 являются соответственно входами-выходами блока вычислительного.

Поскольку блок интерфейсный предназначен для работы в составе различных типов АТС, то количество некоторых буферных каскадов и электронных интеллектуальных ключей блока интерфейсного зависит от количества датчиков, контрольных ламп и стрелочных приборов, установленных на данном типе АТС.

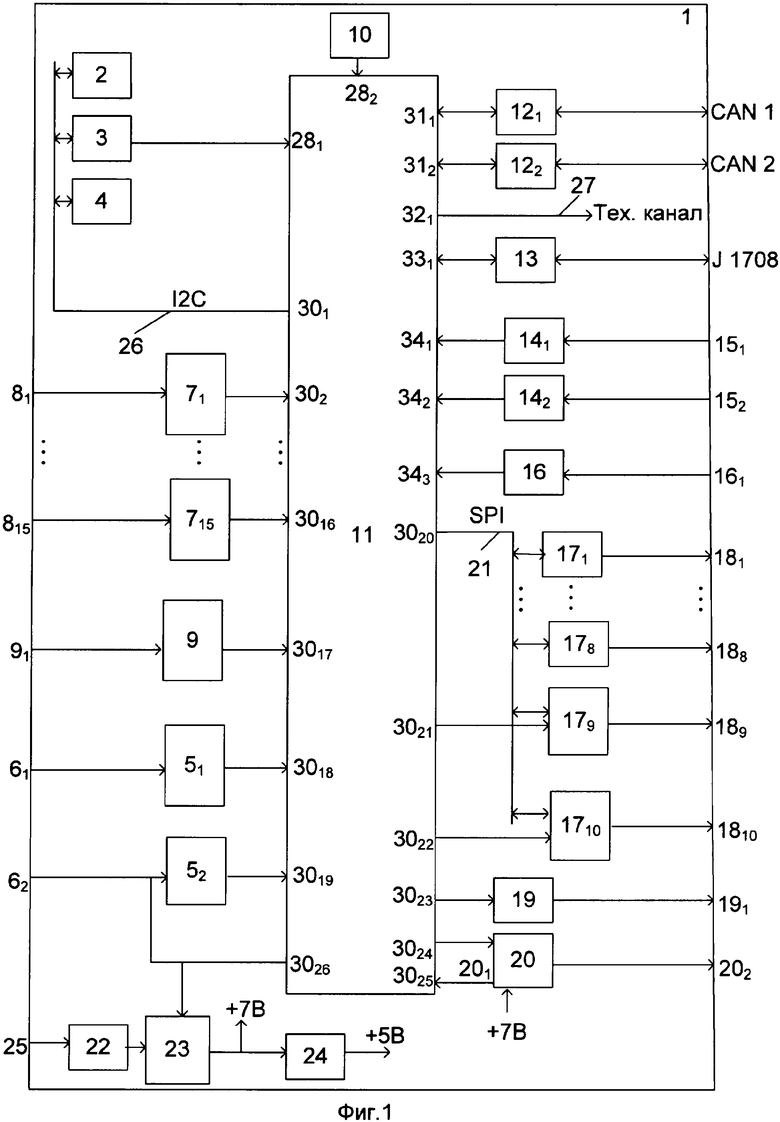

Один из вариантов исполнения структурной схемы блока интерфейсного для системы управления двигателем Deutz представлен на фиг.1 в качестве примера, для случая, когда k=2, t=2, s=1, r=1, q=15, p=2, d=10, m=1, n=1, w=0. На фиг.2 показана схема блока вычислительного. На фиг.3 показана примерная схема подключения блока интерфейсного в АТС.

Блок интерфейсный 1 (фиг.1) включает в себя часы реального времени 2, супервизор питания 3, ЭНППЗУ 4, буферные каскады 51, 52 с входами 61, 62 для подключения дискретных датчиков с коммутацией на питание, буферные каскады 71-715 с входами 81-815 для подключения дискретных датчиков с коммутацией на массу, буферный каскад 9 с входом 91 для подключения частотного датчика, генератор 10, блок вычислительный 11, приемопередатчики интерфейса CAN 121, 122, приемопередатчик интерфейса J 1708 13, буферные каскады 141, 142 с входами 151, 152 для подключения аналоговых датчиков, буферный каскад 16 с входом 161 для подключения резистивного датчика, электронные интеллектуальные ключи 171-1710 с дискретными выходами 181-1810 с коммутацией на массу, причем дискретные выходы 189-1810 с коммутацией на массу предназначены для подключения стрелочных указателей, электронный интеллектуальный ключ 19 с дискретным выходом 191 с коммутацией на питание, формирователь питающего напряжения 20 с выходом 201 ошибки, выходом

202 для питания аналоговых датчиков и входом 203 включения, интерфейс SPI 21, схему защиты 22, выход которой соединен с промежуточным преобразователем напряжения 23, выход которого соединен с линейным стабилизатором напряжения 24, шину питания 25, соединенную со схемой защиты 22, интерфейс I2C 26, технологический канал 27, вход 62 для подключения дискретных датчиков с коммутацией на питание, соединенный с промежуточным преобразователем напряжения 23, причем блок вычислительный 11 (фиг.2) содержит: АЛУ 28, ПЗУ 29, устройство ввода-вывода 30, контроллеры: CAN 31, UART 1 32, UART 0 33, АЦП 34, ОЗУ 35, которые соединены через локальную шину 36, причем входы 281, 282 АЛУ 28 являются соответствующими входами блока вычислительного 11 и соединены соответственно с выходом супервизора питания 3 и выходом генератора 10, входы 302-3016, 3017, 3018, 3019, 3025 устройства ввода-вывода 30 являются соответствующими входами блока вычислительного 11 и соединены соответственно с выходами буферных каскадов 71-715, с выходом буферного каскада 9, с выходами буферных каскадов 51-52 и с выходом формирователя питающего напряжения 20, выходы 3021, 3022, 3023, 3024, 3026 устройства ввода-вывода 30 являются соответствующими выходами блока вычислительного 11 и соединены соответственно со входами электронных интеллектуальных ключей 179, 1710, со входом электронного интеллектуального ключа 19, со входом формирователя питающего напряжения 20 и со входом промежуточного преобразователя напряжения 23, вход-выход 301 устройства ввода-вывода 30 является соответствующим входом-выходом блока вычислительного 11 и соединен через последовательный интерфейс I2C 26 с ЭНППЗУ 4, супервизором питания 3, часами реального времени 2, вход-выход 3020 устройства ввода-вывода 30 является соответствующим входом-выходом блока вычислительного 11 и является последовательным интерфейсом SPI 21, который используется для связи с электронными интеллектуальными ключами 171-1710, входы-выходы 311, 312 контроллера CAN 27 являются соответствующими входами-выходами блока вычислительного 11 и соединены соответственно с приемопередатчиками интерфейса CAN 121, 122, вход-выход 321 контроллера UART 1 32 является соответствующим входом-выходом блока вычислительного 11, соединенный с технологическим каналом 27, вход-выход 331 контроллера UART 0 33 является соответствующим входом-выходом блока вычислительного 11, соединенный с приемопередатчиком интерфейса J 1708 13, входы 341, 342, 343 АЦП 34 являются соответствующими входами блока вычислительного 11, соединенные с соответственными выходами буферных каскадов 141, 142 и выходом буферного каскада 16.

Напряжение питания бортовой сети АТС (на чертеже не показано) подается на схему защиты 22, которая предназначена для защиты от кондуктивных помех бортовой сети АТС. С выхода схемы защиты 22 напряжение питания поступает на промежуточный преобразователь напряжения 23, на выходе которого формируется стабилизированное напряжение 7 В. Включение промежуточного преобразователя напряжения 23 осуществляется сигналом со входа 62 для подключения дискретного датчика с коммутацией на питание (фиг.1), а также сигналом от блока вычислительного 11.

Питание цифровых и аналоговых цепей блока интерфейсного 1 осуществляется напряжением 5 В, которое формируется на выходе линейного стабилизатора напряжения 24.

Напряжение питания аналоговых датчиков (5±0,25) В (фиг.3) формируется на выходе 202 для питания аналоговых датчиков формирователя питающего напряжения 20. Данный формирователь питающего напряжения 20 имеет защиту от короткого замыкания выхода на массу и на положительную шину питания бортовой сети АТС. Управление включением формирователя питающего напряжения 20 осуществляется через вход 203 включения сигналом от блока вычислительного 11 через выход 3024. Выход 201 ошибки формирователя питающего напряжения 20 подключен к входу 3025 блока вычислительного 11.

Супервизор питания 3 вырабатывает сигнал сброса для блока вычислительного 11.

Генератор 10 формирует тактовую частоту для блока вычислительного 11. Буферные каскады 71-715 с входами 81-815 для подключения дискретных датчиков с коммутацией на массу и буферные каскады 51-52 с входами 61, 62 для подключения дискретных датчиков с коммутацией на питание предназначены для преобразования логических уровней входных сигналов от датчиков, установленных на АТС (фиг.3), в логические уровни ТТЛ для подключения к блоку вычислительному 11. Сигнал скорости, например, от тахографа АТС (фиг.3) подается на вход 91 для подключения частотного датчика блока интерфейсного 1, предназначенный для преобразования логических уровней сигнала скорости (0-8 В) в уровни ТТЛ, и через буферный каскад 9 на вход 3017 блока вычислительного 11.

Сигналы аналоговых датчиков и сигнал резистивного датчика АТС (фиг.3) поступают на входы 341, 342, 343 АЦП 30 (фиг.1, 2), являющиеся входами блока вычислительного 11 через входы 151, 152 для подключения аналоговых датчиков буферных каскадов 141, 142 и через вход 161 для подключения резистивного датчика буферного каскада 16 соответственно.

Электронные интеллектуальные ключи 171-1710 выполнены на базе микросхем интеллектуальных электронных ключей TLE6232GP. Управление дискретными выходами 181-1810 с коммутацией на массу осуществляется блоком вычислительным 11 через электронные интеллектуальные ключи с коммутацией на массу по последовательному интерфейсу SPI 21 (фиг.1). Дискретные выходы 181-188 с коммутацией на массу предназначены для подключения контрольных ламп (фиг.3). Управление дискретными выходами 189-1810 с коммутацией на массу для подключения стрелочных указателей (фиг.3) осуществляется блоком вычислительным 11 через электронные интеллектуальные ключи 179-1710 сигналами с широтно-импульсной модуляцией через выходы 3121, 3122 (фиг.1). Управление дискретным выходом 191 с коммутацией на питание осуществляется блоком вычислительным 11 через интеллектуальный электронный ключ 19. От электронных интеллектуальных ключей 171-1710 и интеллектуального электронного ключа 19 в блок вычислительный 11 передается диагностическая информация о состоянии подключенных нагрузок (обрыв, короткое замыкание).

Сохранение конфигурационной информации и истории событий осуществляется в ЭНППЗУ 4. Обмен данными между блоком вычислительным 11 и ЭНППЗУ 4 осуществляется по последовательному интерфейсу I2C 26.

Физические уровни цифровых последовательных интерфейсов (ЦМИК) CAN 1, CAN 2 реализованы на приемопередатчиках интерфейса CAN 121, 122. Физический уровень ЦМИК J 1708 реализован на приемопередатчике интерфейса J 1708 13.

Загрузка программного обеспечения в энергонезависимую память блока вычислительного 11 осуществляется по последовательному технологическому каналу 27, подключенному к контроллеру UART 1 32.

Блок вычислительный 11 может быть выполнен на основе микроконтроллера MB90F543PF фирмы Fujitsu.

Эксплуатация блока интерфейсного в составе АТС с двигателем Deutz уровня Евро-4 показала надежную работу блока интерфейсного в различных режимах работы: управление контрольными приборами двигателя, старт двигателя (включение питания электронного блока двигателя, включение реле стартера), работа двигателя под нагрузкой (передача двигателю информации о положении педали акселератора), управление двигателем в режиме круиз-контроля (передача электронному блоку двигателя команд коррекции крутящего момента), выключение двигателя (передача команды на выключение двигателя, выключение питания электронного блока двигателя). При этом блок интерфейсный разработан с учетом требований ГОСТ Р 50905-96 «Автотранспортные средства. Электронное оснащение. Общие технические требования», ГОСТ Р 52230-2004 «Электрооборудование автотракторное. Общие технические условия» и обеспечивает надежное функционирование в указанных режимах при условиях эксплуатации, соответствующих требованиям, предъявляемым к АТС.

Таким образом, из рассмотренного материала видно, что заявляемое изобретение является новым, промышленно применимым и решает поставленную техническую задачу с заявленным техническим результатом.

| название | год | авторы | номер документа |

|---|---|---|---|

| АВТОМАТИЧЕСКАЯ НРЛС С УВЕЛИЧЕННЫМ НЕОБСЛУЖИВАЕМЫМ ПЕРИОДОМ АВТОНОМНОЙ РАБОТЫ | 2012 |

|

RU2522910C2 |

| Адаптивная система переднего освещения | 2020 |

|

RU2747225C1 |

| Промышленный контроллер | 2017 |

|

RU2642400C1 |

| КОМПЛЕКС ПРОГРАММНО-АППАРАТНЫХ СРЕДСТВ АВТОМАТИЗАЦИИ УПРАВЛЕНИЯ ТЕХНОЛОГИЧЕСКИМИ ПРОЦЕССАМИ | 2004 |

|

RU2279117C2 |

| БОРТОВАЯ ИНФОРМАЦИОННАЯ СИСТЕМА | 2009 |

|

RU2402439C1 |

| Способ потактового управления несколькими шаговыми двигателями с помощью персонального компьютера по каналу USB и устройство для его осуществления | 2018 |

|

RU2704486C1 |

| БЛОК АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ МАЛОГАБАРИТНЫЙ (БАР-М) | 2012 |

|

RU2487385C1 |

| ИНФОРМАЦИОННО-УПРАВЛЯЮЩИЙ КОМПЛЕКС АВТОМАТИЗИРОВАННОЙ СИСТЕМЫ УПРАВЛЕНИЯ ПОДГОТОВКОЙ ДВИГАТЕЛЬНЫХ УСТАНОВОК И ТЕХНОЛОГИЧЕСКИМ ОБОРУДОВАНИЕМ РАКЕТ КОСМИЧЕСКОГО НАЗНАЧЕНИЯ НА ТЕХНИЧЕСКОМ И СТАРТОВОМ КОМПЛЕКСАХ | 2015 |

|

RU2604362C1 |

| Плата-переходник для установки в базовые устройства с процессорным модулем форм-фактора COM EXPRESS | 2024 |

|

RU2838350C1 |

| БЛОК АВТОМАТИЧЕСКОГО РЕГУЛИРОВАНИЯ (БАР) | 2010 |

|

RU2457530C1 |

Изобретение относится к области вычислительной техники и предназначено для использования в составе автотранспортных средств (АТС). Технический результат заключается в создании блока интерфейсного для использования его в составе АТС и предназначенного для обеспечения взаимодействия электронных блоков управления двигателями уровня Евро-4 с органами управления, датчиками, устройствами индикации и другими электронными системами АТС. Он достигается тем, что блок интерфейсный включает в себя часы реального времени, супервизор питания, электрически независимое перепрограммируемое постоянное запоминающее устройство, буферные каскады с входами для подключения дискретных датчиков с коммутацией на питание, буферные каскады с входами для подключения дискретных датчиков с коммутацией на массу, буферный каскад с входом для подключения частотного датчика, генератор, блок вычислительный, приемопередатчики интерфейса CAN, приемопередатчик интерфейса J 1708, буферные каскады с входами для подключения аналоговых датчиков, буферный каскад с входом для подключения резистивного датчика, электронные интеллектуальные ключи с дискретными выходами с коммутацией на массу, электронный интеллектуальный ключ с дискретным выходом с коммутацией на питание, формирователь питающего напряжения с выходом ошибки, выходом для питания аналоговых датчиков и входом включения, интерфейс SPI, схему защиты, промежуточный преобразователь напряжения, линейный стабилизатор напряжения, шину питания, интерфейс I2C, технологический канал. 2 з.п. ф-лы, 3 ил.

1. Блок интерфейсный, предназначенный для обеспечения взаимодействия друг с другом электронных систем автотранспортных средств, содержащий два приемопередатчика интерфейса CAN, отличающийся тем, что в него дополнительно введены часы реального времени, супервизор питания, электрически независимое перепрограммируемое постоянное запоминающее устройство, p буферных каскадов с входами для подключения дискретных датчиков с коммутацией на питание, q буферных каскадов с входами для подключения дискретных датчиков с коммутацией на массу, r буферных каскадов с входами для подключения частотных датчиков, генератор, k приемопередатчиков интерфейса CAN, технологический канал, по которому загружают программное обеспечение вычислительного блока, n приемопередатчиков интерфейса J1708, w приемопередатчиков диагностического интерфейса ISO 9141, t буферных каскадов с входами для подключения аналоговых датчиков, s буферных каскадов с входами для подключения резистивных датчиков, d электронных интеллектуальных ключей с дискретными выходами с коммутацией на массу, m электронных интеллектуальных ключей с дискретными выходами с коммутацией на питание, формирователь питающего напряжения с выходом для питания аналоговых датчиков, выходом ошибки и входом включения, схема защиты, промежуточный преобразователь напряжения, линейный стабилизатор напряжения, блок вычислительный, содержащий соединенные через локальную шину арифметико-логическое устройство, постоянное запоминающее устройство, устройство ввода-вывода, контроллеры CAN, UART 1, UART 0, UART 2, аналого-цифровой преобразователь и оперативное запоминающее устройство, причем входы устройства ввода-вывода блока вычислительного соединены с соответствующими выходами q буферных каскадов с входами для подключения дискретных датчиков с коммутацией на массу, r буферных каскадов с входами для подключения частотных датчиков, p буферных каскадов с входами для подключения дискретных датчиков с коммутацией на питание и с выходом ошибки формирователя питающего напряжения, выходы устройства ввода-вывода блока вычислительного соединены с соответствующими входами m электронных интеллектуальных ключей с дискретными выходами с коммутацией на питание, входом включения формирователя питающего напряжения и входом промежуточного преобразователя напряжения, входы-выходы устройства ввода-вывода блока вычислительного через последовательный интерфейс I2C соединены с электрически независимым перепрограммируемым постоянным запоминающим устройством, часами реального времени, супервизором питания и через последовательный интерфейс SPI с соответствующими входами-выходами d электронных интеллектуальных ключей с дискретными выходами с коммутацией на массу, входы аналого-цифрового преобразователя блока вычислительного соединены с соответствующими выходами t буферных каскадов с входами для подключения аналоговых датчиков, s буферных каскадов с входами для подключения резистивных датчиков, входы-выходы контроллеров CAN, UART 0, UART 2 блока вычислительного соединены с соответствующими входами-выходами k приемопередатчиков интерфейса CAN, n приемопередатчиков интерфейса J1708 и w приемопередатчиков диагностического интерфейса ISO 9141, вход-выход контроллера UART 1 блока вычислительного соединен с технологическим каналом, входы арифметико-логического устройства блока вычислительного соединены соответственно с выходом супервизора питания и выходом генератора, вход промежуточного преобразователя напряжения соединен со схемой защиты, выход - с линейным стабилизатором напряжения, один из входов для подключения дискретных датчиков с коммутацией на питание соединен с промежуточным преобразователем напряжения, схема защиты соединена с шиной питания.

2. Блок интерфейсный по п.1, отличающийся тем, что предельные значения k, d, m, n, w, p, q, r, s, t находятся в следующем диапазоне: k=(1, 2, …4), d=(1, 2…12), m=(1, 2…35), n=(0, 1), w=(0, 1), p=(1, 2…40), q=(1, 2…16), r=(1, 2…4), s=(1, 2, 3), t=(1, 2, 3).

3. Блок интерфейсный по п.1, отличающийся тем, что в блоке вычислительном входы арифметико-логического устройства и входы аналого-цифрового преобразователя являются соответственно входами блока вычислительного, входы устройства ввода-вывода и выходы устройства ввода-вывода являются соответственно входами и выходами блока вычислительного, входы-выходы устройства ввода-вывода и входы-выходы контроллеров CAN, UART 1, UART 0, UART 2 являются соответственно входами-выходами блока вычислительного.

| Способ получения антималярийного средства | 1936 |

|

SU53030A1 |

| ПРОГРАММИРУЕМЫЙ ЛОГИЧЕСКИЙ КОНТРОЛЛЕР | 1995 |

|

RU2101757C1 |

| Предохранительное приспособление для круглых пил | 1934 |

|

SU41167A1 |

| US 2003084201 A1, 01.05.2003. | |||

Авторы

Даты

2009-08-10—Публикация

2007-05-07—Подача