Область техники, к которой относится изобретение

Настоящее изобретение относится к способу определения логического состояния выбранных ячеек памяти, имеющихся в запоминающем устройстве с пассивной матричной адресацией, содержащем управляющие линии (числовые шины) и линии данных (разрядные шины), в котором, в соответствии с заданным протоколом, определенным логическим состояниям приписаны уникальные логические значения и в котором ячейки памяти хранят данные в форме состояния электрической поляризации конденсатороподобных структур, содержащих поляризуемый материал, предпочтительно ферроэлектрический или электретный, способный проявлять гистерезис, а также сохранять неисчезающую электрическую поляризацию в отсутствие внешнего поля, приложенного к указанным конденсатороподобным структурам. Выбор ячеек производят путем активизации управляющей линии и/или линии данных, скрещивающихся на выбираемой ячейке, при этом активизацию управляющей линии или линии данных осуществляют путем приложения разности потенциалов между ними, с подачей таким образом на выбранные ячейки малосигнального зондирующего напряжения, обусловленного приложенной разностью потенциалов и обеспечивающего генерацию указанными ячейками токового отклика. Под малосигнальным зондирующим напряжением в контексте данной заявки понимается напряжение, подача которого на ячейку памяти приводит к формированию этой ячейкой токового отклика, пропорционального поданному напряжению, при сохранении неизменным направления поляризации в данной ячейке. Другими словами, значения амплитуды и/или длительности малосигнального зондирующего напряжения выбирают меньшими, чем значения, необходимые для создания существенных постоянных изменений состояний поляризации указанных ячеек. Данное малосигнальное зондирующее напряжение является изменяющимся во времени, тогда как указанное логическое состояние ячейки определяют путем детектирования в токовом отклике выбранной ячейки компонентов, коррелированных во времени с малосигнальным зондирующим напряжением или с опорными сигналами, сформированными из указанного напряжения, причем решение в отношении логического состояния выбранной ячейки принимают на основе сравнения указанного токового отклика с набором заданных критериев.

Уровень техники

В последние годы было продемонстрировано хранение данных в электрически поляризуемой среде, состоящей из тонких пленок. Особый интерес в этом отношении представляют собой электреты, а также керамические или полимерные ферроэлектрики. При их использовании логическое состояние индивидуальной ячейки памяти представляется направлением вектора поляризации тонкой ферроэлектрической пленки в этой ячейке. В случае ферроэлектриков данные записываются в ячейку за счет обеспечения поляризации пленки в желаемом направлении путем приложения соответственно ориентированного электрического поля, более интенсивного, чем коэрцитивное поле в ферроэлектрике. Главное достоинство таких материалов состоит в том, что они сохраняют свою поляризацию без постоянной подачи к ним электрической энергии, т.е. хранение данных является энергонезависимым.

Были созданы запоминающие устройства (устройства хранения данных), принадлежащие двум основным классам с фундаментальными различиями в архитектуре устройств.

В устройствах, принадлежащих к первому классу, каждая ячейка памяти имеет в своем составе, по меньшей мере, один транзистор. В целом архитектура памяти подобного вида соответствует типу активной матрицы. Ее главным достоинством по сравнению с традиционными устройствами типа SRAM и DRAM является энергонезависимость логического состояния, сохраняемого в ферроэлектрике. Необходимость в одном или более транзисторах в каждой ячейке представляет серьезный недостаток устройств подобного типа с точки зрения сложности и снижения плотности записи данных относительно общей площади устройства.

В устройствах, относящихся ко второму классу и представляющих особый интерес в контексте изобретения, ячейки памяти используются в пассивной матричной архитектуре, в соответствии с которой два набора взаимно ортогональных электродов формируют наборы конденсатороподобных структур в зонах скрещивания электродов. Каждый конденсатор образует ячейку памяти типа сэндвича с ферроэлектрической пленкой, заключенной между электродами.

В соответствии с уровнем техники запись в индивидуальные ячейки памяти или считывание данных из этих ячеек производится путем приложения к материалу каждой интересующей ячейки электрического поля, достаточного для того, чтобы преодолеть эффект гистерезиса и ориентировать электрическую поляризацию в ячейке в направлении электрического поля. Если материал уже был поляризован в этом направлении до приложения к нему поля, никакого инвертирования поляризации не происходит и через ячейку протекает только небольшой кратковременный ток. Однако, если материал был поляризован в противоположном направлении, имеет место инвертирование поляризации, что приводит к протеканию значительно большего кратковременного тока. Таким образом, логическое состояние, т.е. направление электрической поляризации в индивидуальной ячейке памяти, определяется путем приложения к ней электрического поля, напряженность которого достаточна для того, чтобы преодолеть коэрцитивное поле в ферроэлектрике, и детектирования результирующего тока.

По сравнению с устройствами на основе активной матрицы пассивные матричные устройства могут быть изготовлены с намного более высокой плотностью ячеек памяти; при этом сама матричная память является менее сложной. Однако известный процесс считывания из такой матрицы является деструктивным, т.е. приводящим к потере содержимого в ячейке, из которой производится считывание. Как следствие, данные, которые должны быть считаны, необходимо вновь записать в запоминающее устройство, если желательно продолжить сохранение данных. Более серьезным последствием переключения поляризации является усталость, т.е. постепенная потеря способности к переключению поляризации. Как правило, это явление сопровождается необходимостью приложения к ячейке более высокого напряжения для того, чтобы произошло инвертирование поляризации. Усталость ограничивает количество циклов считывания, которое может выдержать конкретная ячейка памяти. Тем самым ограничивается и диапазон применений. Кроме того, усталость приводит к замедлению отклика и к более высоким требованиям к устройству в отношении напряжения. Происходящее при этом постепенное изменение рабочих характеристик для индивидуальной ячейки памяти в конкретном устройстве только в редких случаях может быть предсказано априорно. Поэтому проектирование и эксплуатация должны вестись в расчете на "худший случай", что приводит к неоптимальным режимам.

Предпринимались попытки найти решения, позволяющие производить бездеструктивное считывание из памяти на основе ферроэлектрика при сохранении простой архитектуры ячейки памяти.

Так, Бреннан (С. J. Brennan) в патентах США №5343421; 5309390; 5262983; 5245568; 5151877 и 5140548 описывает ферроэлектрические конденсаторные ячейки и ассоциированные с ними элементарные модули считывания для устройств хранения данных. Путем зондирования емкости с помощью слабых сигналов при одновременном приложении к ферроэлектрику умеренных полей смещения, т.е. полей, которые не приводят к созданию на ячейке памяти во время считывания пиковых напряжений, превосходящих коэрцитивное поле в ферроэлектрике, производится определение направления спонтанной поляризации в конденсаторе и, как следствие, логического состояния ячейки памяти. Однако для практического применения способов и устройств, описанных в перечисленных патентах, необходимо выполнение весьма специфичных условий, приводящих к явлениям, связанным с накоплением на электродах пространственного заряда. Эти явления непосредственно зависят от материалов, используемых в электродах, а также от примыкающего к ним ферроэлектрика. Считывание данных связано с оценкой пространственного заряда, которая может быть получена в шкале времени, совместимой с указанным накоплением заряда. Кроме того, в перечисленных патентах не объяснено, каким образом следует осуществлять распределение во времени и корреляцию малого сигнала и напряжений смещения относительно друг друга, что имеет первостепенное значение для применения в реальных условиях. Не объяснено также, каким образом можно разместить и адресовать ячейки памяти в крупных матрицах с обеспечением эффективных операций считывания и записи.

В международной патентной заявке № PCT/NО01/00472, принадлежащей заявителю настоящего изобретения, раскрыт способ, обеспечивающий бездеструктивное считывание, и устройство для его осуществления применительно к запоминающим устройствам на основе тонкопленочных ферроэлектрических конденсаторов. Считывание осуществляется путем приложения к ячейке памяти комбинации изменяющихся во времени напряжений, вызывающих токовый отклик в режиме слабых сигналов (малосигнальный токовый отклик) с линейными и нелинейными компонентами, которые подвергаются обработке для того, чтобы определить логическое состояние каждой ячейки памяти. Хотя рассмотренные в заявке структуры ячеек памяти, очевидно, могут быть адаптированы к схемам пассивной матричной адресации, практические решения подобной адресации не раскрыты. Данная проблема представляется крайне важной, поскольку именно ее решение определяет, будут ли вышеупомянутые схемы бездеструктивного считывания представлять в конечном итоге практическую ценность или нет.

Подводя итог проведенного обсуждения уровня техники, можно сделать вывод о существовании потребности в устройствах и способах, способных в сочетании с ячейками памяти, сформированными в запоминающие структуры с пассивной матричной адресацией и имеющими форму конденсаторов, заполненных электрически поляризуемым материалом, обладающим гистерезисом, например, ферроэлектриком, обеспечить бездеструктивное считывание данных без искажающих считываемые данные паразитных вкладов от неадресуемых ячеек матрицы.

Раскрытие изобретения

Таким образом, основная задача, на решение которой направлено настоящее изобретение, состоит в разработке стратегий и способов бездеструктивного считывания логического состояния выбранных ячеек памяти, которые адресуются по схеме пассивной матричной адресации. Одновременно должны быть устранены искажения результатов измерений за счет вкладов паразитных сигналов, обусловленных, в основном, емкостными связями в матрице, поскольку именно емкостные связи будут играть главную роль, например, в виде емкостных наводок сигналов (зарядов) от невыбранных (т.е. неадресуемых) ячеек в матрице или емкостных наводок от сети электродов и ячеек, окружающих выбранные ячейки в матрице.

Дальнейшая задача, поставленная перед изобретением, состоит в том, чтобы описать общие процедуры и представить конкретные примеры устройств для осуществления вышеупомянутых стратегий и способов.

Еще одной задачей, решаемой изобретением, является обеспечение считывания в запоминающих устройствах, по существу, свободного от усталости, без необходимости обратной записи после каждой операции считывания.

Решение перечисленных задач, а также реализация дополнительных свойств и достоинств обеспечены созданием способа по настоящему изобретению. Данный способ характеризуется тем, что к выбранной управляющей линии и линии данных или к группе управляющих линий и линий данных прикладывают изменяющиеся во времени потенциалы. Данные потенциалы взаимно скоординированы по уровню и времени таким образом, что результирующие напряжения, поданные на все или на некоторые из невыбранных ячеек в точках скрещивания между неактивными управляющими линиями и активной линией данных или активными линиями данных и/или между неактивными линиями данных и, по меньшей мере, одной активной управляющей линией, содержат только пренебрежимо малые компоненты, находящиеся во временной корреляции с малосигнальным зондирующим напряжением или с опорными сигналами, сформированными из указанного напряжения.

Обычно (что соответствует предпочтительному варианту осуществления способа по изобретению) в каждый момент времени активной является только одна управляющая линия.

Кроме того, представляется желательным, чтобы к неактивным управляющим линиям и/или к неактивным линиям данных прикладывались потенциалы, которые динамически отслеживают с высокой точностью и в реальном времени значения напряжения, приложенного соответственно к активной линии данных и/или к активной управляющей линии. В дополнение или альтернативно управление потенциалами на неактивных управляющих линиях целесообразно осуществлять посредством связанных с ними источников сигнала, которые получают входной сигнал от активной линии данных или от активных линий данных для динамического отслеживания потенциала на указанной активной линии данных или на указанных активных линиях данных.

Управление потенциалами на неактивных линиях данных желательно осуществлять посредством связанных с ними источников сигнала, которые получают входной сигнал от активной управляющей линии для динамического отслеживания потенциала на активной управляющей линии данных. При этом управление потенциалами на неактивных управляющих линиях предпочтительно осуществляют посредством их защелкивания через маршрутизаторы (ключи) и монтажные соединения на значение потенциала на активной линии данных или на активных линиях данных. Можно также осуществлять управление потенциалами на неактивных линиях данных посредством их защелкивания через маршрутизаторы (ключи) и монтажные соединения на значение потенциала на активной линии данных или на активной управляющей линии.

Представляется также целесообразным использовать при реализации способа по изобретению активный электронный контур, соединенный с каждой активной линией данных и поддерживающий заданное значение потенциала на активной линии данных. В данном варианте в качестве заданного значения потенциала желательно выбрать потенциал заземления. Предпочтительно также, чтобы все линии данных являлись при этом активными линиями данных. Далее целесообразно использовать мультиплексор или комплект маршрутизаторов для поочередного подключения активных линий данных к активному электронному контуру, который поддерживает заданное значение потенциала на активной линии данных.

В качестве альтернативы может оказаться предпочтительным использовать мультиплексор или комплект маршрутизаторов для поочередного подключения групп активных линий данных к группе активных электронных контуров, которые поддерживают заданное значение потенциала на активных линиях данных. Кроме того, в данном варианте представляется предпочтительным, чтобы активный электронный контур обеспечивал информацию о заряде или токе, протекающем по активной линии данных.

Согласно одному из предпочтительных вариантов способа по изобретению неактивные управляющие линии защелкивают на потенциал заземления через комплект переключателей или маршрутизаторов.

Кроме того, мультиплексор или комплект маршрутизаторов могут быть использованы для поочередного подключения активных управляющих линий к электронному контуру, который управляет потенциалом на активной управляющей линии в соответствии с заданным протоколом. В этом случае потенциал на активной управляющей линии предпочтительно представляет собой малосигнальное зондирующее напряжение, наложенное на напряжение смещения.

Согласно первому особо предпочтительному варианту способа по изобретению проводят анализ токового отклика выбранных ячеек памяти с использованием метода временного окна при получении синхронизирующих сигналов от контуров, управляющих потенциалом на активной управляющей линии и/или на активной линии данных или на активных линиях данных.

Согласно второму особо предпочтительному варианту способа по изобретению проводят анализ токового отклика выбранных ячеек памяти с использованием синхронного детектирования при получении опорных сигналов в требуемом частотном интервале от контуров, управляющих потенциалом на активной управляющей линии и/или на активных линиях данных. При этом опорный сигнал формируют из того компонента напряжения, приложенного к выбранным ячейкам памяти, который соответствует зондирующему напряжению. Альтернативно опорный сигнал формируют из того компонента напряжения, приложенного к выбранным ячейкам памяти, который соответствует напряжению смещения. Кроме того, данный анализ может быть проведен с использованием двух опорных сигналов, формируемых из компонентов напряжения, приложенного к выбранным ячейкам памяти, один из которых соответствует зондирующему напряжению, а другой - напряжению смещения.

В качестве еще одной альтернативы анализ проводят с использованием доминирующих частотных компонентов, по меньшей мере, одного из следующих изменяющихся во времени напряжений: основной или более высоких гармоник (например, второй или третьей) зондирующего напряжения в случае, когда зондирующее напряжение имеет единственную доминирующую частоту, или основной или более высоких гармоник (например, второй или третьей) одного или более компонентов зондирующего напряжения в случае, когда указанные компоненты имеют две или более отдельные доминирующие частоты, или суммы, или разности частот, генерируемых сложением и/или вычитанием двух или более указанных доминирующих частот.

Для решения поставленных задач и реализации дополнительных преимуществ предлагается также первое устройство для осуществления способа по изобретению. Оно содержит считывающие усилительные контуры, каждый из которых подключен к одной из линий данных и защелкнут на виртуальное заземление, и синхронный усилитель, соединенный с выходами каждого считывающего усилительного контура и имеющий вход подачи опорного сигнала и выход для выведения считанного сигнала. Устройство содержит также комбинированный источник напряжения смещения и сигнала, один выход которого соединен с входом подачи опорного сигнала синхронного усилителя для подачи на него опорного сигнала, драйвер активной управляющей линии, который связан с другим выходом комбинированного источника напряжения смещения и сигнала. Выход драйвера соединен с мультиплексором, производящим выбор активной управляющей линии и выполненным с возможностью подключения к одному из концов каждой управляющей линии. Имеется также комплект маршрутизаторов, связанных с другими концами управляющих линий для защелкивания всех неактивных управляющих линий на потенциал заземления. Данное устройство выполнено с возможностью параллельного считывания всех ячеек памяти на активной управляющей линии.

Кроме того, для решения поставленных задач и реализации дополнительных преимуществ предлагается второе устройство для осуществления способа по изобретению. Данное устройство характеризуется тем, что содержит мультиплексор, подключаемый к одному из концов линий данных и осуществляющий выбор активной линии данных для считывания, и считывающий усилительный контур, соединенный с мультиплексором и защелкнутый на виртуальное заземление. В состав устройства входят также синхронный усилитель, соединенный с выходом считывающего усилительного контура и имеющий вход подачи опорного сигнала и выход для выведения считанного сигнала, комбинированный источник напряжения смещения и сигнала, выход которого соединен с входом подачи опорного сигнала синхронного усилителя для подачи на него опорного сигнала. Имеется также драйвер активной управляющей линии, который связан с другим выходом комбинированного источника напряжения смещения и сигнала и выход которого соединен с мультиплексором. Мультиплексор производит выбор активной управляющей линии и выполнен с возможностью подключения к одному из концов каждой управляющей линии. В устройстве имеются первый комплект маршрутизаторов, связанных с другими концами управляющих линий для защелкивания всех неактивных управляющих линий на потенциал заземления, и второй комплект маршрутизаторов, выполненных с возможностью подключения к другим концам линий данных для защелкивания всех неактивных линий данных на потенциал заземления. Устройство по изобретению выполнено с возможностью параллельной адресации всех ячеек памяти на активной управляющей линии в сочетании с последовательным считыванием сигналов со считывающего усилительного контура согласно соответствующему протоколу синхронизации.

Краткое описание чертежей

Настоящее изобретение станет более понятным из нижеследующего подробного описания предпочтительных вариантов изобретения, которое должно рассматриваться совместно с прилагаемыми чертежами.

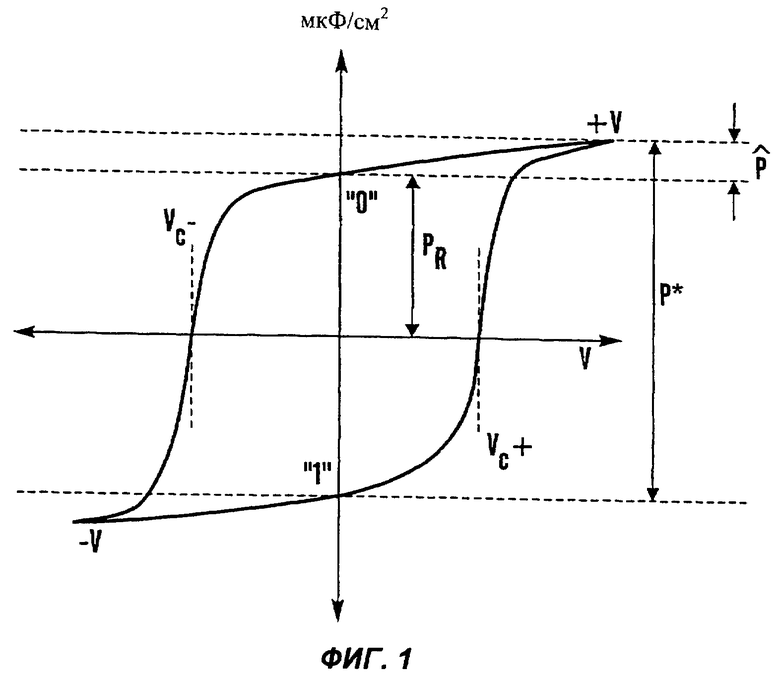

На фиг.1 представлена в общем виде кривая гистерезиса для запоминающего материала ферроэлектрического типа.

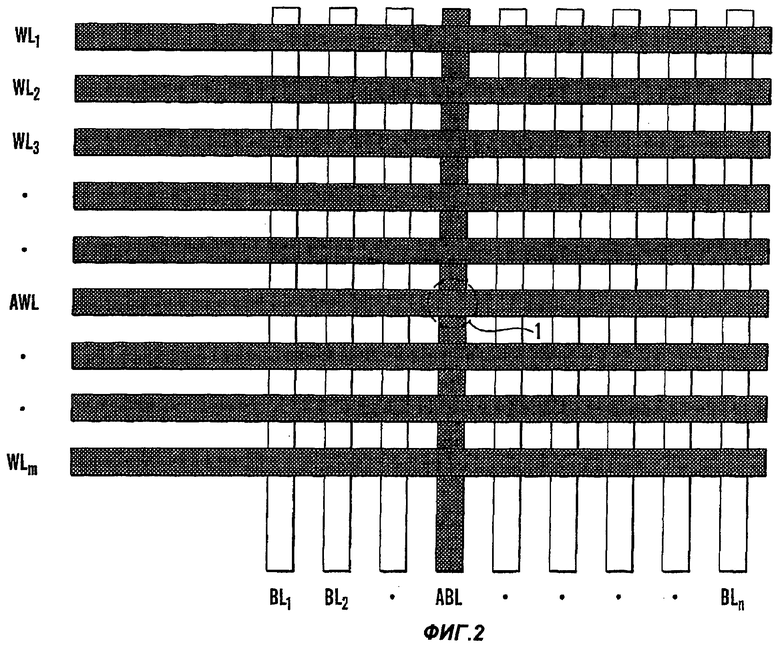

На фиг.2 представлена схема расположения электродов для случая пассивной матричной адресации, например, применительно к ферроэлектрической памяти, используемой при осуществлении настоящего изобретения.

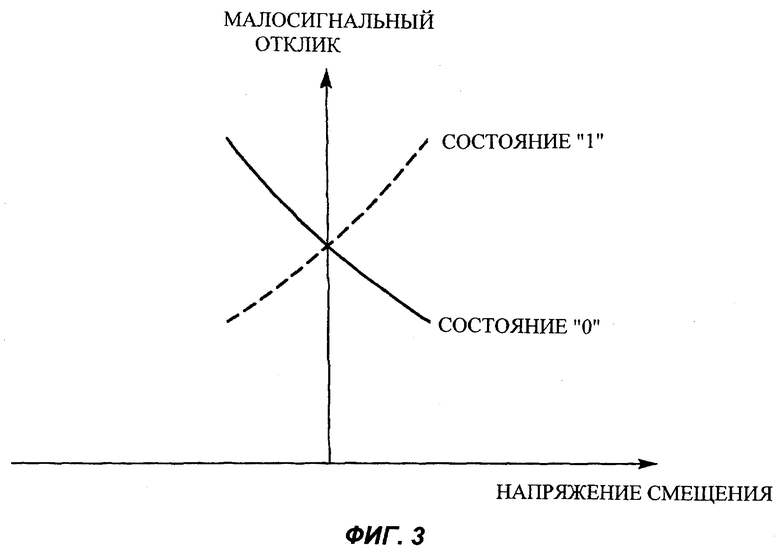

На фиг.3 показан типичный малосигнальный отклик применительно, например, к ферроэлектрической ячейке памяти.

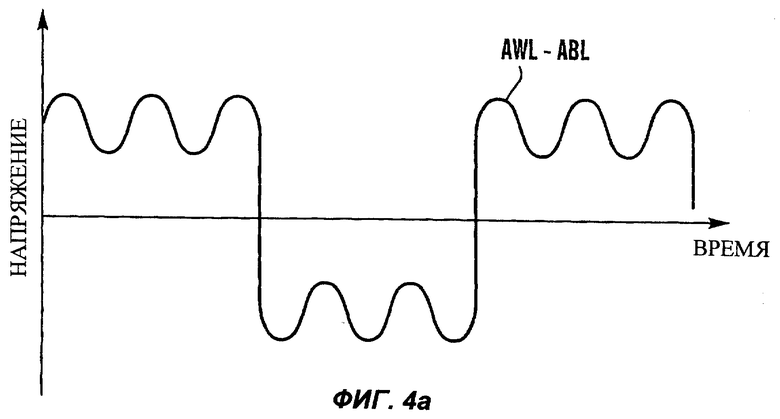

На фиг.4а приведен пример кривой напряжения при считывании.

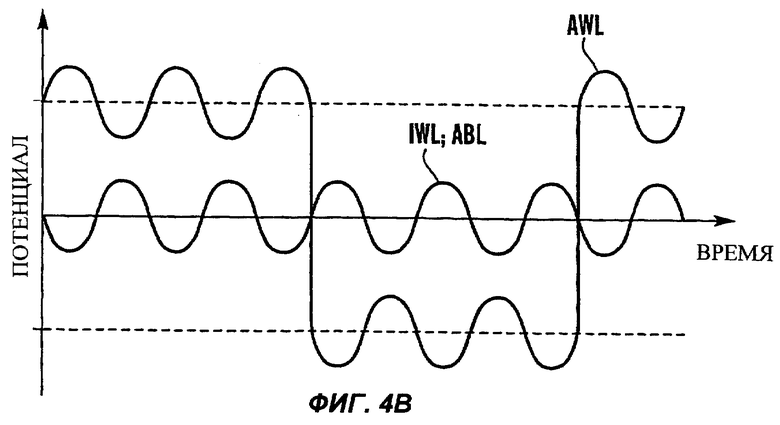

На фиг.4b приведены кривые потенциала, соответствующие кривой напряжения при считывании.

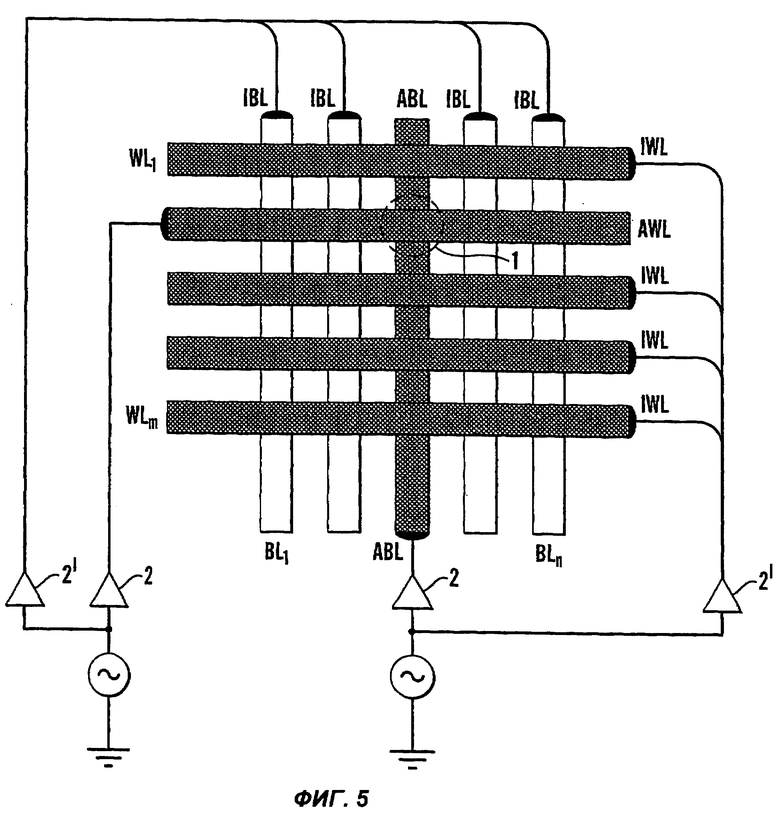

Фиг.5 иллюстрирует принцип первого варианта осуществления способа по изобретению.

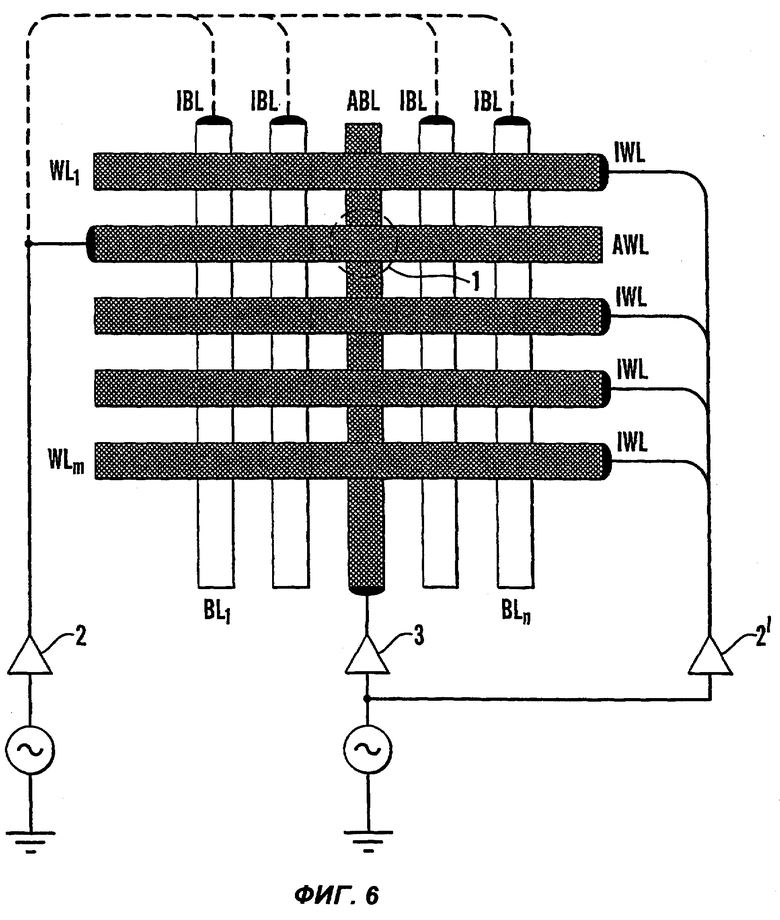

На фиг.6 представлена модификация варианта по фиг.5.

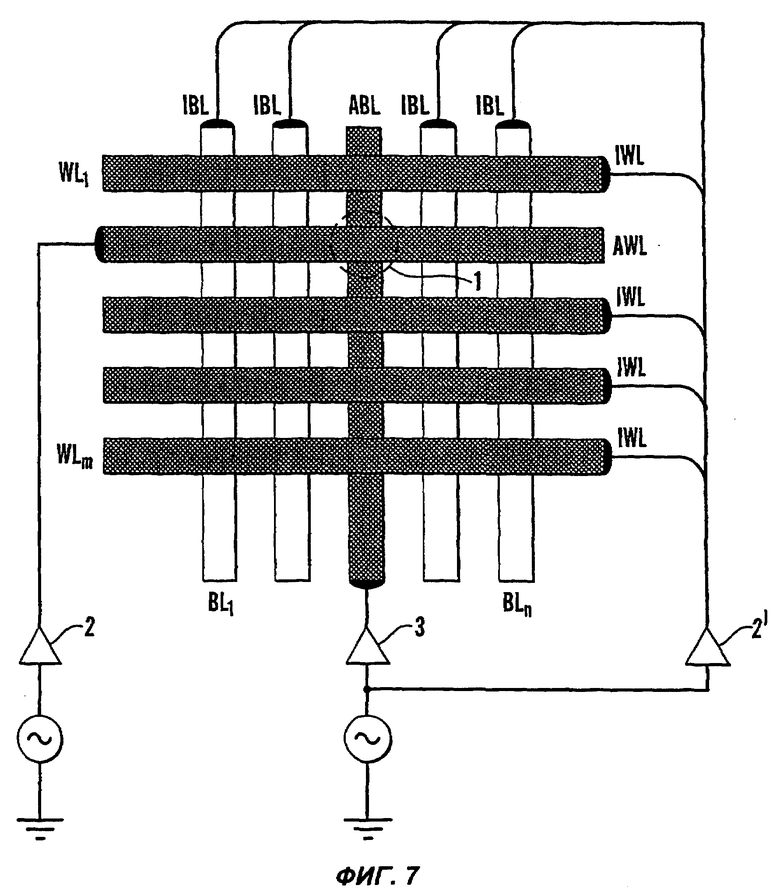

На фиг.7 представлена еще одна модификация варианта по фиг.5.

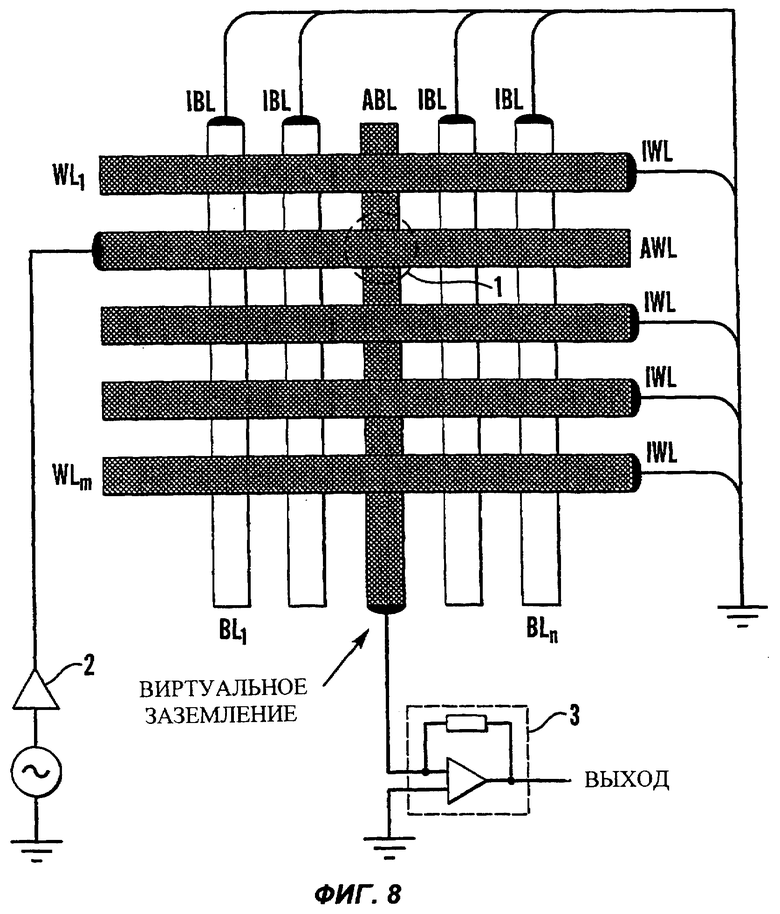

На фиг.8 представлен пример схемы считывающего усилителя, используемого вместе с настоящим изобретением.

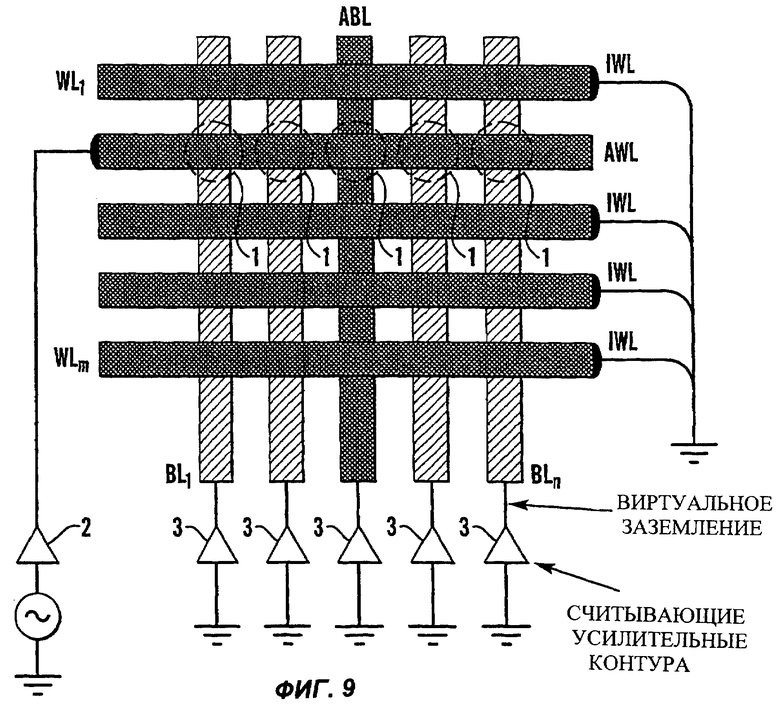

Фиг.9 иллюстрирует принцип второго варианта осуществления способа по изобретению.

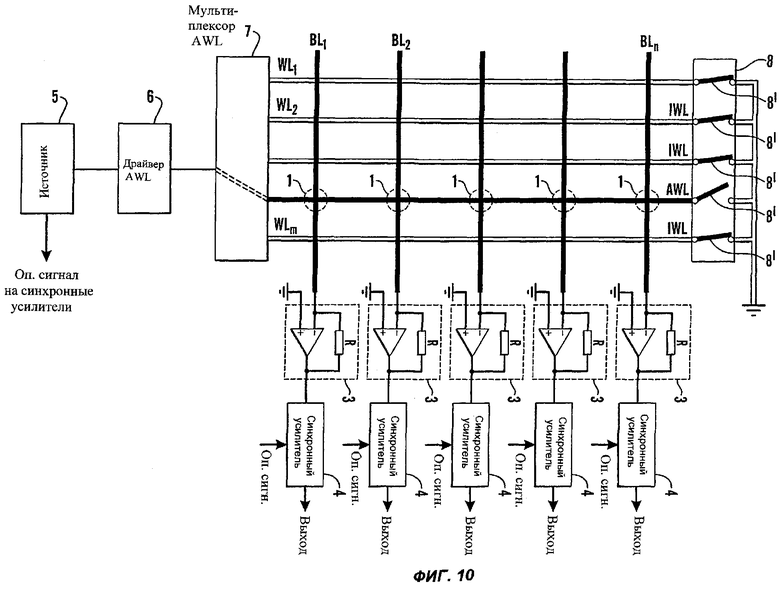

Фиг.10 иллюстрирует структуру первого устройства в соответствии с изобретением, предназначенного для осуществления второго варианта способа по изобретению.

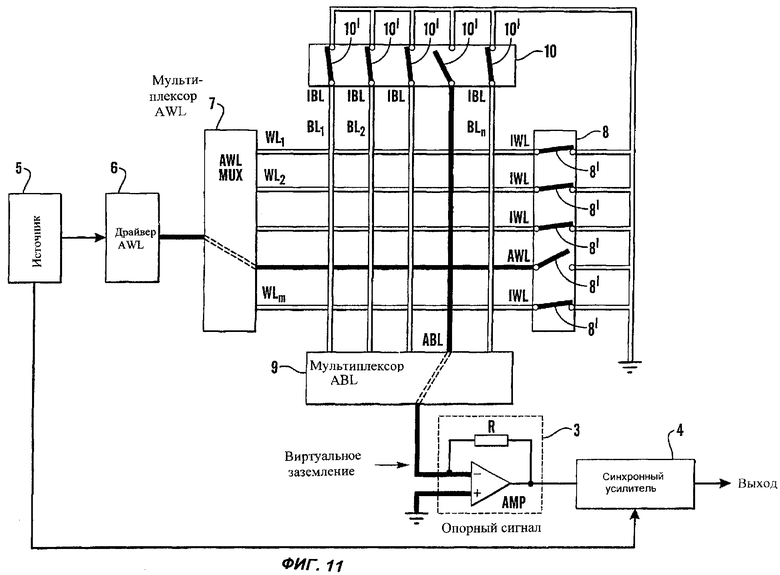

Фиг.11 иллюстрирует структуру второго устройства в соответствии с изобретением, также предназначенного для осуществления второго варианта способа по изобретению.

Осуществление изобретения

Перед тем, как привести подробное описание изобретения, будут кратко рассмотрены его физические основы.

На фиг.1 приведена типичная кривая гистерезиса для ферроэлектрического материала, имеющего при нулевом внешнем поле два стабильных состояния поляризации, которым соответствуют логические состояния, обозначенные на фиг.1, как "0" и "1".

Кривая гистерезиса соответствует значениям электрической поляризации, выраженным в мкФ/см2, в зависимости от электрического потенциала V в вольтах. В варианте, показанном на фиг.1, положительная поляризация принимается соответствующей логическому состоянию "0", тогда как отрицательная поляризация - логическому состоянию "1". Через Vc обозначено коэрцитивное напряжение, через PR - остаточная поляризация, а через  - разность между электрической поляризацией при напряжении насыщения и остаточной поляризацией PR Далее через Р* обозначено суммарное изменение поляризации в результате ее обращения (т.е. изменения знака), которое имеет место, когда ячейка памяти переключается из логического состояния "0" в логическое состояние "1" (такое переключение может иметь место при деструктивном считывании содержимого ячейки памяти).

- разность между электрической поляризацией при напряжении насыщения и остаточной поляризацией PR Далее через Р* обозначено суммарное изменение поляризации в результате ее обращения (т.е. изменения знака), которое имеет место, когда ячейка памяти переключается из логического состояния "0" в логическое состояние "1" (такое переключение может иметь место при деструктивном считывании содержимого ячейки памяти).

Фиг.2 иллюстрирует расположение электродов, обычно применяемое в случае использования ферроэлектрической памяти с пассивной матричной адресацией. Собственно запоминающая среда, т.е. ферроэлектрический материал, находится между первым набором параллельных электродов WL1-WLm, которые далее будут именоваться горизонтальными электродами, и вторым набором параллельных электродов BL1-BLn, которые ориентированы ортогонально электродам первого набора и далее будут именоваться вертикальными электродами. Все эти электроды образуют электродную матрицу. Подача напряжения на горизонтальные и вертикальные электроды воздействует на ячейки памяти, находящиеся в зонах пересечения электродов матрицы. В случае подачи напряжения на конкретные горизонтальный и вертикальный электроды к выбранной ячейке памяти будет приложен соответствующий потенциал. В результате она приобретет электрическую поляризацию, положительную или отрицательную, т.е. соответствующую логическому состоянию "0" или "1", что определяется используемым протоколом.

В контексте настоящего изобретения особое внимание будет уделено некоторым конкретным схемам бездеструктивного считывания, которые были упомянуты в рамках анализа уровня техники и рассматриваются как релевантные по отношению к настоящему изобретению. В типичном случае считывание производится путем измерения отклика ячейки памяти в области малых сигналов при подаче на выбранную ячейку памяти изменяющегося во времени зондирующего напряжения, соответствующего области малых сигналов (малосигнального напряжения) с одновременным наложением опорного напряжения с более медленным изменением во времени по сравнению с зондирующим напряжением. Логическое состояние обычно определяется путем регистрации зависимости получаемого отклика от опорного напряжения. Опорное напряжение может быть сделано изменяющимся по заранее определенному графику. Например, оно может переключаться между двумя значениями, имеющими одинаковые или противоположные полярности, или периодически модулироваться между двумя предельными значениями. В качестве малосигнального отклика может быть выбрана, например, емкость ячейки памяти на частоте зондирующего напряжения. Альтернативно откликом может служить амплитуда или фаза одной из высших гармоник регистрируемого сигнала.

В соответствии с общепринятой терминологией далее показанные на фиг.2 горизонтальные электроды WL будут именоваться управляющими линиями, а вертикальные электроды BL - линиями данных. Те ячейки памяти, которые выбраны для осуществления записи, считывания, стирания или обновления, будут именоваться выбранными ячейками, тогда как остальные ячейки памяти - невыбранными ячейками. Управляющая линия WL и линия BL данных, которые соединены с одной или более выбранными ячейками, именуются соответственно активной управляющей линией (AWL) и активной линией данных (ABL). Аналогично управляющая линия WL и линия BL данных, которые не соединены с какой-либо из выбранных ячеек, именуются соответственно неактивной управляющей линией (IWL) и неактивной линией (IBL) данных.

Фундаментальная и постоянно возникающая проблема при хранении, считывании и стирании данных в матричных устройствах с пассивной адресацией связана с большим количеством электрических соединений внутри сети электродов и ячеек памяти в матрице. В частности, подача напряжения на взаимно пересекающиеся управляющие линии и линии данных с целью адресации к выбранной ячейке или к группе выбранных ячеек в матрице может одновременно привести к тому, что к невыбранным ячейкам памяти будет приложено напряжение, которое способно оказать вредное воздействие на их логические состояния. Кроме того, подобные невыбранные ячейки могут вносить свои вклады в электрические заряды и тем самым искажать отклик, который измеряется на адресуемых ячейках.

Эта проблема может быть проиллюстрирована с помощью фиг.2. Примем, что требуется считать логическое состояние ячейки 1 памяти, расположенной на пересечении активной управляющей линии AWL и активной линии ABL данных в матрице. Предположим далее, что считывание производится путем подачи на ячейку 1 изменяющегося во времени напряжения и измерения результирующего токового отклика. Поскольку измерения осуществляются путем подключения к активным линиям AWL и ABL на краях матрицы, потенциалы, приложенные к этим линиям, оказываются приложенными также к невыбранным ячейкам, связанным с данными линиями. Таким образом, в зависимости от суммарного распределения потенциалов и импедансов по матрице паразитные сигналы от большого количества невыбранных ячеек могут внести свой вклад в измеряемый отклик от адресуемой ячейки 1. С учетом того, что реальные запоминающие устройства могут содержать матрицы с сотнями или тысячами управляющих линий, данная проблема хорошо знакома специалистам в области электронной техники.

Пассивная матричная адресация уникальна тем, что сочетает высокую плотность ячеек в памяти с простотой и гибкостью архитектуры. Однако разработчикам настоящего изобретения неизвестны какие-либо входящие в уровень техники решения проблемы паразитных сигналов в запоминающих устройствах с пассивной матричной адресацией, использующих схемы бездеструктивного считывания типа описанных Бреннаном в вышеперечисленных патентных документах или раскрытых в упомянутой международной заявке PCT/NO01/00472, или подобных им. Все эти схемы бездеструктивного считывания будут представлять только академический интерес, если они не смогут быть скомбинированы с реалистичными и эффективными средствами адресации.

Как это было отмечено выше, настоящее изобретение, в первую очередь, направлено на устранение вкладов от паразитных сигналов типа тех, которые обусловлены наличием емкостных связей. Однако следует учитывать, что в запоминающих устройствах с пассивной матричной адресацией, на использование в которых рассчитан способ по настоящему изобретению, могут иметь место также индуктивные или радиационные связи, приводящие к индуктивным или радиационным наводкам от сети электродов и ячеек, окружающих выбранные ячейки в матрице. Это явление становится более понятным, если рассматривать матричную память как сеть емкостных, индуктивных и резистивных элементов, через которую распространяются изменяющиеся во времени напряжения и токи, имеющие различные частотные составляющие. В связи с этим было проведено имитационное моделирование крупных запоминающих устройств с пассивной матричной адресацией, основанное на использовании упрощенной модели матрицы, а именно модели в виде контура с сосредоточенными параметрами.

В рамках данной модели емкостные, индуктивные и радиационные связи между различными линиями в матрице могут быть описаны с использованием емкостных, индуктивных и радиационных элементов с сосредоточенными параметрами.

Моделирование полей, основанное на двумерной модели, достаточно точно отображающей реальное устройство, дало результат, который нельзя отнести к неожиданным: основной вклад в паразитные сигналы дают емкостные связи, тогда как индуктивными связями в практических задачах можно пренебречь. Радиационные эффекты также оказались пренебрежимо малыми. Несмотря на то, что сигналы, распространяющиеся в матрице, могут иметь различные частотные компоненты, они могут рассматриваться как медленно изменяющиеся во времени, т.е. имеющие соответственно низкие частоты. Любые емкостные и индуктивные связи могут рассматриваться в качестве эффектов в ближнем поле; при этом реальные размеры матрицы гарантируют также отсутствие эффектов запаздывания. На частоте 1 ГГц длина электромагнитной волны составляет 33 см, тогда как устройства, в которых применим способ по изобретению, имеют размеры, соответствующие стандартам технологии интегральных схем. Другими словами, их линейные размеры составляют порядка нескольких миллиметров, не превышая 1 см.

Повышение плотности записи данных, т.е. плотности расположения ячеек в запоминающем устройстве, может сделать это устройство более подверженным паразитным эффектам. Однако любое уменьшение масштаба ширины линий, шага матрицы и размеров ячеек без изменения значений плотности заряда и напряжения поля должно сопровождаться соответствующим снижением рабочих напряжений. Следовательно, можно сделать вывод, что рассматриваемое запоминающее устройство в рамках любых практических задач может считаться состоящим из емкостных структур с сосредоточенными параметрами или зарядов с сосредоточенными параметрами в сети, причем в ходе операции адресации указанные заряды либо являются статическими, либо изменяются лишь в незначительной степени. Это приводит, в крайнем случае, только к эффектам взаимодействия ближнего поля с частотами значительно ниже тех, которые, по расчетам, могут привести к возникновению каких-либо радиационных связей. С учетом приведенных соображений нижеследующее обсуждение конкретных вариантов осуществления способа и устройств согласно изобретению должно рассматриваться как относящееся, в основном, к уменьшению вкладов паразитных сигналов, обусловленных только емкостными связями, без необходимости уделять особое внимание индуктивным или радиационным связям.

Далее настоящее изобретение будет описано более подробно и конкретно на примере различных вариантов его осуществления.

Главная идея настоящего изобретения основана на наблюдении того, что паразитные эффекты обусловлены токами, протекающими через ячейки и электроды в матрице под действием разности потенциалов. Другими словами, данные токи перестали бы протекать, если бы все части матриц все время были эквипотенциальными. Однако процессы считывания, релевантные для изобретения, требуют приложения к выбранным ячейкам изменяющегося во времени напряжения.

В соответствии с настоящим изобретением рассматриваемая проблема решена приложением изменяющихся во времени потенциалов к электродам в матрице таким образом, что соответствующие напряжения смещения и зондирующие напряжения прикладываются к выбранным ячейкам при наличии нулевого напряжения на всех невыбранных ячейках в динамическом режиме. Этот результат достигается благодаря скоррелированному управлению по времени и по уровню потенциалами на управляющих линиях и линиях данных таким образом, что потенциалы на управляющих линиях и линиях данных, которые пересекают невыбранные ячейки, привязаны друг к другу. Таким образом, если потенциал управляющей линии, соответствующей конкретной невыбранной ячейке, будет претерпевать изменения, точно и в реальном времени воспроизводящие изменяющийся во времени потенциал, приложенный к линии данных, связанной с той же ячейкой, данная ячейка будет эквипотенциальной в динамическом режиме. Как будет описано далее со ссылками на предпочтительные варианты осуществления, управляющая линия и линия данных, скрещивающиеся на определенных невыбранных ячейках, могут обе иметь изменяющиеся во времени потенциалы, синхронизированные друг с другом, или быть привязаны (защелкнуты) к одному и тому же квазистатическому потенциалу.

Далее основные принципы изобретения будут проиллюстрированы с помощью фиг.3 и 4. На фиг.3 показан характер отклика в области малых сигналов для ячейки памяти, поляризованной в любом из направлений, соответствующих логическим состояниям "0" или "1". На фиг.4а показана кривая напряжения при считывании, соответствующая выбранной ячейке памяти. Кривая соответствует синусоидальному зондирующему напряжению в режиме слабых сигналов (малосигнальному зондирующему напряжению), наложенному на напряжение смещения в форме прямоугольных импульсов. Примем, что ячейки памяти в режиме малых сигналов характеризуются показанной на фиг.3 зависимостью емкости от напряжения. Как можно видеть, логические состояния "0" и "1" могут быть определены путем подачи напряжения смещения и регистрации результирующих изменений емкости. Напряжение смещения может изменяться во времени, например, иметь форму синусоиды или прямоугольных импульсов с периодом, намного превышающим период малосигнального зондирующего напряжения, используемого для измерения емкости. В последнем случае наблюдаемое напряжение на выбранной ячейке памяти будет изменяться во времени так, как это показано на фиг.4а.

Данное напряжение формируется за счет разности мгновенных значений потенциалов на активной управляющей линии и на активной линии данных, скрещивающихся на выбранной ячейке. Соответствующие потенциалы обозначены на фиг.4b, как AWL и ABL. Здесь потенциалы на активной управляющей линии и активной линии данных имеют вид синусоид с противоположными фазами. Если управлять потенциалом на неактивной управляющей линии IWL таким образом, чтобы он повторял потенциал на активной линии данных, то, как можно видеть из фиг.4b, разность потенциалов между IWL и ABL (соответствующая наблюдаемому напряжению на всех невыбранных ячейках, лежащих на активной линии данных) будет в любой момент времени равна нулю. Таким образом, при регистрации токового отклика с помощью считывающего контура, соединенного с активной линией данных, ко всем ячейкам, за исключением выбранной, будет приложено нулевое напряжение.

Во многих практических ситуациях данная простая процедура совпадения потенциалов на противоположных сторонах невыбранных ячеек должна быть дополнена и модифицирована. В зависимости от используемого режима различения логических состояний (по зависимости емкости от напряжения смещения, по второй или более высокой гармонике, по суммарной или разностной частоте) наиболее вредные вклады в сигнал от паразитных токов обычно имеют место на частотах, значительно отстоящих от частот, которые содержатся в приложенном к выбранным ячейкам компоненте опорного напряжения, в типичном случае являющемся низкочастотным. В связи с этим динамическое выравнивание потенциалов управляющей линии и линии данных во многих случаях должно иметь место только на определенных конкретных частотах, которые выделяются из суммарного напряжения, прикладываемого к выбранным ячейкам памяти. В качестве простого примера можно указать случай, когда измерение зависимости емкости от опорного напряжения производится с использованием высокочастотного зондирующего напряжения с частотой ω, накладываемого на низкочастотное опорное напряжение, имеющее частоту Ω. В предположении, что отклик является линейным, в этом случае достаточно обеспечить выравнивание потенциалов управляющей линии и линии данных для невыбранных ячеек на частоте ω.

Как уже упоминалось, настоящее изобретение фокусируется на устранении или уменьшении влияния емкостных связей. Поэтому важнейшим аспектом изобретения является устранение емкостных наводок в процессе считывания.

На высоких частотах результаты считывания могут дополнительно искажаться паразитными наводками вследствие индуктивных и радиационных связей, обусловленных управляющими линиями и линиями данных в других частях матрицы. Хотя оба этих типа наводок, как было показано выше, являются не столь серьезными, дальнейший и не совсем второстепенный аспект настоящего изобретения заключается в минимизации наводок от паразитных сигналов, обусловленных также и связями данных типов. В соответствии с одним из классов вариантов осуществления изобретения эта задача решается тем, что во время цикла считывания все неадресуемые управляющие линии и линии данных одновременно подвергаются изменениям потенциала, моделирующим релевантные компоненты сигнала, имеющиеся на активной линии данных или группе линий данных. Разумеется, данный вариант игнорирует эффекты задержки, однако в большинстве реальных запоминающих устройств каждая адресуемая матрица будет достаточно малой, а частоты достаточно низкими для того, чтобы рассматриваемое приближение было приемлемым.

Приведенный на фиг.4а и 4b пример возбуждения единственной ячейки показывает, что емкостной наводки от невыбранных ячеек на неактивных управляющих линиях, пересекающих активную линию данных, можно избежать путем скоординированной подачи напряжения на все неактивные управляющие линии таким образом, что к адресуемой ячейке прикладывается только малосигнальное возбуждающее напряжение, не являющееся пренебрежимо малым. Далее будет рассмотрена проблема реализации принципов настоящего изобретения применительно к матрицам, содержащим множество управляющих линий и линий данных. Будут описаны также некоторые предпочтительные варианты изобретения. При этом необходимо учитывать, что приводимые примеры ни в коем случае не исчерпывают всего объема изобретения.

Первый вариант осуществления способа по изобретению будет рассмотрен со ссылками на фиг.5-8, иллюстрирующие адресацию единственной случайно выбираемой ячейки памяти.

На фиг.5 приведен пример считывания из единственной ячейки памяти в случае пассивной матричной адресации, в котором используемые при считывании активная управляющая линия AWL и активная ABL линия данных гальванически изолированы от неактивных управляющих линий и линий данных.

На фиг.5 показано, как наводка от невыбранных ячеек на активной управляющей линии AWL и активной линии ABL данных устраняется путем координированной подачи напряжения на все неактивные управляющие линии IWL и линии IBL данных таким образом, что к адресуемой ячейке 1 прикладывается только напряжение, которое не является пренебрежимо малым. Как можно видеть из фиг.5, этот эффект обеспечивается тем, что все неактивные управляющие линии IWL повторяют мгновенный потенциал на активной линии ABL данных. Одновременно все неактивные линии IBL данных повторяют потенциал на активной управляющей линии AWL. Благодаря этому к любой невыбранной ячейке на активной управляющей линии AWL, а также к любой невыбранной ячейке на активной линии ABL данных не прикладывается никакого напряжения.

В схеме, приведенной на фиг.5, активные и неактивные управляющие линии и линии данных питаются от двух гальванически разделенных, но взаимно скоординированных генераторов 2, 2' сигналов. В результате измерения емкости адресуемой ячейки 1 могут производиться непосредственно на выводах активной управляющей линии и активной линии данных с помощью различных технологий и оборудования.

На фиг.6 показано, как производится детектирование токового отклика с помощью считывающего усилительного контура 3, установленного на активной линии ABL данных, в то время как питание активной управляющей линии AWL осуществляется от генератора 2 сигнала с низким импедансом. Как показано на чертеже, неактивные линии IBL данных могут быть при этом связаны с активной управляющей линией AWL. Таким образом, представленный на фиг.6 вариант можно рассматривать как подкласс схемы, представленной на фиг.5, в котором неактивные линии IBL данных непосредственно привязаны (защелкнуты) по напряжению к активной управляющей линии AWL. Генератор 2 сигнала для управляющей линии в данном случае рассматривается как имеющий очень низкий импеданс, а токовый отклик детектируется считывающим усилительным контуром 3, который регистрирует ток, протекающий в процессе выполнения протокола цикла считывания по активной линии ABL данных. Потенциалы на неактивных управляющих линиях IWL повторяют потенциал на активной линии ABL данных благодаря наличию ведомого генератора 2', показанного также на фиг.5. Хотя неактивные линии IBL данных не вносят вклада за счет емкостной связи в сигнал на активной линии ABL данных, представленная на фиг.6 схема имеет определенные полезные свойства, в частности, потому, что обеспечивает управление потенциалами на неактивных линиях IBL данных. Более простая альтернатива, разумеется, состоит в отключении неактивных линий данных от источника напряжения.

На фиг.7 представлена схема, похожая на схему по фиг.6. Выбранной и в этом случае является ячейка 1; однако теперь все линии WL; BL в электродной матрице привязаны (защелкнуты) с помощью ведомого генератора 2' к потенциалу активной линии данных. Таким образом, фиг.7 представляет другой подкласс схемы по фиг.5. В данном случае все линии в матрице, за исключением активной управляющей линии AWL, воспроизводят потенциал активной линии ABL данных. Достоинство этой схемы в том, что устраняется влияние всех скрещивающихся с активной управляющей линией неактивных управляющих линий IWL как источников паразитного сигнала и, кроме того, предотвращаются наводки от других частей матрицы, в особенности емкостная наводка от близлежащих линий данных.

Модификации первого варианта осуществления изобретения, показанные на фиг.5, 6 и 7, обеспечивают наличие почти нулевого напряжения на всех ячейках, в которых активная линия ABL данных скрещивается с неактивной управляющей линией IWL. В результате единственный не являющийся пренебрежимо малым вклад в ток, протекающий через считывающий усилительный контур 3, исходит из адресуемой ячейки 1. Считывающий усилительный контур 3 может быть сконфигурирован так, как это представлено на фиг.8. Фиг.8 показывает также, что активные линии ABL данных могут быть заданы, как линии, имеющие потенциал виртуального заземления. Подобная схема является стандартной для измерения емкости, однако она может быть использована и в любых других схемах детектирования, релевантных в контексте изобретения. В случае использования операционного усилителя с высоким коэффициентом усиления вход усилителя и, следовательно, линия данных могут быть защелкнуты на желаемый, произвольно выбираемый потенциал. Во многих практических схемах этот потенциал будет идентичен потенциалу заземления системы. В таком случае точка подключения к активной линии ABL данных будет далее именоваться точкой виртуального заземления. Из фиг.7 можно видеть, что при использовании контура детектирования с виртуальным заземлением вся матрица, за исключением активной управляющей линии AWL, находится под потенциалом заземления. Такая схема имеет очевидные достоинства в терминах простоты и экранирования наводок от паразитных сигналов. В этом случае размах напряжения (напряжения смещения и зондирующего напряжения), прикладываемого к выбранной ячейке 1, полностью задается активной управляющей линией AWL, при сохранении базового принципа выравнивания потенциалов, приложенных к невыбранным ячейкам.

Далее, со ссылкой на фиг.9, будет рассмотрен второй вариант осуществления способа по изобретению, в соответствии с которым имеет место параллельная адресация управляющих линий WL. Вновь используется матрица с пассивной адресацией, но теперь с одновременной адресацией полной строки ячеек памяти на управляющей линии при подавлении паразитных сигналов.

Согласно данному, второму варианту каждая линия данных считывается параллельно с одной или более линиями данных, потенциально со всеми другими линиями данных с помощью отдельных считывающих усилительных контуров 3, присоединенных к каждой линии BL данных. Таким образом, в течение цикла считывания вся матрица, за исключением единственной адресуемой управляющей линии AWL, может поддерживаться под одинаковым потенциалом. Так, все неактивные управляющие линии IWL присоединены к источнику выбранного потенциала, например, потенциала заземления, тогда как активная управляющая линия AWL соединена с генератором 2 сигнала, который обеспечивает выработку напряжения смещения, а также малосигнального зондирующего напряжения. Данный генератор 2 сигнала имеет малый импеданс, т.е. он способен поддерживать запрограммированные значения напряжения смещения и зондирующего напряжения на соединенной с ним активной управляющей линии AWL, не испытывая влияния со стороны токов утечки в линиях данных, скрещивающихся с активной управляющей линией. Каждая индивидуальная линия BL данных имеет подключенный к ней считывающий усилительный контур, например, аналогичный показанному на фиг.7. В результате может быть определено значение тока в каждой линии данных. Потенциал на входах считывающих усилителей и, следовательно, на линиях BL данных поддерживается на уровне виртуального заземления. Это гарантирует, что отсутствует какой-либо емкостной перенос заряда в ячейках, связывающих линии BL данных с неактивными (неадресуемыми) управляющими линиями IWL.

При использовании данного варианта могут быть реализованы два важных преимущества.

1) В дополнение к устранению емкостных наводок на активные линии ABL данных от зарядов, имеющихся на невыбранных ячейках, желательно также минимизировать перекрестные помехи, обусловленные емкостными, а в некоторых случаях также индуктивными и радиационными связями в других зонах матрицы адресации. Подобные проблемы обостряются по мере повышения частоты сигналов и/или уменьшения физических расстояний между управляющими линиями и линиями данных, т.е. при совершенствовании конструкций для достижения более высоких характеристик. При использовании рассматриваемого предпочтительного варианта можно достичь значительного снижения наводок от паразитных вкладов в считываемые сигналы, поскольку вся матрица (за исключением активной управляющей линии) может поддерживаться под одинаковым потенциалом, например, потенциалом заземления. Тем самым обеспечиваются возможности существенного снижения паразитных наводок на считываемые сигналы.

2) Поскольку каждая линия BL данных скрещивается с активной (адресуемой) управляющей линией AWL и связана со своим отдельным считывающим усилительным контуром 3, становится возможным производить считывание параллельно со всех ячеек на адресуемой управляющей линии AWL, с соответствующим повышением скорости вывода данных из матрицы.

Для специалистов в области электронной техники должно быть очевидным, что второй вариант осуществления изобретения обеспечивает возможность потенциального упрощения схемы управления за счет прямого монтажа.

Это положение иллюстрируется фиг.10 и 11, на которых представлены соответственно схемы первого и второго устройств, предназначенных для осуществления второго варианта способа по изобретению.

В описанной выше схеме с одновременным доступом к полной управляющей линии принималось, что каждая линия данных связана со своим индивидуальным считывающим усилительным контуром 3. Как правило, желательно располагать ячейки в матрице с максимально возможной плотностью, что соответствует минимизации шага линий данных. Это, однако, приводит к недостатку места для размещения считывающих усилительных контуров у кромки матрицы, причем данная проблема обостряется по мере усложнения подобных контуров.

Один из путей решения проблемы недостатка места состоит в сокращении количества драйверных контуров для управляющих линий и количества считывающих усилительных контуров путем подключения их к управляющим линиям WL и линиям BL данных в матрице посредством ключей (маршрутизаторов). Соответственно, на фиг.10 представлено устройство по изобретению, предназначенное для реализации схемы считывания всего управляющего слова с использованием мультиплексированного подключения активной управляющей линии, синхронизированного с переключаемым подключением неактивных управляющих линий IWL к потенциалу заземления, в сочетании с подключением линий BL данных к потенциалу виртуального заземления посредством контуров детектирования.

Как видно из фиг.10, к одному концу каждой линии BL данных подключен считывающий усилительный контур 3, аналогичный представленному на фиг.8 и находящийся под потенциалом виртуального заземления. К каждому считывающему усилительному контуру 3 присоединен синхронный усилитель 4, имеющий вход подачи опорного сигнала и выход для выведения считанного сигнала. Опорный сигнал генерируется комбинированным источником 5 напряжения смещения и сигнала, причем опорный сигнал от этого источника подается на синхронные усилители 4. Источник 5 напряжения смещения и сигнала имеет также выход, связанный с драйвером 6 активной управляющей линии, выход которого связан с AWL-мультиплексором 7, производящим выбор управляющей линии WL, подлежащей считыванию, т.е. является мультиплексором активной управляющей линии AWL. Одновременно AWL-мультиплексор 7 подает, по мере необходимости, напряжение смещения на неактивные управляющие линии IWL. Противоположные концы управляющих линий соединены с комплектом 8 маршрутизаторов, которые позволяют осуществлять подключение неактивных управляющих линий IWL к потенциалу заземления через соответствующие переключающие средства 8'. Таким образом, обеспечивается возможность считывания полной управляющей линии, т.е. параллельного считывания из всех ячеек 1 памяти, в которых линии BL данных скрещиваются с активными управляющими линиями AWL.

На фиг.11 приведено второе устройство по изобретению, во многом сходное с устройством по фиг.10, но использующее подключение линий BL данных к контуру детектирования через мультиплексор. Более конкретно в устройстве по фиг.11 считывающий усилительный контур 3 подключается к выбранной активной линии ABL данных через ABL-мультиплексор 9 активных линий данных, который может подключаться к одному из концов линий BL данных. Как и раньше, считывающий усилительный контур 3 защелкнут на виртуальное заземление, а его выход подключен к входу единственного синхронного усилителя 4, имеющего выход для выведения считанного сигнала и вход подачи опорного сигнала от комбинированного источника 5 напряжения смещения и сигнала. Выполнение комбинированного источника 5 напряжения смещения и сигнала, драйвера 6 активной управляющей линии и AWL-мультиплексора 7 активной управляющей линии такое же, что и в устройстве по фиг.10; естественно, эти компоненты выполняют те же функции. Кроме того, у противоположных концов управляющих линий WL в устройстве по фиг.11 также имеется комплект 8 маршрутизаторов, позволяющих осуществлять подключение неактивных управляющих линий IWL к потенциалу заземления через переключающие средства 8'. Однако в устройстве по фиг.11 дополнительно предусмотрен второй комплект 10 маршрутизаторов, расположенный у противоположных концов линий BL данных и аналогичным образом содержащий переключающие средства 10', позволяющие защелкивать неактивные линии IBL данных на тот же потенциал заземления, что и неактивные управляющие линии.

Как можно видеть, устройство по фиг.11 реализует схему считывания полной строки, которая в определенной степени напоминает схемы считывания полной строки с деструктивным считыванием, описанные в патентных документах, принадлежащих заявителю настоящего изобретения. Однако необходимо подчеркнуть, что, в противоположность схемам с деструктивным считыванием, в устройстве по изобретению считывание полной строки в сочетании с мультиплексированием может быть осуществлено без потери данных. Поскольку в данном случае считывание является бездеструктивным, ячейки на линиях данных, которые не адресуются посредством переключателей (маршрутизаторов) в конкретном цикле считывания, сохраняют свое логическое состояние. Таким образом, считывание полной строки ячеек может осуществляться путем многократного возбуждения полной управляющей линии в сочетании с последовательным считыванием, реализуемым считывающим усилительным контуром (или контурами).

Для специалистов в соответствующей области должно быть очевидно, что описанные варианты реализации способа и устройства по изобретению приведены только в качестве примеров и ни в коем случае не должны рассматриваться как вносящие какие-либо ограничения. Должно быть понятно, что специалисты в данной области могут предложить другие схемы для выполнения необходимых функций переключений и мультиплексирования, а также драйверных функций, реализуемых при осуществлении способа по настоящему изобретению, без наложения каких-либо ограничений на данный способ и с достижением главной цели изобретения, состоящей в исключении емкостных связей в памяти с пассивной матричной адресацией, состоящей из набора конденсатороподобных структур, содержащих поляризуемый запоминающий материал, за счет обеспечения нулевой разности потенциалов на невыбранных ячейках.

Изобретение относится к способу определения логического состояния выбранных ячеек памяти, имеющихся в запоминающем устройстве с матричной адресацией. Техническим результатом является возможность бездеструктивного считывания логического состояния выбранных ячеек памяти, адресуемых по схеме пассивной матричной адресации, и отсутствие необходимости обратной записи после каждой операции считывания. Устройство для определения логического состояния выбранных ячеек памяти в запоминающем устройстве с пассивной матричной адресацией выполнено подключаемым к ферроэлектрическому запоминающему устройству или образующим его часть и содержит считывающие усилительные контуры, синхронный усилитель, комбинированный источник напряжения смещения и сигнала, драйвер активной управляющей линии, мультиплексор, комплект маршрутизаторов. Другой вариант указанного устройства дополнительно снабжен вторым комплектом маршрутизаторов. Способ описывает работу указанных устройств. 3 н. и 22 з.п.ф-лы, 11 ил.

| US 5666305 A, 09.09.1997.RU 2143752 C1, 27.12.1999.JP 6275062 A, 30.09.1994.JP 5129622 A, 25.05.1993.JP 8102182 A, 16.04.1996. |

Авторы

Даты

2005-10-27—Публикация

2002-02-15—Подача