Область техники, к которой относится изобретение

Настоящее изобретение относится к способу управления набором ячеек памяти или дисплеем с пассивной матричной адресацией, содержащими электрически поляризуемый материал, обладающий гистерезисом, преимущественно ферроэлектрический материал. При этом состояние поляризации индивидуальных, отдельно выбираемых ячеек может быть переключено желаемым образом путем подачи электрических потенциалов или напряжений на управляющие (числовые) шины и шины данных (разрядные шины), формирующие матрицу адресации. Способ предусматривает также введение протокола подачи импульсов напряжения с n уровнями напряжения или потенциала (n≥ 3) таким образом, что указанный протокол задает временную последовательность для индивидуального управления уровнями напряжения, подаваемого на управляющие шины и шины данных координированным во времени образом. Указанные последовательности включают в себя, по меньшей мере, две отличные друг от друга части, образующие "цикл считывания", в течение которого производят детектирование заряда, текущего между указанными выбранными шинами (или выбранной шиной) данных и ячейками, подключенными к указанным шинам (или шине) данных, и "цикл восстановления/записи", в течение которого состояние (состояния) поляризации в ячейках, подключенных к выбранным управляющим шинам (шине) и шинам (шине) данных, приводят в соответствие с набором заданных логических состояний или информационных значений.

Более конкретно настоящее изобретение относится к использованию двух наборов параллельных электродов для индивидуальной адресации точек скрещивания в пассивных матрицах, используемых для целей хранения и отображения данных (далее для упрощения изложения вместо понятия "скрещивание" будет использоваться более употребительное, хотя и менее строгое понятие "пересечение"). Серьезной проблемой в подобных случаях является устранение возмущений для неадресуемых точек пересечения в той же матрице. Другая важная проблема заключается в минимизации накопленного сигнала от неадресуемых ячеек в подобных матрицах во время считывания записанных в них данных. Типичные применения относятся (не ограничиваясь ими) к матрицам, содержащим тонкую ферроэлектрическую пленку, которая действует в качестве материала энергонезависимой (долговременной) памяти.

Уровень техники

Пассивная матричная адресация подразумевает использование двух наборов параллельных электродов, которые пересекаются, как правило, ортогонально, образуя матрицу точек пересечения. Индивидуальное обращение к точкам пересечения может устанавливаться электрическим путем за счет селективного возбуждения соответствующих электродов с краев матрицы. Достоинства такой схемы включают простоту изготовления и высокую плотность расположения точек пересечения при условии, что функциональность матричного устройства может быть обеспечена посредством двухтерминальных соединений в каждой точке пересечения. Особый интерес в данном контексте представляют применения в дисплеях и запоминающих устройствах, связанные с использованием матриц, в которых электроды в каждой точке пересечения расположены с обеих сторон материала, т.е. образуют структуру, подобную конденсатору (и называемую далее "ячейкой"), а материал ячеек обладает поляризуемостью и гистерезисом.

Последнее свойство придает рассматриваемым устройствам свойство долговременности, т.е. они проявляют эффект памяти в отсутствие приложенного электрического поля. При создании разности потенциалов между электродами выбранной ячейки материал ячейки подвергается воздействию электрического поля, что вызывает поляризационный отклик материала. Тем самым могут быть заданы и сохранены желаемые направление и уровень поляризации. Применительно к памяти или управлению яркости дисплея эти параметры могут, например, соответствовать логическим "0" и "1". Аналогичным образом состояние поляризации данной ячейки может быть изменено или определено путем повторного приложения напряжений к двум электродам, служащим для адресации этой ячейки.

Примеры пассивных матричных устройств, использующих ферроэлектрические запоминающие вещества, могут быть обнаружены в литературе, опубликованной 40-50 лет назад. Так, память на основе титаната бария была описана в работе W.J.Merz and J.R.Anderson, "Ferroelectric storage devices", Bell.Lab.Record. 1, pp.335-342 (1955). Вскоре после нее были опубликованы и другие аналогичные работы (см., например, С.F.Pulvari "Ferroelectrics and their memory applications", IRE Transactions CP-3, pp.3-11(1956) и D.S.Campbell "Barium titanate and its use as a memory store", J. Brit. IRE 17 (7) pp.385-395 (1957)). Пример дисплея с пассивной матричной адресацией, энергонезависимость которого достигнута применением ферроэлектрического материала, может быть найден в патенте США № 3725899, выданном по заявке, которая была подана в 1970 г.

С учетом длительной истории развития и очевидных преимуществ представляется удивительным, что принцип пассивной матричной адресации применительно к ферроэлектрикам не получил большего развития в технологическом и коммерческом аспектах. Хотя важные причины для такого положения могут быть обнаружены в отсутствие ферроэлектрических материалов, которые удовлетворяют широкому диапазону минимальных технических и экономических требований в отношении рассматриваемых устройств, основным фактором явились определенные негативные свойства, присущие пассивной матричной адресации. Среди этих свойств выделяется проблема возмущений в неадресуемых точках пересечения. Данное явление хорошо известно и широко освещено в литературе применительно как к дисплеям, так и к матричной памяти. В данном описании это явление не обсуждается, но приводятся ссылки на соответствующие источники: A. Sobel, "Some constraints on the operation of matrix displays", IEEE Trans. Electron Devices (Corresp.) ED-18, p.797 (1971) и L.E.Tannas Jr., "Flat panel displays and CRTs", pp.106 & seq., (Van Nostrand 1985). В зависимости от типа рассматриваемого устройства могут быть заданы различные критерии по устранению или уменьшению возмущений для неадресуемых точек. Как правило, стремятся понизить чувствительность каждой ячейки в матрице по отношению к слабым возмущениям. Этого можно достичь использованием ячеек, отклик которых является нелинейным по напряжению-току, например, благодаря заданию порога, выпрямлению и/или различным формам гистерезиса.

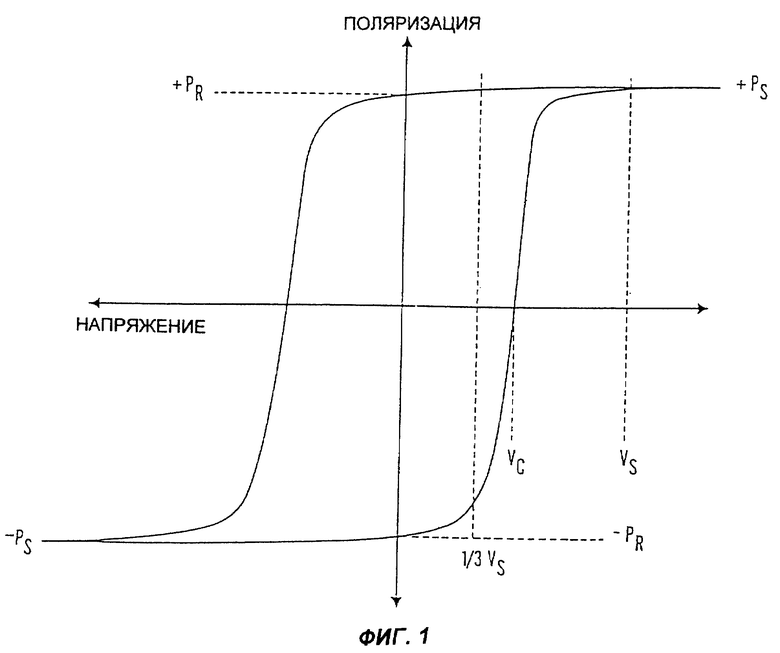

Хотя настоящее изобретение ориентировано на широкое применение, основное внимание будет сконцентрировано на ферроэлектрических запоминающих устройствах, в которых на тонкую пленку ферроэлектрического материала оказывается стимулирующее воздействие в точках пересечения, образующих матрицу, причем при таком воздействии наблюдается петля гистерезиса, представленная в общем виде на фиг.1. В типичном случае запись бита информации осуществляется путем приложения к противоположным сторонам пленки различных напряжений в точке пересечения, в результате чего ферроэлектрик поляризуется или изменяет свою поляризацию. Считывание осуществляется аналогичным образом, т.е. подачей напряжения соответствующего знака, что приводит либо к сохранению той же поляризации после снятия напряжения, либо к ее переключению на противоположное направление. В первом случае в качестве реакции на приложенное напряжение будет протекать небольшой ток, тогда как во втором случае изменение поляризации приводит к протеканию тока, превышающего предварительно определенное пороговое значение. В первом случае точка пересечения может быть (достаточно произвольно) определена, как представляющая "0", а во втором - "1".

Материал, характеризующийся кривой гистерезиса, подобной показанной на фиг.1, будет изменять направление поляризации при приложении электрического поля, превышающего Vc. Однако частичное переключение поляризации будет иметь место и при приложении напряжений, которые меньше указанного значения. Степень изменения поляризации будет зависеть от используемого материала. Таким образом, в матрице с большим количеством точек пересечения повторная стимуляция неадресуемых точек пересечения может в конце концов привести к деградации состояний поляризации в матрице до уровня, при котором возникают ошибки считывания. Количество и тип стимулирующих воздействий, полученных неадресуемыми точками пересечения в пассивной матрице со скрещенными электродами, зависят от режима управления напряжениями на всех шинах (линиях) адресации в процессе выполнения описанных операций (далее этот режим будет именоваться "протоколом подачи импульсов напряжения" или, для краткости, "протоколом переключении" или "протоколом"). Выбор протокола подачи импульсов напряжения зависит от ряда факторов, причем в литературе предлагались различные схемы подачи импульсов, ориентированные на применения, связанные с запоминающими материалами, обладающими гистерезисом. Далее будут рассмотрены несколько примеров, соответствующих уровню техники.

В патенте США № 2942239 описаны протоколы подачи импульсов напряжения для запоминающих устройств с набором магнитных сердечников, каждый из которых имеет кривую гистерезиса, подобную кривой для ферроэлектрика, показанной на фиг.1. Изобретение по данному патенту описано как применимое к элементам памяти, имеющим два сохраняющихся (остаточных) состояния поляризации, в том числе к ферроэлектрикам. Однако оно содержит только указания, относящиеся к хранению данных на магнитных носителях в случае, когда суммарный магнитный поток в каждой ячейке формируется путем сложения или вычитания воздействий, осуществляемых по нескольким независимым шинам, пересекающимся в каждой ячейке. Это проявляется в том, как соединены ячейки в соответствии с предпочтительными вариантами выполнения. При этом протокол считывания предусматривает наложение медленного (или "фонового") стимула, подаваемого на все ячейки в матрице или на их определенное подмножество (например, на строку или столбец), и быстрого "выбирающего" импульса, который прикладывается к пересекающимся шинам (линиям), связанным с адресуемой ячейкой. Не приводится никаких указаний в отношении эффективных протоколов подачи импульсов напряжения, применимых к двухтерминальным ячейкам памяти типа конденсатора и сочетающих высокую скорость и произвольный доступ к данным с восстановлением информации, считанной деструктивным методом.

В патенте США № 3002182 рассматривается проблема потери поляризации при частичном переключении ферроэлектрических ячеек памяти в наборах конденсаторов с ферроэлектрическим заполнением и с пассивной матричной адресацией. Чтобы уменьшить указанные потери при частичном переключении в процессе записи, названный патент рекомендует одновременную подачу импульсов адресации к адресуемым строке и столбцу таким образом, что импульсы первой группы обеспечивают скачок потенциала в типичном случае с +2Vs/3 до +3Vs/4 (где Vs - это номинальное напряжение переключения поляризации - см. фиг.1), тогда как импульсы второй группы обеспечивают переход к отрицательному значению, достаточному для того, чтобы разность потенциалов между электродами в выбранной точке пересечения достигла значения Vs. В то время как остальные столбцы находятся под потенциалом в интервале от +Vs/3 до +Vs/4, только одна выбранная ячейка в матрице подвергается воздействию значительного переключающего поля, при этом частичное переключение в других точках пересечения существенно снижается (степень этого снижения существенно зависит от свойств ферроэлектрика, в частности, от формы его петли гистерезиса и от значения диэлектрической постоянной).

Применительно к альтернативной схеме подачи импульсов тот же патент рекомендует подачу после каждой операции записи дополнительных "импульсов, компенсирующих возмущения", в результате чего потенциал выбранной строки фиксируется на нулевом уровне, а на выбранные и невыбранные столбцы подаются импульсные напряжения, в интервалах от +Vs/3 до +Vs/4 и от -Vs/3 до -Vs/4 соответственно. Утверждается, что последняя операция дополнительно снижает потери поляризации, обусловленные индуцированной частичной поляризацией. Однако не приводится никакого физического обоснования для описанной схемы выбора напряжений, которая представляется в значительной степени основанной на эмпирическом опыте изобретателя при работе с ферроэлектрическими материалами того периода, в частности с титанатом бария.

Хотя базовый выбор полярностей представляется реалистичным и даже интуитивно понятным специалистам в области ферроэлектриков, приведенного описания недостаточно для того, чтобы получить адекватные, т.е. достаточно общие, но применимые в конкретных случаях рекомендации по выбору величин импульсов и их распределения во времени. Для считывания записанной информации или для очистки ячеек перед операцией записи рассматриваемое изобретение предлагает приложение полного напряжения -Vs переключения к выбранной строке (строкам), причем эта рекомендация упоминается, как "хорошо известная в данной отрасли". Выбор напряжений, подаваемых на электроды выбранных столбцов, обсуждается весьма нечетко. Может сложиться впечатление, что потенциал электродов выбранных столбцов фиксируется на нулевом уровне, тогда как невыбранные столбцы находятся под потенциалом от -Vs/3 до -Vs/4 (см. фиг.4В указанного патента). Однако такой выбор приводит к нагрузке на невыбранные ячейки в той же строке, что и выбранная, составляющей от 2Vs/3 до 3Vs/4, т.е. создающей очевидную опасность частичного переключения. Таким образом, создается впечатление, что данное изобретение плохо подходит для ситуаций, в которых между циклами записи имеет место большое количество операций считывания. При этом возникают сомнения в том, применимо ли оно для реальных ферроэлектрических устройств.

В патенте США № 3859642 описана концепция построения памяти, основанной на схеме с пассивной матричной адресацией, в которой набор конденсаторов с программируемой двухуровневой емкостью подвергается во время цикла считывания двухуровневому возбуждению. Функция памяти реализуется использованием двух устойчивых состояний конденсаторов. Принимается, что используются конденсаторы типа МДП (т.е. имеющие структуру металл-диэлектрик-полупроводник) или эквивалентные им, обладающие петлей гистерезиса, центрированной относительно напряжения смещения и существенно сдвинутой относительно точки с нулевым смещением. Запись данных осуществляется путем подачи на шины строки и столбца, пересекающиеся на выбранном конденсаторе, напряжений +V и -V соответственно, чередующихся с напряжениями -V и +V соответственно, в зависимости от того, какое из двух бистабильных состояний нужно записать. Результирующий диапазон напряжений, подаваемых на выбранный конденсатор, составляет таким образом ± 2V и не превышает по абсолютному значению V для невыбранных конденсаторов. При этом значение V задается как лежащее ниже порога для записи. Частичная запись, очевидно, не рассматривается как проблема, и никаких конкретных указаний в этой связи не приводится, если не считать уже рассмотренной простой схемы. Таким образом, содержание патента США № 3859642 не может рассматриваться как вклад в уровень техники, имеющий какую-либо ценность в отношении задач, решаемых настоящим изобретением.

В патенте США № 4169258 описана схема выбора напряжений, кратных одной трети, для адресации к ферроэлектрической матрице. В данном случае для подачи импульсных напряжений на шины х, у в схеме пассивной матричной адресации используется протокол, согласно которому на все шины х, у скоординированным образом подают униполярные напряжения, соответствующие уровням 0, 1/3, 2/3 и 1.

При этом уровень "1" соответствует номинальной амплитуде импульсов, используемых для перевода выбранной ячейки из логического состояния "ВЫКЛ" ("OFF") в состояние "ВКЛ" ("ON") или наоборот. При этом типичное коэрцитивное напряжение находится в интервале от 1/2 до 2/3. Важным ограничением схемы, описанной в данном патенте, является то, что протоколы подачи импульсов напряжения разработаны для случая, когда все ячейки имеют одинаковые исходные значения степени и направления поляризации ("ВЫКЛ"). Это значит, что вся матрица должна быть приведена в данное состояние, прежде чем в ячейки матрицы будет записан новый вариант их состояний. Более того, любое состояние "ВКЛ" на той же у-шине, что и адресуемая ячейка, будет получать возмущающий импульс, соответствующий уровню 2/3 в направлении "ВЫКЛ", который для большинства известных ферроэлектриков приводит к частичному переключению поляризации. Хотя подобные ограничения могут быть приемлемы для некоторых типов дисплеев и запоминающих устройств, для большинства применений они являются недопустимыми.

Полная очистка памяти не требуется при осуществлении способа, подробно описанного в упомянутом патенте США № 4169258 и обозначенного, как "схема с выбором половинного напряжения". Однако в этой схеме невыбранные ячейки подвергаются воздействию возмущающих импульсов, имеющих относительный уровень, равный 1/2. Это обстоятельство обычно рассматривается как неприемлемое для всех практических применений запоминающих устройств, использующих традиционные ферроэлектрические материалы, такие как неорганические керамики. Кроме того, указанная схема описана только в терминах одиночных актов переключения в адресуемых ячейках, которые разрушают состояния поляризации, имевшие место на момент переключения.

Протокол подачи трехуровневых импульсов напряжения описан в патенте США № 5550770. Данный протокол тесно увязан с тем, что соответствующее ему активное ферроэлектрическое запоминающее устройство имеет более высокий уровень интеграции, чем обычные активные ферроэлектрические матрицы с ячейками памяти типа 1Т-1С. Согласно указанному патенту запоминающее устройство сегментируется на блоки памяти таким образом, что все шины данных присоединены к переключающему элементу в виде полевого транзистора, преимущественно типа IGFET (полевой транзистор с изолированным затвором). В результате обеспечивается получение матричной памяти с уменьшенным количеством переключающих элементов или транзисторов, связанных с ячейками памяти, чем в предшествующих активных матричных запоминающих устройствах. Все управляющие шины и шины данных в устройстве по данному патенту перед началом цикла записи или считывания находятся под нулевым электрическим потенциалом.

Для того чтобы инициализировать цикл записи или чтения, транзисторы должны быть открыты путем подачи напряжения, уровень которого должен соответствовать сумме напряжения V0 переключения поляризации и эффективного порогового напряжения для транзистора IGFET. При этом выбор управляющей шины производится посредством декодера управляющей шины. Одиночная шина данных выбирается путем перевода первого переключающего транзистора в открытое состояние (ВКЛ) при удерживании второго переключающего транзистора в закрытом состоянии (ВЫКЛ). Оба эти транзистора включены между каждой шиной данных и выходом декодера шины данных. Соответственно отказ от выбора шины данных производится переводом первого транзистора в состояние ВЫКЛ, а второго - в состояние ВКЛ. Для циклов записи и считывания в рамках протокола подачи импульсов напряжения используется трехуровневая схема, включающая в себя так называемую схему выбора половинных напряжений. При этом утверждается, что так называемая "нагрузка" на невыбранные управляющие шины и шины данных в данном запоминающем устройстве становится сопоставимой с "нагрузкой", имеющей место в полностью активной памяти матричного типа, т.е. в памяти с ячейками типа 1Т-1С.

Как явным образом отмечено в столбце 17 описания патента, предложенный в нем протокол подачи импульсов напряжения представляется вряд ли пригодным для ферроэлектрической памяти с пассивной матричной адресацией типа обозначенного в таблице 1 в том же столбце описания, как известное решение 1. Таким образом, преимущество более высокой степени интеграции, достигнутое в устройстве по рассматриваемому патенту, до некоторой степени ослабляется необходимостью прибегать к такой схеме выбора ячейки памяти, которая требует сначала выбрать блок памяти, а затем выбрать управляющие шины способом, известным из уровня техники. При этом для выбора шин данных должен применяться селектор, снабженный двумя переключающими полевыми МОП-транзисторами для каждой шины данных в столбце блока. Именно это позволяет применить в известном устройстве трехуровневый протокол, использующий напряжение Vs/2 (V0/2 в системе обозначений, принятых в данном патенте), что приводит к уровню возмущений "нагрузки" на неадресуемых ячейках памяти, сопоставимому с аналогичным уровнем в полностью активной памяти матричного типа. Следует также отметить, что рассматриваемое решение не обеспечивает параллельную запись и считывание, а допускает только побитовое считывание и запись, поскольку к каждому столбцу блока может быть подключен только один усилитель считывания. Разумеется, при этом отмечается возможность вести одновременно запись и считывание индивидуальных ячеек в других блоках (сегментах) описанной матричной памяти.

Таким образом, существует очевидная потребность в дальнейшем усовершенствовании различных запоминающих устройств и дисплеев с пассивной матричной адресацией в ситуациях, когда нужно обеспечивать изменение логического содержания индивидуальных ячеек без создания возмущения для других ячеек или возможность очистки или возврата в исходное состояние устройства в целом.

Сущность изобретения

В связи с этим главная задача, на решение которой направлено настоящее изобретение, состоит в том, чтобы разработать протоколы подачи импульсов напряжения в функции от времени для управления шин х и у матрицы с пассивной адресацией в устройствах с постоянной памятью, характеризующихся кривыми гистерезиса ферроэлектрического типа, обеспечивающие минимизацию возмущений для невыбранных ячеек памяти при записи данных в память устройства, а также при считывании данных из памяти.

Следующей задачей является разработка подобных протоколов, которые обеспечивают ослабление переходных токов зарядки/разрядки и тем самым способствуют достижению высокого быстродействия.

Еще одна задача заключается в разработке протоколов указанного типа, которые позволяют применить простые, надежные и недорогие электронные контуры для осуществления операций управления и считывания в матричных запоминающих устройствах.

Решение перечисленных задач, а также другие преимущества достигнуты благодаря созданию способа в соответствии с настоящим изобретением. Данный способ характеризуется тем, что один из используемых уровней напряжения выбирают соответствующим нулевому значению, другой из указанных уровней напряжения выбирают равным напряжению Vs переключения поляризации и, по меньшей мере, один дополнительный уровень напряжения выбирают в интервале между 0 и Vs. В случае, когда протокол подачи импульсов напряжения предусматривает более чем 3 уровня напряжения, выбирают, по меньшей мере, еще один дополнительный уровень напряжения в интервале между 0 и Vs или выбирают, по меньшей мере, еще один дополнительный уровень напряжения в интервале между 0 и Vs и один дополнительный уровень напряжения, превышающий Vs, тогда как интервалы между смежными уровнями напряжения во всех случаях выбираются одинаковыми.

В качестве пары или пар активных уровней напряжения выбирают одну или более пар уровней напряжения таким образом, что разность потенциалов между уровнями напряжения в указанной одной или более парах активных уровней напряжения равна или превышает Vs. В качестве исходных уровней напряжения выбирают один или более уровней напряжения таким образом, что, по меньшей мере, один исходный уровень имеет значение в интервале между 0 и Vs.

Далее, согласно изобретению выбирают индивидуальные ячейки памяти для осуществления операции адресации в форме записи данных в указанные ячейки или считывания данных из указанных ячеек в рамках протокола подачи импульсов напряжения путем подачи каждого из уровней напряжения, образующих пару указанных активных уровней, на управляющую шину и шину данных, пересекающиеся на ячейке, подлежащей выбору, и удерживают перед инициализацией цикла считывания или записи все управляющие шины и шины данных защелкнутыми на одном или более исходных уровнях напряжения.

Затем выполняют операцию записи в цикле записи, входящем в указанную последовательность импульсов, путем защелкивания управляющей шины на одном из уровней из пары указанных активных уровней напряжения и одной или более шин данных на другом уровне из пары указанных активных уровней напряжения или на одном из исходных уровней, близком, насколько это возможно, к уровню напряжения, поданному на указанную управляющую шину, с активацией тем самым управляющей шины и шины или шин данных для выполнения операции записи в выбранную ячейку памяти путем либо установления заданного состояния поляризации в ячейке, либо изменения существующего состояния поляризации в ячейке, либо сохранения существующего состояния поляризации в ячейке неизменным. Заданное состояние поляризации определяется как соответствующее некоторым данным, хранящимся в ячейке. Неактивные управляющие шины и неактивные шины данных при выполнении операции записи защелкнуты на указанном, по меньшей мере, одном исходном уровне напряжения или, в случае использования более чем одного исходного уровня напряжения, переключаются с исходного уровня напряжения на другой исходный уровень напряжения или на иной уровень напряжения. В любом случае разность между указанными уровнями напряжения не превышает Vs.

Согласно изобретению в цикле считывания, входящем в указанную последовательность импульсов, выполняют операцию считывания путем защелкивания управляющей шины и одной или более шин данных на одном из уровней из пары указанных активных уровней напряжения и детектирования заряда, текущего между одной или более активными шинами данных и соответственно одной или более ячейками памяти, соединенными с указанной шиной или шинами данных и характеризующего состояние поляризации соответственно одной или более ячеек памяти, которое определяется как соответствующее некоторым данным, хранящимся в ячейке. Неактивные управляющие шины и неактивные шины данных при выполнении операции считывания защелкнуты на указанном, по меньшей мере, одном исходном уровне напряжения. В случае использования более чем одного исходного уровня напряжения и/или более чем одной пары активных уровней эти шины переключаются с исходного уровня напряжения на другой исходный уровень напряжения или на иной уровень напряжения. В любом случае разность между указанными уровнями напряжения не превышает Vs.

После завершения цикла записи или считывания все управляющие шины и шины данных возвращают на исходные уровни напряжения. При этом выбор уровней напряжения для активных шин в соответствии с протоколом подачи импульсов напряжения в любом случае производят с учетом того, должно ли состояние поляризации ячейки памяти быть установленным, остаться неизменным или измененным в результате операции записи. Выбор уровней напряжений, на которые защелкнуты неактивные управляющие шины и шины данных, между исходными уровнями напряжений и другими уровнями напряжения на операциях записи и считывания производят с учетом уровней напряжений, подаваемых при выполнении этих указанных операций на активные управляющую шину и шину данных. Этот учет осуществляют таким образом, чтобы минимизировать емкостные связи между активными и неактивными шинами и возможные возмущения неадресуемых ячеек памяти.

Согласно изобретению представляется предпочтительным предусмотреть возможность изменения напряжения на одной или более шинах данных под влиянием зарядов, текущих между шиной данных и ячейками, соединенными с шиной данных во время цикла считывания при защелкивании всех напряжений на управляющих шинах и шинах данных во время цикла восстановления/записи.

В соответствии с первым предпочтительным вариантом в случае, когда напряжения на неадресуемых ячейках не превосходят существенно Vs/2, причем Vs соответствует напряжению на адресуемой ячейке во время циклов считывания, восстановления и записи, значения n, а также соответствующие значения nWORD и nBIT для управляющих шин и для шин данных выбирают равными 3.

В соответствии со вторым и третьим предпочтительными вариантами в аналогичном случае значения n, nWORD и nBIT, выбирают равными 4 и соответственно 5, 3 и 3.

Далее, согласно изобретению рекомендуется, чтобы неадресуемые ячейки на активной управляющей шине и на активной (активных) шине (шинах) данных во время циклов считывания и записи были подвергнуты воздействию максимального напряжения, значение которого отклоняется на контролируемое приращение от точных значений Vs/2 или Vs/3. Кроме того, рекомендуется подвергнуть неадресуемые ячейки на активной управляющей шине воздействию напряжения, значение которого превышает точные значения Vs/2 или Vs/3 на контролируемое положительное приращение, и одновременно подвергнуть неадресуемые ячейки на выбранных активных шинах данных воздействию напряжения, значение которого выбирают меньшим точных значений Vs/2 или Vs/3 на контролируемое отрицательное приращение. При этом желательно, чтобы контролируемое положительное приращение было выбрано равным контролируемому отрицательному приращению.

В соответствии с изобретением предпочтительно также производить добавление контролируемого положительного приращения δ 1 к потенциалам ФinactiveWL неактивных управляющих шин и добавление контролируемого положительного приращения δ 2 к потенциалам ФinactiveBL неактивных шин данных. Выбор δ 1=δ 2=0 соответствует протоколу подачи импульсов напряжения с максимальным значением напряжения на невыбранных ячейках, составляющим Vs/2 или Vs/3. Однако предпочтительным представляется выбор δ 1=δ 2≠0.

Представляется также целесообразным осуществлять управление потенциалом исходного уровня (т.е. потенциалом, подаваемым на управляющие шины и шины данных в течение промежутка времени между очередными использованиями протокола подачи импульсов напряжения) таким образом, чтобы его значения являлись одинаковыми для всех управляющих шин и шин данных и соответствующими нулевому напряжению на всех ячейках. Кроме того, целесообразно, чтобы потенциалы исходного уровня на одной или более управляющих шинах и шинах данных выбирались равными одному из следующих значений: а) нулевому потенциалу, б) потенциалу адресуемой управляющей шины в момент инициирования протокола подачи импульсов напряжения, в) потенциалу адресуемой шины данных в момент инициирования протокола подачи импульсов напряжения, г) напряжению питания Vcc. В предпочтительном варианте потенциал исходного уровня на одной или более выбранных шинах данных выбирают таким образом, что он отличается от потенциала на момент начала периода изменения напряжения (цикла считывания). При этом потенциал исходного уровня изменяют до значения, соответствующего началу периода изменения напряжения, когда это значение защелкивается на период времени, сравнимый с постоянной времени зарядки шины (шин) данных, или превосходит указанную постоянную времени ("импульс предварительной зарядки").

Далее, в соответствии с изобретением рекомендуется осуществлять перед циклом считывания изменение напряжения на неактивных управляющих шинах. В результате неадресуемые ячейки на активной шине данных подвергаются воздействию напряжения смещения, равного напряжению, имеющему место на активной шине данных во время цикла считывания. Указанное изменение напряжения на неактивных управляющих шинах начинают в выбранный момент, предшествующий указанному изменению напряжения на активной шине данных. Завершают данное изменение в момент инициирования указанного изменения напряжения на активной шине данных таким образом, что воспринимаемое напряжение смещения на указанных неадресуемых ячейках на активной шине данных подается постоянно с момента инициирования указанного изменения напряжения на неактивных управляющих шинах и до момента завершения указанного изменения напряжения на активной шине данных ("импульс предварительной зарядки").

В заключение, рекомендуется осуществлять предварительный цикл считывания, который предшествует циклу считывания и отделен от него выбранным временным интервалом. Предварительный цикл считывания точно воспроизводит протокол подачи импульсов напряжения и детектирования тока в цикле считывания, но отличается тем, что во время предварительного цикла считывания не производят никакого изменения напряжения на активной управляющей шине. Сигнал, зарегистрированный во время предварительного цикла считывания, используют в качестве входных данных для контура, определяющего логическое состояние или содержание данных в адресуемой ячейке. Согласно предпочтительному варианту этот сигнал вычитают из сигнала, зарегистрированного во время цикла считывания.

Перечень фигур чертежей

Далее будут подробно описаны основные принципы изобретения и приводимые только в качестве примеров предпочтительные варианты его осуществления, которые рассматриваются со ссылками на прилагаемые чертежи.

На фиг.1 представлена иллюстрация принципа кривой гистерезиса для ферроэлектрического запоминающего материала.

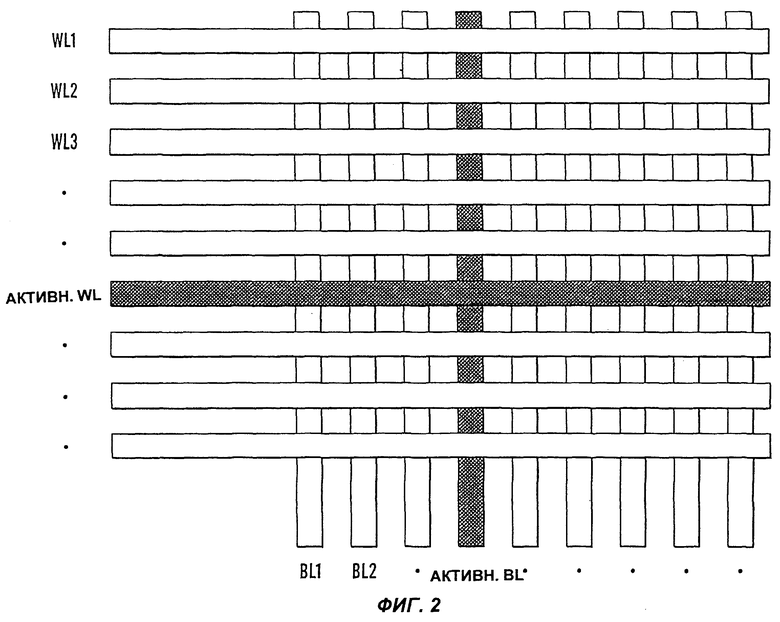

Фиг.2 иллюстрирует принцип пассивной матричной адресации с пересекающимися электродными шинами и с ячейками, содержащими ферроэлектрический материал, расположенный между электродами в зонах их взаимного наложения.

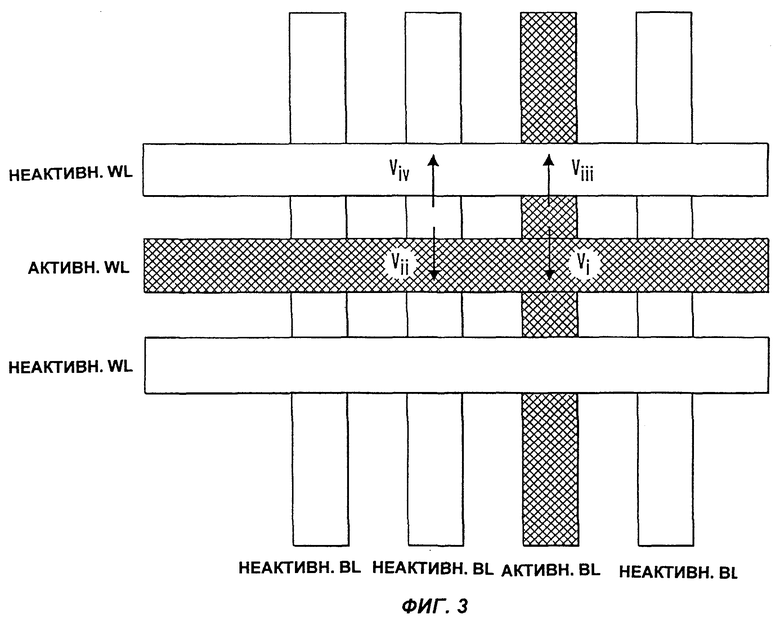

Фиг.3 иллюстрирует сумму приращений напряжения вдоль замкнутой петли в матрице.

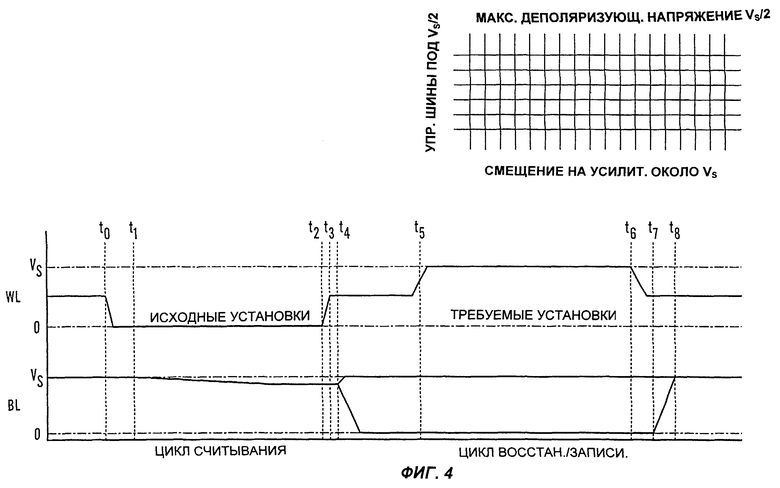

На фиг.4 представлен протокол считывания и записи, требующий контроля за тремя дискретными уровнями напряжения на управляющих шинах и шинах данных.

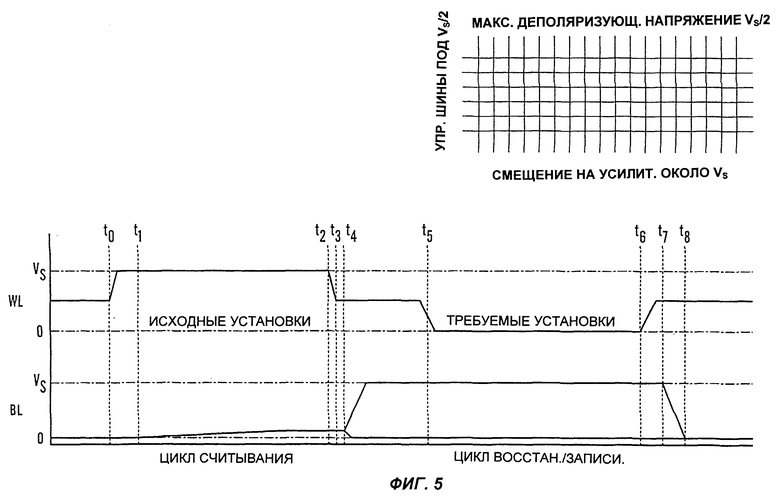

На фиг.5 представлен трехуровневый протокол, альтернативный по отношению к протоколу по фиг.4.

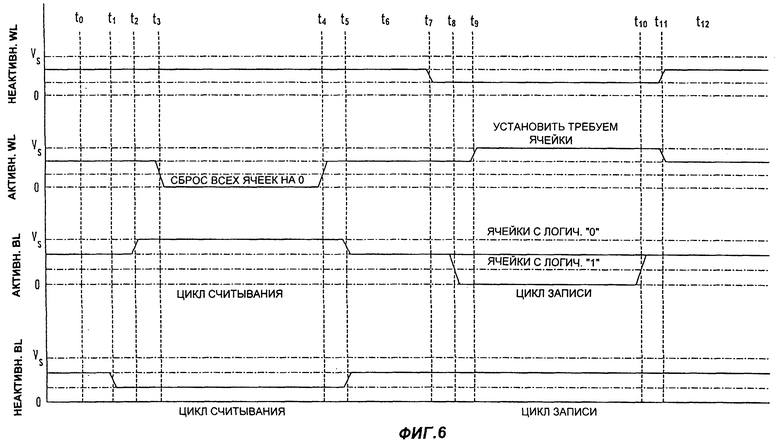

На фиг.6 представлен протокол считывания и записи, требующий контроля за четырьмя дискретными уровнями напряжения на управляющих шинах и шинах данных.

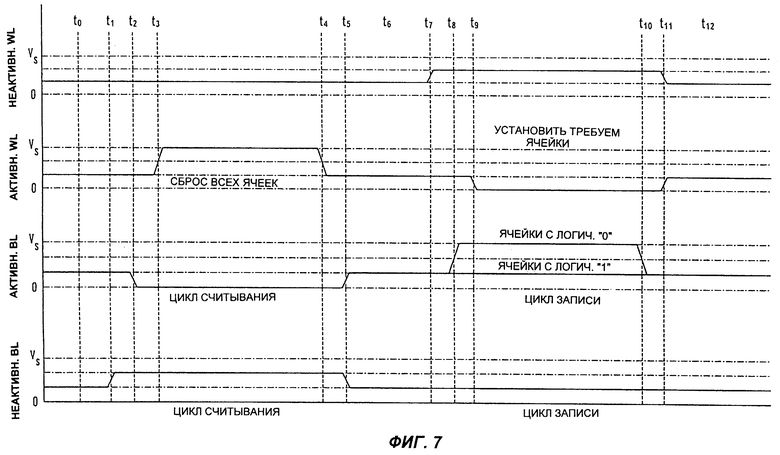

На фиг.7 представлен четырехуровневый протокол, альтернативный по отношению к протоколу по фиг.6.

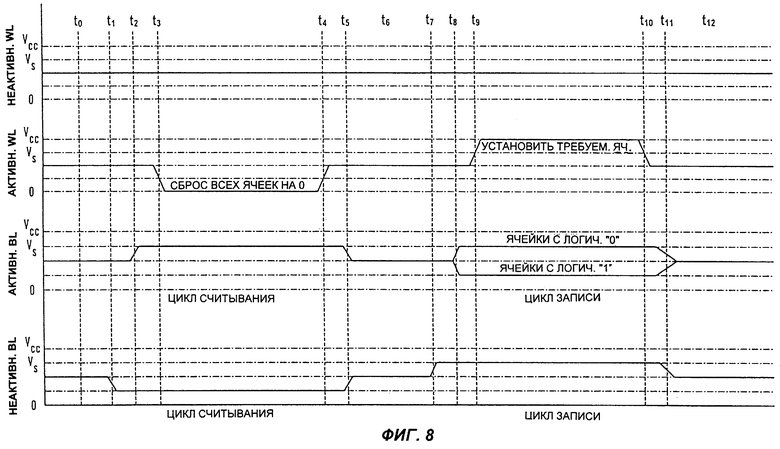

На фиг.8 представлен протокол считывания и записи, требующий контроля за пятью дискретными уровнями напряжения на управляющих шинах и шинах данных.

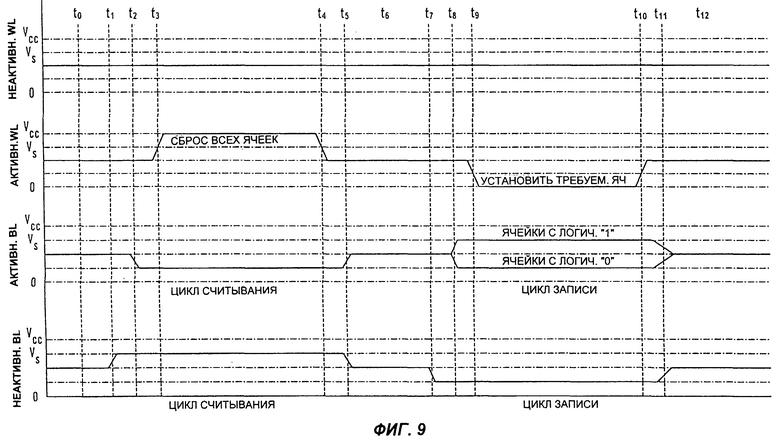

На фиг.9 представлен пятиуровневый протокол, альтернативный по отношению к протоколу по фиг.8.

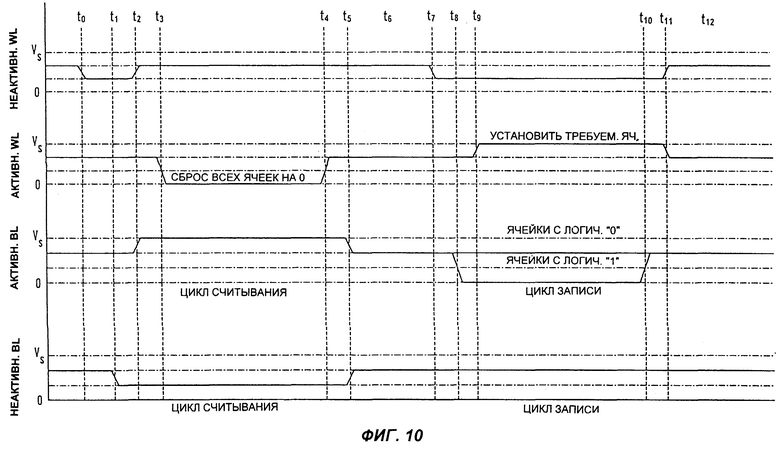

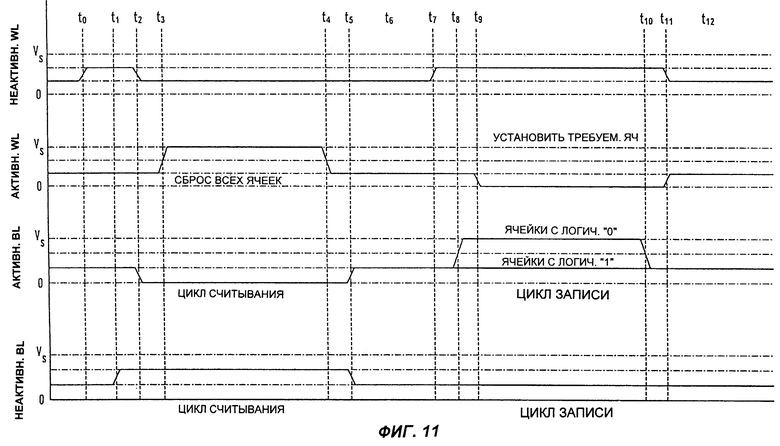

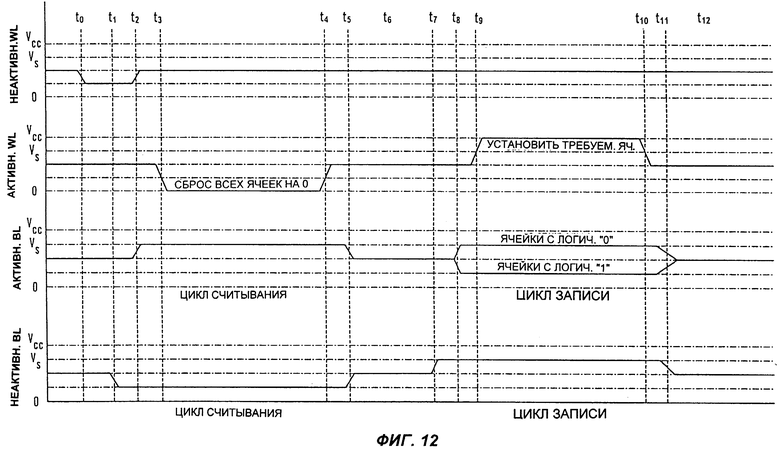

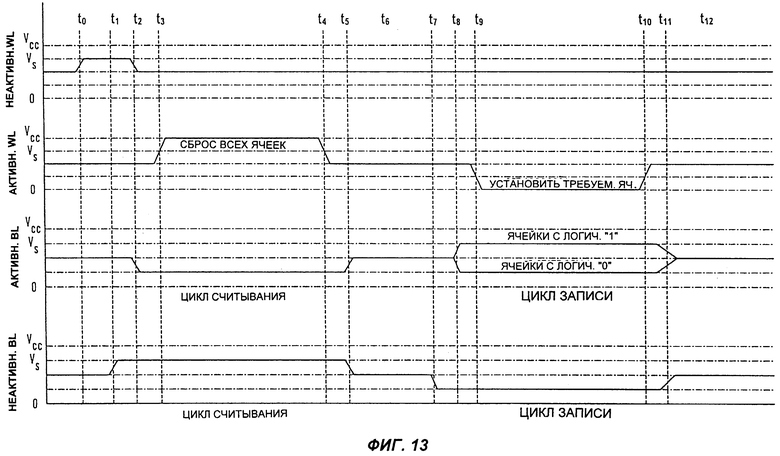

На фиг.10-13 представлены протоколы, альтернативные по отношению к протоколам по фиг.6-9 и отличающиеся наличием импульсов предварительной зарядки на неактивных управляющих шинах.

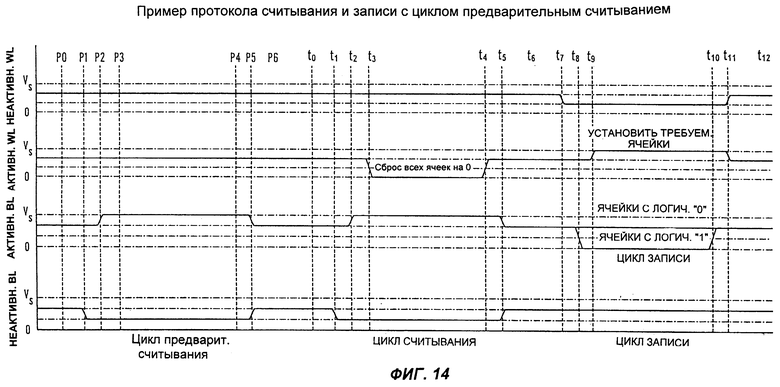

На фиг.14 приведен пример протокола считывания и записи, предусматривающий цикл предварительного считывания.

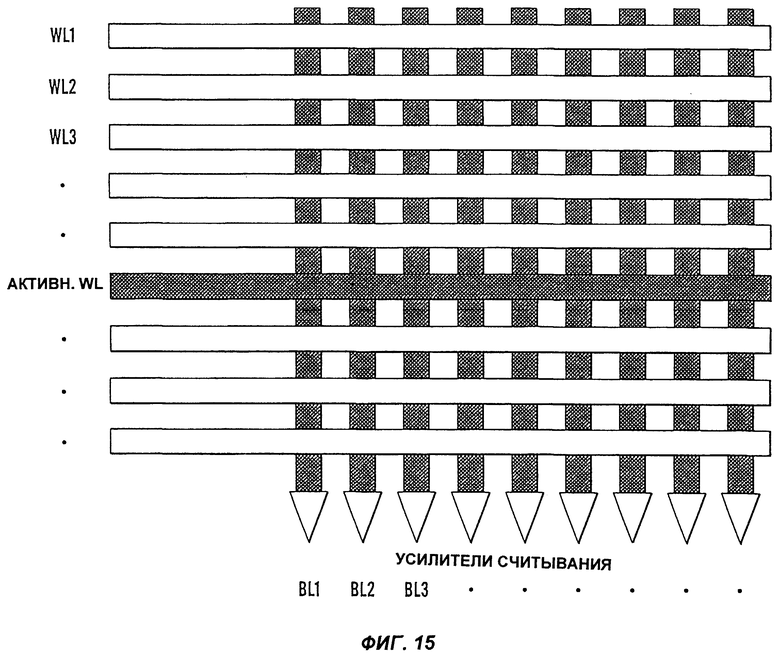

Фиг.15 соответствует схеме считывания, основанной на параллельном детектировании по всей строке.

Сведения, подтверждающие возможность осуществления изобретения

Далее будут достаточно подробно описаны основные принципы настоящего изобретения. Существенным аспектом изобретения является обеспечение координированного управления во времени напряжениями на всех шинах х, у (х-, у-шинах, или линиях) в матрице в соответствии с одним из протоколов, которые будут рассмотрены ниже. Эти протоколы гарантируют, что ни одна неадресуемая ячейка (точка пересечения) в матрице не испытывает воздействия межлинейного напряжения, превосходящего некоторое заданное значение, которое существенно меньше уровня, при котором имеет место возмущение или частичное переключение.

Должно быть понятно, что материалы, реализующие функцию памяти в дисплеях и запоминающих устройствах, рассматриваемые в контексте изобретения, обладают гистерезисом типа изображенного в общем виде на фиг.1. Релевантными материалами в этом плане являются электреты, ферроэлектрики и комбинации этих двух материалов. Для упрощения понимания далее в описании будет предполагаться, что таким материалом служит ферроэлектрик, но это не должно рассматриваться, как ограничение широкого объема изобретения.

Принимается также, что в результате предшествующего воздействия электрических полей материал в условиях нулевого внешнего поля находится в одном из двух состояний поляризации, представленных на фиг.1 точками +РR и -PR. Подача напряжения на ячейку, содержащую ферроэлектрический материал, заставляет ее изменить свое состояние поляризации, которое смещается по кривой гистерезиса хорошо известным специалистам в области ферроэлектриков образом. Для удобства изложения на фиг.1 по оси абсцисс вместо напряженности электрического поля отложены значения напряжения.

Далее применительно к конфигурации пассивной матрицы будет описан порядок подачи импульсов напряжения на пересекающиеся управляющие шины и шины данных. Эти напряжения подаются таким образом, что для единичной, свободно выбираемой ячейки матрицы разность Vs потенциалов (напряжение) между двумя электродами, пересекающимися в точке, соответствующей ячейке, достаточна для того, чтобы заставить ферроэлектрик переключить направление своей поляризации в положительную или отрицательную сторону (в зависимости от полярности поля, созданного между электродами). При этом после снятия внешнего поля поляризация ферроэлектрика соответствует точке +PR или -PR на кривой гистерезиса. В то же время ни одна ячейка в матрице не будет находиться под разностью потенциалов, которая приводит к недопустимому (относительно заранее заданного критерия) изменению ее состояния поляризации. Выполнение данного условия обеспечивается тем, что разность потенциалов, приложенная к неадресуемым ячейкам ("возмущающее напряжение"), никогда не превышает Vs/m, где m - целое число или нецелое число, типичное значение которого составляет 2 и более.

В зависимости от заданной скорости переключения и других требований номинальное переключающее напряжение Vs, используемое для получения требуемого состояния поляризации ферроэлектрика, в типичном случае выбирается существенно большим, чем коэрцитивное напряжение Vc (см. фиг.1). Однако это напряжение не может быть выбрано произвольно большим, поскольку представляемые в данном описании протоколы подачи импульсов предназначены для уменьшения возмущающего напряжения только до некоторого уровня, соответствующего доле (как правило, 1/3) Vs, причем данный уровень должен быть ниже Vc.

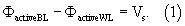

Перед тем как приступить к обсуждению конкретных протоколов, представляется полезным провести рассмотрение связанных с этим проблем в общем виде применительно к матрице, показанной на фиг.2. Для удобства описания в соответствии с общеупотребительной терминологией далее горизонтальные линии ("строки") и вертикальные линии ("столбцы") будут именоваться "управляющими шинами" (сокращенно WL - word lines) и шинами данных (BL - bit lines). В предпочтительном варианте подаваемые напряжения выбираются достаточными для того, чтобы переключить заданную ячейку либо для того, чтобы придать ей требуемое направление поляризации (запись), либо для отслеживания отклика в виде протекания заряда. При этом ячейка выбирается приложением потенциалов к ассоциированным с ней управляющей шине и шине данных ("активным" шинам - см. фиг.2) в соответствии с соотношением:

В то же время многочисленные управляющие шины и шины данных, которые пересекаются на неадресуемых ячейках, должны находиться под потенциалом, меньшим порога для частичного переключения. Каждая из этих "неактивных" управляющих шин и шин данных пересекается соответственно с активной шиной данных и управляющей шиной на неадресуемой ячейке. Обращаясь к фиг.2, можно выделить четыре различных класса ячеек в матрице, характеризующиеся значениями напряжения, приложенного к ячейке:

i) VI=ФactiveBL-ФactiveWL: активная управляющая шина пересекает активную шину данных (выбранная ячейка);

ii) VII=ФinactiveBL-ФactiveWL: активная управляющая шина пересекает неактивную шину данных;

iii) VIII=ФactiveBL-ФinactiveWL: неактивная управляющая шина пересекает нактивную шину данных;

iv) VIV=ФinactiveBL-ФinactiveWL: неактивная управляющая шина пересекает неактивную шину данных.

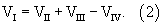

В реальных устройствах в тех случаях, когда желательно минимизировать стоимость и сложность, особый интерес представляет специальный случай, когда все неактивные управляющие шины имеют общий потенциал ФinactiveWL, а все неактивные шины данных имеют общий потенциал ФinactiveBL. Суммируя напряжения по замкнутой петле в матричной сетке типа представленной на фиг.3, получаем следующее соотношение:

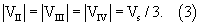

Если VI=Vs, то минимальное напряжение, приложенное к неадресуемым ячейкам, которое может быть достигнуто, составляет:

Для того чтобы это напряжение было достигнуто, на электроды в матрице должны подаваться, по меньшей мере, четыре отдельных потенциала (а именно, Ф0, Ф0+Vs/2, Ф0+2Vs/3, Ф0+Vs, где Ф0 - базовый потенциал). При этом любое изменение потенциала на одном из электродов должно быть скоординировано с настройками других потенциалов для того, чтобы ни на одну ячейку не был подан потенциал, превышающий Vs/3. На практике необходимо принимать во внимание и несколько других факторов, относящихся, в частности, к минимизации переходных токов при переключениях (токов заряда/разряда) и способствующих уменьшению сложности драйверных контуров. В результате могут быть созданы протоколы, подобные описываемым далее. Один из возможных вариантов состоит в общем смещении потенциалов путем добавления или вычитания одного и того же потенциала применительно ко всем четырем уровням.

Пример 1. Трехуровневый протокол переключений (Vs/2)

В некоторых специальных случаях может быть использован упрощенный протокол подачи импульсных напряжений, когда все неактивные управляющие шины и шины данных имеют одинаковый потенциал, т.е. VIV=0. В этом случае минимальное напряжение, которого можно достичь на неадресуемых ячейках, преобразуется к виду:

VII+VIII=Vs/2.

При этом для управления операциями записи и считывания необходимы, по меньшей мере, три отдельных потенциала (а именно, Ф0, Ф0+Vs/2, Ф0+Vs, где Ф0 - базовый потенциал).

Как уже упоминалось, частичное переключение с использованием напряжений на уровне Vs/2 может представлять серьезную проблему, и в таких случаях трехуровневые протоколы становятся неприемлемыми. Однако степень частичного переключения при приложении конкретного напряжения в явном виде зависит от используемого ферроэлектрического материала. Из фиг.1 можно видеть, что материалы, обладающие кривой гистерезиса с формой, близкой к квадратной, способны обеспечить приемлемые показатели во многих применениях.

В последние годы большое внимание в качестве запоминающих сред в новейших системах хранения данных стали привлекать определенные классы ферроэлектриков, такие как органические полимеры. В дополнение к другим привлекательным свойствам эти материалы обладают кривыми гистерезиса, намного более близкими к квадратной форме, чем соответствующие кривые для керамических ферроэлектриков, которые традиционно доминировали в приложениях, относящихся к области энергонезависимых ферроэлектрических запоминающих устройств. По этой причине стала релевантной разработка протоколов подачи импульсных напряжений, соответствующих требованиям реальных и оптимизированных электронных устройств. В связи с существовавшими проблемами частичного переключения, которые затормозили завершение и использование ранних разработок, основанных на трехуровневых протоколах переключения, таким протоколам уделялось очень мало внимания. Настоящее изобретение ставит своей задачей восполнить этот пробел.

Далее будут приведены примеры предпочтительных вариантов.

Фиг.4 и 5 иллюстрируют некоторые трехуровневые протоколы в соответствии с настоящим изобретением, которые охватывают полностью цикл считывания и цикл восстановления/записи. Показаны только диаграммы импульсных напряжений для активных управляющей шины и шины данных. Неактивные управляющие шины, как и неактивные шины данных, могут находиться под стабильным потенциалом Vs/2 на протяжении всего цикла записи/считывания. В альтернативном варианте неактивные шины данных могут быть в течение цикла считывания подключены к отдельному усилителю считывания, который будет находиться под потенциалом, близким к напряжению на шине данных, когда защелка на шине данных снята (считывание с полной строки). На диаграммах, изображенных на фиг.4 и 5, временные маркеры имеют следующие значения:

t0 управляющая шина в защелке, активное снижение напряжения до 0 (фиг.4) или активный подъем до Vs (фиг.5);

t1 защелка на шине данных снята - усилитель считывания включен;

t2 решение относительно шины данных - данные в защелке;

t3 управляющая шина возвращена в исходное состояние Vs/2;

t4 запись данных, находящихся в защелке на шинах данных;

t5 напряжение на управляющей шине доведено до Vs (фиг.4) или до 0 (фиг.5);

t6 управляющая шина возвращена в исходное состояние Vs/2;

t7 шины данных активно возвращены к защелке на Vs (фиг.4) или на 0 (фиг.5);

t8 цикл считывания-записи завершен.

В цикле считывания исследуется состояние поляризации адресуемой ячейки. В зависимости от направления этой поляризации операция считывания может оставить ее неизменной или изменить направление поляризации на противоположное (деструктивное считывание). В последнем случае, если желательно избежать потери хранившейся информации, она должна быть восстановлена (обновлена). Это означает, что в соответствующей ячейке матрицы (необязательно в той же, из которой производилось считывание) поляризация должна изменить направление на противоположное тому, которое придавалось при считывании. Такое изменение осуществляется, как показано на фиг.4, 5, частью протокола, относящейся к восстановлению/записи. Две изображенные ветви этой части протокола для шин данных соответствуют случаям, когда поляризация осталась неизменной и изменила направление. Отдельная операция записи реализуется тривиальным образом путем опускания операции считывания.

Как можно легко видеть из фиг.4 и 5, ни одна неадресуемая ячейка не будет находиться под напряжением, превышающим половину от номинального переключающего напряжения ни при считывании, ни в периоды восстановления/записи. Кроме того, можно видеть, что в последовательности импульсов предусмотрены задержки некоторых событий для того, чтобы облегчить переходные процессы прямого вызова и защелкивания данных. В зависимости от того, каким образом должно функционировать запоминающее устройство, потенциал шины данных в исходном состоянии (или состоянии покоя, т.е. между циклами считывания/восстановления/записи) может быть выбран соответствующим потенциалу шины данных в начале цикла считывания (см. фиг.4 и 5) или потенциалу управляющей шины в исходном состоянии (этот вариант на чертеже не изображен). В первом случае, рекомендуемом в ситуациях, когда цикличность имеет высокую интенсивность и высокую скорость, зарядные токи в начале цикла считывания минимальны. Во втором случае устраняются долгосрочные эффекты поля, наложенного на ячейки (т.е. импринтинг). Из фиг.4 и 5 видно также, что описанный вариант протокола предусматривает снятие защелки, т.е. возможность изменения напряжения на одной или более шинах данных между моментами t1 и t2. Это изменение происходит под влиянием зарядов, текущих во время цикла считывания между шиной данных и соединенными с ней ячейками. В отличие от этого режима во время цикла восстановления/записи имеет место защелкивание всех напряжений на управляющих шинах и шинах данных.

Должно быть понятно, что примеры, представленные на фиг.4 и 5, могут быть модифицированы без нарушения иллюстрируемых ими основных принципов изобретения (например, за счет одновременного сдвига всех потенциалов или небольших отклонений от точного соответствия уровням напряжения в изображенной трехуровневой схеме).

Пример 2. Четырехуровневый протокол переключении (Vs/3)

Как уже было показано, за счет использования, по меньшей мере, четырех различных уровней потенциала на управляющих шинах и шинах данных можно достичь того, что ни на одну неадресуемую ячейку не будет подаваться напряжение, превышающее одну треть от номинального переключающего напряжения. Два предпочтительных варианта протокола для считывания, а также для восстановления/записи в соответствии с изобретением приведены на фиг.6 и 7. Временные маркеры на этих фигурах имеют следующие значения:

t0 исходное состояние: все управляющие шины и шины данных находятся под потенциалом 2Vs/3 (фиг.6) или Vs/3 (фиг.7);

t1 потенциал на неактивных шинах данных изменен на Vs/3 (фиг.6) или 2Vs/3 (фиг.7);

t2 потенциал на адресуемой шине данных изменен на Vs (фиг.6) или 0 В (фиг.7); задержка между моментами t1 и t2 выбирается произвольно, причем допустимы также нулевая и отрицательная задержки;

t3 по истечении программно устанавливаемой задержки потенциал на адресуемой управляющей шине изменяют с исходного значения до 0 В (фиг.6) или Vs (фиг.7), что соответствует напряжению Vs между адресуемыми управляющей шиной и шиной данных; неадресуемые управляющие шины остаются под потенциалом 2Vs/3 (фиг.6) или Vs/3 (фиг.7);

t4 адресуемой управляющей шине возвращен исходный потенциал по истечении задержки на считывание;

t5 всем шинам данных возвращен исходный потенциал;

t6 цикл считывания завершен: все управляющие шины и шины данных находятся в исходном состоянии (2Vs/3 на фиг.6; Vs/3 на фиг.7);

t7 потенциал на неактивных шинах данных изменен на Vs/3 (фиг.6) или 2Vs/3 (фиг.7);

t8 потенциал на адресуемой шине данных (шинах данных), в которой (в которых) должно быть записано логическое состояние "1", изменяют до 0 В; на шинах данных, которые должны остаться в логическом состоянии "0", сохраняют исходный потенциал (фиг.6), потенциал на адресуемой шине данных (шинах данных), в которой (в которых) должно быть записано логическое состояние "0", изменяют до Vs; на шинах данных, которые должны остаться в логическом состоянии "1", сохраняют исходный потенциал (фиг.7);

t9 потенциал на адресуемой управляющей шине изменяют до Vs (фиг.6) или 0 В (фиг.7), обеспечивая тем самым на адресуемой ячейке (адресуемых ячейках) напряжение, составляющее Vs;

t10 по истечении задержки на осуществление записи потенциал на адресуемой шине данных (шинах данных) изменяют до исходного значения 2Vs/3 (фиг.6) или Vs/3 (фиг.7);

t11 всем управляющим шинам возвращен исходный потенциал;

t12 цикл записи завершен: все управляющие шины и шины данных находятся в исходном состоянии.

За исключением некоторого повышения сложности в связи с увеличением количества уровней напряжения основные свойства данного варианта сходны со свойствами ранее описанного варианта с использованием схемы с тремя уровнями. Однако теперь на протяжении всего цикла записи/считывания ни одна неадресуемая ячейка не подвергается действию напряжения, превышающего Vs/3. В результате в большинстве ферроэлектрических материалов, представляющих интерес для рассматриваемых применений, будет иметь место лишь незначительное частичное переключение поляризации. Как и в предыдущем случае, описанная схема подачи напряжений допускает различные варианты ее реализации. Так, вариант по фиг.6 и 7 соответствует возврату в исходное состояние, соответствующее нулевому напряжению на всех ячейках (см. в этой связи обсуждение описанного ранее трехуровневого протокола переключении) при потенциале на управляющих шинах и шинах данных, составляющем 2Vs/3 или Vs/3. Однако для исходного состояния могут быть выбраны и другие потенциалы, подаваемые на управляющие шины и шины данных при выполнении условия о наличии на ячейках нулевого напряжения или напряжения с абсолютным значением, меньшим или равным |Vs|/3. Предполагается, что такие варианты очевидны для специалиста в данной области; поэтому они не будут рассматриваться более подробно.

Временные диаграммы, приведенные на фиг.6 и 7, в принципе эквивалентны, причем одна из них представляет собой "инвертированную" версию другой. Однако на практике какая-то из этих диаграмм может оказаться предпочтительной. Так, схема, представленная на фиг.6, предусматривает наличие на усилителе считывания во время цикла считывания напряжения, близкого к Vs. В то же время в схеме по фиг.7 это напряжение является близким к нулю. Данное обстоятельство может сделать возможным использование низковольтных компонентов с единственным высоковольтным транзистором на каждую шину данных.

Пример 3. Пятиуровневый протокол переключении (Vs/3)

Класс с первого взгляда более сложных, но в некоторых отношениях проще реализуемых протоколов подачи импульсов предусматривает использование на управляющих шинах и шинах данных в течение полного цикла считывания-записи пяти различных уровней потенциала. Развернутые примеры двух предпочтительных вариантов подобных протоколов даны на фиг.8 и 9. Временные маркеры на этих фигурах имеют следующие значения:

t0 исходное состояние: все управляющие шины и шины данных находятся под потенциалом 2Vs/3 (фиг.8) или Vs/3 (фиг.9);

t1 потенциал на неактивных шинах данных изменен на Vs/3 (фиг.8) или 2Vs/3 (фиг.9);

t2 потенциал на адресуемой шине данных изменен на Vs (фиг.8) или 0 В (фиг.9); задержка между моментами t1 и t2 выбирается произвольно, причем допустимы также нулевая и отрицательная задержки;

t3 по истечении программно устанавливаемой задержки потенциал на адресуемой управляющей шине изменяют с исходного значения до О В (фиг.8) или 4Vs/3 (фиг.9), что соответствует напряжению Vs между адресуемыми управляющей шиной и шиной данных; неадресуемые управляющие шины остаются под потенциалом 2Vs/3 (фиг.8) или Vs/3 (фиг.9);

t4 адресуемой управляющей шине возвращен исходный потенциал по истечении задержки на считывание;

t5 всем неактивным шинам данных возвращен исходный потенциал;

t6 цикл считывания завершен: все управляющие шины и шины данных находятся в исходном состоянии (2Vs/3 на фиг.8; Vs/3 на фиг.9);

t7 потенциал на неактивных шинах данных изменен на Vs (фиг.8) или Vs/3 (фиг.9);

t8 потенциал на адресуемой шине данных (шинах данных), в которой (в которых) должно быть записано логическое состояние "1", изменяют до Vs/3; потенциал на шинах данных, которые должны остаться в логическом состоянии "0", изменяют до 0 В (фиг.8), потенциал на адресуемой шине данных (шинах данных), в которой (в которых) должно быть записано логическое состояние "0", изменяют до Vs/3; потенциал на шинах данных, которые должны остаться в логическом состоянии "1", изменяют до Vs (фиг.9);

t9 потенциал на адресуемой управляющей шине изменяют до 4Vs/3 (фиг.8) или 0 В (фиг.9), обеспечивая тем самым на адресуемой ячейке (адресуемых ячейках), напряжение, составляющее Vs; неадресуемые управляющие шины остаются под потенциалом 2Vs/3;

t10 по истечении задержки на осуществление записи потенциал на управляющих шинах изменяют до исходного значения;

t11 всем шинам данных возвращен исходный потенциал;

t12 цикл записи завершен: все управляющие шины и шины данных находятся в исходном состоянии.

В описанном цикле используется пятый уровень напряжения (Vcc). В типичном случае он соответствует 4Vs/3 и подается на активную управляющую шину на время считывания (фиг.9) или восстановления/записи (фиг.8). Можно отметить, что в то время, как четырехуровневые варианты по фиг.6 и 7 требуют использования в рамках полного цикла считывания-записи всех четырех уровней потенциала для всех управляющих шин и шин данных, пятиуровневые варианты по фиг.8 и 9 требуют подачи только трех различных уровней потенциала на управляющие шины и трех различных уровней (но не идентичных первым трем уровням) потенциала на шины данных. Тем самым обеспечиваются возможности для оптимизации и упрощения электронных контуров управления и считывания в устройстве для осуществления способа по изобретению. Дополнительное упрощение может быть достигнуто за счет выбора значения 4Vs/3=Vcc близким к напряжению питания.

Пример 4. Протоколы переключения, предусматривающие предварительную зарядку неадресуемых ячеек на активных шинах данных

При предшествующем изложении основное внимание концентрировалось на предотвращении частичного переключения неадресуемых ячеек. Однако представляется также желательным разработать протоколы переключения, которые одновременно минимизируют влияние протекания паразитных токов внутри матричной памяти во время цикла считывания.

В запоминающих устройствах, основанных на пассивной матричной адресации, плотность записи данных максимизируется путем использования матриц предельно большого размера. Это означает, что каждая матрица должна содержать максимально возможное количество точек пересечения между управляющими шинами и шинами данных, т.е. любая выбранная шина данных должна пересекать большое количество управляющих шин. Когда произведен выбор пересечения определенных управляющей шины и шины данных, большое количество невыбранных точек пересечения между шиной данных и всеми невыбранными управляющими шинами образует большое количество каналов протекания паразитных токов утечки (емкостных, индуктивных, омических), которые могут вносить вклад в замедление работы устройства и уменьшать степень контрастности между реальными значениями логических состояний "1"и"0".

Один из методов уменьшения влияния паразитных токов на определение логических состояний заключается в предварительной зарядке неадресуемых ячеек на активной шине данных до уровня, соответствующего тому уровню, который был бы достигнут в процессе считывания активной ячейки. Эта процедура в неявном виде заложена в протоколы подачи импульсов напряжения, представленные на фиг.6-9. В момент t2, т.е. перед выполнением шага подачи напряжения считывания на активную управляющую шину (соответствующего на указанных фигурах моменту t3), напряжение на активной шине данных изменяют до его значения, соответствующего значению в период считывания. Тем самым создается некоторое дополнительное напряжение между активной шиной данных и всеми управляющими шинами. Это напряжение инициирует протекание паразитных (побочных) токов во всех неактивных ячейках на активной шине данных. Данные токи в типичном случае являются переходными, обусловленными поляризационными явлениями в ячейке, причем спустя короткое время они исчезают или резко уменьшаются. Описанной схеме присущи некоторые недостатки: если временной интервал между моментами t2 и t3 становится слишком большим, он оказывает очевидное влияние на скорость доступа к данным и на общую длительность цикла считывания. Кроме того, кумулятивный (накопленный) эффект повторяющихся циклов с длительными интервалами предварительной зарядки может вызвать частичное переключение и импринтинг, для предотвращения которого напряжение на всех ячейках в исходном состоянии выбиралось равным нулю.

На диаграммах протоколов подачи импульсов напряжения, представленных на фиг.6-13, не приведены моменты, которые связаны с работой усилителя считывания и могут изменяться от схемы к схеме в зависимости от динамики переключения поляризации и отклика в виде паразитных токов для адресуемых и неадресуемых ячеек. Усилители считывания должны быть активированы позднее, чем наступление момента t2 для того, чтобы избежать помех в виде паразитных токов в неадресуемых ячейках, но лишь с небольшой задержкой относительно момента t3 для того, чтобы воспринять любой ток, обусловленный обращением поляризации в активных ячейках, которые будут переключены в результате цикла считывания.

Можно заметить, что при значительном увеличении интервала между моментами t2 и t3 раннему воздействию дополнительного напряжения |Vs/3| подвергаются не только неактивные ячейки на активной шине данных, но также и активная ячейка. В результате до того, как будет включен усилитель считывания, в активной ячейке произойдет утечка части заряда, обусловленного переключением. Величина этого эффекта, который является нежелательным, поскольку он уменьшает считываемый сигнал, зависит от поляризационных характеристик материала памяти в ячейках и может варьироваться от пренебрежимо малого до значительного. В последнем случае можно слегка модифицировать протокол подачи импульсов напряжения, изменив напряжение на неактивных управляющих шинах, как это показано на фиг.10-13. Передний фронт импульса смещения соответствует моменту t0, а его задний фронт совпадает с передним фронтом напряжения смещения, подаваемого на активную шину данных в момент t2. При этом напряжение на неадресуемых ячейках активной шины данных увеличится от нуля до уровня |Vs/3| в момент t0 и останется неизменным до момента t5, в который будет завершен цикл считывания. В данном случае выбор момента t2 может быть оптимизирован относительно процесса считывания в активной ячейке, без учета ограничений, связанных с появлением переходных токов в результате предварительной зарядки неадресуемых ячеек. Как можно видеть из фиг.10-13, в этих модифицированных схемах напряжение на неадресуемых ячейках всегда поддерживается меньшим чем |Vs/3|. Однако теперь в пятиуровневых протоколах для управляющих шин используются не три уровня потенциала, как раньше, а четыре уровня.

Пример 5. Протоколы переключения, предусматривающие цикл предварительного считывания

Теперь будет описана другая схема для преодоления или ослабления проблем, связанных с паразитными токами в неадресуемых ячейках на активных шинах данных.

Для большей конкретности в качестве примера будет рассмотрена четырехуровневая диаграмма, представленная на фиг.6. Схема предварительной зарядки, описанная в предыдущем примере, предусматривает, что потенциал на активной шине данных был доведен до значения, соответствующего циклу считывания, в момент t0, так что к моменту t0, в который происходит переключение активной управляющей шины, возникшие паразитные токи существенно уменьшились. Логическое состояние в адресуемой ячейке определяется усилителем считывания, который регистрирует заряд, протекающий к шине данных в течение заданного временного интервала, который начинается вблизи момента t3 и завершается перед наступлением момента t4.

В идеальном случае подобные схемы с предварительной зарядкой должны обеспечивать возможность детектирования заряда, протекающего как отклик на изменение потенциала на активной управляющей шине без помех со стороны паразитных токов, протекающих через ячейки на неактивных управляющих шинах. Однако на практике паразитные токи могут иметь медленное затухание и/или включать омическую (т.е. некратковременную) составляющую, так что некоторый паразитный заряд будет восприниматься усилителем считывания. Хотя уровень паразитного тока, протекающего через каждую неадресуемую ячейку на активной шине данных, может быть низким, суммирование таких токов по сотням и тысячам неадресуемых ячеек на активной шине данных может дать весьма значительную величину, искажающую результаты считывания.

При допущении, что условия работы являются стабильными и предсказуемыми, подобный вклад паразитных токов может быть в принципе устранен путем вычитания фиксированного количества заряда из заряда, зарегистрированного усилителем считывания в цикле считывания. Однако во многих случаях уровень и вариабельность вкладов паразитных токов делает подобный подход неприемлемым. Действительно, в дополнение к допустимым погрешностям изготовления устройства история усталости и импринтинга может варьироваться в широких пределах для различных ячеек в пределах одного запоминающего устройства и даже в пределах одной шины данных. Кроме того, паразитный ток может сильно зависеть от температуры устройства во время считывания. Далее, паразитный ток, ассоциированный с конкретной неадресуемой ячейкой на активной шине данных, может зависеть от того, в каком логическом состоянии она находится. В этом случае суммарный паразитный ток от всех неадресуемых ячеек на активной шине данных будет зависеть от совокупности данных, записанных в этих ячейках, которая является непредсказуемой.

Для того чтобы получить истинную оценку суммарных паразитных токов, соответствующих конкретному акту считывания, можно ввести контрольный цикл предварительного считывания, который иллюстрируется фиг.14.

Цикл предварительного считывания непосредственно предшествует циклу считывания и отличается от него только в одном отношении, а именно тем, что не включает никакого переключения активной управляющей шины. Усилитель считывания активируется точно в таком же временном интервале относительно моментов изменения потенциала на шине данных, что и в последующем цикле считывания. Таким образом, суммарный заряд, детектированный в цикле предварительного считывания, должен очень точно соответствовать вкладу паразитного тока, детектируемого во время цикла считывания вместе с вкладами от активной ячейки. Заряд, детектированный в цикле предварительного считывания, запоминают и вычитают из заряда, зарегистрированного во время цикла считывания. В результате определяется искомый скорректированный заряд, обусловленный процессом в переключаемой или непереключаемой активной ячейке.

Очевидно, что описанная схема обеспечивает автоматический учет усталости, импринтинга, температуры и логических состояний ячеек. Важное условие ее осуществимости состоит в том, что цикл предварительного считывания не должен реально изменять уровни паразитных токов во время цикла считывания. Следовательно, задержка между моментами Р6 и 0 (см. фиг.14) должна быть достаточной для того, чтобы переходные процессы, связанные с предварительным считыванием, были завершены. В некоторых случаях для того, чтобы получить воспроизводимую оценку паразитных токов, можно проводить два или более последовательных циклов предварительного считывания, предшествующих циклу считывания. Однако это увеличивает сложность схемы и общую длительность считывания.

Совместное рассмотрение фиг.14 с четырехуровневым протоколом подачи импульсов напряжения, представленным на фиг.6, показывает, как принцип контрольного предварительного считывания путем простой адаптации описанного выше примера его реализации может быть применен и для других протоколов, охватываемых настоящим изобретением.

Пример 6. Протоколы переключения, предусматривающие компенсирующие напряжения

Далее будет представлена еще одна схема для преодоления или ослабления проблем, связанных с паразитными токами в неадресуемых ячейках на активных шинах данных.

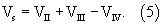

В соответствии с приведенным ранее уравнением (2) минимальное возмущающее напряжение на неадресуемых ячейках составляет Vs/3 (см. уравнение (3)). Соответственно было продемонстрировано, что предпочтительные варианты изобретения, описанные при рассмотрении четырех- и пятиуровневых протоколов переключения, обеспечивают выполнение этого условия. Как будет показано далее, в некоторых случаях предпочтительно несколько отклониться от указанного критерия.

При условии, что ячейки памяти обладают определенными характеристиками в отношении их электрического импеданса и параметров переключения, оказывается возможным получить низкий паразитный ток на шине данных во время операций считывания и одновременно удерживать возмущающее влияние на неадресуемые ячейки на низком уровне.

Примем, что на выбранную ячейку в период, когда ее запоминающий материал претерпевает переключение поляризации, подается напряжение VI=Vs. Тогда:

Представляется желательным понизить суммарный ток утечки на активной шине данных, текущий через неадресуемые ячейки на этой шине. Это может быть достигнуто уменьшением напряжения (т.е. его изменением на величину отрицательного приращения δ ) на неадресуемых ячейках. Таким образом:

Согласно уравнению (5) указанная величина должна быть компенсирована соответствующей подстройкой напряжений на оставшихся неадресуемых ячейках:

В крупной матрице количество ячеек с неактивными управляющими шинами и шинами данных (VIV) значительно превосходит количество ячеек с активной управляющей шиной, пересекающейся с неактивной шиной данных (VII). Следовательно, для того чтобы минимизировать суммарное возмущение неадресуемых ячеек в матрице, можно выдвинуть требование того, чтобы VIV не было изменено для того, чтобы скомпенсировать уменьшение VIII. В этом случае:

Разумеется, данный выбор не является единственно возможным, однако при дальнейшем рассмотрении принимается именно он для того, чтобы упростить понимание основных принципов рассматриваемого решения.

Итак, протокол Vs/3 может быть модифицирован таким образом, что: VI=Vs, VII=Vs/3+5, VIII=Vs/3-5, VIV=-Vs/3. Это возможно, например, при сохранении потенциалов на активных управляющей шине и шине данных неизменными при изменении на величины δ 1, δ 2 положительного приращения потенциалов на всех неактивных управляющих шинах и шинах данных соответственно, при δ 1=δ 2=5.

i) VI=Vs=ФactiveBL-ФactiveWL: активная управляющая шина пересекает активную шину данных (выбранная ячейка);

ii) VII=Vs/3+5=(ФinactiveBL+8)-ФactiveWL: активная управляющая шина пересекает неактивную шину данных;

iii) VIII=Vs/3-δ =ФactiveBL-(ФinactiveWL+δ ) неактивная управляющая шина пересекает активную шину данных;

iv) VIV=-Vs/3=(ФinactiveBL+δ )-(ФinactiveWL+δ ): неактивная управляющая шина пересекает неактивную шину данных.

Значение приращения 5 должно выбираться с учетом двух противоречащих требований. С одной стороны, оно должно быть, насколько это возможно, большим для того, чтобы минимизировать вклады паразитных токов на активной шине данных. С другой стороны, оно должно быть, насколько это возможно, малым для того, чтобы минимизировать возмущение для неадресуемых ячеек. На практике решение должно приниматься исходя из конкретных условий, играющих основную роль в каждом случае.

Кроме того, специалистам в данной отрасли хорошо известно, что электрически поляризуемые материалы, применяемые в качестве запоминающей среды в дисплеях и запоминающих устройствах, могут иметь нелинейные вольтамперные характеристики. Это свойство может быть эффективно использовано при реализации протоколов переключения с использованием компенсирующих напряжений. Однако подобные нелинейные вольтамперные характеристики могут зависеть также от конкретного материала, а также от его обработки и факторов, которые в контексте настоящего изобретения могут зависеть от параметров реально используемого протокола, а также от конструктивных и масштабных факторов. Отсюда вытекает невозможность рассмотрения в общем виде полезного использования нелинейности вольтамперной характеристики неадресуемых ячеек. Вместе с тем применительно к любому конкретному варианту выполнения возможность использования подобных характеристик может быть установлена опытным путем. Однако любой подобный опытный путь должен рассматриваться как лежащий вне пределов настоящего изобретения.

Пример 7. Считывание всей строки

Альтернативное направление в снижении или устранении вклада паразитного тока от неадресуемых ячеек на активных шинах данных при считывании иллюстрируется фиг.15. Все управляющие шины, кроме активной, защелкнуты на потенциал, близкий к потенциалу на входе усилителя считывания (который на фиг.15 определен, как нулевой). Для считывания данных активной управляющей шине придается потенциал VREAD, который вызывает протекание токов через ячейки на пересекаемых шинах данных. Значения этих токов, зависящие от состояния поляризации в каждой ячейке, определяются усилителями считывания, предусмотренными, как это показано на фиг.15, для каждой шины данных.

Приведенная схема обладает следующими преимуществами.

- Напряжения на всех неадресуемых ячейках весьма близки к нулю, благодаря чему устраняются токи утечки, которые в противном случае могли бы исказить отсчет, снимаемый с адресуемых ячеек.

- Напряжение VREAD считывания может быть выбрано значительно более высоким, чем коэрцитивное напряжение, без возникновения частичного переключения в неадресуемых ячейках. За счет этого могут быть достигнуты скорости переключения, близкие к предельным скоростям, ограничиваемым свойствами процесса переключения в поляризуемом материале ячеек.

- Схема совместима с крупными матричными наборами ячеек.

- Высокая степень параллелизма делает возможной высокую скорость считывания данных.

Поскольку считывание является деструктивным, во многих случаях оказывается необходимым повторно записывать данные в запоминающее устройство. Такая запись может быть осуществлена с использованием одной из ранее описанных схем. Для восстановления данных, например, в сочетании с кэшированием, может быть использован набор ячеек запоминающего устройства, отличный от набора, с которого производилось считывание.

Возможные недостатки данной схемы связаны, в основном, с возрастающими требованиями к драйверным контурам и к контурам, выполняющим функции считывания. Действительно, одновременное переключение всех ячеек на одной длинной управляющей шине может приводить к значительным всплескам тока, что подразумевает необходимость в источнике с низким импедансом для драйверного контура и в путях протекания тока, также имеющих низкий импеданс. Кроме того, повышается вероятность перекрестных помех в пределах устройства. Далее, для того, чтобы избежать потери данных, для каждой шины данных требуется отдельный усилитель считывания. В случае максимально высокой плотности размещения ячеек в пассивной матрице данное требование создает проблему компоновки компонентов у кромки матрицы, где к ней подключены усилители считывания.

Приведенные в данном описании протоколы переключения обеспечивают возможность управляемого переключения направления поляризации для любой ячейки в устройстве с пассивной матричной адресацией без приложения к неадресуемым ячейкам возмущающих напряжений, превышающих уровень, близкий к Vs/3.

Как было описано в приведенных примерах, протоколы, предусматривающие подачу импульсных напряжений, непосредственно применимы для считывания логических состояний ячеек памяти, которые во время цикла считывания либо не претерпевают переключения поляризации (т.е. находятся в состоянии, определенном, как логический "0"), либо испытывают переключение поляризации (соответственно находятся в состоянии, определенном, как логическая "1"). Инициализация памяти может предусматривать запись нулей во все ячейки, что в рассматриваемом случае будет означать выполнение цикла считывания (деструктивного считывания). После этого запись может осуществляться путем подачи последовательности импульсов, обеспечивающей изменение поляризации в тех ячейках, которые должны хранить логическую "1" при сохранении состояния остальных ячеек неизменным. Последующее считывание данных из памяти соответственно потребует выполнение цикла восстановления в тех случаях, когда желательно сохранить данные в памяти после проведения деструктивного считывания. Протокол восстановления потребует подачи полной последовательности импульсов, которая соответствует циклу считывания/восстановления в тех случаях, когда для возобновленного хранения данных будут использоваться ячейки, отличные от тех, с которых производилось деструктивное считывание с целью извлечения данных. Если же для этого хранения будут использоваться те же самые ячейки, то ячейки, которые при считывании были определены как хранившие логический "0", могут сохраняться неизменными с осуществлением переключения поляризации только в ячейках, содержавших логическую "1".

Изобретение относится к способу управления набором ячеек памяти или дисплеем с пассивной матричной адресацией, содержащими электрически поляризуемый материал, обладающий гистерезисом, преимущественно ферроэлектрический материал. Его использование позволяет получить технический результат в виде разработки протоколов подачи импульсов напряжения в функции от времени для управления шин х и у матрицы с пассивной адресацией в устройствах с постоянной памятью, характеризующихся кривыми гистерезиса ферроэлектрического типа, обеспечивающих минимизацию возмущений для невыбранных ячеек памяти при записи данных в память устройства, а также при считывании данных из памяти. Технический результат достигается за счет того, что потенциал на выбранных управляющих шинах данных задают таким образом, чтобы он был близким или совпадающим с одним из заданных n уровней потенциала. При этом управление потенциалами, подаваемыми на все управляющие шины и шины данных, осуществляют в соответствии с протоколом таким образом, что управляющие шины последовательно защелкивают на значениях потенциала, выбранных из nWORD значений, в то время как шины данных либо последовательно защелкивают на значениях потенциала, выбранных из nBIT значений, либо подключают на определенный период в пределах временной последовательности импульсов, задаваемой протоколом, к контуру для детектирования зарядов, текущих между шиной или шинами данных и ячейками, соединенными с этими шинами. 15 з.п. ф-лы, 15 ил.

| US 5550770 А, 27.08.1996 | |||

| US 4169258 A, 25.09.1979 | |||

| US 4709995 A, 01.12.1987 | |||

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

| RU 94016378 A1, 27.08.1996. | |||

Авторы

Даты

2004-11-10—Публикация

2001-07-06—Подача