Область техники, к которой относится изобретение

Настоящее изобретение относится к запоминающему устройству на основе энергонезависимой пассивной матрицы, которая содержит электрически поляризуемый диэлектрический материал, обладающий гистерезисом, преимущественно ферроэлектрический материал. При этом указанный запоминающий материал находится в слое, расположенном между первым и вторым наборами электродов адресации с параллельным расположением электродов в пределах каждого набора. Электроды первого набора, которые образуют управляющие (числовые) шины запоминающего устройства, расположены перпендикулярно электродам второго набора, которые образуют шины данных (разрядные шины). В результате в точке скрещивания (называемой далее для большей ясности точкой пересечения) образуется ячейка памяти со структурой типа конденсатора. Подобные ячейки памяти формируют элементы пассивной матрицы запоминающего устройства, в которой может быть произведена селективная адресация каждой ячейки памяти для осуществления операции записи/считывания, с использованием соответствующих управляющей шины и шины данных. Операция записи в ячейке выполняется путем создания желаемого состояния поляризации в ячейке посредством приложения к ней напряжения по соответствующим управляющей шине и шине данных, определяющим эту ячейку. Приложенное напряжение либо устанавливает требуемое состояние поляризации в ячейке, либо способно произвести переключение ее состояния поляризации. Операция считывания выполняется посредством приложения к ячейке памяти напряжения Vs переключения, которое превышает коэрцитивное напряжение

Vc, и детектирования, по меньшей мере, одного электрического параметра выходного тока на шинах данных.

Изобретение относится также к способу считывания из запоминающего устройства описанного типа.

Уровень техники

Ферроэлектрические интегральные схемы обладают революционными свойствами по сравнению с традиционной технологией. Их применения включают энергонезависимые устройства хранения информации, особенно матричные запоминающие устройства, обладающие такими преимуществами, как высокое быстродействие, практически неограниченный срок службы и высокая скорость записи, т.е. свойствами, о которых недавно можно было только мечтать.

Ферроэлектрические матричные устройства можно разделить на два типа, один из которых предусматривает наличие активных элементов, подключенных к ячейкам памяти, а другой не содержит активных элементов. Далее будут охарактеризованы оба этих типа.

Ферроэлектрическая матричная память, имеющая ячейки памяти в форме ферроэлектрических конденсаторов без активных элементов доступа (таких как транзисторы), содержит тонкую ферроэлектрическую пленку с набором параллельных проводящих электродов ("управляющих шин"), нанесенных на одну ее сторону и с, по существу, ортогональным набором проводящих электродов ("шин данных"), нанесенных на другую ее сторону. Подобная конфигурация в дальнейшем будет именоваться "пассивной матричной памятью". В пассивной матричной памяти индивидуальные ферроэлектрические ячейки памяти образуются в точках пересечения противолежащих электродов с образованием матрицы памяти, содержащей ячейки памяти, индивидуальный доступ к которым осуществляется электрическим путем посредством селективного возбуждения, с краев матрицы, соответствующих электродов.

Другой подход к формированию матричной памяти состоит в модифицировании каждой ферроэлектрической ячейки памяти путем включения в нее активного элемента, в типичном случае транзистора доступа, включенного последовательно с ферроэлектрическим конденсатором. Транзистор доступа управляет доступом к конденсатору и блокирует нежелательные сигналы-помехи, например, от соседних ячеек памяти. В типичном случае ячейка памяти может включать в себя ферроэлектрический конденсатор и n-канальный полевой транзистор со структурой металл-оксид-полупроводник (далее сокращенно обозначаемый как МОП-транзистор без индикации для упрощения его типа n или p). Затвор транзистора соединен с управляющей шиной. Истоковая/стоковая область МОП-транзистора соединена с шиной данных. Один электрод ферроэлектрического конденсатора соединен с истоковой/стоковой областью МОП-транзистора, а его второй электрод соединен с так называемой "передающей линией". Описанная схема является в настоящее время общепринятой, и соответствующие ячейки памяти часто определяются как ячейки памяти с одним транзистором и одним конденсатором (1Т, 1С). Хорошо известны и другие концепции, использующие по два транзистора или более. Однако все эти концепции приводят к увеличению количества транзисторов по сравнению с пассивной матричной памятью, что связано с рядом недостатков, таких как уменьшение количества ячеек памяти в пределах заданной площади, повышение сложности и повышенное потребление тока. Далее конфигурация данного типа будет именоваться "активной" матричной памятью, поскольку здесь в каждой ячейке памяти имеется "активный" элемент, например транзистор.

Однако настоящее изобретение относится исключительно к устройствам с пассивной матричной памятью, не содержащей активных элементов, таких как диоды или транзисторы, ассоциированные с ячейкой памяти.

Операции считывания и записи в пассивной матричной памяти могут осуществляться путем так называемой "выборочной адресации", при которой считывание или запись производится только для части ячеек памяти на одной управляющей шине, в типичном случае только для единственной ячейки. Для выполнения такой операции выборочного считывания или записи на неадресуемые ячейки на неактивируемых управляющих шинах и шинах данных подают напряжение смещения в соответствии с так называемым "протоколом подачи импульсов" с тем, чтобы избежать частичного переключения поляризации в неадресуемых ячейках. Выбор протокола подачи импульсов зависит от ряда факторов, причем в литературе описаны различные схемы для применений, связанных с ферроэлектрическими запоминающими материалами, обладающими гистерезисом. В качестве примера можно указать на заявку Норвегии № 20003508, поданную 7 июля 2000 г. заявителем настоящего изобретения и соответствующую международной заявке WO 02/052887. В данной заявке описан протокол для пассивной матричной памяти.

С другой стороны, обычно подача смещения на неадресуемые ячейки приводит к появлению мешающих напряжений. Это может вызвать потерю содержания ячейки памяти или появление токов утечки и других вредных токов, называемых далее "паразитными токами", которые могут маскировать ток адресуемой ячейки памяти во время операции считывания и тем самым маскировать содержание считываемых данных. В зависимости от типа рассматриваемого запоминающего устройства могут быть сформулированы различные критерии в отношении устранения или, по меньшей мере, уменьшения помех для неадресуемых ячеек памяти, в том числе методы устранения паразитных токов. Другой подход состоит в снижении чувствительности каждой ячейки в матрице к слабым возмущениям. Оно может быть достигнуто использованием ячеек, которые обладают нелинейным вольтамперным откликом, характеризующимся, например, наличием порога, выпрямлением и/или различными формами гистерезиса.

Для того чтобы улучшить параметры как активных, так и пассивных ферроэлектрических запоминающих устройств, например, для снижения требований по потребляемой мощности, матричная память может быть разделена, "сегментирована" на блоки меньшего размера, так называемые "сегменты". Обычно подобная сегментация видна пользователю. Другая причина для сегментации вызвана проблемой так называемой "усталости" ферроэлектрических конденсаторов: после того, как ферроэлектрический конденсатор был переключен большое количество раз, соответствующее, например, нескольким миллионам, он не в состоянии сохранять остаточную поляризацию и, следовательно, перестает функционировать. Решением данной конкретной проблемы может быть использование меньших сегментов матрицы для того, чтобы избежать переключения всей строки конденсаторов. Подобное решение описано, например, в документе US-A 5567636. Другим документом, описывающим сегментированную матричную память, является работа Gary F. Derbenwick & al., "Non-volatile Ferroelectric Memory for Space Applications", Celis Semiconductor Corporation, Colorado Springs. Данный документ описывает сегментированную матричную память, способную обеспечить снижение потребляемой мощности в активной матрице, использующей архитектуру ячейки типа один транзистор - один конденсатор (1Т, 1С).

Примеры запоминающих устройств с пассивной матрицей, использующей ферроэлектрический запоминающий материал, могут быть найдены в литературе, относящейся еще к 40-50м годам. В частности, в статье W.J.Merz and J.R.Anderson, "Ferroelectric storage devices", Bell. Lab. Record. 1, pp. 335-342 (1955) описана память на основе титаната бария. Аналогичные исследования были опубликованы вскоре после опубликования названной статьи (см., например, С.F.Pulvari, "Ferroelectrics and their memory applications", IRE Transactions CP-3, pp. 3-11 (1956), и D.S.Campbell, "Barium titanate and its use as a memory store", J. Brit. IRE 17 (7), pp. 385-395 (1957)). Другой пример пассивной матричной памяти может быть найден в публикации IBM Technical Disclosure Bulletin, Vol. 37, No. 11, November 1994. Однако ни один из названных документов не описывает решение проблемы, связанной с возмущением неадресуемых ячеек.

Другим подходом к преодолению названной проблемы могло бы стать модифицирование ферроэлектрического материала таким образом, чтобы получить петлю гистерезиса в форме квадрата. Однако подобный подход еще не был описан в литературе достаточно подробно.

Сущность изобретения

Таким образом, существует потребность в пассивной матричной памяти, свободной от вышеперечисленных недостатков, таких как наличие возмущений на неадресуемых ячейках.

С учетом изложенного задача, на решение которой направлено настоящее изобретение, состоит в создании запоминающего устройства с пассивной матричной памятью, в котором решена проблема, связанная с возмущениями неадресуемых ячеек памяти. Другая задача, решаемая изобретением, заключается в создании запоминающего устройства с пассивной матричной памятью, в котором минимизировано влияние кумулятивных сигналов от неадресуемых ячеек в процессе считывания хранящихся данных. Наконец, еще одной задачей, поставленной перед изобретением, является разработка способа считывания в запоминающем устройстве с пассивной матричной памятью, совместимого с решением вышеперечисленных задач.

Решение названных задач, а также различные преимущества и новые свойства обеспечены согласно настоящему изобретению созданием запоминающего устройства с пассивной матричной памятью, которое характеризуется тем, что управляющие шины разделены на сегменты, причем каждый сегмент содержит множество смежных шин данных матрицы и задается этим множеством. Предусмотрены также средства для присоединения каждой шины данных, приписанной сегменту, к ассоциированному средству считывания, обеспечивающие одновременное соединение всех ячеек памяти, связанных с управляющей шиной в данном сегменте, для считывания по шинам данных, входящих в сегмент. Каждое средство считывания выполнено с возможностью детектирования потока заряда в шине данных, соединенной с указанным средством для того, чтобы определить логическое значение, хранящееся в ячейке памяти, заданной шиной данных.

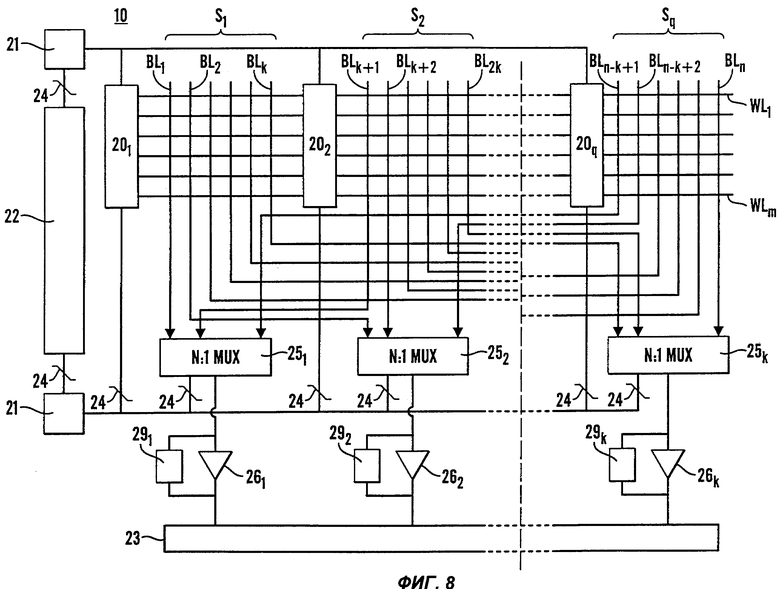

В соответствии с первым предпочтительным вариантом запоминающего устройства согласно изобретению средства для одновременного соединения каждой шины данных, приписанной сегменту, с ассоциированным средством считывания во время адресации представляют собой мультиплексоры. В этом случае количество мультиплексоров соответствует наибольшему количеству шин данных, задающих сегмент, и каждая шина данных в сегменте соединена с соответствующим ей мультиплексором. Кроме того, предпочтительно, чтобы выход каждого мультиплексора был соединен с единственным средством считывания, которое предпочтительно представляет собой усилитель считывания.

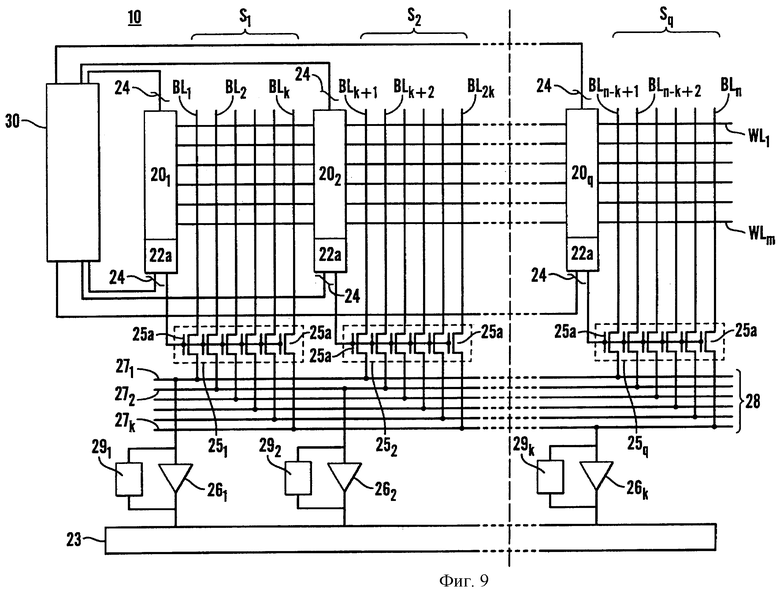

В соответствии со вторым предпочтительным вариантом запоминающего устройства согласно изобретению средства для одновременного соединения каждой шины данных, приписанной сегменту, с ассоциированным средством считывания во время адресации представляют собой вентильные средства. В этом случае все шины данных одного сегмента могут быть соединены с соответствующим им единственным вентильным средством. При этом каждое из вентильных средств имеет количество выходов, соответствующее количеству шин данных в соответствующем сегменте, тогда как каждый выход каждого вентильного средства соединен с соответствующей ему линией, входящей в состав выходной информационной шины. Количество таких линий, каждая из которых соединена с единственным средством считывания, соответствует наибольшему количеству шин данных в одном сегменте.

Вентильное устройство в данном варианте предпочтительно содержит пропускающие вентили, а средство считывания предпочтительно представляет собой усилитель считывания.

Решение вышеперечисленных задач и достижение соответствующих преимуществ обеспечиваются также согласно настоящему изобретению созданием способа считывания в энергонезависимом запоминающем устройстве с пассивной матричной памятью. Способ по изобретению характеризуется тем, что управляющие шины разделяют на ряд сегментов, каждый из которых содержит множество смежных шин данных матрицы и определяется ими, соединяют каждую шину данных в пределах сегмента управляющей шины с ассоциированным средством считывания, поочередно активируют, в соответствии с протоколом, по одной управляющей шине сегмента, устанавливая потенциал активируемой управляющей шины сегмента равным напряжению Vs переключения в течение, по меньшей мере, части цикла считывания при удерживании всех шин сегмента на нулевом потенциале, и определяют логические значения, хранившиеся в индивидуальных ячейках памяти и воспринятые средствами считывания во время цикла считывания.

В соответствии с предпочтительным вариантом осуществления данного способа в те интервалы времени, когда не производится считывания или записи ни в одной ячейке памяти, все управляющие шины и все шины данных удерживают под исходным потенциалом, составляющим около 1/3 напряжения Vs переключения, активируют, в соответствии с протоколом, по одной управляющей шине, устанавливая потенциал активируемой управляющей шины сегмента равным напряжению Vs переключения в течение, по меньшей мере, части цикла считывания при удерживании всех шин указанного сегмента на нулевом потенциале, и определяют логические значения, хранившиеся в индивидуальных ячейках памяти и воспринятые средствами считывания во время цикла считывания.

В довершение, решение поставленных задач и достижение соответствующих преимуществ достигается также в соответствии с настоящим изобретением благодаря использованию энергонезависимого запоминающего устройства с пассивной матричной памятью в любом из описанных выше вариантов для создания устройства трехмерного хранения данных с множеством образующих стопу слоев, в котором каждый слой содержит одно энергонезависимое запоминающее устройство с пассивной матричной памятью.

Перечень фигур

Далее изобретение будет описано более подробно путем обсуждения его общих основ и предпочтительных вариантов осуществления, которые следует рассматривать совместно с прилагаемыми чертежами.

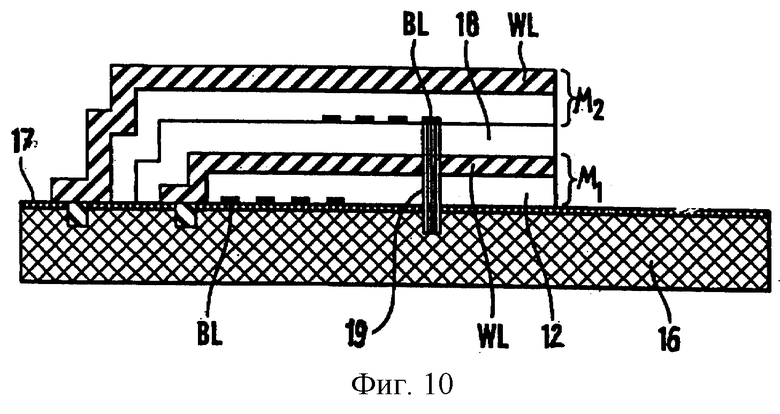

Фиг.1 иллюстрирует принцип петли гистерезиса для ферроэлектрического запоминающего материала.

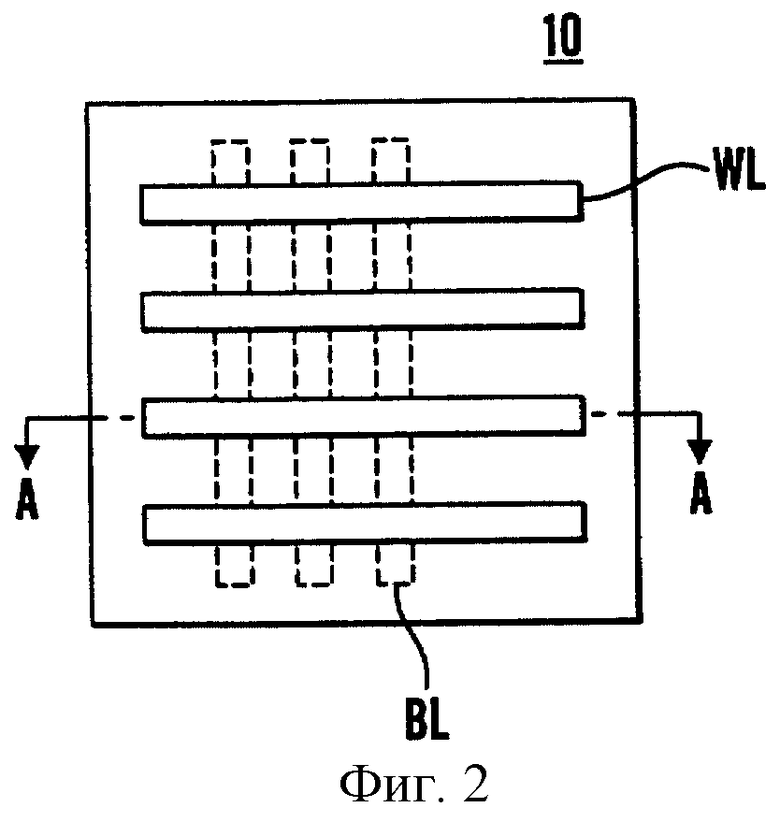

Фиг.2 представляет собой схематичную диаграмму части пассивной матричной памяти с пересекающимися электродными линиями, в которой ячейки памяти содержат ферроэлектрический материал, локализованный между электродами в местах их взаимного наложения.

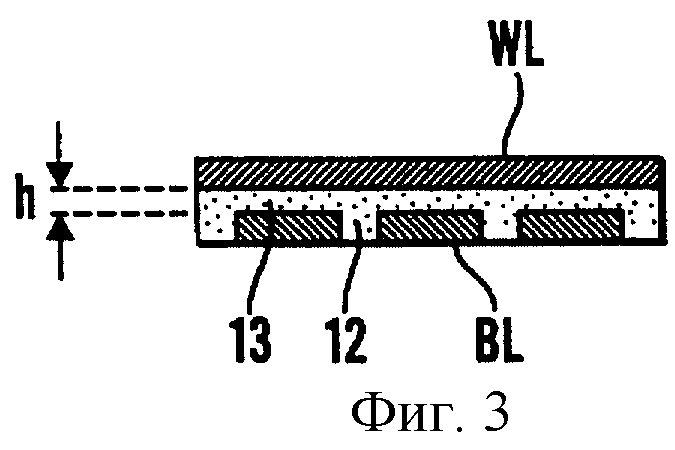

На фиг.3 в увеличенном масштабе показано сечение по линии А-А на фиг.2.

Фиг.4 представляет собой функциональную блок-диаграмму, иллюстрирующую считывание полного информационного слова в ферроэлектрической матричной памяти.

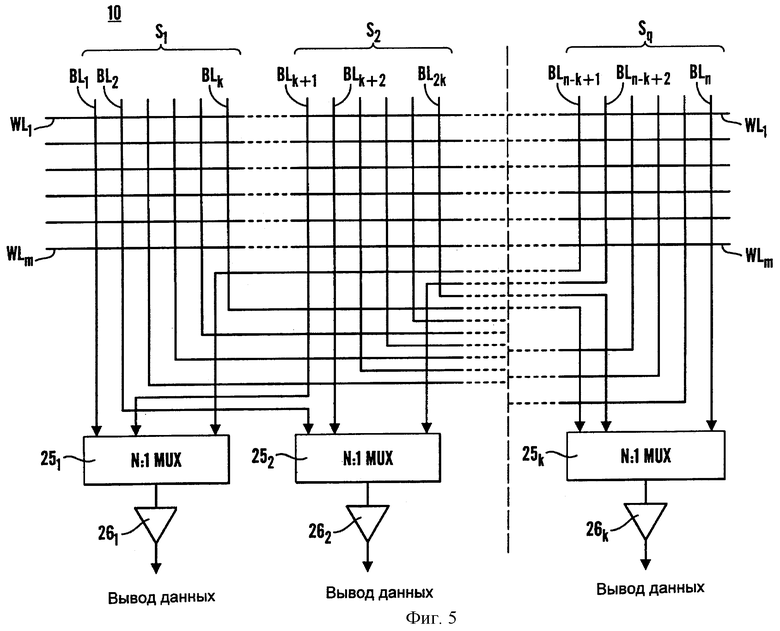

Фиг.5 представляет собой функциональную блок-схему, иллюстрирующую пассивную матричную память в соответствии с предпочтительным вариантом изобретения, содержащую сегментированные управляющие шины.

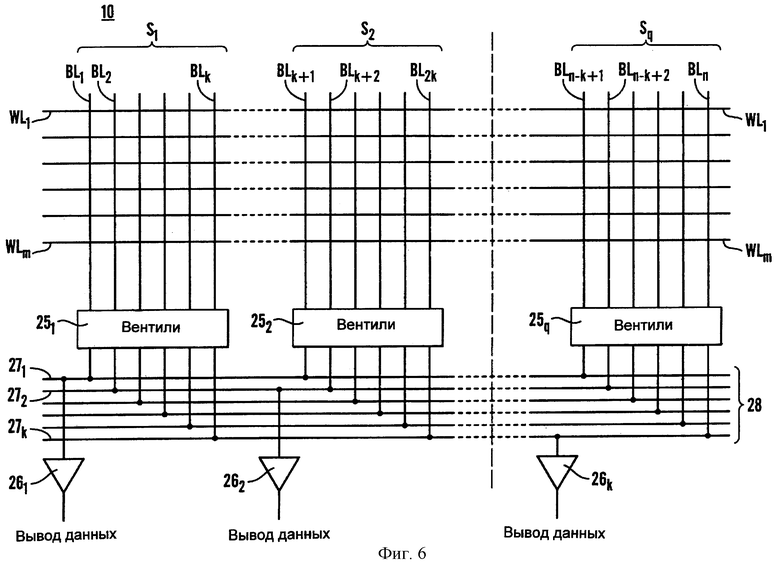

Фиг.6 представляет собой функциональную блок-схему, иллюстрирующую пассивную матричную память в соответствии с другим предпочтительным вариантом изобретения, содержащую сегментированные управляющие шины.

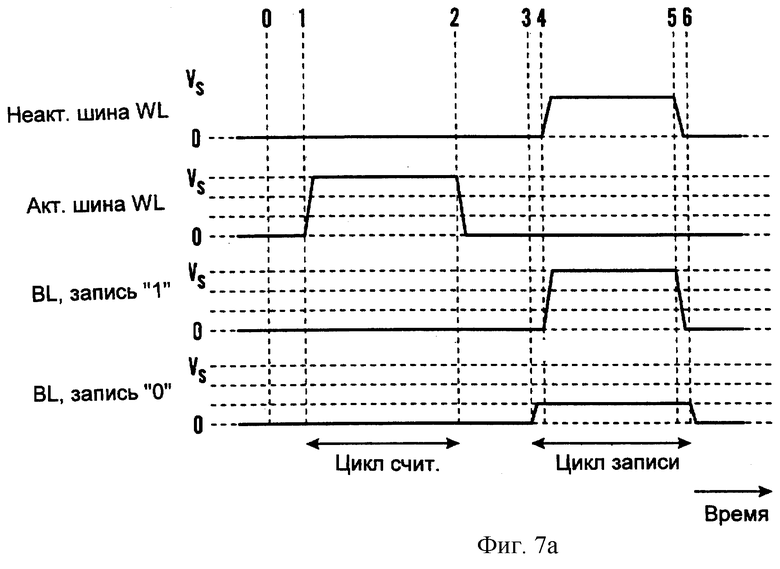

На фиг.7а приведена простая временная диаграмма считывания полного информационного слова с последующим циклом записи/обновления, предназначенная для адресации управляющей шины сегмента матричной памяти в режиме "считывания полного информационного слова".

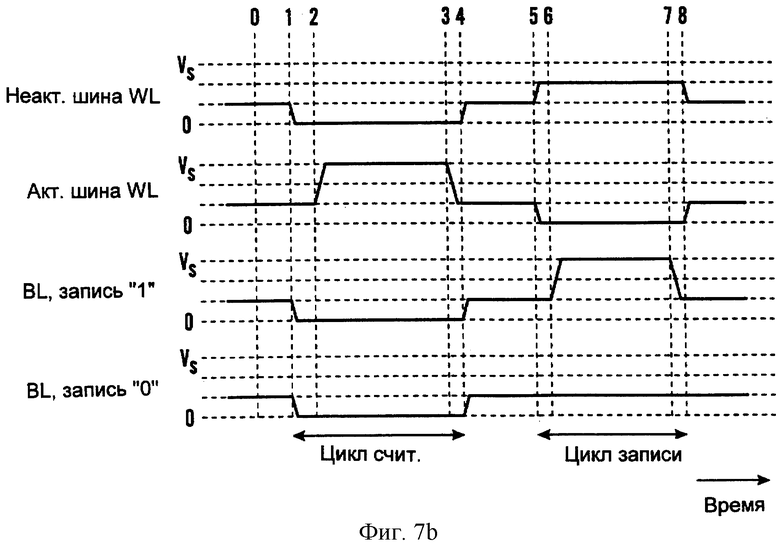

Фиг.7b соответствует варианту временной диаграммы по фиг.7а.

На фиг.8 представлен вариант устройства, аналогичный показанному на фиг.5, но с электрической сегментацией управляющих шин.

На фиг.9 представлен вариант устройства, аналогичный показанному на фиг.6, но с электрической сегментацией управляющих шин.

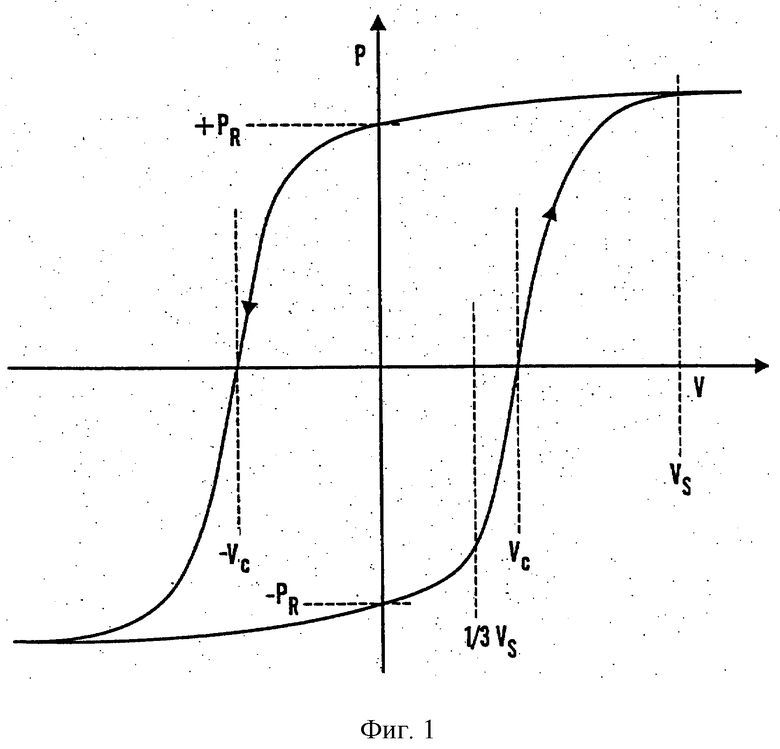

Фиг.10 схематично иллюстрирует, как матричная память по фиг.5 или 6 может быть встроена в устройство трехмерного хранения данных.

Сведения, подтверждающие возможность осуществления изобретения

Чтобы добиться лучшего понимания того, как работает пассивная матричная память и даже ее отдельная ячейка, детальному описанию предпочтительных вариантов осуществления изобретения будет предшествовать обсуждение его основных принципов. В этой связи будет сделана ссылка на фиг.1, где представлена так называемая "петля гистерезиса" для ферроэлектрического материала. Фиг.1 соответствует представлению поляризации Р ферроэлектрического материала как функции разности потенциалов V. Значение поляризации будет перемещаться по петле в обозначенном направлении. Ферроэлектрический материал, характеризующийся петлей гистерезиса типа показанной на фиг.1, будет изменять направление своей суммарной поляризации ("переключаться") при приложении напряжения VS, которое превышает так называемое коэрцитивное напряжение VC.

Когда напряжение V превысит коэрцитивное напряжение VC, поляризация Р резко изменяется, принимая большое положительное значение +Рr (предполагается, что при нулевом электрическом поле поляризация была отрицательной). Данная положительная поляризация +Рr сохраняется до тех пор, пока большое отрицательное напряжение -VS, превышающее по абсолютному значению отрицательное коэрцитивное напряжение -VC, снова не изменит поляризацию, придав ей отрицательное значение. Как следствие, запоминающие устройства, снабженные конденсаторами, содержащими ферроэлектрический материал, будут обнаруживать эффект памяти в отсутствие приложенного внешнего электрического поля. Это делает возможным энергонезависимое сохранение данных путем приложения к ферроэлектрическому материалу разности потенциалов, которая вызывает поляризационный отклик. Направление и уровень отклика могут быть, таким образом, заданы и сохранены в желаемом состоянии. Аналогичным образом может быть определено состояние поляризации. Далее будет более подробно описан процесс хранения и определения содержания данных.

С учетом требуемой скорости переключения и других факторов номинальное (переключающее) напряжение VS, используемое для управления состоянием поляризации ферроэлектрического материала, в типичном случае выбирается существенно большим, чем коэрцитивное напряжение VC. На фиг.1 номинальное значение в общем виде обозначено штриховой линией, однако его выбор никак не ограничивается данным значением. Могут быть использованы и другие значения.

Фиг.2 иллюстрирует часть матрицы m× n, входящей в состав запоминающего устройства 10 с пассивной матричной памятью, у которой имеются два взаимно противолежащих набора параллельных электродов, а именно электродов, соответствующих управляющим шинам (или линиям) WL, и электродов, соответствующих шинам (или линиям) BL данных. Электроды, соответствующие управляющим шинам WL, и электроды, соответствующие шинам BL данных, расположены взаимно перпендикулярно, причем в зоне их взаимного пересечения они образуют боковые стенки индивидуальных объемных элементов изоляционного ферроэлектрического материала (подробно описываемых далее), которые, в свою очередь, определяют объем конденсатороподобных ячеек памяти в матричной памяти.

На фиг.3 показано сечение матрицы по линии А-А на фиг.2. Диэлектриком в каждом "конденсаторе" является ферроэлектрический материал 12. При этом толщина данного материала определяет высоту h объемных элементов, которые, в свою очередь, определяют ячейки 13 памяти. Для облегчения понимания на фиг.2, 3 показаны только три зоны пересечения между управляющей шиной WL и шинами BL 10 данных.

При создании в ячейке 13 разности Vs потенциалов между противолежащими электродами, т.е. управляющей шиной WL и шиной BL данных, ферроэлектрический материал в данной ячейке будет подвергаться действию электрического поля Е, что вызовет поляризационный отклик. Данный отклик может быть задан и сохранен в одном из двух стабильных состояний, соответствующих положительной и отрицательной поляризации, как это следует из фиг.1. Эти два состояния представляют двоичные состояния "1" и "0". Аналогичным образом, состояние поляризации ячейки 13 может быть изменено или считано путем повторного приложения разности потенциалов между двумя противолежащими электродами WL и BL и адресации к ячейке 13. Это приведет к тому, что после снятия разности потенциалов поляризация останется неизменной или переключится на противоположное направление. В первом случае в качестве отклика на приложенное напряжение будет протекать малый ток, тогда как во втором случае изменение поляризации приведет к протеканию значительного тока.

Для того чтобы решить, имеет место "0" или "1", ток сравнивается с опорным значением, которое может быть получено различными методами (не изображены). Если считывание является деструктивным, состояние поляризации в некоторых ячейках будет переключено на противоположное. Например, состояние поляризации в ячейке может быть переключено на "0" независимо от того, какое состояние ("1" или "0") было считано. Начальное состояние может быть вновь записано в ячейку, входящую в состав памяти, для того, чтобы сохранить информацию, имеющуюся в памяти, т.е. считанное значение. Более детальное описание того, как функционирует пассивная матричная память, будет дано далее, при описании предпочтительного варианта изобретения.

Далее, также чтобы облегчить понимание настоящего изобретения, будет дана ссылка на фиг.4, иллюстрирующую другой способ считывания для пассивной матричной памяти 11, далее именуемый "считывание полного информационного слова". В соответствии с этим способом активная управляющая шина WL (на фиг.4 это первая управляющая шина WL1), связанная с интересующей ячейкой 13 памяти, считывается по всей длине строки, т.е. в каждой ячейке 13 памяти, определяемой шиной ВL1,... BLn. Считывание полного информационного слова само по себе представляет известную концепцию, описанную, например, в документе US-A 6157578. Однако решение, описанное в указанном документе, относится к активному матричному запоминающему устройству и служит цели повышения скорости переноса данных, хранящихся в относительно крупном блоке матричной памяти. Настоящее изобретение, напротив, относится только к пассивной матричной памяти. В связи с этим известные решения, относящиеся к активным матрицам, являются для него нерелевантными, поскольку в активных устройствах не возникают проблемы помех для неадресуемых ячеек.

Необходимо отметить, что в соответствии с протоколом подачи импульсов для считывания полного информационного слова в пассивной матричной памяти неиспользуемые управляющие шины (в рассматриваемом случае шины WL2,... m) могут находиться под тем же потенциалом или, по существу, под тем же потенциалом, что и шины BL1,... n данных. Значение тока I зависит от состояния поляризации каждой ячейки 13; оно определяется средствами 26 считывания, по одному на каждую шину BL данных, как это показано на фиг.4. Средствами считывания могут, например, служить усилители считывания.

Способ считывания полного информационного слова обеспечивает несколько преимуществ. Например, напряжение считывания может быть выбрано намного более высоким, чем коэрцитивное напряжение, не вызывая частичного переключения в неадресуемых ячейках; при этом данный способ пригоден для большой матрицы.

Фиг.5-7 иллюстрируют предпочтительные варианты настоящего изобретения. На фиг.7 представлены временные диаграммы, которые соответствуют нулевым возмущениям для неадресуемых ячеек памяти при подаче напряжения Vs на все ячейки активной управляющей шины WL1 во время считывания всех ячеек в активном сегменте. Предпочтительная временная диаграмма дана на фиг.7а, а альтернативная временная диаграмма - на фиг.7b.

Как можно видеть из фиг.5, где представлен предпочтительный вариант пассивной матричной памяти по настоящему изобретению, соответствующая матрица имеет размерность m× n, т.е. образована m управляющими шинами WL1,... m и n шинами BL1,... n данных. Управляющие шины разделены на q сегментов S, причем каждый сегмент задается k смежными шинами BL данных матрицы. Предпочтительно значения k равны для всех сегментов, так что q· k=n. Для считывания первая шина данных в каждом сегменте S может быть подключена посредством первого мультиплексора 251 к первому средству 261 считывания. Вторая шина данных в каждом сегменте должна быть соответственно связана со вторым мультиплексором 252; соответственно k-ая линия в каждом сегменте будет связана с последним мультиплексором 25k.

Количество мультиплексоров (MUX) 25, следовательно, должно быть равно наибольшему количеству шин BL данных, задающих сегмент. Разумеется, ничего не препятствует тому, чтобы количество шин данных в каждом сегменте S было различным; однако, если ячейки памяти на шинах данных сегмента содержат информационные слова одинаковой длины, значение k будет одним и тем же для всех сегментов. Каждый мультиплексор 25 соединен со средством 26 считывания для считывания данных. Количество средств 26 считывания соответственно также будет равно наибольшему количеству k шин BL данных, задающих сегмент.

В отличие от обычных вариантов пассивной матричной памяти, в которых используется частичное считывание, все ячейки 13 памяти в сегменте управляющей шины одновременно присоединены к средствам 26 считывания, так что все битовые точки на сегменте управляющей шины могут считываться параллельно. Конкретным вариантом средств считывания могут служить усилители считывания. Для облегчения понимания на фиг.5 показаны только два первых сегмента S1, S2 и последний сегмент Sq; это справедливо также для мультиплексоров 25 и для усилителей 26 считывания.

Доступ к данным, которые хранятся и/или должны храниться в матричной памяти 11, может быть осуществлен с помощью ассоциированных декодера строки и декодера столбца, которые на фиг.5 не изображены. Данные, которые записаны в ячейках 13 матричной памяти 11, могут быть считаны с использованием протокола подачи импульсов, например, как это было упомянуто в связи с фиг.5, с помощью усилителей 26 считывания, которые соединены с шинами BL данных через мультиплексоры 25. Все шины BL данных, которые задают один сегмент S, связаны с мультиплексорами 25, и выбор этих шин производится только тогда, когда заданная управляющая шина WL в этом сегменте является активной. В соответствии с данным способом все шины данных, соответствующие активной управляющей шине WL в сегменте S, считываются параллельно в конфигурации "считывание полного информационного слова", причем все шины данных распределены между усилителями 26 считывания.

В практических применениях пассивное запоминающее устройство может представлять собой, например, память объемом 16 Мбит, разделенную на 8 сегментов S(q=8), и содержать 256000 управляющих шин WL, каждой из которых соответствует 64 бита. В этом случае в каждом сегменте S будет 8 шин BL данных, т.е. k=8. Возможны, конечно, и другие архитектуры, например с 9, 16 или 32 битами в каждом сегменте S.

В другом предпочтительном варианте осуществления изобретения в каждом сегменте имеются, по меньшей мере, 256 ячеек 13 памяти. В случае использования мультиплексоров 25 32:1 ширина матрицы будет соответствовать 8192 битам при дублировании только 32 драйверов управляющих шин. Разумеется, каждая управляющая шина будет сегментирована в соответствии с количеством используемых усилителей 26 считывания.

На фиг.6 показан альтернативный вариант выполнения запоминающего устройства согласно изобретению. В этом варианте мультиплексоры заменены вентильными средствами 25. Вентильные средства 25 активируют шины BL данных таким же образом, что и мультиплексоры.

Предпочтительно выполнить вентильные средства 25 в виде пропускающих вентилей, соединенных с каждой шиной BL данных в сегменте S. В то время как количество мультиплексоров 25 в варианте по фиг.5 должно быть равно количеству шин BL данных в сегменте S, т.е. k, количество пропускающих вентилей в варианте по фиг.6 должно соответствовать количеству q сегментов S. Количество выходов на каждом пропускающем вентиле соответствует количеству шин BL данных в соответствующем сегменте S. Для того чтобы обеспечить параллельное считывание ячеек 13 памяти активной управляющей шины WL в сегменте S, для каждой шины BL в сегменте используется отдельный усилитель 26 считывания. При этом каждый усилитель 26 считывания соединен с одной из линий 27, входящих в состав информационной шины 28. Первый выход пропускающего вентиля соединен с первой линией 271 информационной шины; его второй выход - со второй линией 272 этой шины и т.д. Количество линий 27 и усилителей считывания равно, очевидно, наибольшему количеству шин BL данных, которые определяют сегмент S.

На фиг.7а и 7b приведены альтернативные временные диаграммы для цикла считывания полного информационного слова.

На фиг.7а приведена временная диаграмма цикла записи/считывания ("восстановление", "повторная запись") полного информационного слова для сегмента управляющей шины. Приведенная временная диаграмма основана на четырехуровневом протоколе. В соответствии с этой диаграммой в период, когда не происходит считывания или записи ни в какую ячейку памяти матрицы, все управляющие шины и все шины данных находятся под исходным напряжением, соответствующим нулевому напряжению. Каждая ячейка памяти имеет адрес, который задается пересечениями активированной управляющей шины WL и всех шин BL данных, входящих в сегмент, подлежащий считыванию.

Во время цикла считывания неактивные управляющие шины WL и все шины BL данных следуют одной и той же кривой изменения потенциала. Во время цикла считывания управляющая шина, контактирующая с ячейками, подлежащими считыванию, находится под переключающим напряжением VS. В этом временном интервале все шины данных находятся под нулевым напряжением. Применительно к представленной временной диаграмме приложение переключающего напряжения VS на сторону ячейки, соответствующую управляющей шине, и нулевого напряжения на другую сторону той же ячейки, соответствующую шине данных, означает, что в ячейку записывается "0". Таким образом, для обеих представленных диаграмм после завершения операции считывания все ячейки на активных управляющих шинах приводятся в состояние, соответствующее "0". Следовательно, для того чтобы восстановить данные, записанные в памяти, будет необходимо повторно записать "1" только на тех шинах данных, которые имеют ячейки, которые должны содержать "1". Эта операция на обеих приведенных диаграммах соответствует подаче на ячейку, в

которой должна быть записана "1", напряжения обратной полярности во время цикла записи.

Фиг.7b соответствует альтернативной временной диаграмме, основанной на четырехуровневом протоколе. В соответствии с данным вариантом в период, когда не происходит считывания или записи ни в какую ячейку памяти матрицы, все управляющие шины и все шины данных находятся под исходным напряжением VS/3.

В вариантах осуществления изобретения по фиг.5 и 6 управляющие шины могли быть в принципе непрерывными, т.е. они проходят без разрывов через все отдельные сегменты, которые определяются только соответствующими шинами данных. В подобном случае необходимо использовать мультиплексирование и адаптированные к этому протоколы считывания и записи. Однако использование слишком длинных управляющих шин не дает никакого преимущества. Эта проблема не возникает в случае ограниченного количества сегментов и ограниченного количества шин данных в каждом сегменте, как это имело место в рассмотренном ранее примере, где использовались 256000 управляющих шин и 8 сегментов с 8 шинами данных в каждом сегменте. Емкость памяти в этом случае, как уже указывалось, составит 16 Мбит.

Однако непрерывные управляющие шины обладают и другими недостатками. Если битовые точки, соответствующие ячейкам памяти в сегмент S, считываются при высоком напряжении на активной управляющей шине, то же самое высокое напряжение будет приложено ко всей активной управляющей шине во всех сегментах. В результате, хотя будут подсоединены только шины данных в адресуемых сегментах, могут иметь место емкостные связи и паразитные токи, оказывающие влияние, например, на ячейки памяти, соответствующие смежным неактивным управляющим шинам в том же сегменте. Это может привести к появлению ложных сигналов или шумовой составляющей. Как следствие, в практических реализациях запоминающего устройства согласно изобретению представляется желательным иметь возможность сегментации управляющих шин электрическим путем таким образом, чтобы управляющая шина была подключена к драйверу только в пределах адресуемого сегмента. В то же время соответствующие сегменты управляющей шины в остальных сегментах должны оставаться неподключенными. Такой подход особенно релевантен в случае применения протокола по фиг.7; причем он может быть реализован в варианте запоминающего устройства по фиг.8, который в основных чертах соответствует варианту по фиг.5.

Неизображенный драйвер, входящий в группу 20 драйверов, выбирается посредством селектора 22 сегмента (который, например, может быть выполнен в виде селекторной шины) таким образом, что происходит активация управляющей шины WL в выбранном сегменте S для выполнения цикла считывания или записи. Мультиплексоры 25, которые управляются селектором 22 сегмента, могут быть соединены с выбранным драйвером в группе 20 посредством переключателей 24; их управление от селектора 22 осуществляется через переключаемую кэш-память 21. Конкретный мультиплексор 25 одновременно адресуется для соединения шин BL данных в адресуемом сегменте с усилителем 26 считывания. Из чисто практических соображений каждая управляющая шина WL в сегменте может быть присоединена к логическому элементу "И", например к CMOS-вентилю или пропускающему вентилю. При этом сегмент будет адресоваться через управляющую шину или дешифратор адреса. Например, в сегменте S1 выбирается управляющая шина WL1, и напряжение в данном сегменте будет подано только на эту управляющую шину. В этом случае при деструктивном считывании все ячейки памяти и управляющие шины WL1 в пределах сегмента S1 будут находиться под нулевым напряжением, в то время как мультиплексор 25 подсоединяет все шины данных в сегменте S1 к соответствующим усилителям 261...26k считывания. При этом может быть осуществлено считывание всех ячеек на активированной управляющей шине, т.е. в том случае, если управляющая шина в сегменте была задана таким образом, чтобы включить информационное слово, обеспечивается возможность считать полное информационное слово.

В то время, как производится детектирование состояния всех ячеек на выбранной управляющей шине WL1, остальные управляющие шины WL2...WLm и шины BL1-BLk находятся под исходным напряжением, близким к напряжению смещения на усилителях 26 считывания. В принципе, в этом случае не будет возникать мешающий вклад от остальных ячеек в сегменте. Не будет также напряжения смещения на ячейках, связанных с шиной данных, которое могло бы привести к появлению мешающих сигналов на входе усилителей 26 считывания. Данные на выходе усилителя 26 считывания переносятся на двустороннюю информационную шину 23, в то время как логический контур 29 записи включен параллельно выходу мультиплексоров для записи данных в битовые точки ячеек на активной управляющей шине в сегменте. При этом управляющие шины выбираются соответствующим образом посредством селектора 22, как и в случае считывания.

Предпочтительно также предусмотреть буферные блоки 21 памяти на переключаемых выходах селектора 22. Эти блоки связывают драйверы и мультиплексоры 25 посредством множества переключателей 24 линий, управляемых селектором 22.

На фиг.9 представлен вариант, функционально эквивалентный варианту по фиг.8 и в то же время имеющий сходство с вариантом по фиг.6, а именно использующий вентильные средства вместо мультиплексоров 25. Каждое вентильное средство может содержать переключающие транзисторы 25а, по одному на каждую шину, которые функционируют, как пропускающие вентили. Таким образом, в вентильном средстве 25 будет содержаться k переключающих транзисторов 25а. Как и в варианте по фиг.8, предусмотрены группы 20 драйверов по одной на каждый сегмент, тогда как селектор 22 заменен селектором 22а группы драйверов. Адресация отдельной управляющей шины WL осуществляется с выхода шины 30 адресации управляющих шин под управлением селектора 22а группы драйверов. При считывании шины BL данных подсоединяются к линиям 27 информационной шины 28, а информационный выход усилителя считывания подсоединен к двусторонней информационной шине 23. Подобно варианту по фиг.8, имеется логический контур 29 записи, включенный параллельно усилителям 26 считывания. Когда производится запись, соответствующий сегмент управляющей шины выбирается с помощью селекторов 22а групп драйверов, с адресацией через шину 30 адресации управляющей шины.

Такие необходимые устройства и средства для селекции, декодирования и адресации, как, например, логический контур синхронизации, хорошо известны специалистам в данной области и широко применяются в запоминающих устройствах с матричной адресацией, где они являются активными или пассивными. Поэтому в их детальном описании нет необходимости.

Количество используемых уровней напряжения и конкретные значения этих уровней, используемые в протоколе подачи импульсов, могут выбираться достаточно свободно при условии, что выполняются требования для осуществления считывания полного информационного слова. При этом полярность напряжений в используемом протоколе может быть изменена на обратную.

При изготовлении реальных контуров для воплощения запоминающего устройства по настоящему изобретению матричная память может быть выполнена на подложке с интегрированными в нее драйверами управляющей шины с тем, чтобы не увеличивать общую площадь устройства.

Сегментированные управляющие шины могут быть также применены при использовании памяти в виде образующих стопу слоев. В этом случае шины BL данных соединяются по вертикали с мультиплексорами 25 или вентильными средствами. Это иллюстрируется фиг.10, представляющей собой схематичное, в сечении изображение варианта изобретения, в котором запоминающие устройства 10 по настоящему изобретению собраны в стопу. Тем самым реализуется устройство трехмерного хранения данных, в котором каждый слой (слой М памяти) содержит одно запоминающее устройство 10. Благодаря тому, что запоминающие устройства расположены с взаимным сдвигом, управляющие шины WL и шины данных BL могут быть соединены через так называемые краевые соединители 19 (т.е. чередующиеся горизонтальные и вертикальные соединения, "выступающие за край") с драйверными и управляющими контурами в подложке 16. Подложка 16 (на которую нанесен изолирующий слой 17) может быть неорганической, например, на основе кремния; благодаря этому указанные контуры могут быть реализованы с использованием совместимой CMOS-технологии. На фиг.10 показаны только два слоя M1, M2 памяти, разделенных промежуточным диэлектрическим слоем 18 (и только ограниченное количество шин данных), однако реальное устройство трехмерного хранения данных может содержать очень большое количество слоев памяти, от 8 и до свыше 100 и более. В результате будет реализована память с очень большой емкостью и высокой плотностью записи, поскольку каждый слой памяти будет иметь толщину около 1 мкм или даже менее.

Достоинства данной пассивной матричной памяти - это простота изготовления и высокая плотность расположения ячеек. Другие достоинства состоят в следующем.

а) Если управляющие шины сегментированы электрически, неадресуемые ячейки памяти в течение цикла считывания будут находиться под нулевым потенциалом (или малым потенциалом), если используется протокол по фиг.7а. Это приведет к уменьшению количества мешающих сигналов, которые могли бы привести к потере содержимого памяти, а также к устранению всех помех во время операции считывания, приводящих к возникновению паразитных токов.

б) Скорость переноса данных будет соответствовать максимальной скорости, определяемой количеством шин данных в сегменте.

в) Напряжение VS считывания может быть выбрано намного большим, чем коэрцитивное напряжение, и это не приведет к частичному переключению в неадресуемых ячейках. Как следствие, можно использовать скорости переключения, приближающиеся к максимально возможной скорости для соответствующего поляризуемого материала ячеек.

г) Способ считывания совместим с крупными матрицами.

Кроме того, запоминающее устройство согласно изобретению может быть реализовано с меньшим количеством усилителей считывания. Это является существенным преимуществом в случае памяти большого объема, а также в отношении мощности, потребляемой усилителями считывания. Данная мощность может быть довольно высокой, но ее можно понизить до некоторой степени за счет правильного управления драйверными контурами и контурами адресации. Далее, сокращение количества усилителей считывания подразумевает, что площадь, выделяемая считывающим средствам, может быть сбалансирована таким образом, чтобы обеспечить общую оптимизацию площади запоминающего устройства. Наконец, сегментация управляющих шин означает, что погрешности во время считывания или адресации в случае дефекта в единственной управляющей шине будут локализованы в единственном информационном слове.

Изобретение относится к запоминающему устройству на основе энергонезависимой матричной памяти. Техническим результатом является возможность локализации погрешностей во время считывания или адресации в единственном информационном слове, устранение возмущений на неадресуемых ячейках. Энергонезависимое запоминающее устройство содержит электрически поляризуемый диэлектрический материал, находящийся в слое, расположенном между первым и вторым наборами адресации с параллельным расположением электродов в пределах каждого набора, управляющие шины и шины данных, средство считывания и средства для подсоединения каждой шины данных к ассоциированному средству считывания. Способ описывает работу указанного устройства. Устройство трехмерного хранения данных содержит множество образующих стопу слоев, каждый из которых содержит одно вышеуказанное энергонезависимое запоминающее устройство. 3 с. и 9 з.п. ф-лы, 10 ил.

| US 5567636 А, 22.10.1996 | |||

| Матричный накопитель и способ управления записью, считыванием и стиранием информации в накопителе | 1987 |

|

SU1596392A1 |

| Машина для нарезания пищевых продуктов на куски правильной формы | 1972 |

|

SU486901A1 |

| US 4599709 A, 08.07.1986 | |||

| IBM Technical Disclosure Bulletin | |||

| Пишущая машина | 1922 |

|

SU37A1 |

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

Авторы

Даты

2005-01-27—Публикация

2001-08-24—Подача