Область техники, к которой относится изобретение

Настоящее изобретение относится в широком смысле к способу управления ферроэлектрическим или электретным запоминающим устройством, содержащим ячейки памяти на основе тонкопленочного поляризуемого ферроэлектрического или электретного материала, обладающего гистерезисом и предпочтительно представляющего собой тонкую ферроэлектрическую или электретную полимерную пленку. Устройство содержит также первый и второй наборы электродов, взаимно параллельных в пределах одного набора. При этом электроды первого набора расположены, по существу, ортогонально по отношению к электродам второго набора; кроме того, электроды первого и второго наборов находятся в прямом или непрямом контакте с тонкопленочным материалом, образующим ячейки памяти. Поляризационное состояние индивидуальных ячеек памяти можно считывать, обновлять или записывать путем подачи соответствующих напряжений на индивидуальные электроды первого и второго наборов. Способ по изобретению реализует протокол подачи импульсов напряжения заданной амплитуды и длительности, включающий циклы считывания и записи/обновления, состоящие из временных последовательностей импульсов напряжения заданной амплитуды и длительности. При осуществлении считывания данных из ячеек памяти цикл считывания предусматривает приложение набора разности напряжений к электродам первого и второго наборов. При осуществлении записи/обновления данных, хранящихся в ячейках памяти, цикл записи/обновления в составе протокола подачи импульсов напряжения предусматривает приложение к электродам первого и второго наборов иного набора разности напряжений. Указанные наборы разностей напряжений соответствуют заданному массиву значений потенциалов, причем этот заданный массив содержит, по меньшей мере, три отдельных значения потенциала.

Изобретение относится также к ферроэлектрическому или электретному запоминающему устройству для осуществления способа согласно изобретению. Данное устройство содержит ячейки памяти на основе тонкопленочного поляризуемого ферроэлектрического или электретного материала, обладающего гистерезисом, например, на основе тонкой ферроэлектрической или электретной полимерной пленки, а также первый и второй наборы электродов, взаимно параллельных в пределах одного набора. Электроды первого и второго наборов расположены, по существу, ортогонально по отношению к электродам другого набора и находятся в прямом или непрямом контакте с тонкопленочным материалом, образующим ячейки памяти. Поляризационное состояние индивидуальных ячеек памяти может быть считано, обновлено или записано путем подачи соответствующих напряжений на индивидуальные электроды первого и второго наборов.

Подача напряжений производится с использованием протокола подачи импульсов напряжения, включающего циклы считывания и записи/обновления, состоящие из временных последовательностей импульсов напряжения заданной амплитуды и длительности. Цикл считывания предусматривает приложение набора разности напряжений к электродам первого и второго наборов с осуществлением считывания данных из ячеек памяти. Цикл записи/обновления в составе протокола подачи импульсов напряжения предусматривает приложение к электродам первого и второго наборов иного набора разности напряжений с осуществлением записи/обновления данных, хранящихся в ячейках памяти. При этом указанные наборы разностей напряжений соответствуют заданному массиву значений потенциалов, причем этот заданный массив содержит, по меньшей мере, три отдельных значения потенциала.

Устройство по изобретению снабжено также блоком управления драйверами для приложения к электродам через драйверные контуры заданного массива значений потенциалов с целью осуществления указанных операций по отношению к выбранным ячейкам памяти в соответствии с протоколом подачи импульсов напряжения, предусматривающим операции считывания и записи/обновления.

Уровень техники

Ферроэлектрики - это электрически поляризуемые материалы, которые при отсутствии электрического поля обладают, по меньшей мере, двумя равновесными ориентациями вектора спонтанной поляризации, причем переключение вектора спонтанной поляризации между этими равновесными ориентациями может быть осуществлено под действием электрического поля. Эффект памяти, имеющий место в подобных материалах с двумя стабильными состояниями остаточной поляризации, может быть использован в запоминающих устройствах. Одно из указанных состояний поляризации рассматривается как логическая "1", а другое - как логический "0". Типичные схемы с пассивной матричной адресацией могут быть реализованы с применением двух взаимно скрещивающихся (предпочтительно ортогональных) наборов электродов (взаимно параллельных в пределах каждого набора). Такие наборы электродов образуют матрицу или массив точек скрещивания, индивидуальный доступ к которым может быть осуществлен селективным возбуждением соответствующих электродов с краев матрицы.

Слой ферроэлектрического материала помещают между наборами электродов с образованием за счет этого в данном материале, в зонах скрещивания электродов, конденсатороподобных структур, действующих в качестве ячеек памяти. При приложении разности потенциалов между двумя электродами ферроэлектрический материал подвергается воздействию электрического поля. Это вызывает поляризационный отклик, как правило, следующий за кривой гистерезиса или ее частью. Задавая направление и напряженность электрического поля можно привести ячейку в желаемое логическое состояние, в котором она будет оставаться. Пассивная адресация описанного типа обеспечивает простоту изготовления и высокую плотность расположения точек скрещивания.

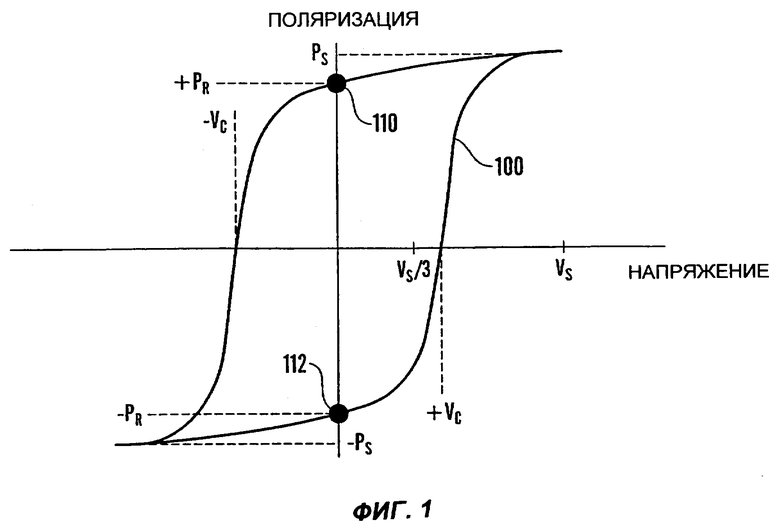

Как показано на фиг.1, материал, обладающий кривой 100 гистерезиса, изменяет направление своей поляризации при приложении к нему электрического поля, которое превосходит коэрцитивное поле Еc. Из соображений удобства приведенная кривая гистерезиса построена с откладыванием по оси абсцисс не напряженности электрического поля, а напряжения. Значения напряжения рассчитываются путем умножения значений напряженности на толщину слоя ферроэлектрического материала. Поляризация Ps насыщения достигается каждый раз, когда ячейка памяти подвергается воздействию номинального переключающего напряжения Vs. Однако на практике в случае приложения более слабых электрических полей будет иметь место частичное переключение. Степень частичного переключения зависит от свойств материала, однако многократное приложение электрических полей, даже имеющих напряженность меньшую, чем напряженность коэрцитивного поля, в конце концов приведет к ухудшению состояний 110, 112 остаточной поляризации +РR, -PR в такой степени, что впоследствии это может привести к ошибкам считывания.

Значения напряженности электрических полей задаются протоколом переключений (называемым также протоколом подачи импульсных напряжений), обеспечивающим подачу напряжений к запоминающему массиву в процессе операций считывания и записи. Выбор соответствующего протокола необходим для того, чтобы при считывании информации из индивидуальной ячейки или при записи в нее избежать возмущающих воздействий на другие ячейки. С этой целью протокол подачи импульсных напряжений предусматривает и обеспечивает подачу определенных заданных напряжений на электроды таким образом, чтобы осуществить выбор ячейки для адресации и произвести операцию адресации, в то же самое время удерживая мешающие влияния на другие ячейки на минимальном уровне. С целью минимизации мешающих воздействий было разработано множество протоколов подачи импульсных напряжений. Некоторые примеры подобных протоколов можно найти в патенте США №3002182, в патенте США №4169258 и в международной заявке WO 02/05287.

Поляризационные свойства ферроэлектрических и электретных материалов, как правило, зависят от факторов окружающей среды, а также от предыдущих адресаций. Это может приводить к проблемам, когда подобные материалы используются в запоминающих устройствах, работающих в различных условиях и в различных рабочих режимах. В этой связи следует отметить, что собственно ферроэлектрические материалы образуют подкласс электретов и характеризуются способностью иметь постоянную поляризацию, соответствующую одному из двух состояний устойчивой поляризации, а также наличием гистерезиса. При дальнейшем рассмотрении уровня техники и предпочтительных вариантов осуществления изобретения в целях облегчения понимания будет, как правило, подразумеваться, что запоминающий материал представляет собой ферроэлектрик, т.е. обладает как гистерезисом, так и двумя поляризациями различной полярности.

Как уже упоминалось, поляризационные свойства могут подвергаться влиянию температуры окружающей среды, в которой находится ферроэлектрический материал. Большинство ферроэлектрических материалов претерпевают структурный фазовый переход из высокотемпературной неферроэлектрической фазы в низкотемпературную ферроэлектрическую фазу. Этот переход имеет место при температуре Тс, называемой точкой Кюри. Для титаната-цирконата свинца, популярного неорганического ферроэлектрического материала, точка Кюри соответствует 360°С. Рабочая температура ферроэлектрического запоминающего устройства обычно существенно ниже данного значения, так что никаких проблем, связанных с точкой Кюри, практически не возникает.

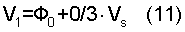

Однако, если ферроэлектрический материал представляет собой полимер, повышение его температуры или повышение температуры устройства в целом становится важным возмущающим фактором. Фиг.2 иллюстрирует одно из возможных влияний, которое повышение температуры оказывает на гистерезисную кривую 100. Более узкая кривая представляет ферроэлектрические свойства материала при повышенной температуре. При этом можно заметить повышение чувствительности к электрическому полю, поскольку коэрцитивное напряжение VCL при низкой температуре является более высоким, чем коэрцитивное напряжение VСН при высокой температуре. Если приложенное электрическое поле остается неизменным, несмотря на изменение температуры, риск нежелательного изменения направления поляризации на обратное под действием напряжения, приложенного к неадресуемым точкам скрещивания, будет возрастать. Кроме того, скорость переключения поляризации в ферроэлектрическом запоминающем материале будет возрастать по мере повышения температуры.

Хорошо известный факт наличия температурной зависимости гистерезисной кривой отмечается в патенте США №5487029. Здесь утверждается, что для того, чтобы предотвратить нежелательную ошибочную запись в ферроэлектрическую память в результате изменения температуры, необходимо настраивать используемое при записи напряжение в соответствии с отрицательной зависимостью от температуры, что соответствует температурным характеристикам гистерезисной кривой. В этой связи рассматривается использование генератора напряжения, вырабатывающего напряжение для записи, которое стабилизировано зенеровским диодом (стабилитроном) с отрицательной температурной характеристикой. Таким образом, стабилитрон обеспечивает корректировку напряжения, адаптируя его к отрицательной температурной зависимости ферроэлектрических конденсаторов. Однако согласование характеристик стабилитрона с гистерезисной кривой ферроэлектрического материала представляет собой сложную задачу. В связи с этим в указанном патенте признается, что для температурной компенсации могут быть использованы и другие методы, однако никаких приемлемых альтернатив не приводится.

Следует также отметить, что техника в рассматриваемой области развивалась в контексте неорганических керамических ферроэлектрических материалов. Такие материалы, как правило, сохраняют свою физическую целостность и ферроэлектрические свойства в температурном интервале, существенно превышающем температуры, при которых работают реальные запоминающие устройства. В качестве примера можно еще раз указать на титанат-цирконат свинца (PZT), у которого точка Кюри, выше которой исчезает спонтанная поляризация, соответствует 360°С. Значительный контраст с подобными свойствами проявляет развивающийся класс запоминающих устройств, основанных на использовании ферроэлектрических органических веществ (полимеров), у которых точка Кюри и/или точка плавления лежат ниже 200°С. Подобные материалы обладают существенными преимуществами в терминах обрабатываемости, стоимости, гибкости в техническом аспекте и др. Вместе с тем, в некоторых случаях они могут создавать проблемы в связи с изменением их электрических характеристик вследствие изменения температуры в пределах заданного рабочего интервала температур.

Кроме того, исследования ферроэлектрических запоминающих материалов и ферроэлектрической памяти с пассивной матричной адресацией, проведенные заявителем настоящего изобретения, обнаружили, что характеристики переключения запоминающих материалов в виде ферроэлектрических полимеров не имеют простой зависимости от температуры. При этом зависимость данных характеристик от рабочей температуры может носить более сложный характер и проявляться в том, что повышение температуры не всегда вызывает, как это можно было бы ожидать, соответствующее повышение скорости переключения

В дополнение к этому было обнаружено, что изменения скорости переключения запоминающего материала могут иметь место и под действием других факторов окружающей среды, отличных от температуры. Другими словами, такие факторы могут быть связаны с влиянием окружающей среды, включая ее температуру, но не ограничиваясь ею. Так, влияние на ферроэлектрические свойства полимера могут оказывать, например, атмосферная влажность, механические напряжения, электрические напряжения, а также предыдущая история адресации к ячейкам памяти. В общем случае можно утверждать, что динамический отклик ячейки памяти будет зависеть от большого количества факторов. При этом, хотя и не требуется изолировать отдельные вклады от данных факторов, совершенно ясно, что их суммарный вклад влияет тем или иным образом на динамические показатели отклика запоминающего материала. Для того чтобы в общем виде устранить подобное влияние, следовало бы отслеживать отклик ячейки памяти на операцию адресации путем сравнения мгновенного отклика с эмпирически определенным опорным откликом, т.е. с откликом, полученным при тщательно контролируемых условиях. После этого следует настроить параметры импульсного напряжения, подаваемого в рамках протокола, применяемого при осуществлении операций адресации в памяти с пассивной матричной адресацией, в которой в качестве запоминающего материала используется ферроэлектрический полимер.

Говоря более конкретно, протокол подачи импульсов напряжения задает уровни напряжения, которые должны подаваться в определенной временной последовательности на соответствующие активные и неактивные линии управления и линии данных при выполнении операции адресации. Таким образом, в этом своем аспекте протокол подачи импульсов напряжения определяет длительности не только импульсов, но и интервалов между ними. Другими словами, при прочих равных условиях параметры протокола подачи импульсов напряжения должны рассматриваться как выбранные и зафиксированные применительно к осуществлению операций адресации. Однако исследования, проведенные заявителем настоящего изобретения, ясно показали, что отклик ячейки памяти, характеризуемый соответствующим параметром (например, скоростью переключения или ее производной по времени), представляет собой динамичную величину. Иначе говоря, этот отклик изменяется во времени в зависимости от различных факторов, рассмотренных выше. Кроме того, важным фактором может являться предыдущая история адресации. Как уже отмечалось, в число факторов входит и реальная рабочая температура запоминающего материала (которая ранее упрощенно принималась равной температуре окружающей среды при условии, что устройство находится в состоянии теплового равновесия; однако такое равенство не всегда имеет место). При этом рабочая температура, в частности ячейки памяти, может зависеть как от текущих операций адресации, так и от истории адресации, а также от теплоты, рассеиваемой сопутствующими электронными контурами.

Раскрытие изобретения

В связи с изложенным основной задачей, решаемой настоящим изобретением, является разработка способа, обеспечивающего устранение или ослабление проблем, вызываемых изменениями гистерезисной кривой, коэрцитивного напряжения и скорости переключения применительно к операциям адресации в ферроэлектрических или электретных запоминающих устройствах. Таким образом, указанная основная задача, по существу, состоит в устранении изменений или дрейфа отклика ячеек памяти под влиянием окружающей среды, истории адресации и различных напряжений, возникающих в процессе работы ферроэлектрической или электретной памяти, независимо от того, обусловлены ли указанные напряжения механическими, электрическими, химическими или тепловыми факторами или их комбинацией.

Задача, поставленная перед изобретением, заключается также в разработке способа компенсации изменений скорости переключения без применения контуров для стабилизации напряжения, которые обычно являются чувствительными к температурным эффектам и которым присущ дрейф. Более конкретно, задача состоит в разработке способа температурной компенсации, применимого к параметрам протокола подачи импульсов напряжения и особенно эффективного при использовании применительно к полимерным ферроэлектрическим или электретным запоминающим материалам в виде тонких пленок.

И, наконец, задачей, поставленной перед изобретением, является разработка ферроэлектрического или электретного запоминающего устройства, реализующего способ по изобретению.

Решение перечисленных задач, а также достижение других особенностей и преимуществ обеспечено созданием способа, который характеризуется операциями:

(а) определения, по меньшей мере, одного параметра, характеризующего изменение отклика ячеек памяти на прикладываемые к ним разности напряжений;

(б) определения, по меньшей мере, одного корректирующего фактора для импульсов напряжения, входящих в состав протокола подачи импульсов напряжения, на основе указанного, по меньшей мере, одного параметра, характеризующего изменение отклика ячеек памяти на прикладываемые к ним разности напряжений;

(в) выбора для корректировки протокола подачи импульсов напряжения, по меньшей мере, одного из следующих параметров указанного протокола: амплитуд импульсов, длительностей импульсов и интервалов между импульсами;

(г) корректировки одного или более значений, по меньшей мере, одного из выбранных параметров протокола подачи импульсов напряжения в соответствии с указанным, по меньшей мере, одним корректирующим фактором, с обеспечением тем самым корректировки одной или более амплитуд импульсов, одной или более длительностей импульсов и одного или более интервалов между импульсами либо по отдельности, либо в комбинации в соответствии с обнаруженным изменением отклика ячеек памяти.

В соответствии с изобретением представляется предпочтительным корректировать значения амплитуд импульсов и/или длительностей импульсов напряжения, обеспечивающих переключение, в составе протокола подачи импульсов напряжения.

В одном из желательных вариантов способа согласно изобретению определение, по меньшей мере, одного параметра, характеризующего изменение отклика, при выполнении операции (а) осуществляют путем определения, по меньшей мере, одного параметра, характеризующего скорость переключения в ферроэлектрическом запоминающем устройстве, а определение, по меньшей мере, одного корректирующего фактора при выполнении операции (б) осуществляют путем определения корректирующего фактора, зависящего от скорости переключения.

В данном варианте рекомендуется определять, по меньшей мере, один параметр, характеризующий скорость переключения, при выполнении операции (а) путем измерения мгновенной скорости переключения в ферроэлектрическом запоминающем устройстве. В этом случае измерение скорости переключения предпочтительно осуществляют путем измерения скорости переключения одной или более опорных ячеек памяти или, альтернативно, путем анализа текущих операций адресации, включающих переключение ячеек памяти в ферроэлектрическом запоминающем устройстве.

Кроме того, в данном варианте рекомендуется определять, по меньшей мере, один параметр, характеризующий скорость переключения, при выполнении операции (а) путем непрерывного мониторинга скорости переключения в ферроэлектрическом запоминающем устройстве. При этом корректируют протокол подачи импульсов напряжения посредством создания с помощью, по меньшей мере, одного корректирующего фактора, зависящего от скорости переключения, прикладываемых разностей напряжения. Указанный протокол настраивают в реальном времени в соответствии с изменением в отклике на приложенные разности напряжений, причем настроенный в реальном времени протокол подачи импульсов напряжения применяют для корректировки, по меньшей мере, одного из значений параметра протокола подачи импульсов напряжения при выполнении операции (г).

Корректирующий фактор, зависящий от скорости переключения, при выполнении операции (б) может быть предпочтительно определен путем вычислений или считывания из таблицы соответствия. Альтернативно, при выполнении операции (б) могут быть определены первый и второй корректирующие факторы, зависящие от скорости переключения.

Согласно другому предпочтительному варианту способа по изобретению определение, по меньшей мере, одного параметра, характеризующего изменение отклика, при выполнении операции (а) может быть осуществлено путем определения, по меньшей мере, одного параметра, характеризующего температуру запоминающего устройства. Соответственно определение, по меньшей мере, одного корректирующего фактора при выполнении операции (б) может быть осуществлено путем определения, по меньшей мере, одного корректирующего фактора, зависящего от температуры.

В данном варианте желательно, чтобы определение, по меньшей мере, одного параметра, характеризующего температуру, при выполнении операции (а) осуществлялось путем прямого определения рабочей температуры ферроэлектрического запоминающего устройства. Соответственно определение корректирующего фактора, зависящего от температуры, при выполнении операции (б) осуществляют путем вычислений или считывания из таблицы соответствия.

В качестве альтернативы при выполнении операции (б) осуществляют определение первого и второго корректирующих факторов, зависящих от температуры. В таком случае первый корректирующий фактор предпочтительно определяют как температурный коэффициент. Данный коэффициент используют при выполнении операции (г) для корректировки всех значений, по меньшей мере, одного из параметров протокола подачи импульсов напряжения. Второй корректирующий фактор предпочтительно определяют как напряжение смещения, которое используют при выполнении операции (г) для корректировки, по меньшей мере, одного значения амплитуды или значения (уровня) потенциала.

В рамках рассматриваемого варианта представляется желательным корректировку значений параметра при выполнении операции (г) сначала осуществлять путем первой корректировки в соответствии с первым корректирующим фактором, зависящим от температуры, а затем путем второй корректировки в соответствии со вторым корректирующим фактором, зависящим от температуры. В той же мере желательным представляется осуществлять указанную корректировку сначала путем первой корректировки в соответствии со вторым корректирующим фактором, зависящим от температуры, а затем путем второй корректировки в соответствии с первым корректирующим фактором, зависящим от температуры.

В соответствии с еще одним предпочтительным вариантом способа по изобретению определение, по меньшей мере, одного параметра, характеризующего изменение отклика, при выполнении операции (а) осуществляют путем определения, по меньшей мере, одного параметра, характеризующего температуру запоминающего устройства, посредством измерения скорости переключения ячеек памяти в запоминающем устройстве и использования установленной корреляции между измеренной скоростью переключения и действительной температурой запоминающего материала ячеек памяти для определения указанной действительной температуры.

В этой связи измерение скорости переключения осуществляют путем измерения скорости переключения одной или более опорных ячеек памяти. Альтернативно, данное измерение осуществляют путем анализа текущих операций адресации, вызывающих переключение ячеек памяти в ферроэлектрическом запоминающем устройстве.

Решение перечисленных выше задач, поставленных перед изобретением, а также реализация дополнительных особенностей и преимуществ достигнуты также созданием ферроэлектрического или электретного запоминающего устройства. Устройство по изобретению характеризуется тем, что содержит:

средство для определения, по меньшей мере, одного параметра, характеризующего изменение отклика ячеек памяти на прикладываемые к ним разности напряжений;

калибровочную память, присоединенную к выходу указанного средства для определения, на основе указанного параметра, характеризующего изменение отклика ячеек памяти, по меньшей мере, одного корректирующего фактора,

один или более контроллеров, присоединенных к выходу калибровочной памяти для осуществления корректировки одного или более значений, по меньшей мере, одного параметра протокола подачи импульсов напряжения, причем контроллеры присоединены также к управляющим входам управляющего блока и/или блока управления драйверами.

Устройство по изобретению снабжено также декодерами строк и столбцов, включенными между выходами блока управления драйверами и электродами. При этом оно выполнено с возможностью подачи импульсов напряжения в составе протокола, скорректированного в соответствии с изменением отклика ячеек памяти, через драйверные контура и декодеры строк и столбцов на электроды.

В предпочтительном варианте указанное средство соединено с одной или более парами опорных ячеек памяти. Желательно также, чтобы между набором усилителей считывания и калибровочной памятью был включен анализатор сигналов для проведения анализа отклика ячеек памяти при осуществлении применительно к ним операций считывания или записи/обновления.

Представляется, кроме того, желательным, чтобы в запоминающем устройстве по изобретению указанное средство содержало датчик температуры для определения рабочей температуры ферроэлектрического запоминающего устройства. В этом случае датчик температуры, калибровочная память и драйверные контуры могут быть выполнены в составе контура температурной компенсации. Данный контур температурной компенсации может представлять собой как аналоговый, так и цифровой контур.

Краткое описание чертежей

Настоящее изобретение будет пояснено далее более подробно при рассмотрении вариантов его осуществления, приводимых в качестве примеров и сопровождающихся ссылками на прилагаемые чертежи.

На фиг.1, как уже упоминалось, схематично представлена кривая гистерезиса для ферроэлектрического запоминающего материала.

На фиг.2, как уже упоминалось, дано сопоставление двух кривых гистерезиса, принадлежащих одному ферроэлектрическому запоминающему материалу и зарегистрированных при различных температурах.

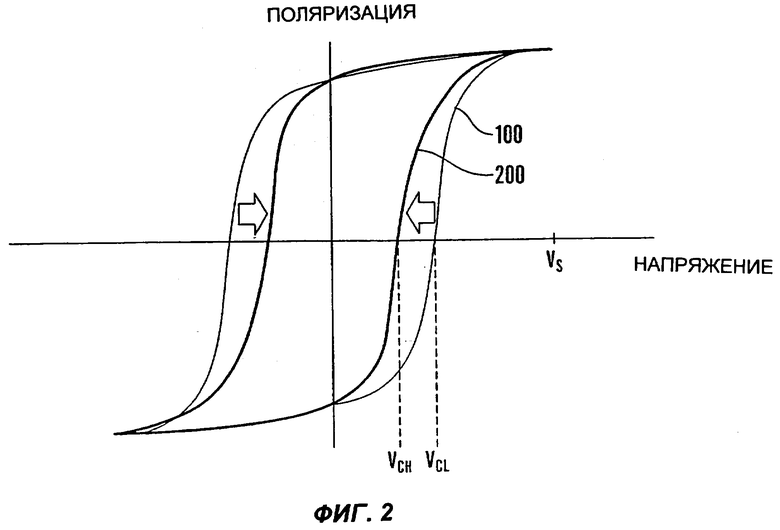

Фиг.3 представляет собой блок-схему, иллюстрирующую запоминающий контур в соответствии с предпочтительным вариантом его выполнения.

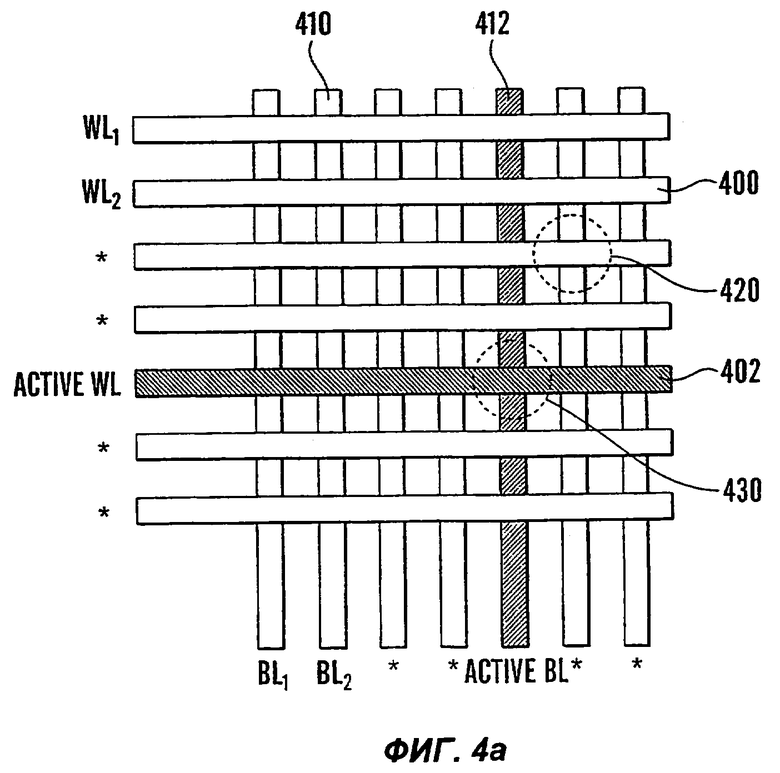

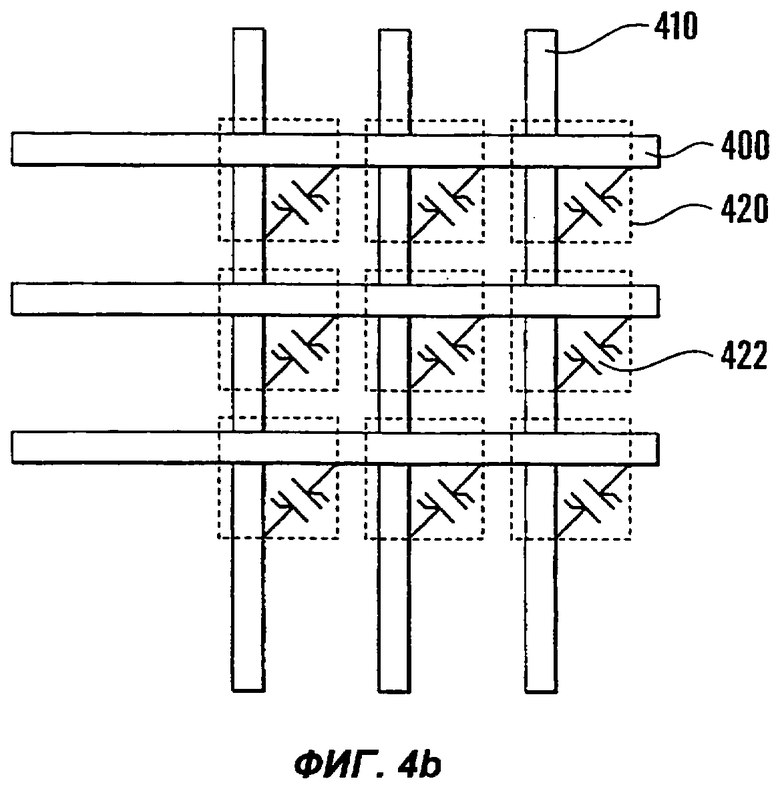

Фиг.4а поясняет принцип построения памяти с пассивной матричной адресацией.

Фиг.4b поясняет принцип построения пассивной матричной памяти, ячейки которой содержат ферроэлектрический материал, локализованный между взаимно налагающимися скрещенными электродами.

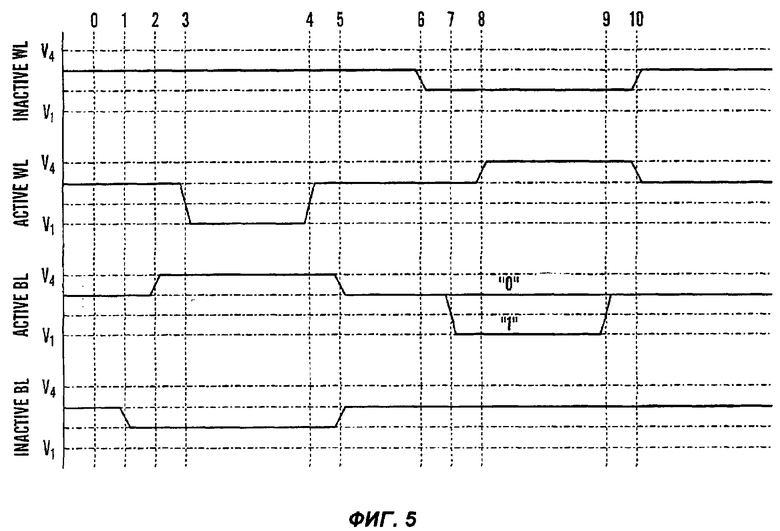

Фиг.5 иллюстрирует протокол подачи импульсов напряжения при считывании и записи с четырьмя различными значениями потенциала, подаваемого на управляющие линии и на линии данных.

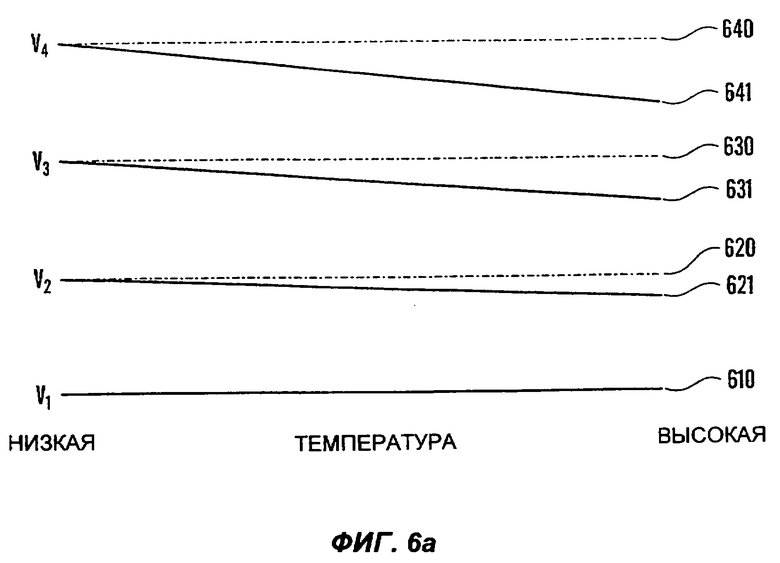

На фиг.6а схематично показаны значения потенциала, используемые в протоколе переключения и изменяющиеся в зависимости от температуры в соответствии с первым предпочтительным вариантом изобретения.

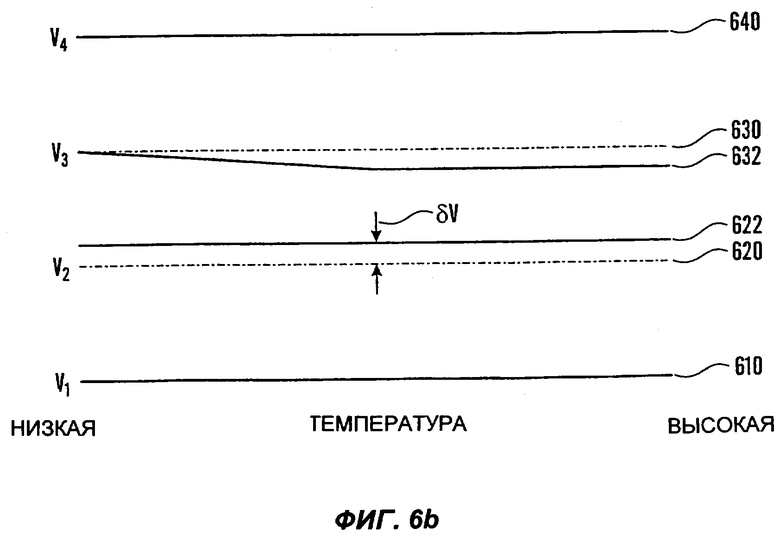

На фиг.6b схематично показаны значения потенциала, используемые в протоколе переключения и изменяющиеся в зависимости от температуры в соответствии со вторым предпочтительным вариантом изобретения.

На фиг.6с схематично показаны значения потенциала, используемые в протоколе переключения и изменяющиеся в зависимости от температуры в соответствии с третьим предпочтительным вариантом изобретения.

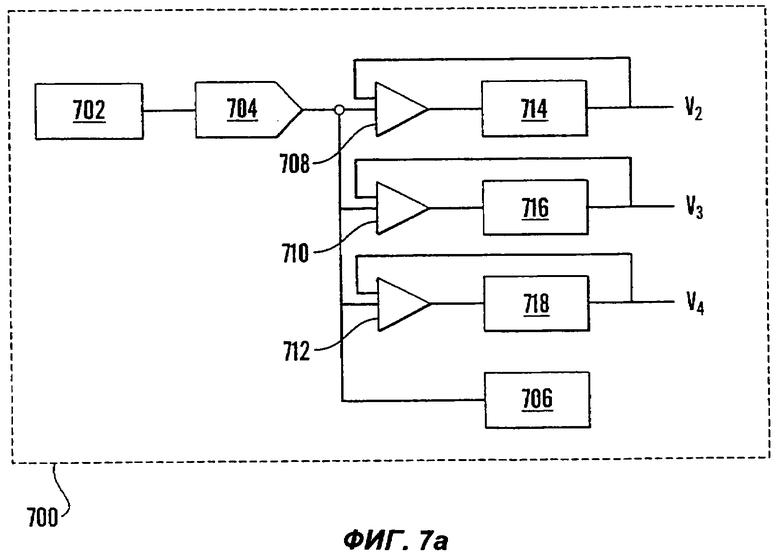

Фиг.7а представляет собой блок-схему, иллюстрирующую аналоговый контур температурной компенсации согласно изобретению.

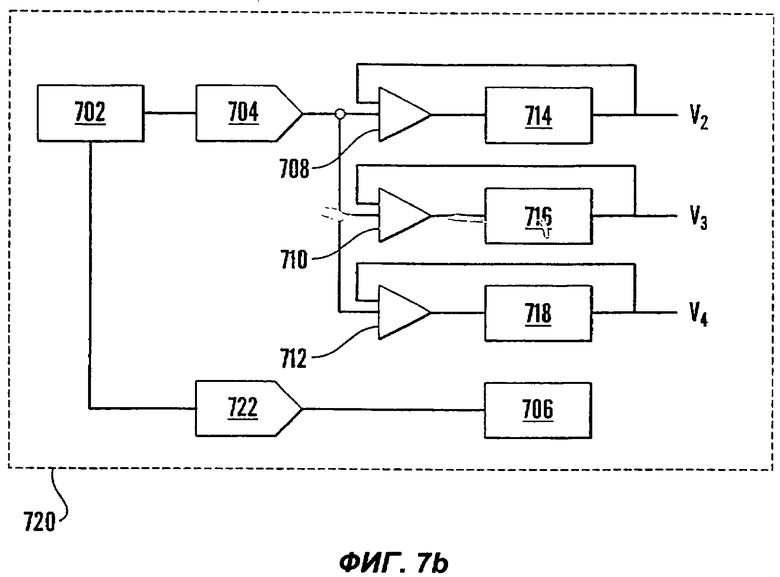

Фиг.7b представляет собой блок-схему, иллюстрирующую цифровой контур температурной компенсации согласно изобретению.

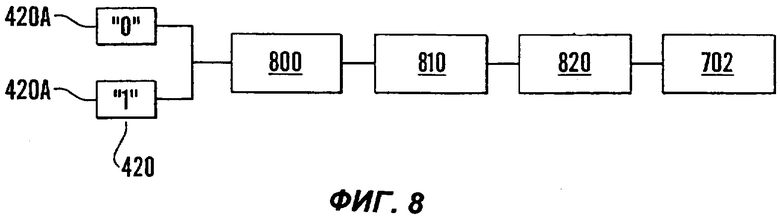

Фиг.8 представляет собой блок-схему, иллюстрирующую систему, соответствующую дальнейшему развитию контуров температурной компенсации по фиг.7а и 7b для определения действительной скорости переключения согласно изобретению.

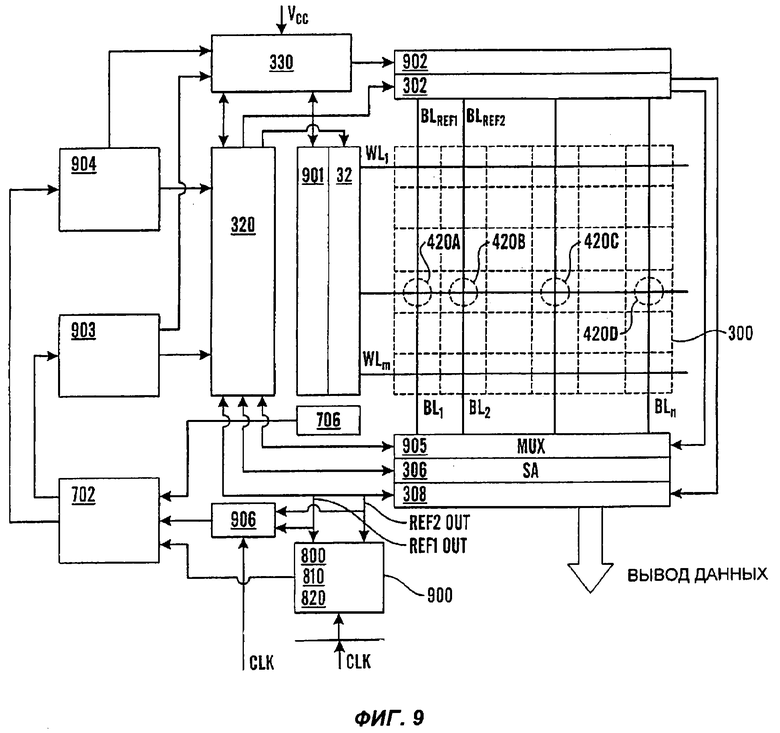

На фиг.9 представлено устройство с пассивной матричной адресацией, в котором может быть реализован способ по изобретению.

Осуществление изобретения

Прежде чем настоящее изобретение будет пояснено со ссылками на предпочтительные варианты его осуществления, приводится краткое рассмотрение его основных принципов со ссылкой на структуру ферроэлектрических запоминающих устройств с матричной адресацией и на основы адресации в подобных устройствах.

Фиг.3 иллюстрирует в форме упрощенной блок-схемы структуру и функциональные элементы ферроэлектрического запоминающего устройства с матричной адресацией, которое может быть адаптировано для целей настоящего изобретения, т.е. которое может быть реализовано с использованием способа согласно изобретению. Блок 310 памяти содержит запоминающую матрицу 300, декодеры 32 и 302 строк и столбцов соответственно, усилители 306 считывания, защелки 308 данных и избыточные управляющие линии и линии данных 304, 34. Декодеры 32, 302 строк и столбцов декодируют адреса ячеек памяти, тогда как считывание осуществляется посредством усилителей 306 считывания. Защелки 308 данных удерживают считываемые данные до тех пор, пока их часть или все данные не будут перенесены в управляющий (логический) блок 320. Данные, считанные из блока 310 памяти, будут характеризоваться некоторой частотой появления ошибок по битам, которая может быть уменьшена путем замены дефектных управляющих линий и линий данных в запоминающей матрице 300 на избыточные управляющие линии и линии данных 304, 34. Для того чтобы осуществлять обнаружение ошибок, блок 310 памяти может иметь поля данных, содержащих код с исправлением ошибок.

Управляющий блок 320 обеспечивает цифровой интерфейс для блока 310 памяти и осуществляет управление операциями записи и считывания в запоминающей матрице 300. В управляющем блоке 320 имеются также средства инициализации памяти и логические средства для замещения дефектных управляющих линий и линий данных избыточными управляющими линиями и линиями данных. Блок 330 управления драйверами запоминающего устройства связывает управляющий блок 320 с внешними шинами. Может быть предусмотрен также генератор 340 подкачки заряда для генерирования некоторых из напряжений, которые необходимы для выполнения операций записи и считывания в ячейках памяти. Может быть предусмотрен также отдельный синхронизирующий вход, связанный с блоком 330 управления драйверами через осциллятор (не изображен). Этот вход будет использоваться генератором 340 подкачки заряда для того, чтобы обеспечить подкачку заряда независимо от скорости передачи данных в приложении, использующем блок 310 памяти. При этом, однако, выполнение общих функций подкачки заряда будет задаваться драйверными контурами, как это будет пояснено со ссылкой на фиг.9.

Поскольку способ согласно изобретению приложим к протоколам подачи импульсов напряжения, используемым для пассивной адресации ферроэлектрических или электретных запоминающих устройств с матричной адресацией, в которых запоминающим материалом является ферроэлектрический или электретный полимер, далее подобные протоколы будут описаны более подробно.

Протоколы подачи импульсов напряжения, используемые при пассивной адресации к ферроэлектрическим или электретным запоминающим матрицам, запоминающий материал которых представляет собой ферроэлектрический или электретный полимер, представляют собой последовательности импульсов. Амплитуды этих импульсов задаются относительно опорного напряжения, которое может быть равным нулю. Указанные амплитуды импульсов находятся в интервале от опорного напряжения до соответствующего напряжения переключения. При этом выбор данного напряжения может зависеть от используемого запоминающего материала; однако в любом случае оно должно превышать коэрцитивное напряжение. Реальное количество уровней напряжения, предусматриваемых протоколом подачи импульсов напряжения, может равняться трем и даже превышать это значение. Дробные значения напряжения, т.е. значения, лежащие между напряжением переключения и нулевым напряжением, выбираются в соответствии с так называемым правилом (схемой) выбора напряжения.

Предпочтительно используется правило выбора половины или, даже более предпочтительно, одной трети напряжения. Выполнение данного правила гарантирует, что неадресуемые ячейки памяти и неактивные управляющие линии и линии данных не подвергаются действию напряжений или электрических полей, превышающих выбранную долю напряжения Vs переключения. Гарантируется также, что активация управляющих линий и линий данных предпочтительно предусматривает только изменение потенциала, соответствующее одному из выбранных дробных значений напряжения. Заявителем было показано, что в действительности минимальное среднее напряжение на любой невыбранной управляющей линии и линии данных в запоминающей матрице не может быть меньше, чем Vs/3. Следовательно, использование правил выбора напряжения, соответствующих дробным значениям напряжения, меньшим чем Vs/3, т.е. правил выбора одной четверти напряжения и т.д., не дает никакого выигрыша.

Представляется желательным пояснить далее в общем виде применение протоколов подачи импульсов напряжения и функционирование предпочтительного варианта изобретения со ссылкой на матрицу, представленную на фиг.4а и 4b. В соответствии с принятой терминологией горизонтальные электроды (соответствующие строкам матрицы) будут далее именоваться управляющими линиями (word lines, WL) и обозначаться как 400. Вертикальные электроды (соответствующие столбцам матрицы) будут далее именоваться линиями данных (bit lines, BL) и обозначаться, как 410. Названные электроды находятся в пределах запоминающей матрицы 300. Представляется желательным осуществлять подачу напряжения, которое является достаточно большим, чтобы обеспечить переключение направления поляризации в выбранной ячейке 420 памяти (т.е. в ячейке 430). Такое переключение может быть произведено либо с целью задать конкретное требуемое направление поляризации в ячейке (что соответствует операции записи), либо для отслеживания направления поляризации (что соответствует операции считывания). Ферроэлектрический материал, расположенный между электродами, как уже упоминалось, функционирует, как ферроэлектрический конденсатор 422 (см. фиг.4b). Следовательно, выбор ячейки 420 памяти осуществляется созданием потенциалов на ассоциированных с ней управляющей линии 402 и линии 412 данных, т.е. на активной управляющей линии и активной линии данных, таким образом, чтобы выполнялось условие:

В то же время потенциал на многочисленных управляющих линиях 400 и линиях 410 данных, которые скрещиваются на неадресуемых ячейках 420 памяти, должен контролироваться таким образом, чтобы мешающие напряжения на этих ячейках 420 находились ниже порогового уровня для частичного переключения. Каждая из этих неактивных управляющих линий 400 и линий 410 данных скрещивается соответственно с активной линией 412 данных (ACTIVE BL=ABL) и с активной управляющей линией 402 (ACTIVE WL=AWL) на одной из неадресуемых ячеек 420. Можно выделить четыре различных класса ячеек памяти в зависимости от напряжений, поданных на эти ячейки:

(1) Vi=ФactiveBL-ФactiveWL (активная управляющая линия скрещивается с активной линией данных);

(2) Vii=ФinactiveBL-ФactiveWL (активная управляющая линия скрещивается с неактивной линией данных);

(3) Viii=ФactiveBL-ФinactiveWL (неактивная управляющая линия скрещивается с активной линией данных);

(4) Viv=ФinactiveBL-ФinactiveWL (неактивная управляющая линия скрещивается с неактивной линией данных).

Класс (1) соответствует выбранной (адресуемой) ячейке 430, а классы (2)-(4) - невыбранным (неадресуемым) ячейкам 420 (см. фиг.4а; 4b).

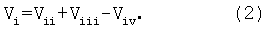

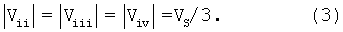

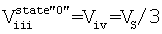

В реальных устройствах, в которых желательно минимизировать затраты и сложность конструкции, особый интерес представляет случай, когда все неактивные управляющие линии 400 находятся под общим потенциалом ФinactiveWL и соответственно все неактивные линии 410 находятся под общим потенциалом ФinactiveBL. Суммирование напряжений по замкнутому контуру в пределах сетки матрицы дает следующее условие:

Если Vi=Vs, то минимальное значение напряжения, которое может быть приложено к неактивным ячейкам 420 памяти, составляет

Для того чтобы реализовать данные соотношения, необходимо использовать 4 отдельные значения потенциала, например, Ф0, Ф0+Vs/3, Ф0+2Vs/3, Ф0+Vs, где Ф0 - опорный потенциал. Потенциал должен быть создан на электродах матрицы, причем любое изменение потенциала на одном из электродов должно быть скоординировано с настройкой других потенциалов для того, чтобы ни к одной ячейке 420 памяти не было приложено напряжение, превышающее Vs/3. На практике необходимо принимать во внимание и несколько других факторов, связанных, например, с минимизацией переходных токов при переключении (переходных токов заряда или разряда) и с уменьшением сложности драйверных контуров.

Существуют также и другие протоколы, например, трехуровневый протокол, в котором напряжение, прикладываемое к неадресуемым ячейкам 420, составляет Vs/2 при условии, что в реальной ситуации значение Vs/2 будет меньше, чем Vc. Однако тип используемого протокола не вносит никаких ограничений в настоящее изобретение. Далее протокол переключений будет рассмотрен более подробно.

Фиг.5 иллюстрирует четырехуровневый протокол подачи импульсов напряжения, охватывающий цикл считывания и цикл записи (или обновления). Из приводимого примера видно, что ни одна из неадресуемых ячеек не подвергается воздействию напряжения, превышающего треть от номинального напряжения переключения. Временные метки с номерами от 1 до 10 указывают на различные виды активности в рамках рассматриваемого протокола по фиг.5. Предполагается, что значение Ф0 составляет 0 В. Далее будут рассмотрены различные виды активности.

Момент t0 соответствует состоянию покоя, когда все управляющие линии и все линии данных находятся под напряжением 2Vs/3.

В момент t1 напряжение на неактивных линиях 410 данных (INACTIVE BL) изменяют от значения покоя до значения, составляющего Vs/3. В результате к ячейкам будет приложено напряжение Vii=Viv=-Vs/3.

В момент t2 напряжение на активных линиях 410 данных (ACTIVE BL) изменяют до значения, составляющего Vs. В результате Vi=Viii=Vs/3. Теперь все точки скрещивания находятся под напряжением, абсолютное значение которого составляет одну треть от номинального напряжения переключения. Временная задержка для момента t2 относительно момента t1 выбирается произвольно, причем она может принимать также нулевое или отрицательные значения.

Момент t3 соответствует началу задержки в цикле считывания, которая продолжается до момента t4. В данный период потенциал на активной управляющей линии 402 (ACTIVE WL) падает до 0 В. При этом напряжение Vi становится равным Vs, что делает возможным произвести считывание адресуемых ячеек. Значение Viii остается равным Vs/3, тогда как значения Vii и Viv остаются равными -Vs/3.

В момент t4 задержка в цикле считывания завершается и напряжение на активной управляющей линии возвращается к значению 2Vs/3, т.е. ситуация становится аналогичной ситуации после момента t2.

В момент t5 все линии данных возвращаются к состоянию покоя. Данный шаг является обратным по отношению к рассматриваемым совместно двум шагам, выполненным в моменты t2 и t3. Цикл считывания завершен, и все управляющие линии и линии данных возвратились к состоянию покоя, аналогичному существовавшему в момент t0.

В момент t6 происходит снижение потенциала на неактивных управляющих линиях 400 (INACTIVE WL) относительно значения Vs/3, соответствующего состоянию покоя, что соответствует первому шагу в составе цикла записи или обновления. В результате имеет место соотношение: Viii=Viv=Vs/3.

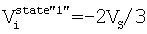

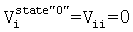

В момент t7 активные линии данных, через которые должна быть осуществлена запись логического состояния "1", приобретают потенциал, равный 0 В, в то время как активные линии, которым должно соответствовать логическое состояние "0", остаются под потенциалом покоя, равным 2Vs/3. Если рассматривать только цикл записи или обновления, активные линии данных, которым должно соответствовать логическое состояние "0", ничем не отличаются от неактивных линий. Однако разница состоит в том, что во время цикла считывания эти линии ведут себя как активные линии данных. Данная проблема (которая имеет скорее лингвистический характер) имеет место применительно к запоминающим системам с деструктивным считыванием. В результате описанных изменений возможны следующие напряжения на ячейках памяти:  ,

,  и

и  , тогда как

, тогда как  (можно видеть, что теперь

(можно видеть, что теперь  явно превышает Vs/3, так что может начаться переключение направления поляризации; однако, это не создает никаких проблем, поскольку именно в эти ячейки должна быть произведена запись на следующем шаге).

явно превышает Vs/3, так что может начаться переключение направления поляризации; однако, это не создает никаких проблем, поскольку именно в эти ячейки должна быть произведена запись на следующем шаге).

Момент t8 соответствует началу задержки в цикле записи или обновления, которая продолжается до момента t9. В данный период потенциал на активной управляющей линии повышается до Vs. Значение  теперь соответствует -Vs, что позволяет произвести запись в выбранные ячейки или осуществить их обновление. Значения

теперь соответствует -Vs, что позволяет произвести запись в выбранные ячейки или осуществить их обновление. Значения  и Vii уменьшаются до -Vs/3, т.е. становятся равными значению

и Vii уменьшаются до -Vs/3, т.е. становятся равными значению  . Значения

. Значения  и Viv остаются равными Vs/3.

и Viv остаются равными Vs/3.

В момент t9 задержка в цикле записи или обновления завершается и все линии данных возвращаются к значению 2Vs/3. В результате Vi=Vii=-VS/3 и Viii=Viv=VS/3.

В момент t10 потенциалы всех управляющих линий возвращаются к состоянию покоя. Данный шаг является обратным по отношению к рассматриваемым совместно двум шагам, выполненным в моменты t6 и t8. Цикл записи или обновления завершен, и все управляющие линии и линии данных возвратились к состоянию покоя, аналогичному существовавшему в момент t0 или t5.

Протокол подачи импульсов напряжения (протокол переключении), описанный со ссылкой на фиг.5, может быть инвертирован таким образом, что в состоянии покоя все управляющие линии и линии данных находятся под напряжением, соответствующим одной трети номинального напряжения переключения, т.е. Vs/3. Тогда все активные управляющие линии должны находиться под напряжением Vs во время цикла считывания и под напряжением 0 В во время цикла записи или обновления. Аналогично, следует соответственно модифицировать напряжения на неактивных управляющих линиях и линиях данных. За исключением конкретных используемых уровней напряжения основные особенности будут аналогичными для всех протоколов переключения, независимо от количества уровней. Кроме того, хотя при описании предпочтительных вариантов осуществления изобретения были рассмотрены четыре уровня напряжения, должно быть очевидно, что системы, использующие протоколы с меньшим или с большим количеством уровней, также могут выиграть от использования изобретения.

Для того чтобы разъяснить главные аспекты настоящего изобретения, далее, в качестве примеров, будут рассмотрены некоторые варианты его осуществления, относящиеся к протоколам подачи импульсов напряжения и касающиеся конкретной проблемы изменения характеристик переключения ферроэлектрических запоминающих материалов в случае изменения температуры.

Конкретными проявлениями таких изменений являются уменьшение напряженности коэрцитивного поля или возрастание скорости переключения по мере возрастания температуры, как это было описано в ходе анализа уровня техники. В том случае, когда ферроэлектрический материал представляет собой тонкую полимерную пленку, может возникнуть также проблема, состоящая в ослаблении поляризационных свойств по мере приближения к точке Кюри. Кроме того, предыдущая история переключении ферроэлектрического запоминающего материала может также оказывать влияние на его текущие ферроэлектрические свойства, в частности на его свойства, проявляющиеся через параметр гистерезисной кривой. Отрицательное влияние на свойства переключения ферроэлектрического материала, т.е. на историю его переключении, могут, например, оказывать такие хорошо известные явления, как усталость и "импринтинг". Этими явлениями нельзя пренебречь при рассмотрении свойств переключения при высокой температуре.

Общее решение проблемы таких температурных эффектов, как увеличение скорости переключения или уменьшение коэрцитивного напряжения в ферроэлектрическом запоминающем устройстве, предлагаемое настоящим изобретением, заключается во введении температурной компенсации в значения потенциала, соответствующие прикладываемым разностям напряжений в рамках протоколов подачи импульсов напряжения в процессе адресации к памяти. Такое решение предполагает необходимость определения температуры либо путем прямого измерения, либо с применением какого-либо косвенного метода. Как это будет описано далее, прямое измерение рабочей температуры ферроэлектрического запоминающего устройства может быть легко осуществлено путем установки датчика температуры в запоминающий контур или на плату, несущую данный контур. В этом случае датчик температуры будет воспринимать рабочую температуру ферроэлектрического запоминающего контура или температуру среды, окружающей данный контур. В общем случае температура окружающей среды необязательно совпадает с истинной рабочей температурой самого запоминающего материала в период выполнения цикла адресации. В частности, хорошо известно, что переключение ферроэлектрических ячеек памяти на основе полимерного материала может привести к появлению термомеханических напряжений в запоминающем материале.

Особенно вероятно возникновение подобных проблем в случае известной из уровня техники трехмерной архитектуры памяти, в которой рассеяние генерируемого тепла и демпфирование механических колебаний может привести к тому, что в любой текущий момент истинная рабочая температура запоминающего материала, как следствие медленного рассеяния тепла, будет выше, чем температура среды, окружающей запоминающий контур. Однако измерение температуры непосредственно в запоминающем слое может оказаться непрактичным. Вместе с тем, поскольку существует зависимость между температурой и скоростью переключения ячейки памяти, можно измерить эту скорость переключения при выполнении операции адресации, а затем использовать заранее установленную корреляцию между скоростью переключения и температурой запоминающего материала для определения этой температуры. При рассмотрении приводимых далее предпочтительных вариантов измерения, каждый из которых предусматривает температурную компенсацию применительно к одному или более значений потенциала в рамках протоколов подачи импульсов напряжения, не будет приводиться ссылок на конкретный предпочтительный вариант определения температуры. Это означает, что температура может измеряться прямым или косвенным методом, как это было пояснено выше.

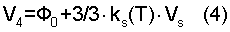

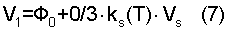

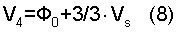

В первом предпочтительном варианте изобретения проблема того, что рабочая температура может быть достаточно близкой к точке Кюри ферроэлектрического материала, решается путем введения температурного коэффициента ks(T) для изменения номинального переключающего напряжения Vs. На фиг.6а-6b четыре заданных значения V1, V2, V3, V4 потенциала (показанные на фиг.5) изображены штрихпунктирными линиями и обозначены, как 610, 620, 630 и 640. Следует отметить, что в контексте изобретения Vi, Vii, Viii и Viv - это наблюдаемые значения напряжений, приложенных к ячейкам 420 памяти, тогда как v1, V2, V3, V4 соответствуют истинным потенциалам. Это означает, что V1 равняется Ф0, V4 равняется Ф0+Vs и т.д. Как видно из приводимых ниже формул, температурный коэффициент может использоваться применительно ко всем значениям потенциала:

Простейший вариант температурного коэффициента соответствует линейной зависимости от температуры. Пример подобного температурного коэффициента приведен на фиг.6а. В данном случае можно записать: ks(T)=а+b·Т. Потенциалы 621, 631, 641, полученные из потенциалов V2, V3, V4 соответственно и скомпенсированные с учетом температуры, отстоят друг от друга на одинаковое расстояние. В зависимости от свойств рассматриваемого ферроэлектрического материала температурный коэффициент может соответствовать и нелинейной температурной зависимости, например, описываемой выражением ks(T)=а+b·Т0,9 или ks(T)=а+b·ес·T. Альтернативная возможность состоит в использовании разности между рабочей температурой и точкой Кюри. Подобные, более сложные альтернативы могут оказаться необходимыми, поскольку разность между рабочей температурой и точкой Кюри для ферроэлектрических полимеров намного меньше, чем для других запоминающих материалов. Как следствие, рекомендуется использовать не только отрицательную температурную зависимость стабилитрона (как это описано в патенте США №5487029). Математические операции, необходимые для определения температурного коэффициента в любой момент времени, могут выполняться внутри ферроэлектрического запоминающего устройства, например, в управляющем (логическом) блоке 320. Альтернативно они могут выполняться вне данного устройства и быть реализованы просто в виде таблиц соответствия. Если рассматриваемое запоминающее устройство является небольшим, таблицы соответствия могут быть сокращены.

Во втором предпочтительном варианте проблема того, что рабочая температура может быть достаточно близкой к точке Кюри ферроэлектрического материала, решается путем введения напряжения смещения в одно или более значений потенциала. Пример использования подобных напряжений смещения приведен в международной заявке WO 02/05287, в которой низкая нагрузка от паразитных токов на линии данных во время операции считывания скомпенсирована дополнительной подачей напряжения смещения на неактивные управляющие линии 400 и неактивные линии 410 данных. Получаемый результат состоит в том, что Vii переходит в Vii+δ, a Viii - в Viii-δ. Однако необходимо с осторожностью выбирать значение δ, поскольку наблюдаемое значение напряжения на ячейках 420, в которых неактивные линии скрещиваются с активными, в любых сочетаниях, в некоторые моменты возрастает. Это соответственно увеличивает риск нежелательного обращения направления поляризации.

В отличие от описанного решения, настоящее изобретение предусматривает добавление напряжения δV смещения к одному или к двум значениям потенциала. В приводимых далее формулах напряжение δV смещения добавляется к потенциалу V2 для того, чтобы уменьшить наблюдаемое напряжение на ячейках 420 памяти, в которых неактивные управляющие линии 400 скрещиваются с неактивными линиями 410 данных. Такие скрещивания составляют большинство точек в запоминающей матрице 300 и, следовательно, данное решение оказывает наибольшую помощь в уменьшении опасности нежелательного обращения направления поляризации. Тем не менее, и в этом случае необходима осторожность при выборе значения δ.

На фиг.6b показано, что добавление напряжения δV смещения приводит к повышению скорректированного потенциала 622 относительно исходного потенциала 620, обозначенного штрихпунктирной линией. В альтернативном варианте может иметь место одновременное снижение потенциала 630 на величину δV, т.е. до скорректированного потенциала 632. Аналогично температурному коэффициенту в первом рассмотренном варианте напряжение смещения может изменяться в зависимости от температуры. Подобное изменение показано на фиг.6b для скорректированного потенциала 632. В отличие от первого предпочтительного варианта, скорректированные потенциалы 622, 632 больше не находятся на равном расстоянии друг от друга.

В третьем предпочтительном варианте изобретения используется сочетание температурного коэффициента ks(T) и напряжения δV смещения. Фиг.6с иллюстрирует влияние температурного коэффициента на скорректированные потенциалы 621, 631, 641 (соответствующие представленным на фиг.6а). При этом суммарный эффект, включая влияние напряжения δV смещения, представлен в виде дополнительной коррекции потенциалов до значений 623, 633.

При реализации описанных трех предпочтительных вариантов могут быть использованы контуры, представленные на фиг.7а и 7b. В них имеется датчик температуры для отслеживания рабочей температуры или окружающей температуры, которая может быть использована для определения рабочей температуры этих контуров. На фиг.7а представлен аналоговый контур 700 температурной компенсации, который может быть введен в состав генератора 340 подкачки заряда. Калибровочная память 702 обеспечивает информацию о температурном коэффициенте и/или о напряжениях смещения, которые подаются в цифроаналоговый преобразователь 704. Преобразованная информация вместе с сигналом от датчика 706 температуры поступает на комплект компараторов 708, 710, 712. В результате генераторы 714, 716, 718 подкачки заряда обеспечивают управление потенциалами V2, V3 и V4. Обычно V1 соответствует потенциалу земли, т.е. Ф0=0 В.

На фиг.7b представлен цифровой контур 720 температурной компенсации, который также может быть введен, например, в состав генератора 340 подкачки заряда. Входной сигнал от датчика 706 температуры поступает в калибровочную память 702 через аналого-цифровой преобразователь 722. Данные, хранящиеся под соответствующим адресом в калибровочной памяти 702, подаются в цифроаналоговый преобразователь 704, а от него на комплект компараторов 708, 710, 712. И в этом случае генераторы 714, 716, 718 подкачки заряда обеспечивают управление потенциалами V2, V3 и V4, в то время как V1 соответствует потенциалу земли (Ф0=0 В).

Контуры по фиг.7а и 7b могут быть модифицированы для того, чтобы обеспечить возможность применения других протоколов переключения, использующих большее или меньшее количество уровней, а также протоколов, в которых значение Ф0 не равно нулю. Должно быть понятно, что количество компараторов 708, 710, 712 или генераторов 714, 716, 718 подкачки заряда может изменяться в зависимости от количества используемых уровней или от того, равняется ли нулю Ф0 или нет.

Как было указано выше, три рассмотренных предпочтительных варианта изобретения могут использоваться также в сочетании с непрямым определением рабочей температуры. В этом случае рабочая температура будет соответствовать действительной рабочей температуре самой запоминающей среды во время осуществления операций адресации или переключения. Такое непрямое определение будет осуществляться посредством процедуры, основанной на измерении скорости переключения ячеек памяти, как это будет пояснено со ссылкой на фиг.8.

На фиг.8 показана система для непрямого определения рабочей температуры ферроэлектрического запоминающего устройства. В качестве опорных ячеек памяти используются две ячейки 420А, 420В. Данные опорные ячейки памяти могут находиться в составе запоминающей матрицы 300 или в составе отдельного опорного массива. В одной из ячеек установлено логическое состояние "0", а во второй - логическое состояние "1". В процессе работы производится считывание обеих опорных ячеек памяти. Детектор 800 уровня непрерывно осуществляет вычитание плотности заряда в ячейке, соответствующей "1", из плотности заряда в ячейке, соответствующей "0". Схема подобного типа была описана в международной заявке WO 02/05288. Разность между плотностями зарядов увеличивается в процессе считывания. Однако на эту разность между плотностями зарядов влияют также окружающие условия, например, температура, влажность и т.д. Компаратор 810 сравнивает разность плотностей зарядов с заранее определенным уровнем и выдает столовый сигнал счетчику 820. Счетчик 820 начинает счет одновременно с началом операции считывания. Значение истекшего интервала времени посылается в калибровочную память 702 с целью задать рабочую температуру, которая соответствует времени, необходимому для того, чтобы разность между плотностями зарядов достигла заранее определенного уровня.

Далее будет описан четвертый вариант осуществления изобретения, в котором корректировка импульсов напряжения, используемых в рамках протокола подачи импульсов напряжения, производится изменением не амплитуды импульсов, а их длительности. Другими словами, протокол подачи импульсов напряжения настраивается таким образом, что, по меньшей мере, длительность импульса переключения уменьшается пропорционально увеличению скорости переключения. Данное увеличение скорости, разумеется, может быть обусловлено влиянием повышения температуры. Однако в общем случае скорость переключения можно рассматривать в качестве параметра отклика ячеек памяти, который может изменяться под влиянием не только температуры, но и выполненной операции адресации, изменений свойств ячейки памяти, а также различных факторов окружающей среды.

При уменьшении длительности импульсов по мере возрастания скорости переключения считываемый сигнал не будет существенно уменьшаться при высоких температурах, в то время как влияние мешающих напряжений на неадресуемые ячейки памяти уменьшится.

Для того чтобы обеспечить управление длительностью импульсов, запоминающее устройство должно содержать контроллер длительности, который осуществляет корректировку длительности импульсов в составе протоколов подачи импульсов напряжения, предпочтительно в качестве отклика на информацию о действительной скорости переключения. Разумеется, поскольку конкретный протокол включает в себя последовательности импульсов с различными параметрами импульсов, такими как длительность, полярности, интервалы между импульсами и др., характер корректировки длительности импульсов может зависеть от типа импульсов, используемых в рамках конкретного протокола. На практике корректировку длительности импульсов можно рассматривать также как корректировку временной последовательности в рамках протокола подачи импульсов напряжения или, по меньшей мере, части этой последовательности. Другими словами, корректировка длительности импульсов может комбинироваться с корректировкой интервалов между различными импульсами в составе протокола. Как и в предыдущих случаях, такие корректировки можно производить на основе измерений температуры, т.е. с использованием соответствующего датчика для прямого измерения температуры (как это было описано выше). В этом случае значения настроек длительности находятся с помощью таблицы соответствия.

Еще более предпочтительным может являться определение скорости переключения путем адресации и мониторинга одной или более опорных ячеек памяти (тестируемых ячеек памяти), объединенных в матрицу подобно тому, как это сделано с ячейками памяти для обычного хранения данных. В этом случае скорость переключения будет использоваться в качестве параметра, характеризующего отклик ячейки памяти, который определяется просто выполнением операции адресации для осуществления операции считывания из опорных ячеек памяти. Преимущество использования скорости переключения состоит в том, что ее изменения будут отображать влияние и других факторов, таких как влажность, давление, механические напряжения и др.

Далее со ссылкой на фиг.9 будет обсуждено ферроэлектрическое запоминающее устройство, выполненное с возможностью осуществления способа по изобретению. Некоторые составляющие части этого устройства уже были описаны со ссылкой на фиг 3; поэтому они будут рассмотрены очень кратко. Как и в устройстве по фиг.3, запоминающая матрица 300 содержит ячейки 420 памяти, расположенные в матрице в точках скрещивания управляющих линий WL и линий BL данных. Представленная матрица имеет размерность m×n, т.е. представляет собой матрицу, имеющую m управляющих линий WL и n линий BL данных. Линии BL данных присоединены к набору усилителей 306 считывания, в состав которого входит множество усилителей считывания (sense amplifiers - SA), каждый из которых соединен с одной из линий BL данных. Тем самым обеспечивается возможность считывания полной строки. Однако для того, чтобы сократить число усилителей считывания, управляющие линии могут быть разбиты на сегменты, так что каждый сегмент содержит n/k управляющих линий, где к - целое число. В этом случае набор усилителей 306 считывания будет содержать n/k усилителей. Это означает, что для подсоединения каждой линии данных, входящей в адресуемый сегмент, к одному из усилителей SA считывания с целью осуществления параллельного считывания или записи для всех ячеек памяти в сегменте управляющих линий необходимо использовать мультиплексор 905 (обозначенный также, как MUX). Другими словами, мультиплексор 905 не используется в случае, если запоминающее устройство допускает считывание полной строки, т.е. параллельное считывание всех ячеек, соответствующих одной управляющей линии.

Вместо генератора 340 подкачки, показанного на фиг.3, могут быть использованы драйверные контуры, например, х-драйвер 901 и у-драйвер 902, которые обычно служат для подачи импульсов напряжения в соответствии с реализуемым протоколом соответственно на управляющие линии WL и линии BL данных. Выбор ячеек 420 памяти, например, при операции считывания или записи, происходит непосредственно при выполнении операции адресации через х-декодер 32 и у-декодер 302. Управляющие линии WL и линии BL данных могут быть выбраны в качестве активных путем соответствующего повышения или понижения их потенциала относительно постоянного уровня напряжения (состояния покоя), определяемого как доля переключающего напряжения Vs, заданного относительно нулевого потенциала (или плавающего заземления). При этом неактивные управляющие линии и линии данных остаются под потенциалом, соответствующим состоянию покоя, или приобретают другой потенциал, составляющий долю переключающего напряжения Vs.

Имеются также опорные ячейки 420А и 420В памяти, находящиеся на линиях BLREF1 и BLREF2 данных. Эти ячейки могут быть переведены соответственно в первое и второе состояния поляризации, т.е. представлять собой логический "0" и логическую "1". Опорные ячейки 420А и 420В памяти, присоединенные соответственно к линиям BLREF1 и BLREF2 данных, образуют часть запоминающей матрицы точно таким же образом, что и другие ячейки 420 памяти. Поэтому они будут подвергаться таким же мешающим воздействиям или динамическим изменениям (включая воздействие операций адресации, факторов окружающей среды и др.), которые могут иметь место в других ячейках памяти. Следует также учесть, что пара опорных ячеек памяти может быть предусмотрена аналогичным образом на каждой управляющей линии WL. Адресация к опорным ячейкам 420А, 420В памяти производится при выполнении операции считывания, причем результат считывания детектируется посредством набора усилителей 306 считывания. Соответствующие выходные сигналы REF1 и REF2 поступают в блок 900 определения скорости переключения. С этой целью блок 900 имеет вход CLK синхронизации. Скорость считывания записывается в калибровочной памяти 702, выход которой присоединен к контроллеру 903 длительности импульсов. Второй выход калибровочной памяти 702 присоединен к контроллеру 904 амплитуды импульсов. Разумеется, оба контроллера 903, 904 подключены также к управляющему блоку 320. Запоминающее устройство может дополнительно содержать датчик 706 температуры для слежения за рабочей температурой. Выход этого датчика также подключен к калибровочной памяти 702.

Как показано на фиг.9, в качестве желательного дополнительного компонента может присутствовать анализатор 906 сигналов, имеющий вход CLK синхронизации и подключенный к выходу опорных ячеек 420А, 420В памяти. Этот анализатор может быть использован для проведения более глубокого анализа, причем не только характеристик скорости переключения, но, например, также и характеристик поляризационного отклика ячеек памяти. Выход анализатора 906 сигналов также подключен к калибровочной памяти 702.

В результате в калибровочной памяти 702 будут храниться измеренные опорные значения, а, возможно, также и вектор, отображающий историю ранее выполненных по отношению к опорным ячейкам памяти операций адресации и сопоставления. Кроме того, из калибровочной памяти будут извлекаться корректирующие значения либо для длительности импульсов, либо для интервалов между импульсами, либо для амплитуд импульсов. В зависимости от используемого варианта эти корректирующие значения подаются в контроллер 903 длительности импульсов или в контроллер 904 амплитуды импульсов. Длительность импульса будет корректироваться на некоторую величину ±δt, тогда как амплитуда импульса будет аналогичным образом корректироваться на некоторую величину ±δV. Должно быть понятно, что генератор импульсов будет формировать входные импульсы с заранее заданной амплитудой и/или длительностью, поступающие в блок 330 управления драйверами. При этом корректирующие параметры, поступающие от контроллера 903 длительности импульсов или контроллера 904 амплитуды импульсов, могут подаваться непосредственно в генератор импульсов для того, чтобы учесть эти корректирующие параметры при определении амплитуды и/или длительности импульсов. Очевидно также, что одновременная корректировка и амплитуды и длительности импульсов требует синхронизированной работы контроллеров 903, 904.

Необходимо также отметить, что показанный на фиг.9 блок 900 определения скорости переключения будет идентичен или аналогичен системе, проиллюстрированной на фиг.8, тогда как калибровочная память 702 будет общей для любого варианта управляющих воздействий. Это означает, что контроллеры 903, 904 в предпочтительном варианте будут являться компонентами генератора импульсов, который осуществляет корректировку длительности и амплитуды импульсов с учетом корректирующих значений, поступающих из калибровочной памяти 702. Длительность импульсов целесообразно задавать, используя для этой цели управление синхронизацией, как это хорошо известно специалистам. Управление амплитудой импульсов может быть осуществлено посредством генераторов подкачки, обеспечивающих возможность настраивать формируемое напряжение в зависимости от значения корректирующей величины ±δV. На практике функция подкачки заряда в рассматриваемом устройстве реализуется посредством драйверных контуров, т.е. х-драйвера 901 и у-драйвера 902, под управлением основного управляющего блока 320, в который от соответствующего источника подается питающее напряжение VCC.

Что касается других компонентов запоминающего устройства, представленного на фиг.9, они должны повторять аналогичные компоненты устройства по фиг.3. При этом принимается очевидным, что их функции в запоминающем устройстве подобного типа должны быть ясны для специалистов в данной области и не требуют дальнейшего описания. В заключение можно отметить, что корректировка протокола подачи импульсов напряжения в зависимости от изменений отклика ячеек памяти будет приводить к уменьшению мешающих напряжений (т.е. переходных напряжений, генерируемых, например, из-за наличия емкостных связей или токов утечки в матрице, образованной скрещиванием электродов), прикладываемых к неадресуемым ячейкам памяти при выполнении операции адресации. Кроме того, предлагаемые процедуры будут способствовать ослаблению эффектов усталости и импринтинга, по отношению к которым ячейка памяти является более чувствительной при более высокой скорости переключения или при снижении коэрцитивного поля, что, в частности, имеет место при повышении температуры.

Хотя различные рассмотренные варианты осуществления относились к использованию ферроэлектриков, должно быть понятно, что настоящее изобретение (с соответствующими модификациями) может быть применено и к любому электретному материалу, который обладает свойствами биполярной поляризации и в котором поляризационный отклик изменяется систематическим образом во время функционирования запоминающего устройства, независимо от того, вызывается ли это изменение факторами окружающей среды или реальной историей адресации.

В соответствии со способом управления ферроэлектрическим или электретным запоминающим устройством при считывании данных из ячеек памяти данного устройства на первый и второй наборы электродов подают первое множество разностей напряжения. При записи или обновлении данных в ячейках памяти на первый и второй наборы электродов подают второе множество разностей напряжения. В обоих этих случаях первое и второе множества разностей напряжения соответствуют массиву значений потенциала, задаваемых протоколом подачи импульсов напряжения, который включает временные последовательности импульсов напряжения. При этом производят определение, по меньшей мере, одного параметра, характеризующего изменение отклика ячеек памяти, и используют этот параметр для определения, по меньшей мере, одного корректирующего фактора для импульсов напряжения. С использованием, по меньшей мере, одного корректирующего фактора осуществляют коррекцию, по меньшей мере, одного параметра подаваемых импульсов. Изобретение относится также к ферроэлектрическому или электретному запоминающему устройству для осуществления данного способа. 2 н. и 26 з.п. ф-лы, 13 ил.

ячейки (420) памяти на основе тонкопленочного поляризуемого ферроэлектрического или электретного материала, обладающего гистерезисом, например, на основе тонкой ферроэлектрической или электретной полимерной пленки, и первый и второй наборы электродов (WL, BL), взаимно параллельных в пределах одного набора, причем электроды первого (WL) и второго (BL) наборов расположены, по существу, ортогонально по отношению к электродам другого набора и находятся в прямом или непрямом контакте с тонкопленочным материалом, образующим ячейки (420) памяти, а поляризационное состояние индивидуальных ячеек памяти можно считывать, обновлять или записывать путем подачи соответствующих напряжений на индивидуальные электроды (402, 412) первого и второго наборов электродов, причем способ реализует протокол подачи импульсов напряжения заданной амплитуды и длительности, включающий циклы считывания и записи/обновления, состоящие из временных последовательностей импульсов напряжения заданной амплитуды и длительности, при этом цикл считывания предусматривает приложение набора разности напряжений к электродам первого и второго наборов с осуществлением считывания данных из ячеек (420) памяти, цикл записи/обновления в составе протокола подачи импульсов напряжения предусматривает приложение к электродам (WL, BL) первого и второго наборов иного набора разности напряжений с осуществлением записи/обновления данных, хранящихся в ячейках (420) памяти, указанные наборы разностей напряжений соответствуют заданному массиву значений потенциалов, причем этот заданный массив содержит, по меньшей мере, три отдельных значения потенциала, отличающийся тем, что включает операции (а) определения, по меньшей мере, одного параметра, характеризующего изменение отклика ячеек памяти на прикладываемые к ним разности напряжений; (б) определения, по меньшей мере, одного корректирующего фактора для импульсов напряжения, входящих в состав протокола подачи импульсов напряжения, на основе указанного, по меньшей мере, одного параметра, характеризующего изменение отклика ячеек памяти на прикладываемые к ним разности напряжений; (в) выбора для корректировки протокола подачи импульсов напряжения, по меньшей мере, одного из следующих параметров указанного протокола: амплитуд импульсов, длительностей импульсов и интервалов между импульсами; и (г) корректировки одного или более значений, по меньшей мере, одного из выбранных параметров протокола подачи импульсов напряжения в соответствии с указанным, по меньшей мере, одним корректирующим фактором, с обеспечением тем самым корректировки одной или более амплитуд импульсов, одной или более длительностей импульсов и одного или более интервалов между импульсами либо по отдельности, либо в комбинации в соответствии с обнаруженным изменением отклика ячеек памяти.

| СПОСОБ ОТВЕРЖДЕНИЯ ПОЛИЭФИРНЫХ СМОЛ И КОМПОЗИЦИЙ НА ИХ ОСНОВЕ | 0 |

|

SU205287A1 |

| US 6272037 B1, 07.08.2001 | |||

| МАТРИЧНЫЙ НАКОПИТЕЛЬ ДЛЯ ПОСТОЯННОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1986 |

|

SU1378682A1 |

| JP 10083679, 31.03.1998. | |||

Авторы

Даты

2007-04-10—Публикация

2003-09-10—Подача