Изобретение относится к области измерительной техники и может быть использовано для измерения параметров волоконно-оптических линий передачи информации.

Известно устройство для измерения коэффициента битовых ошибок линий передачи, включающее два генератора псевдослучайных последовательностей, сравнивающее устройство, синхрогенератор, накопитель числа ошибок [1 (стр.62, рис.6.5)].

Генераторы псевдослучайной последовательности находятся на разных концах линии передачи. Генераторы синхронизируются от одного синхрогенератора. Сигнал, выработанный первым генератором псевдослучайной последовательности и прошедший контролируемую линию передачи, сравнивается побитно с выходным сигналом второго генератора. В случае несовпадения передаваемых бит вырабатывается сигнал ошибки, накапливаемый в счетчике. Коэффициент битовых ошибок определяется отношением количества битов, пораженных ошибками, к общему числу переданных битов.

Устройство имеет следующие недостатки:

- при проверке линий связи большой длины не всегда имеется возможность синхронизации генераторов псевдослучайных последовательностей от одного источника;

- устройство не содержит оптоэлектронных и электрооптических преобразователей для контроля волоконно-оптических линий связи.

Рассмотренные недостатки не позволяют использовать это устройство для контроля коэффициента битовых ошибок протяженных волоконно-оптических линий передачи информации.

Известны отечественные и зарубежные устройства для измерения коэффициента битовых ошибок в каналах передачи информации (в том числе волоконно-оптических):

- EDT-135 фирма Global Headquarters (USA), [2];

- "УКОЛ-15", ЗАО "Технодалс" (Санкт-Петербург, Россия) [3];

- ЕВН 30/120 предприятие "ЭЛЕКТРОНИКА" (Венгрия) [4];

- OG-3 фирма "Siemens" [5];

- ИКО-2-2(5) ЗАО "Супертехприбор" [5];

- ИД-2/8/34 фирма "Радиан" [6];

- СМ-Е1 фирма "Симос" [7].

Все перечисленные устройства построены по одной функциональной схеме и содержат генераторы псевдослучайных последовательностей на разных концах линии и синхрогенератор на передающем конце контролируемой линии. Для функционирования всех рассматриваемых устройств необходима каналообразующая аппаратура, которая формирует тестовый измерительный сигнал, состоящий одновременно из псевдослучайной последовательности и импульсов синхронизации. Причем для замешивания сигналов синхронизации в передаваемое сообщение все рассматриваемые устройства используют трехуровневые линейные коды HDB-3 или AMI (отрицательный уровень, положительный уровень, нулевое значение). Волоконно-оптические линии передачи информации могут работать только с двухуровневыми линейными кодами (оптический сигнал всегда однополярный - уровень оптической мощности нулевой или ненулевой).

Таким образом, рассматриваемые устройства не могут быть использованы при контроле волоконно-оптических линий передачи без дополнительного преобразования трехуровневого линейного кода в двухуровневый. Так как необходимы сложные кодирующие и декодирующие устройства, устройства имеют сложную архитектуру и дороги (измеритель битовых ошибок на скорость передачи 34 Мбит/с стоит около $6000). Кроме проверяемого канала передачи - волоконно-оптической линии связи - тестируются одновременно устройства каналообразования и конверторы линейных кодов, поэтому трудно выделить биты, пораженные ошибками непосредственно в волоконно-оптическом тракте.

Наиболее близким по конструктивным признакам к предлагаемому устройству является устройство измерения битовых ошибок, описанное в [8].

Устройство содержит две секции: генераторную и секцию анализатора. Генераторная секция содержит регистр сдвига, тактовый генератор, кодер, устройство сравнения, причем выход тактового генератора подключен к входу синхронизации регистра сдвига и одному из входов кодера, первый вход устройства сравнения подключен к выходу одного из разрядов регистра сдвига, второй - к выходу последнего разряда регистра сдвига, а выход - к входу данных регистра сдвига. Секция анализатора содержит второй регистр сдвига, два устройства сравнения, счетчик ошибок (битов, пораженных ошибками), декодер, причем выход синхронизации декодера подключен к входу синхронизации регистра сдвига, первый вход второго устройства сравнения подключен к выходу одного из разрядов второго регистра сдвига, второй - к выходу последнего разряда второго регистра сдвига, а выход - к входу данных второго регистра сдвига, первый вход третьего устройства сравнения подключен к выходу второго регистра сдвига, второй вход - к выходу данных декодера, а выход третьего устройства сравнения подключен к входу счетчика битов, пораженных ошибками.

Устройство работает следующим образом. Тактовый генератор генераторной секции вырабатывает периодические импульсы (импульсы синхронизации), сдвигающие информацию на входе данных в регистр. Вход данных регистра сдвига подключается к выходу логического элемента сравнения "ИСКЛЮЧАЮЩЕЕ ИЛИ". Элемент сравнения "ИСКЛЮЧАЮЩЕЕ ИЛИ" вырабатывает сигнал логической единицы, если биты информации на его входах не совпадают, и сигнал логического нуля, если биты совпадают. Входы логического элемента подключаются к выходу регистра сдвига (выходу последнего разряда) и выходу одного из разрядов этого регистра. Такая схема включения позволяет организовать генератор псевдослучайной последовательности бит. Длина псевдослучайной последовательности (число разрядов регистра) определяется рекомендациями ITU-T О.51 в зависимости от скорости цифровой передачи в канале. Кроме того, существует рекомендация по выбору конфигурации тестовой последовательности. Так, для скорости цифровой передачи в канале от 64 до 8448 кбит/с псевдослучайная битовая последовательность должна описываться полиномом D15+D-14+1=0, а для скорости 34368 кбит/с - полиномом D23+D-18+1=0. Чтобы смоделировать псевдослучайную последовательность, описываемую полиномом D15+D-14+1=0, необходимо в схеме, описанной выше, подключить к входам логического элемента сравнения "ИСКЛЮЧАЮЩЕЕ ИЛИ" выходы 15-го и 14-го разрядов сдвигающего 15-и разрядного регистра. Аналогично, для моделирования псевдослучайной последовательности, описываемой полиномом D23+D-18+1=0, необходимо подключить к входам логического элемента сравнения "ИСКЛЮЧАЮЩЕЕ ИЛИ" выходы 23-го и 18-го разрядов сдвигающего 23-х разрядного регистра.

Сгенерированная псевдослучайная последовательность направляется на информационный вход кодера. На вход синхронизации кодера поступает сигнал от тактового генератора. Устройство кодера зависит от скорости передачи информации в канале.

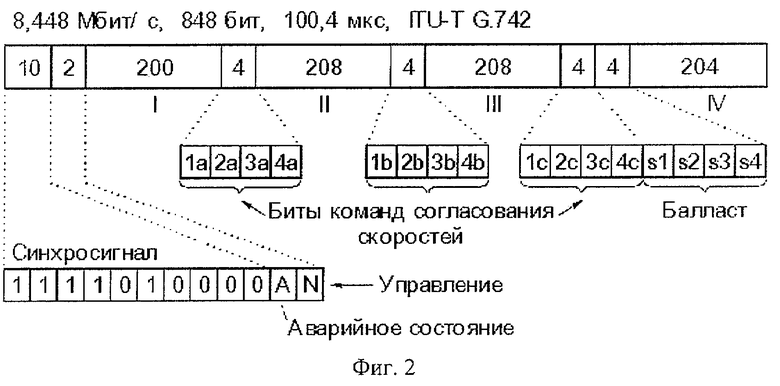

Сигналы синхронизации от тактового генератора и данные с выхода регистра сдвига поступают на входы кодирующего устройства (кодера), объединяющего эти сигналы в кодовую последовательность. В простейшем случае используется плезиохронная цифровая иерархия (ПЦИ или PDH). Для скорости передачи информации 2048 кбит/с реализуется синхронное мультиплексирование восьмиразрядных кодовых комбинаций и при этом формируется первичный цифровой сигнал, обозначаемый Е1. Структура первичного цифрового сигнала, согласно рекомендаций G.704 и G.732, представлена на фиг.1.

Он состоит из 32-канальных позиций длительностью 3,91 мкс каждая с общей длительностью, равной 125 мкс. Нулевой и шестнадцатый интервалы предназначены для служебных целей:

- нулевой канальный интервал (КИ0) для передачи сигналов: синхронизации, контроля, управления и оповещения об аварии;

- шестнадцатый канальный интервал КИ16 служит для передачи сигнальных сообщений, синхронизации по сверхциклу и индикации аварийного состояния.

Псевдослучайная тестовая последовательность заполняет канальные информационные интервалы с 1 по 15, с 17 по 29 и 31.

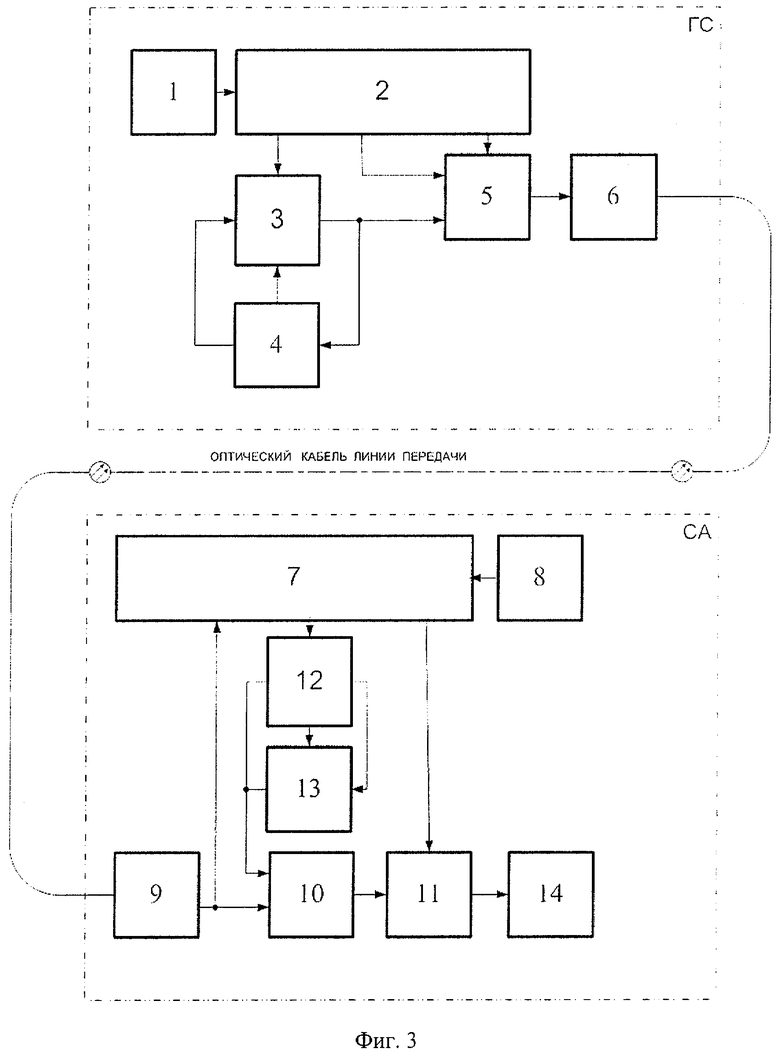

Последующие ступени иерархии (характеризующиеся большей скоростью передачи) могут быть получены путем побитового мультиплексирования нескольких сигналов первой ступени, например вторая ступень (Е2) обеспечивается объединением четырех сигналов Е1 с формированием цикла длительностью 100,4 мкс (см. фиг.2).

Для цифрового потока Е2 первые десять бит представляют собой синхросигнал. Весь цикл поделен на четыре блока I, II, III, IV командами согласования скоростей, которые применяются для оповещения приемной стороны о наличии вставок, выравнивающих скорости потоков Е1 и удаляемых на приеме.

Блоки I, II, III, IV содержат чередующиеся информационные биты четырех сигналов Е1 с тестовой псевдослучайной последовательностью.

Аналогично получается цикловая структура третьей степени мультиплексирования Е3, в которой обеспечивается скорость передачи 34,368 Мбит/с, однако при этом побитово объединяются четыре потока Е2 или шестнадцать потоков Е1 и длительность цикла уменьшается до 44,7 мкс. Четвертая степень мультиплексирования обеспечивает скорость передачи 139,264 Мбит/с (рассматриваемое в качестве прототипа устройство обеспечивает именно этот уровень иерархии) и последняя пятая степень плезиохронной цифровой иерархии обеспечивает скорость 564,992 Мбит/с.

Рассматриваемое устройство может также работать с виртуальными контейнерами систем передачи информации с синхронной цифровой иерархией (СЦИ или SDH). При этом кодер устройства заполняет всю информационную полосу контейнера тестовой последовательностью.

Декодер секции анализатора выполняет обратную функцию кодера, он из структурированного цифрового потока извлекает сигналы синхронизации и тестовую псевдослучайную последовательность. Сигналы синхронизации поступают на вход синхронизации второго генератора псевдослучайной последовательности, аналогичного находящемуся в генераторной секции и состоящему из второго регистра сдвига и второго логического элемента сравнения "ИСКЛЮЧАЮЩЕЕ ИЛИ". Выделенная декодером тестовая псевдослучайная последовательность подается на один из входов третьего логического элемента "ИСКЛЮЧАЮЩЕЕ ИЛИ", на второй вход элемента подается псевдослучайная последовательность с выхода второго генератора псевдослучайной последовательности (выхода второго регистра сдвига). При несовпадении бит последовательностей логический элемент вырабатывает сигнал логической единицы, подсчитываемый счетчиком ошибок. Коэффициент битовых ошибок определяется отношением количества бит, пораженных ошибками, к общему числу переданных бит.

Устройство имеет следующие недостатки:

- высокую стоимость и сложность изготовления;

- не позволяет выделить биты, пораженные ошибками непосредственно в канале передачи, так как эти ошибки суммируются с ошибками в кодере, декодере, каналах синхронизации;

- стандартные линейные коды цифровых потоков от Е1 и выше HDB-3 или AMI имеют трехуровневую структуру и не могут быть переданы по волоконно-оптической линии связи (для передачи необходимо преобразование трехуровневого кода в двухуровневый, которое может внести дополнительные битовые ошибки в канал передачи).

Не все цифровые линии передачи используют структурированные цифровые потоки ПЦИ (PDH) или СЦИ (SDH). Существуют локальные цифровые системы сбора данных, использующие сигналы, поступающие от измерительных преобразователей физических величин, системы телеметрии, использующие цифровые каналы передачи для контроля и управления объектами, имеющие собственную структуру цифровых потоков [10]. Для контроля коэффициента битовых ошибок для таких линий передачи нецелесообразно использовать дорогостоящую каналообразующую аппарату.

Предложенное устройство решает задачи упрощения и возможности измерения количества бит, пораженных ошибками непосредственно в волоконно-оптических линиях передачи информации.

Сущность изобретения заключается в том, что в генераторную секцию устройства введены микроконтроллер, электронный коммутатор, передающий оптические модуль, в секцию анализатора устройства введены второй микроконтроллер, второй электронный коммутатор, приемный оптические модуль, второй тактовый генератор, причем выход тактового генератора генераторной секции подключается к входу синхронизации первого микроконтроллера, один из выходных портов первого микроконтроллера соединен с входом синхронизации первого регистра сдвига, выход регистра сдвига через коммутатор, второй вход которого подключен к одному из выходных портов микроконтроллера, а вход управления - к другому выходному порту микроконтроллера, соединен с входом передающего оптического модуля, оптически связанного волоконно-оптическим кабелем с приемным оптическим модулем, выход которого подключен к одному из входных портов второго микроконтроллера и к одному из входов второго устройства сравнения, выход устройства сравнения подключен к счетчику битов, пораженных ошибками через второй электронный коммутатор, вход управления которого соединен с одним из выходных портов второго микроконтроллера, один из выходных портов микроконтроллера соединен с входом синхронизации регистра сдвига секции анализатора, выход тактового генератора секции анализатора подключен к входу синхронизации второго микроконтроллера.

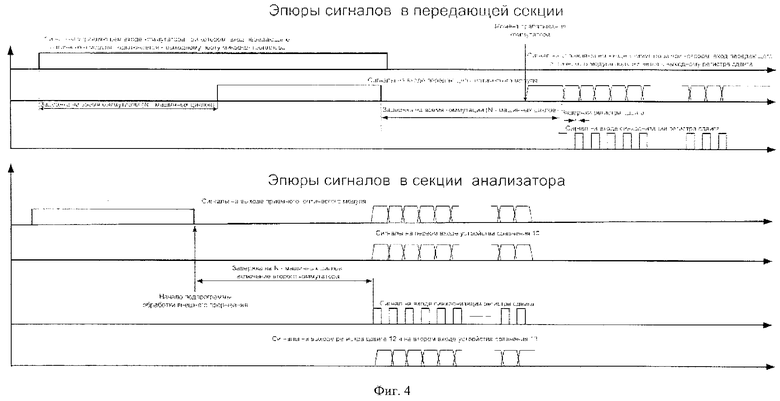

На фиг.3 изображена структурная схема измерителя коэффициента битовых ошибок в волоконно-оптических линиях передачи.

Устройство состоит из генераторной секции ГС и секции анализатора СА. Генераторная секция содержит тактовый генератор 1, микроконтроллер 2, регистр сдвига 3, устройство сравнения 4, электронный коммутатор 5, передающий оптический модуль 6. Секция анализатора содержит второй микроконтроллер 7, второй тактовый генератор 8, приемный оптический модуль 9, второе устройство сравнения 10, второй электронный коммутатор 11, второй регистр сдвига 12, третье устройство сравнения 13, счетчик битов, пораженных ошибками 14. Секции соединяются волоконно-оптическим кабелем, не входящим в состав устройства, а входящим в состав контролируемой волоконно-оптической линии передачи.

Устройство работает следующим образом.

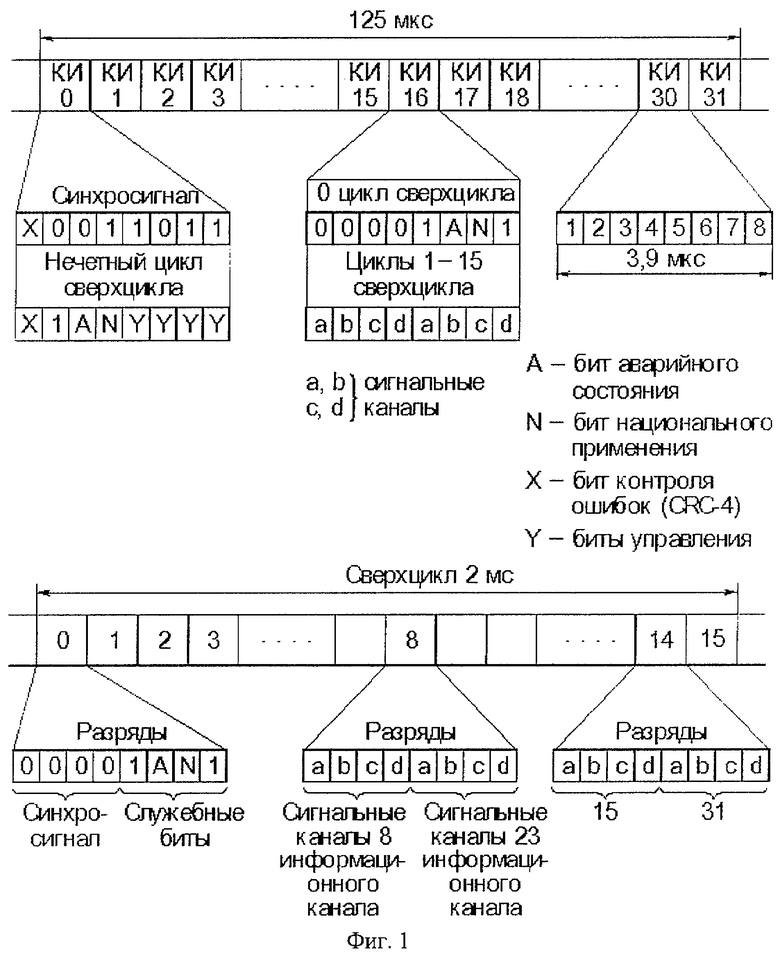

При включении питающих напряжений микроконтроллеры 2 и 7 начинают выполнять инструкции, записанные в резидентной памяти программ. Эпюры процессов в различных точках генераторной секции и секции анализатора представлены на фиг.4.

Выполнение программы начинается с установки на управляющем входе коммутатора 5 сигнала, разрешающего подключение входа передающего оптического модуля к выходному порту микроконтроллера 2. После ожидания в течение времени выполнения N машинных циклов, за которое происходит срабатывание коммутатора 5, на выходе этого порта генерируется стартовый импульс. Длительность этого импульса выбирается исходя из двух условий:

- длительность стартового импульса должна превышать длительность импульсов данных, передаваемых по линии передачи, и обеспечивать энергетический запас, достаточный для передачи его без искажений;

- длительность стартового импульса должна соответствовать разрешенному диапазону по длительности для передающего и приемного модулей.

После генерации стартового импульса микроконтроллер 2 устанавливает на управляющем входе коммутатора 5 сигнал, разрешающий подключение входа передающего оптического модуля 6 к выходу регистра сдвига 3. После ожидания, в течение которого происходит срабатывание коммутатора 5, на выходе микроконтроллера 2, соединенного с входом синхронизации, регистра сдвига 3 генерируется последовательность синхроимпульсов. Длительность синхроимпульсов определяется длительностью машинного цикла микроконтроллера 2 и определяется частотой тактового генератора 1. Частота следования должна соответствовать скорости передачи данных, на которой тестируется линия связи. Число импульсов в последовательности синхроимпульсов должно соответствовать рекомендациям ITU-TO.152 (ГОСТ 26783-85). Регистр сдвига 3 по фронту импульсов синхронизации генерирует на своем выходе псевдослучайную последовательность импульсов. Структура псевдослучайной последовательности задается устройством сравнения 4 в соответствии с рекомендациям ITU-TO.152 (ГОСТ 26783-85) и определяется номерами разрядов регистра 3, выходы которых соединены с входами устройства сравнения 4. Псевдослучайная последовательность через коммутатор 5 направляется на вход передающего оптического модуля 6, далее преобразуется в оптический сигнал и направляется в тестируемую волоконно-оптическую линию передачи.

Микроконтроллер 2 переходит к формированию следующей тестовой последовательности, состоящей из стартового импульса и псевдослучайной последовательности заданной длительности и структуры.

Сгенерированная генераторной секцией тестовая последовательность по волоконно-оптической линии передачи информации поступает на оптический вход приемного оптического модуля секции анализатора 9. Выход приемного оптического модуля 9 подключен к входу микроконтроллера 7 и одному из входов устройства сравнения 10. Второй микроконтроллер 7 по спаду сигнала на его входе начинает выполнять подпрограмму обработки внешнего прерывания. Подпрограмма обработки прерывания выполняет следующие действия:

- запрещает внешне прерывания;

- формирует сигнал на входе второго коммутатора 11, разрешающий подключение выхода устройства сравнения 10 с входом счетчика бит, пораженных ошибками 14 (в исходном состоянии коммутатор разомкнут);

- через N машинных циклов (частоты генераторов 1 и 8 должны быть равны) формирует последовательность синхроимпульсов, аналогичную последовательности сформированной в генераторной секции;

- после формирования последовательности синхроимпульсов отключает коммутатор 11 (разрывает связь между счетчиком бит, пораженных ошибками 14, и выходом устройства сравнения 10);

- разрешает внешние прерывания.

На этом подпрограмма обработки прерывания заканчивает свою работу.

Последовательность импульсов синхронизации, сформированная микроконтроллером 7, направляется на вход синхронизации регистра сдвига 12 аналогичного регистру сдвига 3. Регистр 12 совместно с устройством сравнения 13 формирует псевдослучайную последовательность, аналогичную последовательности, сформированной регистром 3 и устройством сравнения 4. Эта последовательность направляется на второй вход устройства сравнения 10, где сравнивается с псевдослучайной последовательностью с выхода фотоприемного модуля 9. При несовпадении битов последовательностей вырабатывается сигнал ошибки, который подается на вход счетчика 14. Отношение числа битов, пораженных ошибками, к общему числу переданных битов определяет коэффициент битовых ошибок. Подсчет переданных бит может вести как микроконтроллер 2, так и второй микроконтроллер 7.

Таким образом, достигается цель - обеспечивается возможность измерения коэффициента битовых ошибок волоконно-оптических линий передачи и устройство значительно упрощается, так как не содержит сложных кодирующих и декодирующих устройств для передачи импульсов синхронизации совместно с тестовыми последовательностями битов.

Использованная литература

1. Бакланов И.Г. Тестирование и диагностика систем связи. - М: Эко-Трендз, 2001, - 264 с.

2. Информация с Web-сервера компании Global Headquarters, http://www.acterna.com.

3. Информация с Web-сервера компании "Энергия Телеком", http://www.energy-telecom.ru.

4. Информация с Web-сервера компании "ЭЛЕКТРОНИКА", http://www.elektronika.ru.

5. Информация с Web-сервера Интернет-проекта "RusCable.ru", http://www.ruscable.ru.

6. Информация с Web-сервера компании "Радиан", http://www.radian.spb.ru.

7. Тестер СМ-Е1. Техническое описание и инструкция по эксплуатации СМ2. 135.000ТО, июль, 2003 г.

8. Информация с Web-сервера компании Trend Communications, http://www. trendcomms.corn от марта 2004 г.

9. Иванов Ю.П., Левин Л.С. и др. Комплекс оконечной аппаратуры цифровых систем передачи на БИС // Электросвязь, 1992, №3.

10. ГОСТ РВ 50899-96. Сети сбора данных волоконно-оптические на основе волоконно-оптических датчиков. Общие технические требования.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕРФЕЙС ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО ОПТИЧЕСКОМУ КАНАЛУ | 2005 |

|

RU2289207C1 |

| ОПТИЧЕСКИЙ РЕФЛЕКТОМЕТР | 2002 |

|

RU2214583C1 |

| ВОЛОКОННО-ОПТИЧЕСКИЙ ДАТЧИК ДЕФОРМАЦИЙ | 2004 |

|

RU2282142C1 |

| ОПТИЧЕСКИЙ РЕФЛЕКТОМЕТР | 2007 |

|

RU2339929C1 |

| СИНХРОНИЗАЦИЯ ПЕРЕДАЧИ ДАННЫХ В ДВУСТОРОННЕЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2156035C2 |

| СПОСОБ ПЕРЕДАЧИ ИНФОРМАЦИИ С ЗАЩИТОЙ ОТ ОШИБОК, СПОСОБ ПРИЕМА ИНФОРМАЦИИ С ЗАЩИТОЙ ОТ ОШИБОК И ПЕРЕДАЮЩАЯ СИСТЕМА ДЛЯ ПЕРЕДАЧИ ИНФОРМАЦИИ | 1996 |

|

RU2186459C2 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| Декодирующее устройство | 1991 |

|

SU1812637A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

Изобретение относится к измерительной технике, предназначено для проверки качества волоконно-оптических линий передачи информации и может найти применение в технике связи, в электронной промышленности при производстве оптических оптоэлектронных модулей, а также в других отраслях промышленности при производстве пассивных оптических компонентов для волоконно-оптических систем связи, влияющих на качество передачи информации. Технический результат состоит в упрощении и обеспечении возможности измерения коэффициента битовых ошибок, связанных непосредственно с влиянием волоконно-оптических линий передачи информации. Для этого в устройство введены микроконтроллеры, один из которых вырабатывает стробирующие импульсы, направляемые в контролируемую волоконно-оптическую линию передачи перед тестовой псевдослучайной последовательностью, а второй, принимая стробирующие импульсы, вырабатывает сигналы синхронизации. 5 ил.

Измеритель коэффициента битовых ошибок в волоконно-оптических линиях передачи, содержащий установленные в генераторной секций устройство сравнения, тактовый генератор и регистр сдвига, выход и дополнительный выход которого соединены с входами устройства сравнения, выход которого подключен к входу данных регистра, установленные в секции анализа второй регистр сдвига, выход и дополнительный выход которого соединены с входами второго устройства сравнения, выход которого подключен к входу данных второго регистра сдвига, счетчик битов, пораженных ошибками, третье устройство сравнения, первый вход которого соединен с выходом второго регистра сдвига, отличающийся тем, что в генераторную секцию введены микроконтроллер, электронный коммутатор, передающий оптический модуль, соединенный с тестируемой волоконно-оптической линией передачи, в секцию анализа введены второй микроконтроллер, второй тактовый генератор, второй электронный коммутатор и приемный оптический модуль, соединенный со вторым концом тестируемой волоконно-оптической линии передачи, причем выход тактового генератора генераторной секции соединен с входом синхронизации первого микроконтроллера, выходы которого связаны с входом синхронизации первого регистра сдвига, первым коммутируемым и управляющим входами электронного коммутатора, выход первого регистра сдвига подключен ко второму коммутируемому входу электронного коммутатора, выход которого соединен с входом передающего оптического модуля, выход тактового генератора секции анализа соединен с входом синхронизации второго микроконтроллера, выходы которого подключены к входу синхронизации второго регистра сдвига, управляющему входу второго электронного коммутатора, выход приемного оптического модуля соединен с входом второго микроконтроллера и вторым входом третьего устройства сравнения, выход которого соединен с входом счетчика битов, пораженных ошибками, через второй электронный коммутатор.

| Способ приготовления мыла | 1923 |

|

SU2004A1 |

| СПОСОБ УПРАВЛЕНИЯ ПРОЦЕССОМ ИЗГОТОВЛЕНИЯ ОПТИЧЕСКОГО ВОЛОКНА И СПОСОБ ИЗГОТОВЛЕНИЯ ОПТИЧЕСКОГО ВОЛОКНА | 1991 |

|

RU2096354C1 |

| US 4435850 А, 06.03.1984 | |||

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

Авторы

Даты

2005-10-27—Публикация

2004-05-12—Подача