Изобретение относится к вычислительной и информационной технике и может быть использовано для создания разнообразной аппаратуры компьютерных и информационных технологий, в том числе военной, ракетно-космической, экологической и бытовой сферах.

Наиболее близким к предлагаемому устройству является процессор [1], содержащий блок управления внешней памятью, местную память, блок микропрограммного управления, блок управляющей памяти. Основным недостатком данной структуры является недостаточно высокое быстродействие процессоров из-за относительно невысокой скорости передачи сигналов между блоками процессора.

Техническим результатом является повышение производительности, помехозащищенности и надежности процессоров, используемых в разнообразной аппаратуре компьютерных и информационных технологий.

Это достигается тем, что в оптический процессор, содержащий блок управления внешней памятью, блок местной памяти, блок микропрограммного управления, блок управляющей памяти, введены оптическая общая системная шина, блоки кэш памятей, блоки арифметико-логических операций с фиксированной точкой, блоки арифметико-логических операций с плавающей точкой, блоки конвейерных операций, блок управления процессора, оптический блок ввода/вывода сигналов процессора, внешняя магистраль ввода/вывода сигналов процессора, внутренняя оптическая магистраль ввода/вывода сигналов процессора, местные шины ввода/вывода, оптические блоки ввода/вывода, оптические шины ввода/вывода, оптические блоки дешифрации входных/выходных сигналов, местные шины связи с общей системной шиной, причем входы/выходы каждого блока управления внешней памятью, блока местной памяти, блока микропрограммного управления, блока управляющей памяти, блока кэш памятей, блоков арифметико-логических операций с фиксированной точкой, блоков арифметико-логических операций с плавающей точкой, блоков конвейерных операций, блока управления процессора, через соответствующие последовательно расположенные и связанные между собой местную шину ввода/вывода, оптический блок ввода/вывода, оптическую шину ввода/вывода, оптический блок дешифраторов входных/выходных сигналов, местную шину связи с общей системной шиной оптически связаны с оптической общей системной шиной, входы/выходы которой через последовательно расположенные и оптически связанные внутреннюю оптическую магистраль ввода/вывода сигналов процессора, оптический блок ввода/вывода сигналов в процессор связаны с внешней магистралью ввода/вывода сигналов в процессор, вход/выход которой является входом/выходом оптического процессора.

А также тем, что оптическая общая системная шина содержит одну единственную оптическую магистраль.

А также тем, что оптическая общая системная шина содержит оптическую магистраль адресов, оптическую магистраль данных, оптическую магистраль управления.

Данная совокупность существенных признаков и связей между ними позволяет получить устройство, обладающее более чем в 1000 раз большей производительностью, помехозащищенностью и надежностью.

Сущность изобретения заключается в том, что на основе использования оптических методов передачи сигналов, применения оптической общей системной шины, использующей в качестве передающей среды свободное пространство и/или световоды (волоконные и/или интегральные), оригинальных схем оптического ввода/вывода сигналов из блоков процессора, оригинальной структуры процессора создана архитектура оптического процессора ВЕРБ-1 Александра ВЕРБОВЕЦКОГО, позволяющая существенно повысить производительность, помехозащищенность и надежность процессоров и различной аппаратуры, построенной на их основе.

Таким образом, предложенный оптический процессор ВЕРБ-1 Александра ВЕРБОВЕЦКОГО обладает свойствами, не присущими известным устройствам. Это объясняется новой совокупностью существенных признаков и новыми связями, изложенными выше.

Сравнение предлагаемого устройства с известными свидетельствует о соответствии его критерию «новизна», а отсутствие в аналогах отличительных признаков предлагаемого устройства - о соответствии критерию «изобретательский уровень».

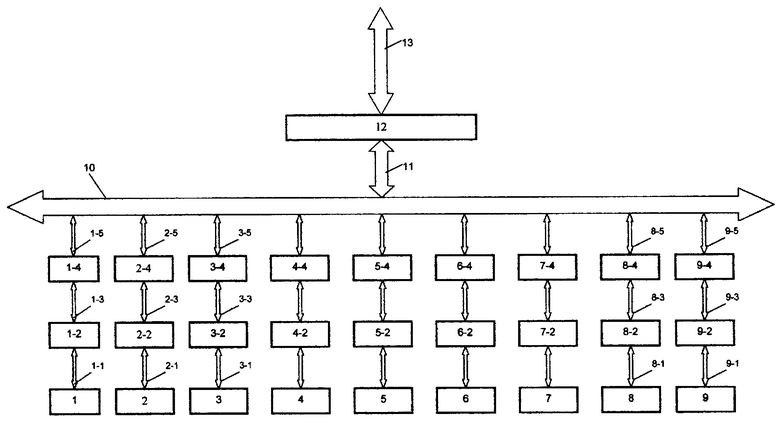

На чертеже приведена функциональная схема оптического процессора ВЕРБ-1 Александра ВЕРБОВЕЦКОГО.

Оптический процессор ВЕРБ-1 Александра ВЕРБОВЕЦКОГО содержит:

блок управления внешней памятью 1, имеющий местные шины ввода/вывода 1-1, оптические блоки ввода/вывода 1-2, оптические шины ввода/вывода 1-3, оптические блоки дешифраторов входных/выходных сигналов 1-4, местные шины связи с общей системной шиной 1-5; блок микропрограммного управления 2, имеющий местные шины ввода/вывода 2-1, оптические блоки ввода/вывода 2-2, оптические шины ввода/вывода 2-3, оптические блоки дешифраторов входных/выходных сигналов 2-4, местные шины связи с общей системной шиной 2-5; блок местной памяти 3, имеющий местные шины ввода/вывода 3-1, оптические блоки ввода/вывода 3-2, оптические шины ввода/вывода 3-3, оптические блоки дешифраторов входных/выходных сигналов 3-4, местные шины связи с общей системной шиной 3-5; блок кэш памятей 4, имеющий местные шины ввода/вывода 4-1, оптические блоки ввода/вывода 4-2, оптические шины ввода/вывода 4-3, оптические блоки дешифраторов входных/выходных сигналов 4-4, местные шины связи с общей системной шиной 4-5; блок арифметико-логических операций с фиксированной точкой 5, имеющий местные шины ввода/вывода 5-1, оптические блоки ввода/вывода 5-2, оптические шины ввода/вывода 5-3, оптические блоки дешифраторов входных/выходных сигналов 5-4, местные шины связи с общей системной шиной 5-5; блок арифметико-логических операций с плавающей точкой 6, имеющий местные шины ввода/вывода 6-1, оптические блоки ввода/вывода 6-2, оптические шины ввода/вывода 6-3, оптические блоки дешифраторов входных/выходных сигналов 6-4, местные шины связи с общей системной шиной 6-5; блоки конвейерных операций 7, имеющие местные шины ввода/вывода 7-1, оптические блоки ввода/вывода 7-2, оптические шины ввода/вывода 7-3, оптические блоки дешифраторов входных/выходных сигналов 7-4, местные шины связи с общей системной шиной 7-5; блок управляющей памяти 8, имеющий местные шины ввода/вывода 8-1, оптические блоки ввода/вывода 8-2, оптические шины ввода/вывода 8-3, оптические блоки дешифраторов входных/выходных сигналов 8-4, местные шины связи с общей системной шиной 8-5; блок управления процессором 9, имеющий местные шины ввода/вывода 9-1, оптические блоки ввода/вывода 9-2, оптические шины ввода/вывода 9-3, оптические блоки дешифраторов входных/выходных сигналов 9-4, местные шины связи с общей системной шиной 9-5; оптическую общую системную шину 10; внутреннюю оптическую магистраль ввода/вывода сигналов процессора 11; оптический блок ввода/вывода сигналов в процессор 12; внешняя магистраль ввода/вывода сигналов в процессор 13.

Блок управления внешней памятью 1 предназначен для осуществления динамического обмена данными между процессором и внешней по отношению к процессору памятью, в состав блока могут входить памяти ключей защиты, сверх оперативная память, память многоабонентного доступа, блок динамического преобразования адресов при реализации виртуальной памяти. Блок 1 может быть выполнен на электронных, оптоэлектронных и оптических компонентах.

Местные шины ввода/вывода 1-1 служат для передачи электрических или оптических сигналов, могут содержать магистрали адресов, данных и управления, имеющие в зависимости от варианта передаваемых сигналов, в качестве проводящей среды, например, металлические проводники, один или несколько световодов (волоконных и/или интегральных) или свободное пространство.

Оптические блоки ввода/вывода 1-2 служат для согласования и, в случае необходимости, преобразования входных/выходных электронных или оптических сигналов в оптические или электрические, в соответствии с типом выполнения блока 1. Для преобразования входных электронных сигналов в оптические эти блоки могут быть выполнены, например, в виде линеек или матриц лазерных диодов, каждый из которых излучает, например, на своей длине волны λi, где i=1,2,3...р, при этом р - максимальное число сигналов, передаваемых параллельным кодом, а при передаче сигналов последовательно-параллельным кодом, последовательные оптические сигналы передаются, например, каждым лазерным диодом на различных длинах волн λj (где j=1, 2,3... s, s - максимальное число сигналов, передаваемых последовательным кодом), отличных от длин волн оптических сигналов, которые передаются параллельным кодом. Если на входы блока 1-2 поступают оптические сигналы; то на их входах дополнительно могут располагаться линейки или матрицы фотоприемников.

Оптические шины ввода/вывода 1-3 служат для передачи оптических сигналов и могут содержать магистрали адресов, данных и магистрали управления, имеющие в качестве передающей среды, например, один или несколько световодов (волоконные и/или интегральные) или свободное пространство.

Оптические блоки дешифраторов входных/выходных сигналов 1-4 служат для выделения определенной группы спектральных оптических сигналов из множества групп спектральных оптических сигналов, распространяющихся по оптической общей системной шине 10, которые соответствуют блоку 1. Блок 1-4 может быть выполнен, например, на основе световодной (волоконной и/или интегральной) оптики с использованием дифракционных решеток или спектральных фильтров, мультиплексоров, демультиплексоров.

Местная шина связи с оптической общей системной шиной 1-5 служит для передачи оптических сигналов в/из оптической системной шины 10 от/к блоку 1 и может состоять из одной магистрали или содержать магистрали адресов, данных и управления. Магистрали могут быть выполнены в виде одного или нескольких световодов (волоконных и/или интегральных) или свободного пространства.

Блок микропрограммного управления 2 осуществляет в режиме разделения времени или спектрального уплотнения управление работой блоками процессора и некоторыми процедурами каналов ввода/вывода, используя для этого микропрограммы, хранящиеся в управляющей памяти. При этом он выдает предписание микрокомандой управляющие сигналы в соответствующие блоки процессора, формирует адрес следующей микрокоманды и обрабатывает прерывание микропрограмм. При прерывании микропрограммы в блоке запоминается адрес следующей подлежащей выполнению микрокоманды. Блок 2 может иметь электронное, оптоэлектронное или оптическое выполнение.

Шины 2-1, 2-3, 2-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 2-2, 2-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок местной памяти 3 процессора может служить для хранения операндов и результатов операций, значения базовых адресов и индексов, данных блока восстановления и диагностики, управляющих слов активных подканалов. Блок 3 может иметь, например, электронное, оптоэлектронное или оптическое выполнение.

Шины 3-1, 3-3, 3-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 3-2, 3-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок кэш памятей 4 служит для согласования пропускных способностей внешней к процессору памяти и процессора для реализации в процессоре производительности, равной производительности его операционных блоков, и может состоять из нескольких модулей кэш-памяти. Блок 4 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 4-1, 4-3, 4-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 4-2, 4-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок арифметико-логических операций с фиксированной точкой 5 служит для выполнения арифметических операций с двоичными числами с фиксированной точкой, шестнадцатеричными (двоично-кодированными) числами с плавающей точкой, десятичными (двоично-кодированными) числами переменной длины, логические операции над логическими кодами фиксированной и переменной длины, операции над алфавитно-цифровыми полями, операции формирования исполнительных адресов операндов. Блок 5 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 5-1, 5-3, 5-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 5-2, 5-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок арифметико-логических операций с плавающей точкой 6 служит для выполнения арифметических и логических операций над кодами слов, представленными числами с плавающей точкой. Блок 6 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 5-1, 5-3, 5-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 5-2, 5-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Шины 6-1, 6-3, 6-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 6-2, 6-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блоки конвейерных операций 7 служат для выполнения операций при обработке информации на конвейерном принципе, например при выполнении матричных операций. Блок 7 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 7-1, 7-3, 7-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 7-2, 7-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок управляющей памяти 8 предназначен для хранения микропрограмм управления и является полностью перезагружаемой. Блок 8 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 8-1, 8-3, 8-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 8-2, 8-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Блок управления процессором 9 предназначен для управления работой процессора и основан на смешанном аппаратно-микропрограммном принципе. Блок 8 может быть выполнен на электронных, оптоэлектронных и оптических элементах.

Шины 9-1, 9-3, 9-5 имеют то же назначение и выполнение, что и аналогичные шины 1-1, 1-3, 1-5.

Блоки 9-2, 9-4 имеют то же назначение и выполнение, что и аналогичные блоки 1-2, 1-4.

Оптическая общая системная шина 10 служит для передачи оптических сигналов между различными блоками оптического процессора и может содержать одну единственную оптическую магистраль в виде одного световода (волоконного и/или интегрального) или свободного пространства, или может содержать магистраль адресов, магистраль данных и магистраль управления. Каждая магистраль может иметь в качестве передающей оптической среды, один или несколько световодов (волоконных и/или интегральных) или свободное пространство.

Внутренняя оптическая магистраль ввода/вывода сигналов процессора 11 служит для передачи оптических сигналов из внешних по отношению к процессору устройств в оптическую общую системную шину процессора и может содержать одну магистраль или магистрали адресов, данных и управления, имеющие в качестве передающей среды, например, один или несколько световодов (волоконных и/или интегральных) или свободное пространство.

Оптический блок ввода/вывода сигналов в процессор 12 служит для согласования внешних по отношению к процессору сигналов с оптическими сигналами, передаваемыми по оптической общей системной шине процессора, и может иметь выполнение, аналогичное блоку 1-2.

Внешняя магистраль ввода/вывода сигналов в процессор 13 служит для передачи электрических или оптических сигналов из внешних по отношению к процессору устройств в или из процессора и может содержать одну магистраль или магистрали адресов, данных и управления. В зависимости от передаваемых по магистралям сигналов, в качестве их передающей среды могут использоваться либо металлические проводники, либо один или несколько световодов (волоконных и/или интегральных) или свободное пространство.

Оптический процессор ВЕРБ-1 Александра ВЕРБОВЕЦКОГО работает следующим образом.

Каждый из передающих информацию: блоков 1-9 процессора, передает ее в виде электронных или оптических сигналов, которые через соответствующие шины 1-1, 1-3, 1-5...9-1, 9-3, 9-5 и блоки 1-2, 1-4...9-2, 9-4 поступают в оптическую общую системную шину 10 в виде спектральных оптических сигналов со спектральным или временным уплотнением.

Спектральные оптические сигналы от всех передающих блоков 1-9 одновременно со спектральным уплотнением распространяются по общей системной шине 10 и поступают во все входные местные оптические шины 1-5...9-5.

В каждом из принимающих информацию блоков 1-9 оптические блоки дешифраторов 1-4...9-4 настраиваются управляющими сигналами на пропускание групп спектральных оптических сигналов, передаваемых от соответствующих передающих информацию блоков, с которыми они производят сеанс связи. Затем выделенные этими блоками дешифрации оптические сигналы в данном принимающем канале преобразуются и поступают на обработку в соответствующие блоки 1-9.

Следует отметить, что передача информации по всем шинам системы может производиться сигналами как только со спектральным уплотнением, так и одновременно со спектральным и временным уплотнениями, а сеансы связи всех блоков системы могут осуществляться как одновременно, так и группами с разделением во времени.

Использование изобретения позволит реализовать оптическими методами связь между блоками процессора по оптической общей системной шине, увеличив более чем в 1000 раз его производительность, помехозащищенность и надежность. Такие оптические процессоры ВЕРБ-1 Александра ВЕРБОВЕЦКОГО могут широко применяться в разнообразной радиоэлектронной аппаратуре военного, ракетно-космического, экологического и бытового назначения как наземного, так и бортового базирования.

ЛИТЕРАТУРА

1. А.А.Вербовецкий «Основы компьютерных технологий & персональные ПК», Москва, АЛЕКС, 2003 г., с.314 (с.128).

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТИЧЕСКИЙ АССОЦИАТИВНЫЙ ПОИСКОВЫЙ ПРОЦЕССОР "ВЕРБ-2" АЛЕКСАНДРА ВЕРБОВЕЦКОГО | 2003 |

|

RU2263946C2 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СИГНАЛЬНЫЙ ПРОЦЕССОР "ВЕРБ-3" АЛЕКСАНДРА ВЕРБОВЕЦКОГО | 2003 |

|

RU2263340C2 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ КОМПЬЮТЕР "АЛЕКС-ВЕРБ" АЛЕКСАНДРА ВЕРБОВЕЦКОГО | 2004 |

|

RU2284050C2 |

| ОПТОЭЛЕКТРОННАЯ СИСТЕМНАЯ ПЛАТА ДЛЯ ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА | 2001 |

|

RU2205443C2 |

| ОПТОЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ОБЩЕЙ СИСТЕМНОЙ ШИНОЙ | 1999 |

|

RU2144206C1 |

| ОПТОЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1999 |

|

RU2155367C1 |

| Процессор | 1984 |

|

SU1247884A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1991 |

|

RU2042193C1 |

| ОПТИЧЕСКАЯ ИНТЕРФЕЙСНАЯ СЕТЬ КОМПЬЮТЕРНОЙ ПЕРИФЕРИИ | 2001 |

|

RU2206117C2 |

| Процессор для мультипроцессорной системы | 1989 |

|

SU1688252A1 |

Изобретение относится к компьютерной и информационной технике, а именно к вычислительным устройствам, выполненным на оптоэлектронной элементной базе. Техническим результатом является повышение производительности, помехозащищенности и отказоустойчивости заявленного устройства в условиях воздействия мощных электромагнитных полей на аппаратуру как наземного, так и бортового базирования, используемую в разнообразных компьютерных и информационных технологиях. Для этого процессор содержит блок управления внешней памятью, блок местной памяти, блок микропрограммного управления, блок управляющей памяти, оптическую общую системную шину, блоки кэш памятей, блоки арифметико-логических операций с плавающей точкой, блоки арифметико-логических операций с фиксированной точкой, блоки конвейерных операций, блок управления процессора, оптический блок ввода/вывода сигналов процессора, внутренняя оптическая магистраль ввода/вывода сигналов процессора, местные шины ввода/вывода, оптические блоки ввода/вывода, оптические шины ввода/вывода, оптические блоки дешифрации входных/выходных сигналов, местные шины связи с общей системной шиной. 2 з.п. ф-лы, 1 ил.

| ОПТОЭЛЕКТРОННАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА С ОБЩЕЙ СИСТЕМНОЙ ШИНОЙ | 1999 |

|

RU2144206C1 |

| Основы компьютерных технологий & современные ПК | |||

| М.: Алекс, 2002, с | |||

| Прибор, автоматически записывающий пройденный путь | 1920 |

|

SU110A1 |

Авторы

Даты

2005-11-10—Публикация

2003-08-06—Подача