Область техники, к которой относится изобретение

Настоящее изобретение относится к электродной решетке, содержащей первый и второй тонкопленочные электродные слои с электродами в форме полосковых электрических проводников в каждом слое, причем электроды второго электродного слоя скрещены или ориентированы, по существу, перпендикулярно по отношению к электродам первого электродного слоя. По меньшей мере, один из электродных слоев расположен на изолирующей поверхности подложки или объединительной платы. При этом электродные слои расположены в параллельных взаимно смещенных плоскостях, контактирующих с цельным слоем функциональной среды, находящейся между указанными слоями.

Настоящее изобретение относится также к устройству, содержащему, по меньшей мере, одну электродную решетку, содержащую первый и второй тонкопленочные электродные слои с электродами в форме полосковых электрических проводников в каждом слое. Электроды второго электродного слоя скрещены или ориентированы, по существу, перпендикулярно по отношению к электродам первого электродного слоя. По меньшей мере, один из электродных слоев расположен на изолирующей поверхности подложки или объединительной платы, при этом первый и второй электродные слои расположены в параллельных взаимно смещенных плоскостях, контактирующих с цельным слоем функциональной среды, находящейся между указанными слоями.

Устройство по изобретению содержит также функциональные элементы, образованные в объеме функциональной среды и определяемые зонами взаимного наложения электродов первого электродного слоя и электродов второго электродного слоя с формированием набора с матричной адресацией. Каждый такой функциональный элемент может быть активирован путем подачи напряжения на скрещивающиеся электроды, задающие этот функциональный элемент. Физическое состояние данного функционального элемента под действием приложенного к нему электрического потенциала может быть изменено на временной или постоянной основе или переключено между двумя различимыми физическими состояниями. При этом подача напряжения соответствует адресации указанного функционального элемента с целью осуществления операции записи или считывания.

В зависимости от свойств используемой функциональной среды функциональные элементы способны функционировать в качестве переключаемых логических элементов в устройстве обработки данных, ячеек памяти в устройстве хранения данных или пикселов в устройстве отображения информации с адресацией функциональных элементов по схеме матричной адресации.

Уровень техники

Настоящее изобретение, в первую очередь, касается электродных решеток для использования в устройствах, содержащих функциональные элементы, образующие планарный набор, в котором адресация элементов осуществляется посредством первой электродной решетки с параллельными полосковыми электродами, расположенными по одну сторону от функциональных элементов в контакте с ними, и второй электродной решетки с аналогичными электродами, которые ориентированы, однако, перпендикулярно электродам первой электродной решетки и расположены по другую сторону от функциональных элементов в контакте с ними. В совокупности названные элементы образуют так называемое устройство с матричной адресацией. Устройства подобного типа могут, например, содержать функциональные элементы в виде логических ячеек или ячеек памяти. При этом функциональные элементы могут содержать одно или более активных переключающих средств. В таком случае устройство с матричной адресацией называется устройством с активной матричной адресацией. Альтернативно, функциональные элементы могут содержать только пассивные средства, например, резистивные или емкостные. В таком случае устройство с матричной адресацией называется устройством с пассивной матричной адресацией.

Последнее из названных устройств рассматривается как обеспечивающее более эффективный вариант адресации, например, в случае запоминающих устройств, поскольку в составе ячейки памяти не требуется иметь никаких переключающих элементов, в частности, транзисторов. Одновременно представляется желательным обеспечить как можно более высокую плотность записи сохраняемых данных. Однако существующие правила конструирования накладывают ограничения на минимальный размер ячейки и одновременно ограничивают коэффициент заполнения, т.е. площадь поверхности запоминающего материала, которая реально может быть использована для целей хранения информации в устройстве с матричной адресацией.

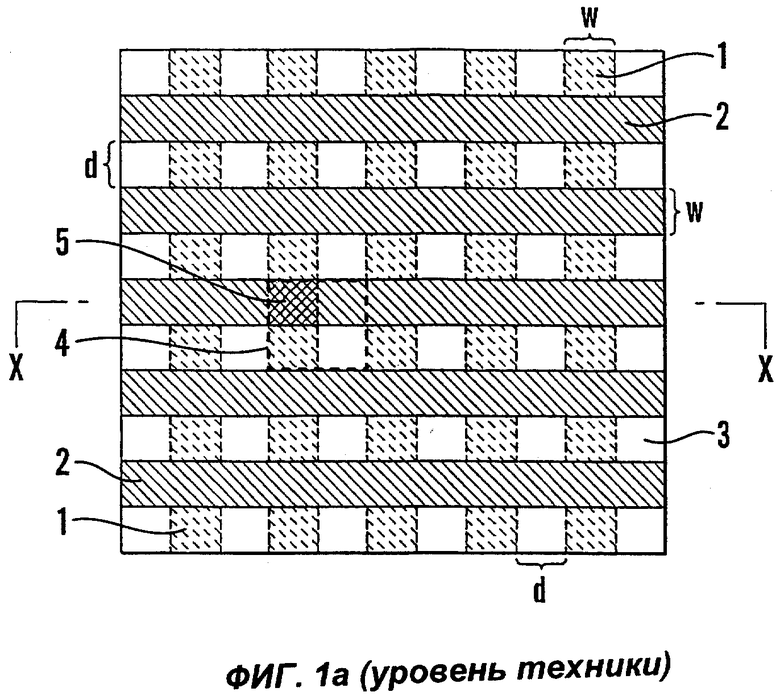

На фиг.1а изображено известное устройство с матричной адресацией, которое содержит цельный планарный слой функциональной среды 3, расположенный между первой электродной решеткой, содержащей параллельные полосковые электроды 1, имеющие ширину w и отстоящие друг от друга на расстояние d, и схожей второй электродной решеткой, содержащей параллельные полосковые электроды 2, имеющие такую же ширину. При этом электроды 2 ориентированы перпендикулярно электродам 1. Взаимное наложение электродов 1, 2 соответствующих электродных решеток задает в цельном слое функциональной среды 3 функциональные элементы 5. Посредством подачи напряжения на электроды, скрещивающиеся в зоне расположения функционального элемента (который может представлять собой, например, логическую ячейку или ячейку памяти), его функциональное состояние может быть изменено или переключено.

Фиг.1b, на котором известное устройство по фиг.1а показано в сечении плоскостью Х-Х, поясняет взаимное расположение электродов 1, 2 и цельного слоя функциональной среды 3, расположенного между ними, а также положение функционального элемента 5. Как правило, свойства функциональной среды 3 подбираются таким образом, что подача напряжения на скрещенные электроды 1, 2 оказывает влияние только на функциональный элемент 5, расположенный в зоне скрещивания этих электродов, т.е. в непосредственной близости от функционального элемента 5. Если функциональная среда 3, образующая цельный слой, является электропроводной, указанное условие может быть выполнено за счет придания ей свойств анизотропной электропроводности. Другими словами, проводимость будет иметь место только в вертикальном направлении, при отсутствии какого-либо тока через слой функциональной среды к другим функциональным элементам.

Однако во многих приложениях функциональная среда, образующая цельный слой, может не обладать электропроводностью, т.е. представлять собой диэлектрик. Следовательно, функциональный элемент может рассматриваться, как обладающий высоким сопротивлением или являющийся диэлектриком, т.е. как конденсатор. При этом диэлектрическая функциональная среда может представлять собой поляризуемый неорганический или органический материал, обладающий гистерезисными свойствами. К числу подобных материалов относятся как ферроэлектрические, так и электретные материалы. Поляризационные и гистерезисные свойства подобных материалов могут быть использованы для создания, например, ферроэлектрических или электретных матричных запоминающих устройств, имеющих конфигурацию, подобную представленной на фиг.1а. В устройствах такого типа состояние поляризации ячейки памяти, т.е. функционального элемента 5, может быть задано подачей соответствующего напряжения на электроды, задающие ячейку памяти, лежащую в зоне их взаимного скрещивания. При этом поляризацию ячейки можно переключать; альтернативно, ячейка может быть возвращена в свое исходное состояние посредством операций, соответствующих записи и считыванию данных в эту ячейку.

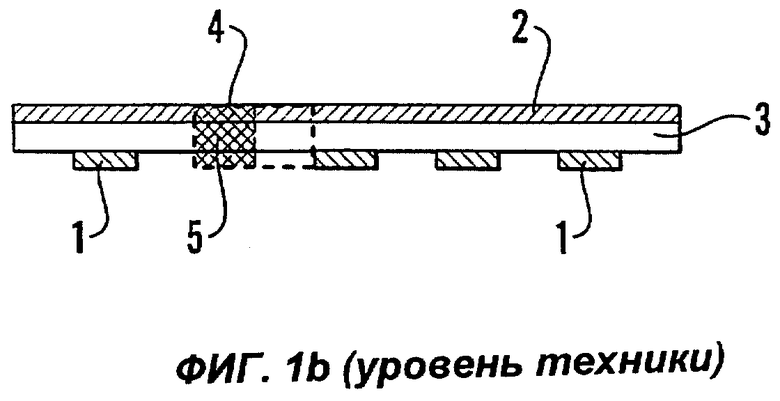

Функциональные характеристики подобных матричных устройств, естественно, зависят не только от свойств выбранной функциональной среды, но также от архитектурных и структурных ограничений, накладываемых при создании запоминающего устройства. Емкость запоминающей среды 3, выполненной в виде цельного слоя, зависит от размера и плотности расположения ячеек 5 памяти. В свою очередь, данные параметры зависят от минимального технологически достижимого размера, который может быть реализован в процессе изготовления устройства. Например, когда электроды формируются посредством металлизации, т.е. путем нанесения слоя металла, которому затем придается заданный рисунок с использованием фотомикролитографического процесса с применением фотолитографических масок в сочетании, например, с травлением, минимальный технологически достижимый размер f определяется свойствами маски. В свою очередь, свойства маски будут зависеть от длины волны используемого излучения. Другими словами, на современном уровне развития технологии указанный размер f будет составлять 0,15-0,2 мкм. Как следствие, ширина w электродов 1, 2 и расстояние между ними будут примерно того же порядка.

В этой связи можно отметить, что параметр 2f обычно называется шагом, а максимальное количество разрешаемых линий на единицу длины, достигаемое с применением известной технологии изготовления, задается параметром 0,5f. Соответственно, максимальное количество элементов на единицу площади задается коэффициентом 0,25f2. Следовательно, если рассмотреть участок 4, показанный на фиг.1, площадь ячейки, как это видно из фиг.1с (на которой участок 4 изображен более детально), составит f2. При этом становится понятно, что для каждой ячейки требуется пространство, соответствующее участку 4, площадь которого составляет 4f2, т.е. в 4 раза превышает площадь f2 поверхности ячейки. Из проведенного анализа ясно, что матрица, представленная на фиг.1а, имеет коэффициент заполнения, равный 0,25 (т.е. f2/4f2). Следовательно, степень использования поверхности, сформированной слоем функциональной среды 3, является низкой. Для того чтобы достичь более высокого коэффициента заполнения или более высокой плотности расположения ячеек 5 в слое функциональной среды 3, представляется желательным либо увеличить коэффициент заполнения, либо добиться более высокого разрешения в процессе изготовления матрицы, т.е. перейти к размерам, меньшим чем 0,1 мкм. Однако во втором случае, хотя и появится возможность увеличить общее количество ячеек на той же площади, возможность повышения коэффициента заполнения не будет гарантирована.

В случае матричных устройств активного типа, которые содержат, по меньшей мере, один активный переключающий элемент, ассоциированный с каждым функциональным элементом (т.е. с ячейкой), коэффициент заполнения имеет еще меньшее значение и в типичном случае составляет только 1/6, т.е. 16,7%.

Из патента США №5017515 известен процесс, обеспечивающий получение сублитографических расстояний между элементами интегральной схемы. Как показано на фиг.1 названного документа, известный процесс применим для формирования плотно расположенных параллельных полосковых электродов 13, 19, изолированных друг от друга посредством изолирующего элемента 14. Данный элемент свободен от каких-либо ограничений на размер, налагаемых использованием фотомикролитографического процесса. Как следствие, данный элемент может быть выполнен очень тонким по сравнению с размерами проводников, т.е. электродов. В указанном патентном документе описано, каким образом электродные решетки, изготовленные предлагаемым способом, могут быть применены для формирования полосковых электродов для элементов с плавающим затвором в интегральной схеме, например, в полупроводниковом запоминающем устройстве, ячейки памяти которого содержат переключающую и запоминающую транзисторные структуры. При этом разрядные шины (шины данных) образованы соответствующим допированием подложки, очевидно, с применением для допирования той же фотомаски, которая применяется при формировании электродного слоя высокой плотности. Управляющие электроды 42 для разрядных шин и для числовых (управляющих) шин изолированы с помощью соответствующего изолятора от полосковых электродов 13, 19 плавающих затворов. Результирующая структура представляет собой полупроводниковое запоминающее устройство с набором мультитерминальных ячеек памяти, содержащих транзисторы.

Однако в данном патенте США №5017515 не содержится никаких указаний по формированию электродных решеток с двумя электродными слоями, каждый из которых содержит электроды, расположенные с высокой плотностью и ориентированные таким образом, что электроды двух указанных слоев совместно образуют электродную матрицу, пригодную для адресации функциональных элементов в составе цельного слоя функциональной среды, расположенной между электродными слоями и находящейся в контакте с этими слоями. Эффективное использование матричной адресации к функциональным элементам в составе цельного слоя функциональной среды предполагает также высокую степень планаризации, которой должны обладать слои устройства с матричной адресацией описанного типа. Однако это требование является труднодостижимым с использованием известной технологии, поскольку создание топографических структур, ориентированных в ортогональном направлении над подложкой, подразумевает, что дополнительные электродные слои будут воспроизводить контуры данной структуры в своих поверхностных элементах. Кроме того, известные решения оказались бы непригодными в случае, когда множество наборов с матричной адресацией должны быть собраны в стопу с образованием объемных (трехмерных) устройств типа стопы из множества запоминающих устройств с матричной адресацией, известных из уровня техники.

Пример устройства с матричной адресацией, выполненного в виде устройства обработки данных или запоминающего устройства, содержащего электронные слои, расположенные по обе стороны от цельного слоя функциональной среды таким образом, что электроды данных слоев образуют ортогональную электродную матрицу, описан, например, в международной заявке WO 98/58383. Разумеется, устройства подобного типа выиграют от повышения плотности расположения функциональных элементов в составе матрицы независимо от конкретного вида функциональных элементов, в частности, когда эти элементы представляют собой ячейки памяти, при условии, что данные элементы соответствуют зоне взаимного наложения скрещивающихся электродов первого и второго электродных слоев.

Раскрытие изобретения

С учетом изложенного главная задача, на решение которой направлено настоящее изобретение, состоит в том, чтобы обеспечить возможность повышения коэффициента заполнения в матричных устройствах вышеописанного типа до значений, приближающихся к 1, и тем самым достичь максимального использования площади цельного слоя функциональной среды 3 в подобных устройствах. При этом на это использование не должны влиять ограничения, связанные с реальным или практичным значением минимального технологически достижимого размера f. Действительно, коэффициент заполнения не будет изменяться при уменьшении размера f, хотя подобное уменьшение, разумеется, будет приводить к дальнейшему увеличению количества функциональных элементов, которые можно сформировать в цельном слое функциональной среды 3.

Матричные устройства типа представленного на фиг.1а могут быть собраны в стопу, с установкой устройств друг на друга для формирования объемных устройств. В таком случае каждое единичное устройство отделяется от следующего устройства в стопе посредством разделительного или изолирующего слоя для того, чтобы подача напряжений на электроды одного из таких устройств и переключение функциональных элементов этого устройства не влияли на смежные устройства в стопе. Подобные объемные устройства, разумеется, обеспечивают возможность создания объемных запоминающих устройств большой емкости. Однако нетрудно понять, что за счет повышения коэффициента заполнения до значений близких к 1 (т.е. к 100%), суммарная емкость единичного матричного устройства может приблизиться к емкости четырех аналогичных матричных устройств обычного типа, собранных в стопу для формирования объемного устройства.

Хотя не существует теоретического предела для количества устройств, образующих стопу, можно рассматривать как недостаток такой стопы появление нежелательных электрических, физических и тепловых связей, которые могут возникать между устройствами, собираемыми в стопу, например, в случае широкомасштабной параллельной адресации к функциональным элементам входящих в стопу устройств. Еще одним недостатком является наличие отклонений от плоскостности, присущее каждому из устройств, составляющих стопу. Хотя такое устройство может рассматриваться как, по существу, планарное, отклонения от плоскостности будут накапливаться по мере добавления очередных устройств к стопе. В результате, по мере увеличения количества устройств в стопе, она будет содержать все большее количество неровностей. Наличие подобных неровностей будет также весьма нежелательным при реализации технологии изготовления, по существу, планарных контуров.

С учетом данного обстоятельства дополнительная задача, решаемая настоящим изобретением, заключается в увеличении суммарной емкости, определяемой общим количеством функциональных элементов, которые могут быть реализованы в матричном устройстве, и в снижении за счет этого необходимости разработки многослойных или объемных устройств в виде многослойной стопы в тех случаях, когда сопоставимая емкость может быть достигнута с использованием стопы, содержащей только четверть от количества устройств или слоев, необходимых при использовании известной технологии.

Кроме того, изобретение решает задачу создания электродной решетки, которая легко может быть реализована с достижением очень высокой степени плоскостности, т.е. с устранением поверхностных неровностей. Тем самым электродная решетка становится более приспособленной для использования в объемных устройствах типа стопы.

Перечисленные задачи, а также дополнительные преимущества и свойства реализуются в соответствии с настоящим изобретением за счет создания электродной решетки. Электродная решетка по изобретению характеризуется тем, что каждый из тонкопленочных электродных слоев содержит первый набор указанных электродов с шириной wa и высотой ha, отстоящих друг от друга на расстояние d, равное их ширине wа или превышающее ее, второй набор указанных электродов с шириной wb и высотой hb, находящихся в промежутках между электродами первого набора и электрически изолированных от них посредством тонкой пленки из электрически изолирующего материала толщиной δ, расположенной, по меньшей мере, вдоль боковых краев параллельных электродов первого и второго наборов с формированием между указанными электродами изолирующей стенки толщиной δ, существенно меньшей ширины wa или ширины wb, причем расстояние d между электродами первого набора составляет wb+2δ, а электродные слои с электродами и с тонкой изолирующей пленкой образуют цельные планарные слои в составе электродной решетки.

Электропроводный материал электродов, по меньшей мере, одного из электродных слоев предпочтительно нанесен непосредственно на поверхность подложки.

Кроме того, желательно, чтобы электроды одного из электродных слоев были открыты на наружную сторону указанного слоя, противоположную по отношению к другому электродному слою. Альтернативно, поверхность одного из электродных слоев, противоположная по отношению к другому электродному слою, может быть закрыта подложкой.

В одном из предпочтительных вариантов осуществления изобретения площади поперечных сечений электродов обоих наборов электродов могут быть равными, т.е. выполняется соотношение waha=wbhb.

В другом предпочтительном варианте площадь поперечного сечения электродов первого набора электродов выбрана отличной от площади поперечного сечения электродов второго набора, т.е. waha≠wbhb.

Согласно еще одному предпочтительному варианту электроды обоих наборов выполнены из одного электропроводного материала.

В следующем предпочтительном варианте осуществления изобретения электроды второго набора электродов выполнены из электропроводного материала, отличного от электропроводного материала, из которого выполнены электроды первого набора электродов.

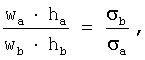

Применительно к данному варианту представляется желательным, чтобы электропроводные материалы, из которых выполнены электроды первого и второго наборов электродов, обладали электрическими проводимостями σа и σb соответственно, удовлетворяющими соотношению:

обеспечивающему одинаковость электропроводных свойств электродов первого и второго наборов электродов.

При этом предпочтительно, чтобы в электродной решетке по изобретению изолирующие стенки между электродами первого набора электродов и электродами второго набора электродов составляли части тонкой пленки изолирующего материала, нанесенной в виде протяженного слоя, покрывающего электроды первого набора электродов, а также подложку в промежутках между электродами первого набора электродов. В данном случае электроды второго набора электродов образованы в углублениях между указанными стенками и расположены над частями тонкой пленки, покрывающими подложку. В то же время верхние поверхности электродов второго набора электродов находятся в одной плоскости с поверхностью части изолирующей тонкой пленки, покрывающей верхнюю поверхность электродов первого набора. Электроды первого и второго наборов электродов имеют равные высоты hb=ha, a электродные слои, содержащие электроды и изолирующую тонкую пленку, образуют цельный планарный слой в составе электродной решетки.

Согласно еще одному предпочтительному варианту выполнения электродной решетки изолирующие стенки между электродами первого набора электродов и электродами второго набора электродов составляют части тонкой пленки изолирующего материала, нанесенной в виде слоя, покрывающего боковые края электродов первого набора электродов вплоть до их верхних поверхностей, а также подложку в промежутках между электродами первого набора электродов. Электроды второго набора электродов образованы в углублениях между указанными стенками и расположены над частями тонкой пленки, покрывающими подложку. При этом верхние поверхности электродов второго набора электродов находятся в одной плоскости с верхними кромками изолирующих стенок и с верхними поверхностями электродов первого набора электродов. Электроды второго набора электродов в данном случае имеют высоту hb=ha-δ, а электродные слои, содержащие электроды и изолирующую тонкую пленку, образуют цельный планарный слой толщиной ha в составе электродной решетки.

В следующем предпочтительном варианте выполнения электродной решетки изолирующие стенки между электродами первого набора электродов и электродами второго набора электродов составляют части тонкой пленки изолирующего материала, нанесенной в виде слоя, покрывающего электроды первого набора электродов, вплоть до подложки. Электроды второго набора электродов образованы в углублениях между указанными стенками и расположены непосредственно на подложке, причем верхние поверхности электродов второго набора электродов находятся в одной плоскости с поверхностью части изолирующей тонкой пленки, покрывающей верхнюю поверхность электродов первого набора электродов. В данном случае электроды первого набора электродов имеют высоту ha=hb-δ, а электродные слои, содержащие электроды и изолирующую тонкую пленку, образуют цельный планарный слой толщиной hb в составе электродной решетки.

Вышеперечисленные задачи, а также дополнительные преимущества и свойства реализуются в соответствии с настоящим изобретением также за счет разработки способа изготовления электродного слоя в составе электродной решетки. Способ по изобретению характеризуется тем, что включает операции нанесения на подложку планарного слоя электропроводного материала толщиной ha и профилирования планарного слоя электропроводного материала с формированием первого набора полосковых электродов шириной wa и высотой ha, пространственно отделенных друг от друга углублениями, образованными при осуществлении профилирования. Операция профилирования в этом случае включает удаление частей электропроводного материала, делая тем самым открытой поверхность подложки между полосковыми электродами первого набора электродов. В результате электроды первого набора электродов оказываются расположенными друг от друга на расстоянии а, равном ширине углублений между указанными электродами, а также равном или превышающем значение wa.

Далее способ по изобретению включает операцию формирования тонкой пленки изолирующего материала, покрывающей, по меньшей мере, боковые края электродов первого набора электродов, а также операцию нанесения электропроводного материала в углубления между частями тонкой пленки, покрывающими боковые края электродов первого набора электродов. При этом имеет место формирование второго набора электродов, имеющих ширину wb и высоту hb, с образованием электродного слоя в виде цельного планарного слоя в составе электродной решетки.

Предпочтительный вариант осуществления способа по изобретению включает формирование изолирующей тонкой пленки в виде цельного слоя, покрывающего как электроды первого набора электродов, так и открытую поверхность подложки. Данный вариант включает также нанесение электропроводного материала для образования второго набора электродов в углубления между электродами первого набора электродов и поверх изолирующей тонкой пленки и осуществление планаризации электродного слоя таким образом, чтобы верхняя поверхность электродов второго набора электродов находилась на одном уровне с изолирующей тонкой пленкой, покрывающей электроды первого набора электродов.

Согласно другому предпочтительному варианту способ по изобретению включает формирование изолирующей тонкой пленки в виде цельного слоя, покрывающего электроды первого набора электродов и открытую поверхность подложки, а также нанесение электропроводного материала для образования второго набора электродов в углубления между электродами первого набора электродов и поверх изолирующей тонкой пленки. Способ включает далее осуществление планаризации электродного слоя таким образом, чтобы удалить изолирующую тонкую пленку с верхней поверхности электродов обоих наборов, открыв тем самым верхнюю поверхность электродов и обеспечив расположение верхних поверхностей электродов обоих наборов и верхних кромок изолирующей тонкой пленки на одном уровне, соответствующем верхней поверхности электродного слоя.

Согласно еще одному предпочтительному варианту способ по изобретению включает формирование изолирующей тонкой пленки в виде цельного слоя, покрывающего электроды первого набора электродов и открытую поверхность подложки, и удаление изолирующей тонкой пленки со дна углублений, открывая тем самым поверхность дна, но оставляя части изолирующей тонкой пленки, покрывающие электроды первого набора электродов вплоть до подложки. Предусматриваются также нанесение электропроводного материала для образования второго набора электродов в указанные углубления и осуществление планаризации электродного слоя. Планаризация проводится таким образом, чтобы обеспечить расположение верхних поверхностей электродов второго набора и поверхности изолирующей тонкой пленки, покрывающей электроды первого набора, на одном уровне, соответствующем верхней поверхности электродного слоя.

В соответствии с другим вариантом осуществления способ по изобретению включает нанесение цельного слоя функциональной среды, покрывающего один электродный слой, сформированный на подложке, и контактирующего с электродами данного электродного слоя, и последующее формирование второго электродного слоя непосредственно на цельном слое функциональной среды посредством операций, аналогичных операциям, использованным при формировании электродного слоя на подложке. Желательно после этого покрыть электродный слой, сформированный на цельном слое функциональной среды, подложкой или объединительной платой.

Далее, при осуществлении способа по изобретению в качестве материала электродов первого набора и/или подложки предпочтительно выбирают материал, пригодный для осуществления поверхностного оксидирования, и формируют изолирующую тонкую пленку посредством оксидирования поверхности, по меньшей мере, материала электродов или подложки посредством, по меньшей мере, одной операции оксидирования.

Вышеперечисленные задачи, а также дополнительные преимущества и свойства реализуются в рамках настоящего изобретения, кроме того, за счет создания устройства обработки и/или хранения данных, характеризующегося прежде всего тем, что электроды в составе электродной решетки расположены в соответствующих электродных слоях, имеют примерно одинаковую ширину w и изолированы друг от друга посредством изолирующей тонкой пленки толщиной δ, составляющей долю от ширины w. При этом минимальное значение w сопоставимо с минимальным технологически достижимым размером f. Коэффициент заполнения функциональной среды функциональными элементами близок к 1 при общем количестве функциональных элементов, близком к максимальному пределу, составляющему A/f2, т.е. определяемому общей площадью А поверхности функциональной среды, заключенной между электродными слоями, и указанным размером f.

Краткое описание чертежей

Настоящее изобретение станет лучше понятно из изучения, совместно с прилагаемыми чертежами, нижеследующего описания некоторых вариантов осуществления устройства и электродной решетки, а также способа ее изготовления.

Фиг.1а-1с иллюстрируют известное устройство с пассивной матричной адресацией, обладающее типичным коэффициентом заполнения, присущим устройством подобного типа, описанным выше.

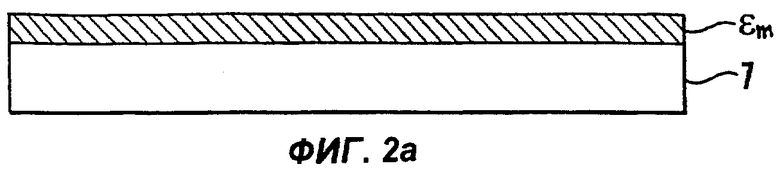

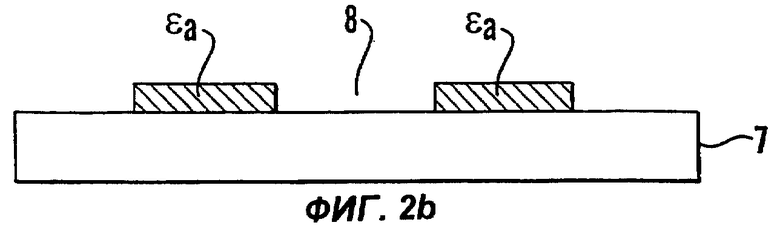

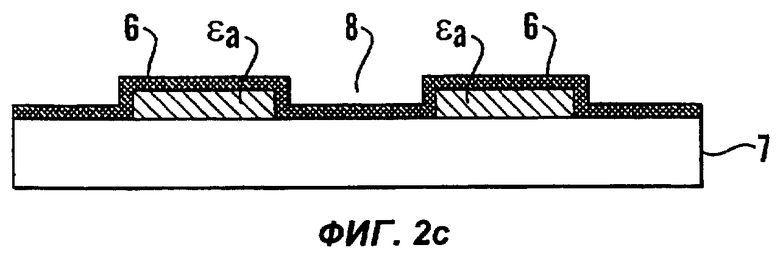

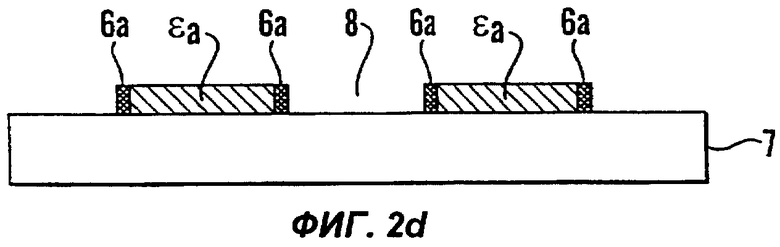

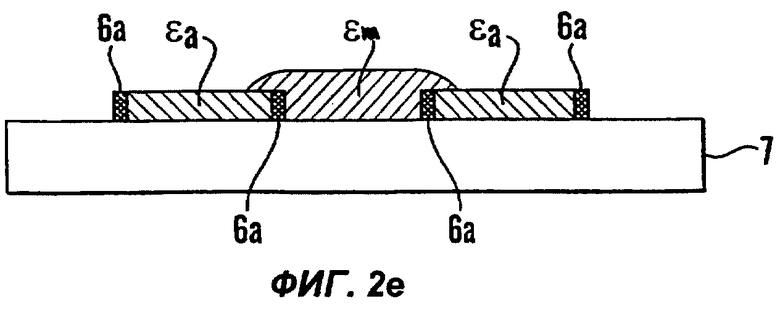

На фиг.2a-2f схематично иллюстрируются операции способа изготовления первого варианта электродного слоя согласно изобретению.

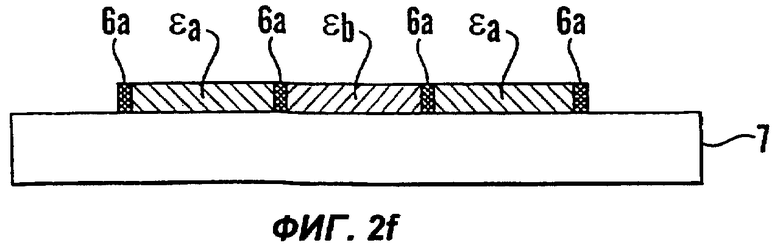

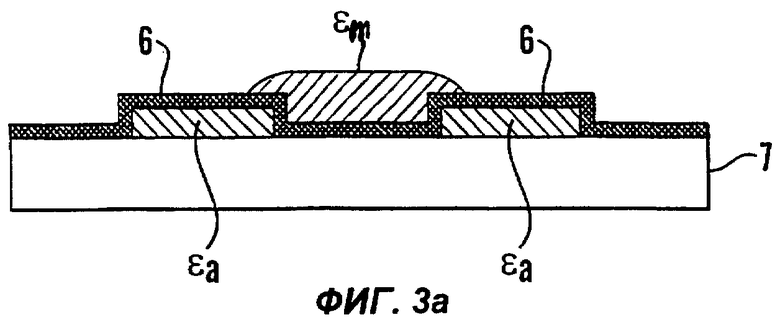

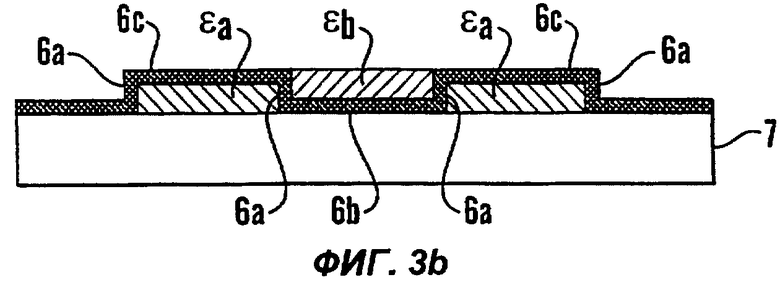

Фиг.3а и 3b схематично иллюстрируют операции, используемые при изготовлении второго варианта электродного слоя согласно изобретению после выполнения операции, соответствующей фиг.2с.

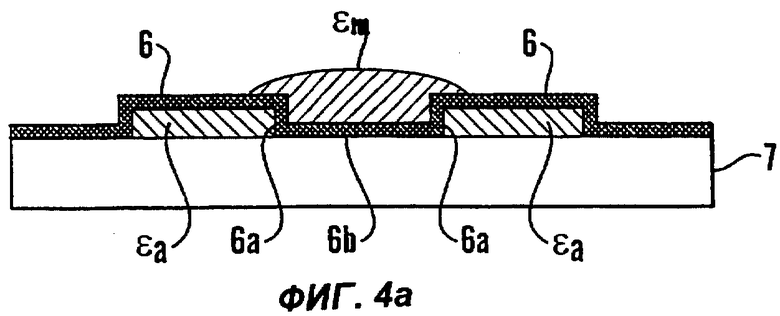

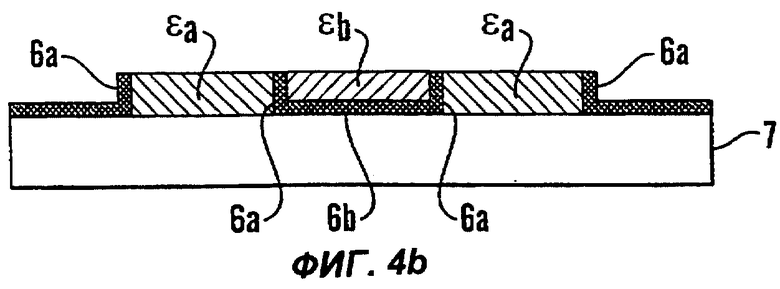

Фиг.4а и 4b схематично иллюстрируют операции, используемые при изготовлении третьего варианта электродного слоя согласно изобретению после выполнения операции, соответствующей фиг.2с.

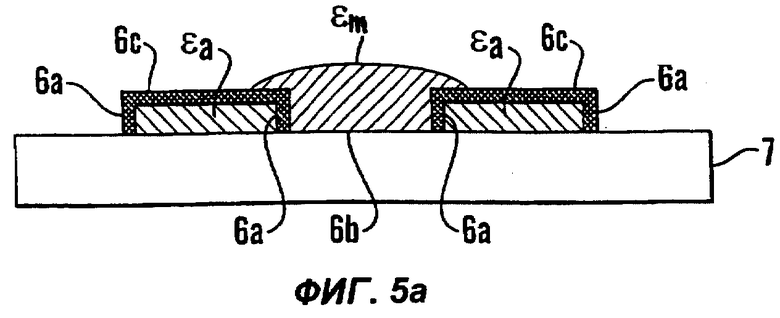

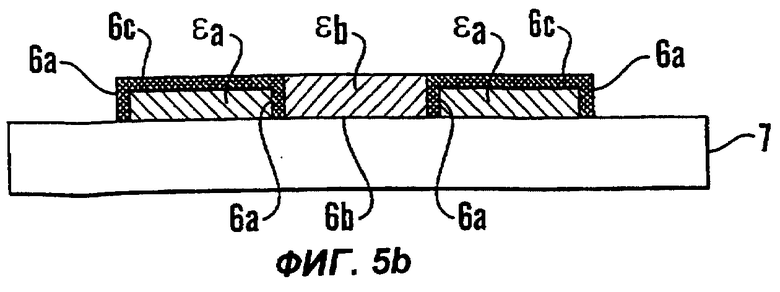

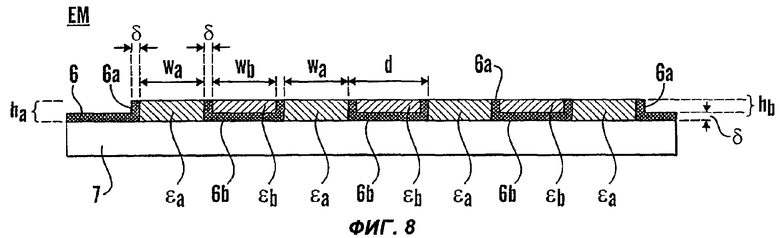

Фиг.5а и 5b схематично иллюстрируют операции, используемые при изготовлении четвертого варианта электродного слоя после выполнения операции, соответствующей фиг.2b или 2с.

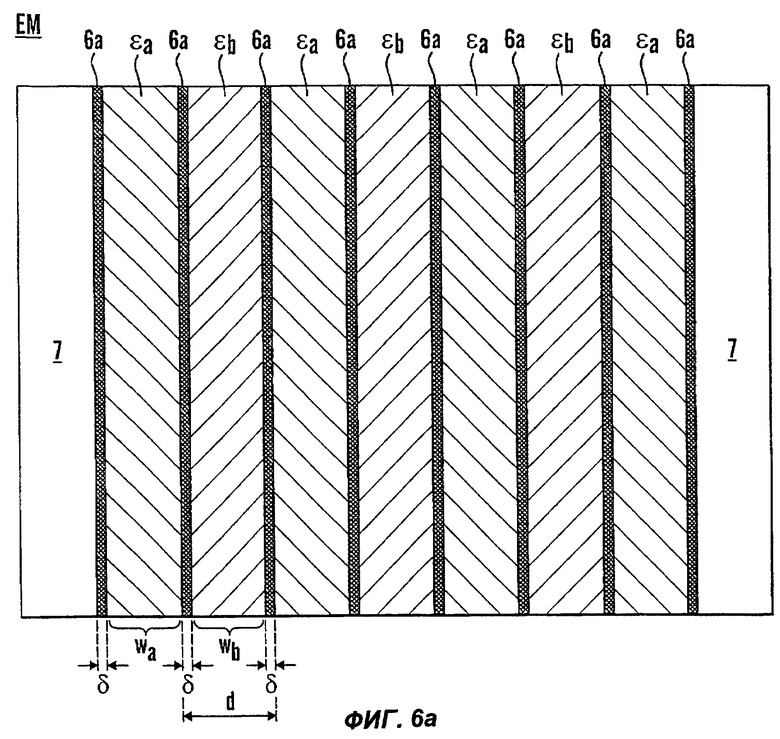

На фиг.6а, на виде сверху, схематично представлен вариант выполнения электродного слоя в электродной решетке согласно изобретению.

На фиг.6b вариант электродного слоя по фиг.6а схематично изображен в сечении.

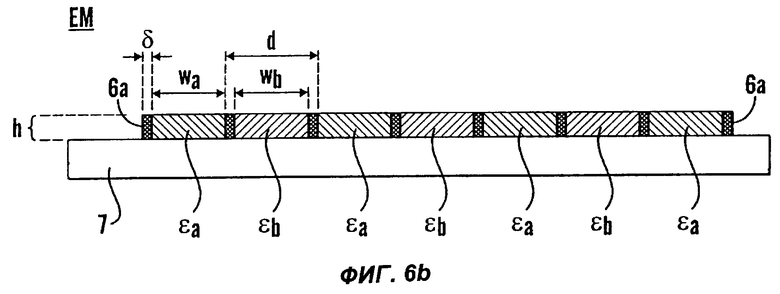

На фиг.7 схематично, в сечении, изображен другой вариант выполнения электродного слоя в электродной решетке согласно изобретению.

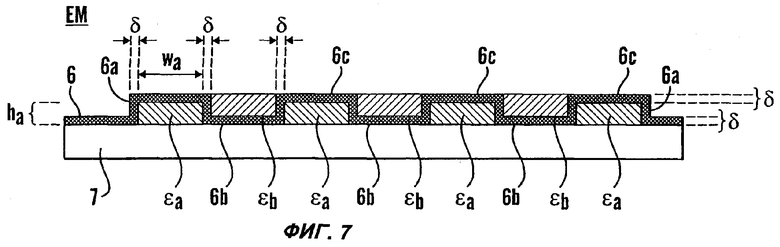

На фиг.8 схематично, в сечении, изображен третий вариант выполнения электродного слоя в электродной решетке согласно изобретению.

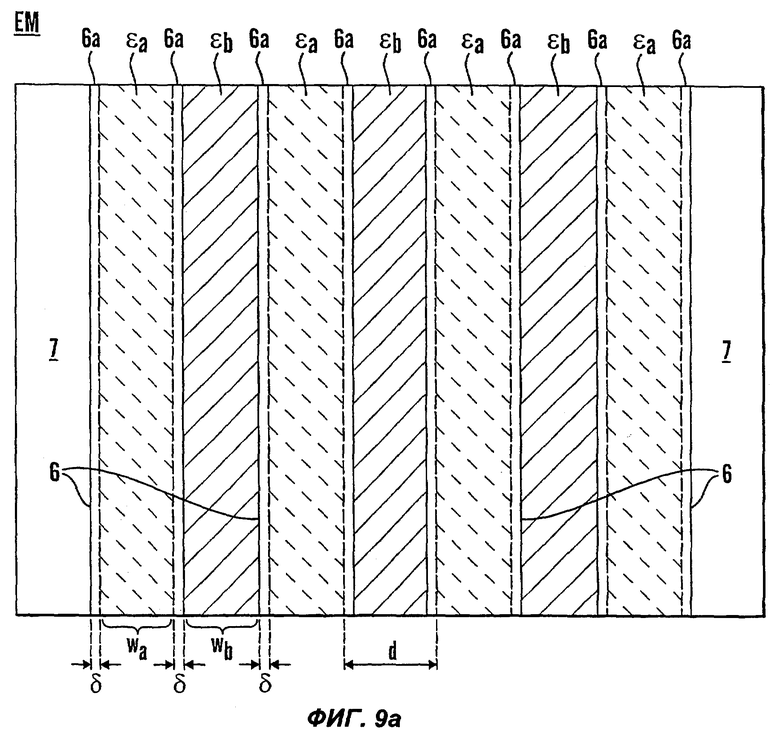

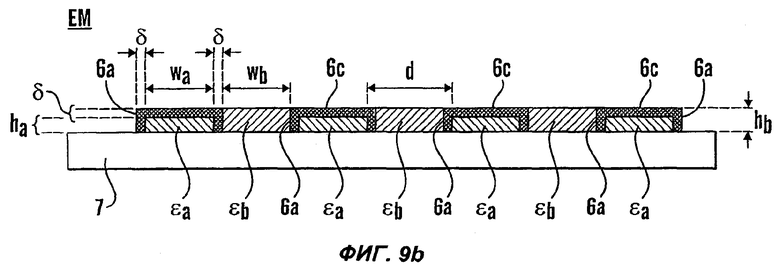

На фиг.9а, на виде сверху, схематично представлен четвертый вариант выполнения электродного слоя в электродной решетке согласно изобретению.

На фиг.9b вариант электродного слоя по фиг.9а схематично изображен в сечении.

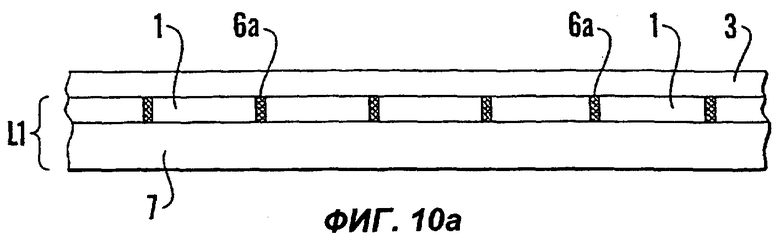

На фиг.10а в сечении представлен вариант выполнения первого электродного слоя, который покрыт цельным слоем функциональной среды, в составе электродной решетки согласно изобретению.

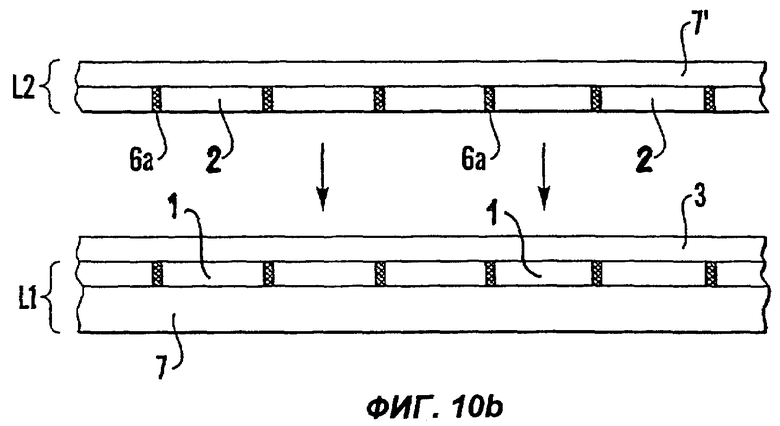

На фиг.10b показан второй электродный слой, выполненный аналогично первому электродному слою, и установленный в положение, соответствующее формированию электродной решетки по изобретению.

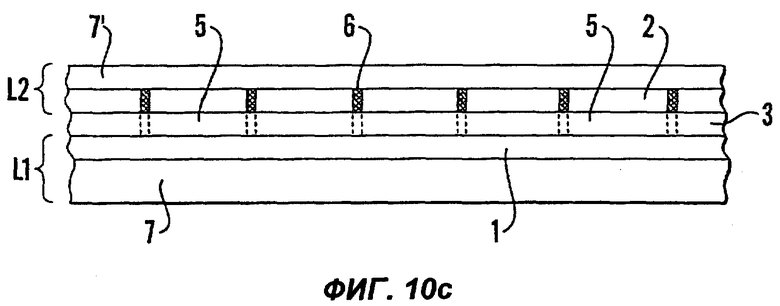

На фиг.10с представлен предпочтительный вариант электродной решетки по изобретению.

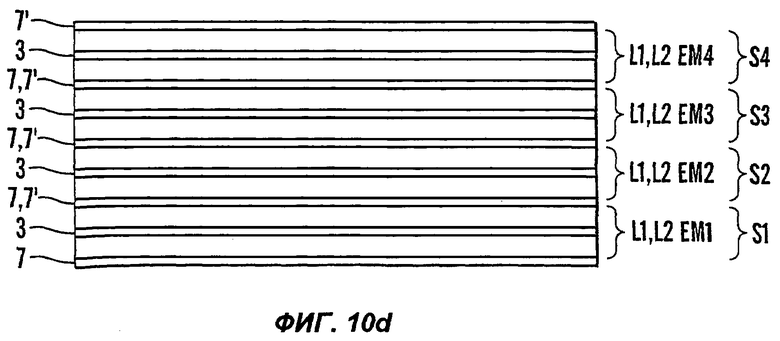

На фиг.10d показано, как множество электродных решеток может быть собрано в стопу с образованием объемного устройства.

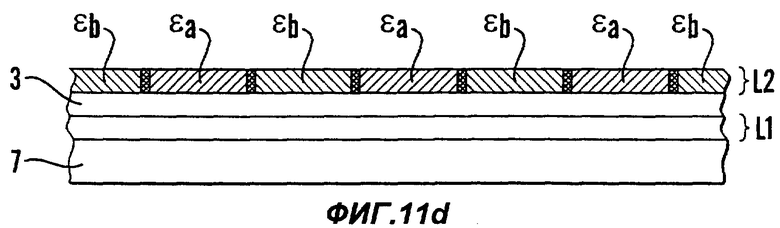

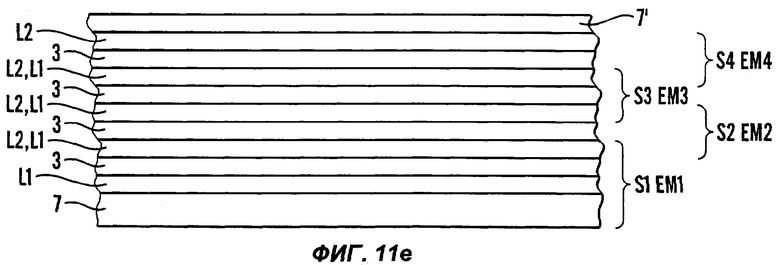

Фиг.11a-11d схематично иллюстрируют операции, используемые при изготовлении еще одного варианта электродной решетки согласно изобретению.

На фиг.11е показано, как множество электродных решеток согласно данному варианту может быть собрано в стопу с образованием объемного устройства.

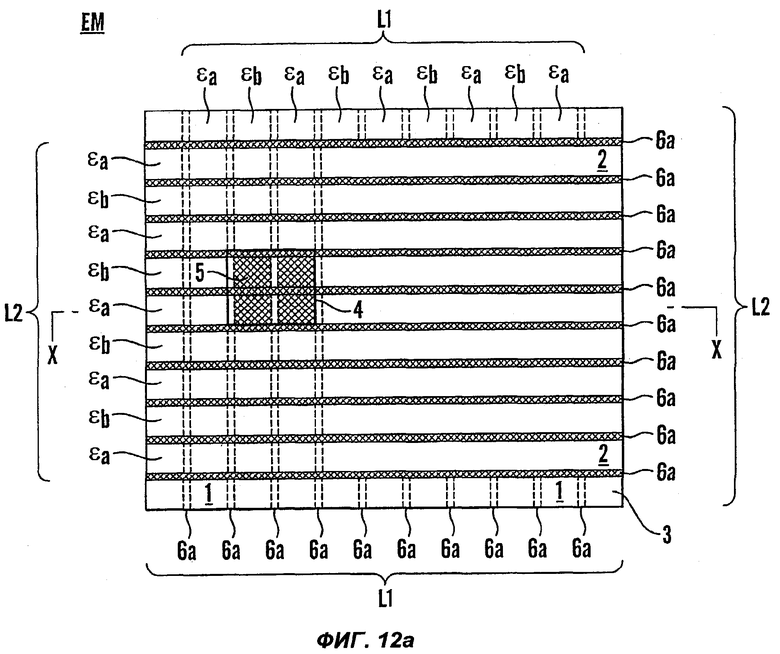

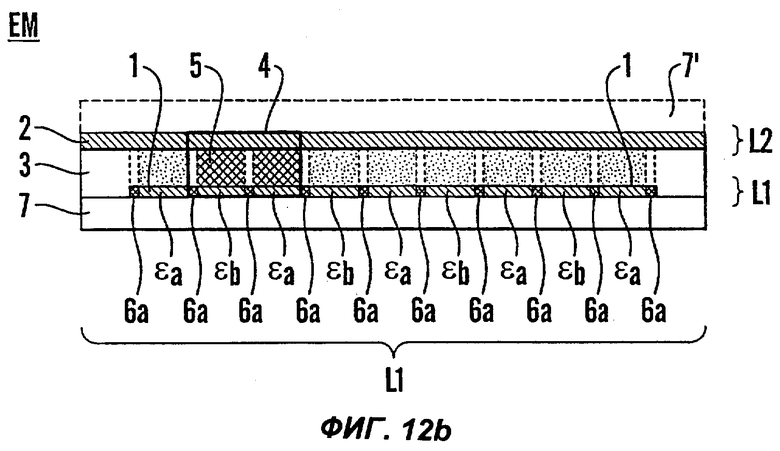

На фиг.12а, на виде сверху, изображено устройство с матричной адресацией, соответствующее настоящему изобретению, снабженное электродной решеткой по изобретению.

Фиг.12b соответствует сечению устройства по фиг.12а плоскостью Х-Х.

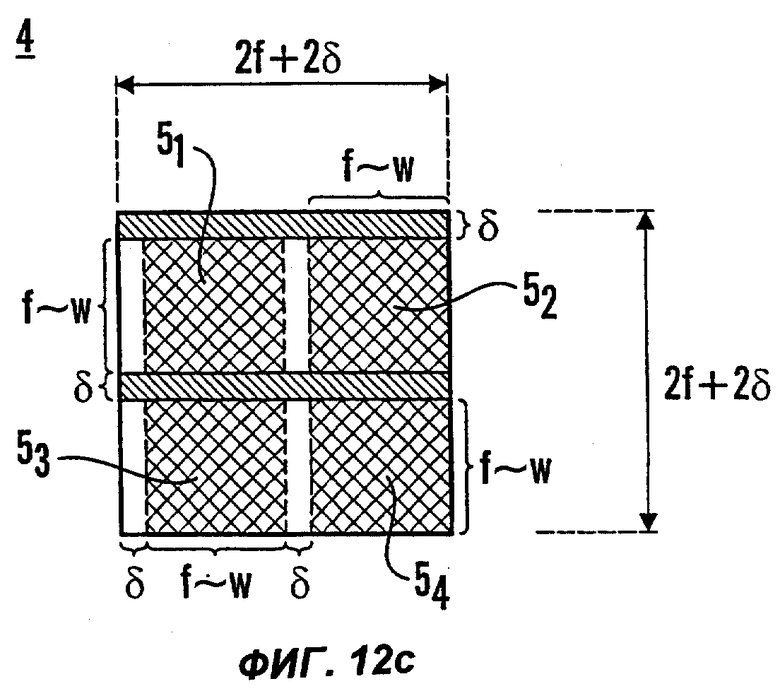

На фиг.12с представлена часть устройства по фиг.12а, иллюстрирующая коэффициент заполнения, достижимый с помощью настоящего изобретения.

Осуществление изобретения

Далее будет подробно описана электродная решетка по настоящему изобретению. При этом будут даны ссылки на фиг.2-5, иллюстрирующие различные варианты изготовления электродного слоя в данной электродной решетке. Необходимо учитывать, что названные фигуры являются весьма схематичными: в частности, на них показано лишь минимальное количество электродов, достаточное для пояснения производственных операций и структуры электродного слоя в электродной решетке по изобретению.

В соответствии с изобретением электродная решетка содержит два однотипных электродных слоя L1, L2, электроды ε которых обращены к цельному (единому) слою 3 функциональной среды, расположенной между электродными слоями и находящейся в контакте с электродами этих слоев. Второй электродный слой L2, разумеется, может быть сформирован путем аналогичных операций. При этом должен быть соответствующим образом расположен относительно первого электродного слоя L1 и слоя 3 функциональной среды, как это будет более подробно объяснено далее со ссылками на предпочтительные примеры выполнения электродной решетки ЕМ. Далее будет описано также, каким образом электродные решетки могут быть собраны в стопу с целью создания объемной (трехмерной) структуры, содержащей множество электродных решеток по настоящему изобретению.

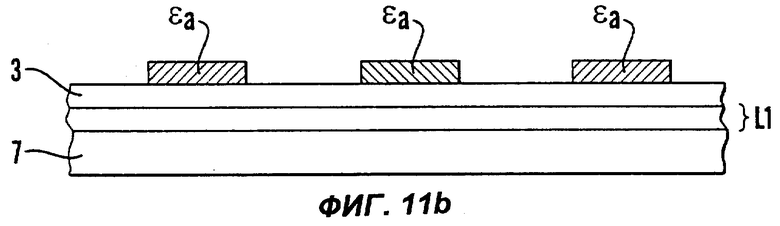

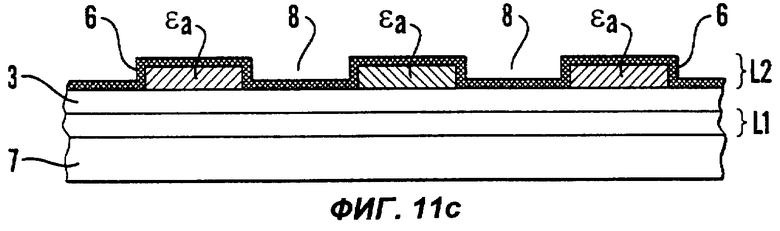

На фиг.2а показано, что на подложку 7 (которая может быть выполнена из любого подходящего материала при обязательном условии, что он должен иметь, по меньшей мере, одну поверхность с изоляционными свойствами) наносится слой электропроводного материала εm. В рассматриваемом случае слой материала εm наносится на поверхность подложки 7, обладающую изоляционными свойствами. На второй операции, которая иллюстрируется фиг.2b, из слоя электропроводного материала εm в соответствии с заданным рисунком посредством операции профилирования формируются электроды εa, образующие первый набор Еа электродов, расположенных на расстоянии d друг от друга. При этом между электродами εa образуются углубления 8. Должно быть понятно, что ширина w электродов εа, обеспечиваемая на операции профилирования, ограничивается минимальным размером f, достижимым в используемой технологии. Например, при использовании обычной технологии фотомикролитографии с применением фотомасок и с последующим травлением значение f может быть доведено до 0,15 мкм или даже менее. При этом данный размер будет предельным как для минимальной ширины электродов εа, так и для расстояния d между ними.

На третьей производственной операции, которая иллюстрируется фиг.2с, полосковые электроды εa и открытые части подложки 7 покрывают тонкой пленкой 6 изолирующего материала, напыленной или сформированной с использованием любого иного подходящего процесса, например, путем химического осаждения из паров, распыления и т.д. Как это хорошо известно специалистам в данной отрасли, изолирующий слой на основе пленки 6 может быть сделан предельно тонким, например, составляющим несколько нанометров, т.е. его толщина δ будет очень малой по сравнению с шириной wa электродов εа.

На четвертой производственной операции, которая иллюстрируется фиг.2d, производят удаление изолирующего слоя 6, покрывающего электроды εа и подложку 7. Для удаления данного слоя 6 можно применить процесс, отличный от процесса, использованного при профилировании электродов εа. Альтернативно, можно применить сочетание соответствующих процессов. Так, обычно предпочтительным является использование фотомикролитографии с последующим травлением. В этом случае, как и на операции, представленной на фиг.2b, могут быть использованы соответствующие фотомаски, согласованные с шириной wa электродов εа и учитывающие значение расстояния d, соответствующего углублениям между данными электродами. По завершении четвертой операции получают структуру, представленную на фиг.2d. Единственными частями 6а, которые остаются покрытыми слоем тонкой пленки 6, являются боковые края полосковых электродов εa.

На пятой производственной операции, которая иллюстрируется фиг.2е, в углубления 8 между электродами εa вводят другой электропроводный материал, который в общем случае может быть тем же материалом εm, который был использован для получения первого набора Еа электродов. Разумеется, данный электропроводный материал εm может быть нанесен в виде единого слоя, покрывающего как электроды εа, так и углубления 8. Однако в изображенном варианте данный материал наносится, в основном, только в пределах углублений 8. Нанесение данного материала может быть осуществлено аналогично нанесению слоя электропроводного материала, проиллюстрированному фиг.2а, например, осаждением из паровой фазы, распылением и т.д.

В заключение, на фиг.2f изображена операция планаризации, на которой удаляют электропроводный материал εm до получения высоты (толщины) слоя, соответствующей высоте изолирующих стенок 6а. В результате формируются полосковые электроды εb, образующие второй набор Еb электродов, каждый из которых расположен между электродами εа, образующими первый набор Еа электродов. При этом электроды εa изолированы от электродов εb с помощью изолирующих стенок 6а, соответствующих частям тонкой пленки 6. Углубления 8 при этом можно рассматривать и как формы, в которые вводится электропроводный материал ε посредством соответствующего литьевого процесса.

Электродный слой для использования в составе электродной решетки согласно изобретению, полученный описанным образом и схематично представленный на фиг.2f, показан также на виде сверху на фиг.6а. Изображенный на этой фигуре электродный слой L содержит множество взаимно параллельных полосковых электродов εa, εb, находящихся на подложке 7. Электроды εа могут рассматриваться как принадлежащие первому набору Еа электродов, сформированных на операции профилирования (см. фиг.2b), тогда как расположенные между ними электроды εb могут рассматриваться как принадлежащие второму набору Еb электродов, сформированных на операциях, представленных на фиг.2е, 2f. При этом расстояние между электродами εа равно d, ширина электродов εа равна wa, а ширина электродов εb равна wb. Величины wa, wb и d будут взаимно сопоставимыми и будут иметь примерно одинаковые значения. Эти значения близки к минимальному достижимому размеру f, обусловленному характеристиками процесса профилирования, который был использован для получения структуры, показанной на фиг.2b.

В то же время толщина δ изолирующих стенок 6а между электродами εb, εа не ограничивается параметром f и может находиться в диапазоне нанометров. Единственное ограничение при выборе δ состоит в том, что она должна быть достаточной, чтобы предотвращать электрические дефекты и пробои между электродами εа, εb. Другими словами, при условии, что поверхность подложки 7, связывающей электроды, также является электрически изолирующей, все параллельные полосковые электроды εа, εb будут электрически изолированы друг от друга. Представленный на фиг.6b вид, соответствующий сечению электродной решетки по фиг.6а, не требует дополнительных пояснений. Можно лишь отметить, что высота электродов εа, εb, а также изолирующих стенок 6а, равна h, и, кроме того, выполняется соотношение d=wb+2δ. При условии, что расстояние d между электродами εа задано, как wa+2δ, электроды εа, εb будут иметь одинаковую ширину w, так что все электроды εа, εb будут иметь одинаковое поперечное сечение, а также одинаковую проводимость (при условии, что все они выполнены из одинакового материала εm).

Преимущества электродных решеток ЕМ, выполненных на основе электродных слоев L в отношении достигаемых значений коэффициента заполнения, будут рассмотрены далее при рассмотрении устройства по изобретению, представленного на фиг.10а.

Фиг.3а и 3b иллюстрируют операции, используемые при изготовлении второго варианта электродного слоя L в составе электродной решетки по изобретению. Операции, соответствующие фиг.3а, начинают выполняться над структурой, представленной на фиг.2с, т.е. после нанесения изолирующей тонкой пленки 6. Как показано на фиг.3а, электропроводный материал εm, который и в данном случае может быть таким же, что и материал, использованный для электродов εа, вводят в углубления 8 (см. фиг.2с) с помощью любого подходящего для этого процесса, после чего выполняют операцию планаризации с получением структуры, показанной на фиг.3b. Эта структура соответствует второму варианту электродного слоя L в соответствии с изобретением. В данном варианте электроды εа первого набора покрыты изолирующей тонкой пленкой 6, участки которой формируют стенки 6а вдоль боковых краев электродов εа. Участки 6с тонкой пленки 6 расположены на верхней поверхности электродов εa, а участки 6b - на дне углублений 8. Эти участки покрыты электропроводным материалом εm, который на заключительной операции подвергают обработке для получения электродов εb, образующих второй набор Еb электродов, верхние поверхности которых расположены на одном уровне с участками 6с изолирующей тонкой пленки 6, покрывающими электроды εа.

Данный вариант представлен в сечении на фиг.7. Следует отметить, что электроды εa не будут находиться в омическом контакте с любым электропроводным материалом, который может находиться над этими электродами. Однако тонкая пленка 6 не препятствует емкостной связи между электродами εb и электропроводным материалом. Таким образом, данный вариант выполнения электродного слоя L согласно изобретению предназначен для приложений, в которых применительно к электродам εa, εb требуется установление только емкостной связи. Следует также отметить, что высота hb электродов εb меньше, чем высота ha электродов εа на величину, соответствующую толщине δ тонкой пленки 6. Для того чтобы получить одинаковое поперечное сечение для всех электродов εа, εb, ширина wb электродов εb должна быть соответственно увеличена из расчета того, что после операции планаризации, в результате которой верхняя поверхность электродов εb лежит на одном уровне с участками 6с тонкой пленки 6, значение hb равно ha-δ (см. фиг.7).

Фиг.4а и 4b иллюстрируют операции, используемые при изготовлении третьего варианта электродного слоя L в составе электродной решетки по изобретению. Операции, соответствующие фиг.4а, начинают выполняться над структурой, представленной на фиг.2с, т.е. после того, как подложка 7 и электроды εа будут покрыты тонкой пленкой 6. Далее для формирования электродов εb наносят электропроводный материал εm, заполняя и покрывая углубления 8 (см. фиг.2с) с получением структуры, изображенной на фиг.4а. Разумеется, как и в предыдущих вариантах, электропроводный материал ε может быть таким же, что и материал, использованный для электродов εа. Затем осуществляют операцию планаризации, в ходе которой удаляют участки тонкой пленки 6, покрывающей электроды εа, а также избыток материала εm, из которого сформированы электроды. При этом, как это видно из фиг.4b, поверхности электродов εа, εb, совпадающие с поверхностью электродного слоя, расположены на одном уровне, совпадающем с уровнем верхних кромок изолирующих стенок 6а, представляющих собой участки тонкой пленки 6.

Данный третий вариант выполнения в сечении представлен на фиг.8, из которой можно видеть, что поверхности электродов εа, εb открыты, т.е. эти электроды пригодны для осуществления как емкостной, так и омической связи с соответствующими контактами или с расположенным над ними функциональным материалом. Ограничения, относящиеся к минимальным значениям ширины wа, wb электродов εа, εb, применимы и к данному варианту. Далее, можно видеть, что высота ha электродов εa отличается от высоты hb электродов εb на величину δ, соответствующую толщине изолирующих стенок 6а, образованных участками тонкой пленки 6. Аналогично предыдущему случаю, это означает, что расстояние d между электродами εа при выполнении операции профилирования должно быть увеличено для того, чтобы получить электроды εа, εb с одинаковым поперечным сечением (если это представляется желательным, например, для обеспечения одинаковой проводимости электродов, изготовленных из одного материала или из материалов с одинаковой проводимостью). Планаризация может быть легко осуществлена с использованием любых подходящих технологий, например, используя химико-механическое полирование, управляемое травление или управляемый микроабразивный процесс.

Фиг.5а и 5b иллюстрируют операции, используемые при изготовлении четвертого варианта электродного слоя L, которые начинают выполняться над структурой по фиг.2b или 2с. Если исходной является структура по фиг.2b, это означает, что электроды εа изготовлены из электропроводного материала, обладающего соответствующими свойствами, например из титана или алюминия. В этом случае они могут быть подвергнуты селективному оксидированию (окислению) с образованием изолирующей тонкой пленки 6, покрывающей электроды, включая их боковые края, с образованием изолирующих стенок 6а, и их верхние поверхности, с образованием участков 6с тонкой пленки, как это показано на фиг.5а. Однако процесс, который иллюстрируется фиг.5а, может начинаться и с использованием структуры, показанной на фиг.2с. Это означает, что изолирующая тонкая пленка 6 должна быть удалена путем травления на тех участках, где она покрывает подложку, т.е. в углублениях 8, оставляя тонкую пленку только на электродах εа, т.е. на участках 6а, 6с. Однако подобный процесс требует применения второй операции маскирования, что ведет к повышению стоимости процесса.

Используя селективное оксидирование электродов εа перед нанесением материала εm, предназначенного для образования электродов εb, можно реализовать намного более дешевый способ формирования изолирующей тонкой пленки 6, покрывающей электроды εa. Затем в углубления 8 между электродами εa наносят электропроводный материал εm, который, разумеется, изолирован от электродов εa, как это было описано раньше, с помощью изолирующих стенок 6а. Затем, как видно из фиг.5b, выполняют планаризацию с удалением избытка электропроводного материала εm для формирования электродов εb в углублениях 8 между изолирующими стенками 6а. В этом варианте электроды εb, как показано на фиг.5b, покрывают изолирующую поверхность подложки 7 и находятся в прямом контакте с ней.

Рассмотренный четвертый вариант соответствует электродному слою, представленному на виде сверху на фиг.9а и в сечении на фиг.9b. Из этих фигур можно видеть, что электроды εa имеют высоту ha, тогда как электроды εb имеют высоту hb, отличную от высоты ha. Площади поперечного сечения электродов εа, εb будут составлять соответственно wa·ha и wb·hb. Отсюда следует, что для получения электродов εa, εb с одинаковой шириной wa=wb=w необходимо обеспечить соответствующее расстояние d между электродами εa первого набора Еа электродов при выполнении операции профилирования, которая иллюстрируется фиг.2b. Поскольку участки 6с тонкой пленки 6 покрывают в данном варианте верхние поверхности электродов εа, представленный четвертый вариант электродного слоя L, очевидно, ограничен использованием только емкостной связи с любым контактирующим с ним материалом, нанесенным сверху на данный слой. На виде сверху электродный слой по фиг.9а похож на аналогичный слой в варианте по фиг.6а, за исключением того, что электроды εа в первом из этих слоев покрыты участками 6с изолирующей тонкой пленки 6.

Как уже упоминалось, изолирующая тонкая пленка 6 может наноситься любым подходящим для этого методом, например путем химического осаждения из паров, а также распылением соответствующих веществ в жидкой или твердой фазах. Однако если материал εm, применяемый для изготовления электродов, может быть окислен, изолирующая тонкая пленка может быть сформирована, например, методом термического оксидирования с образованием структуры, показанной на фиг.2с. Данный метод будет применим, например, в случае, когда материал электродов наносят методом металлизации с использованием металлов типа титана, алюминия или меди, которые обычно применяют в электронной промышленности в качестве материалов электродов. Если при этом подложка 7 выполнена из кремния, ее поверхность в зонах, не закрытых электродами εа, может быть одновременно подвергнута оксидированию с целью сформировать на ней изолирующий слой SiO2. Альтернативно, как уже упоминалось, изолирующие участки тонкой пленки могут быть сформированы, как это показано на фиг.5а, путем селективного оксидирования электродов εа до того, как в углубления между этими электродами будет введен электропроводный металл. Соответствующие методы селективного оксидирования хорошо известны специалистам и поэтому не будут рассматриваться в данном описании.

На фиг.10а в сечении представлен вариант выполнения первого электродного слоя L1 в составе электродной решетки согласно изобретению. Электродный слой L1 покрыт цельным слоем функциональной среды, покрывающим электроды 1 и находящимся в контакте с ними. На фиг.10b показан второй слой электродной решетки L2; электроды этого слоя расположены на подложке 7', которая соответствует подложке 7 первого электродного слоя L1. Второй электродный слой, разумеется, во всех аспектах аналогичен первому электродному слою. Оба электродных слоя соединяются вместе с образованием составной электродной решетки ЕМ в соответствии с настоящим изобретением, которая, в дополнение ко второму электродному слою, содержит первый электродный слой L1 и единый слой функциональной среды. Полученная составная электродная решетка в собранном виде показана в сечении на фиг.10с. Однако здесь первый электродный слой L1 развернут на 90°, а второй электродный слой L2 ориентирован таким образом, что его электроды 2 скрещены, т.е. ортогональны электродам 1 первого электродного слоя L1.

Результирующая структура представляет собой плотную электродную матрицу, находящуюся в контакте с цельным слоем функциональной среды, в пределах которого в зонах скрещивания (наложения) электродов 1, 2, принадлежащих соответственно первому и второму электродным слоям L1, L2, задаются соответствующие функциональные элементы. Структура составной электродной решетки в виде электродной матрицы обеспечивает возможность матричной адресации функциональных элементов в составе цельного слоя функциональной среды, например, путем подачи напряжения на выбранный электрод 1 первого электродного слоя L1 и на выбранный электрод 2 второго электродного слоя L2. В результате в зоне взаимного наложения этих электродов к функциональной среде 3 прикладывается напряжение (разность потенциалов). Тем самым в адресуемом функциональном элементе индуцируется изменение физического параметра, например, в виде изменения его импеданса.

Если функциональная среда представляет собой поляризуемый ферроэлектрический или электретный материал, то, как это было описано ранее, устройство, представленное на фиг.10с, может рассматриваться в качества запоминающего устройства с пассивной матричной адресацией. В данном случае подача напряжений на соответствующие электроды первого и второго электродных слоев будет поляризовать функциональный элемент 5, расположенный между скрещивающимися электродами 1, 2. Таким образом, функциональный элемент 5 будет представлять собой ячейку памяти в ферроэлектрическом или электретном запоминающем устройстве.

Специалистам соответствующей отрасли должно быть понятно, что для осуществления драйверных и управляющих функций в связи с операциями адресации к ячейкам памяти, когда функциональная среда представляет собой запоминающий материал, электроды должны быть присоединены к периферийным драйверным контурам и к контурам управления. На фиг.10d показано, как множество устройств описанного типа, содержащих электродные решетки, могут быть собраны в стопу, в состав которой входят как электродные решетки, так и функциональная среда, и которая таким образом образует объемное (трехмерное) устройство. Легко видеть, что в устройстве подобного типа возможна индивидуальная параллельная адресация каждой электродной решетки при наличии соответственно подсоединенного периферийного контура.

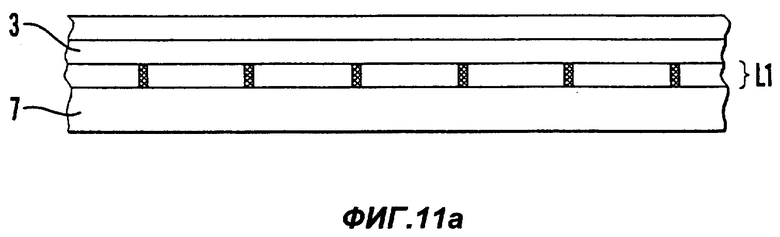

Второй вариант электродной решетки по настоящему изобретению иллюстрируется фиг.11a-11d, на которых поясняются различные этапы ее изготовления. На фиг.11а представлен вариант выполнения, в котором первый электродный слой L1 соответствует слою, показанному на фиг.2f и сформированному на подложке 7. При этом на первый электродный слой L1 нанесен цельный слой функциональной среды 3, находящийся в контакте с электродным слоем. Указанный цельный слой подвергнут планаризации, после чего он использован в качестве подложки для формирования на нем второго электродного слоя L2, как это показано на фиг.11b-11d. Процесс формирования второго электродного слоя повторяет операции, описанные ранее со ссылкой на фиг.2a-2f. Получаемый в результате второй электродный слой L2 не перекрывается объединительной платой. Вместо этого, он подвергается планаризации, после чего на него сверху наносят второй слой 3 функциональной среды, который служит подложкой для нанесения третьего электродного слоя L3. Описанный процесс далее может быть повторен, т.е. должно быть ясно, каким образом происходит формирование структуры в виде стопы, содержащей множество электродных решеток ЕМ (см. фиг.11е). Однако данный объемный вариант устройства с применением электродных решеток по изобретению отличается от варианта, представленного на фиг.10d тем, что второй электродный L2 первой электродной решетки EM1 теперь одновременно является первым электродным слоем L1 второй электродной решетки EM2 и т.д.

В результате в устройстве в виде стопы, содержащей n электродных решеток EM1-EMn, общее количество электродных слоев будет не 2n (как в случае, когда электродные решетки в составе устройства взаимно изолированы посредством подложек (или объединительных плат 7, 7'), а n+1. Тем самым будет уменьшен вертикальный размер (толщина) готовой структуры в случае реализации трехмерного варианта устройства. Однако в данном варианте только каждая вторая электродная решетка (например, первая, третья и т.д.) может быть адресована параллельно. Это ограничение обусловлено тем, что электродные слои, от второго до последнего слоя, способны контактировать со слоями функциональной среды 3, расположенными по обе стороны от электродного слоя.

Нанесение второго электродного слоя L2 непосредственно на функциональную среду может создать особые проблемы, когда материал функциональной среды представляет собой, например, органический материал с низкой температурой плавления, а электроды второго электродного слоя L2 должны представлять собой проводники из какого-либо неорганического (например, металлического) материала. В частности, в том случае, когда функциональная среда является ферроэлектрическим или электретным запоминающим материалом, изготовленным из полимера или сополимера, подобный материал будет иметь температуру плавления вблизи 200°С. В этом случае металлизация такого материала, т.е. нанесение непосредственно на него слоя металлического покрытия может привести к расплавлению материала в поверхностном слое. Кроме того, последующее травление на операции профилирования, выполняемой с целью формирования параллельных полосковых электродов, будет оказывать разрушительное воздействие на свойства материала рассматриваемого типа. Было, однако, обнаружено, что существует возможность нанесения металлизирующего слоя без создания недопустимо высоких термических напряжений в функциональной среде, например, в виде полимерного материала.

Оказалось, что различные варианты распыления из жидкой или твердой фазы, в частности, с применением для этой цели электронных или ионных пучков могут быть осуществлены в температурном диапазоне, совместимом с температурными ограничениями, которые должны соблюдаться в отношении функциональной среды. При этом особая осторожность должна соблюдаться на операции профилирования. В частности, ухудшения функциональных свойств материала, образующего функциональную среду, при осуществлении профилирования металлизирующего слоя с использованием ионных реакций можно избежать, если применять высокоселективные реагенты. Другими словами, оказывается возможным использовать слой функциональной среды 3 в качестве подложки для последующего нанесения и профилирования второго электродного слоя, даже если этот процесс включает в себя металлизацию и последующее травление слоя материала, использованного для формирования электродов второго электродного слоя L2.

Далее со ссылками на фиг.12а-12с будет описано устройство по настоящему изобретению, содержащее электродные решетки, выполненные согласно изобретению. Из этого описания будет понятно, каким образом данные электродные решетки позволяют достичь в устройстве по изобретению коэффициента заполнения, близкого к 1.

На фиг.12а, на виде сверху, представлен вариант выполнения устройства по изобретению, соответствующий устройству с пассивной матричной адресацией. Функциональная среда в виде цельного слоя расположена между двумя электродными слоями L1, L2, образующими электродную решетку ЕМ согласно изобретению. Первый электродный слой L1, который, в зависимости от свойств используемой функциональной среды, может соответствовать любому из вариантов, представленных на фиг.6-9, идентичен второму электродному слою L2. Однако, как показано на чертеже, параллельные полосковые электроды 2 второго электродного слоя ориентированы под углом (предпочтительно прямым) по отношению к соответствующим электродам 1 первого слоя. В зоне, соответствующей взаимному наложению пары электродов 1, 2, в расположенной между ними функциональной среде 3 задается функциональный элемент 5. Функциональный элемент 5 может состоять из полупроводникового неорганического или органического материала или из диэлектрического материала, способного к поляризации и обладающего гистерезисными свойствами. Таким материалом, например, может быть ферроэлектрический или электретный, причем предпочтительно органический материал в виде полимера или сополимера. В двух последних случаях должна использоваться емкостная связь, позволяющая применить варианты электродного слоя, показанные в сечении на фиг.7 или 9b.

Дальнейшее описание устройства по изобретению, в целях краткости изложения, будет ограничено вариантом, соответствующим устройству хранения данных, а именно ферроэлектрическому устройству хранения данных, предпочтительно с функциональной средой, выполненной из органического материала в форме полимера или сополимера. Однако варианты осуществления изобретения ни в коем случае не ограничены подобным устройством, причем его возможности должны быть очевидны специалистам существующей области. Кроме того, для упрощения понимания на фиг.12а не представлены никакие драйверные контура, а также контура считывания и управления. Однако в реальных вариантах осуществления они могут быть реализованы с применением КМОП-технологии на кремниевой основе. При этом они могут быть выполнены на объединительной плате 7, если она изготовлена из того же материала. В этом случае формирование и соединение электродов 1, 2 с названными контурами будут реализованы хорошо известными для специалистов методами.

Уже было упомянуто, что активный материал 3 расположен между электродными слоями L1, L2, как это наиболее наглядно показано на фиг.12b, соответствующей сечению устройства по фиг.12а плоскостью Х-Х. В зоне взаимного наложения (скрещивания) электродов 1, 2 в функциональной среде 3, представляющей собой, например, ферроэлектрический материал, задается функциональный элемент 5, а именно ячейка памяти. При приложении напряжения к электродам 1, 2, входящим в состав электродных слоев L1, L2 соответственно, функциональный материал в соответствующей ячейке 5 памяти способен переходить из исходного состояния в поляризованное. Поляризованное состояние ферроэлектрического запоминающего материала может быть выбрано для сохранения логического значения, причем знак (направление) поляризации может переключаться на противоположный (например, с + на -). Подобное переключение может происходить в ходе так называемого процесса деструктивного считывания, производимого с целью определить логическое состояние ячейки памяти (которое может соответствовать либо двоичному 0, либо двоичной 1). Однако считывание может и не быть деструктивным, т.е. логическое состояние ячейки памяти будет оставаться неизменным после завершения считывания. Этого можно достичь, например, при приложении к электродам 1, 2, задающим ячейки 5 памяти, такого напряжения, которое не приведет к переключению состояния поляризации этой ячейки.

В физических терминах взаимно налагающиеся электроды 1, 2 из электродных слоев L1, L2 в сочетании с заключенной между ними ферроэлектрической средой 3, образующей ячейку 5 памяти, можно рассматривать в качестве конденсаторной структуры. В связи с этим ферроэлектрические запоминающие устройства рассматриваемого типа классифицируются, как разновидность емкостного устройства хранения данных. При этом электроды εa, εb в каждом из слоев L1, L2 разделены только очень тонкой пленкой 6 изолирующего материала, имеющей толщину δ. Эта толщина δ составляет лишь очень малую долю ширины w электродов εa, εb, которая, скорее всего, соответствует минимальному технологически достижимому размеру f. Отсюда вытекает, что электродная решетка ЕМ согласно изобретению позволяет повысить коэффициент заполнения до значения, близкого к единице. Следует еще раз отметить, что в общем случае электроды εa, εb могут иметь различные значения своей ширины wa, wb. Однако, поскольку wa≅wb, то в реальных ситуациях можно считать, что они имеют одинаковую ширину w.

Преимущество от использования приведенных соотношений можно видеть при рассмотрении планарного участка 4, содержащего, как это показано на фиг.12с, четыре ячейки 51-54 памяти. Суммарная площадь участка, занимаемая изолирующими стенками 6а, находящимися между электродами и определяющими размеры ячеек 51-54 памяти, и самими электродами, входящими в состав электродных слоев L1, L2, описывается выражением 4f2+8fδ+4δ2. Отсюда следует, что поскольку в устройстве по изобретению δ составляет лишь малую часть значения размера f или ширины w электродов 1, 2, коэффициент заполнения в устройстве по изобретению близок к 100%. Другими словами, практически вся площадь функциональной среды 3, заключенной между электродными слоями L1, L2, будет занята ячейками 5 памяти, т.е. среднее значение площади поверхности ячейки памяти будет составлять f2. Например, если принять значение f≅w за 1, a δ=0,01f, общая площадь рассматриваемого участка будет составлять 4+8·0,01+0,0004≅4,08. Коэффициент заполнения будет соответственно равен 4/4,08=0,98, т.е. 98%.

Если площадь доступной поверхности активного материала 3 равна А, то максимальное количество ячеек 5 памяти в матрице устройства по изобретению будет близким A/f2. Например, если из конструктивных соображений значение f выбрано равным 0,2 мкм, а площадь А участка функциональной среды 3, на котором можно разместить ячейки 5 памяти, равняется 106 мкм2, общее количество адресуемых функциональных элементов, т.е. ячеек памяти, способных хранить по 1 биту, составит 0,98·106/0,2=24,5·106. Соответственно, плотность хранения данных будет около 25 Мбит/мм2. В известных же устройствах, в которых электроды отстоят друг от друга на расстояние d, определяемое значением минимального технологически достижимого размера f, такой же планарный участок 4, что и показанный на фиг.12а, будет содержать только одну ячейку 5 памяти, т.е. коэффициент заполнения будет равен 0,25 (т.е. 25%). Естественно, максимально достижимое количество ячеек памяти составит лишь четвертую часть от количества, которое может быть достигнуто в устройстве, использующем электродную решетку по настоящему изобретению.

Из изложенного следует, что устройство по настоящему изобретению, содержащее два электродных слоя L1, L2 и функциональную среду 3, расположенную между ними, будет иметь такую же емкость памяти, что и четыре аналогичных устройства, выполненные по обычной технологии и собранные в стопу с целью формирования объемного устройства хранения данных. Однако ничего не препятствует и сборке в стопу устройств типа показанных на фиг.12b, также с целью формирования объемного устройства хранения данных, обладающего высокой емкостью и высокой плотностью хранения данных. В этом случае поверх каждого электродного слоя L2 может быть помещена подложка 7', которая действует как разделительный и/или изолирующий слой между первым устройством стопы и смежным с ним устройством. Очевидно, что с помощью настоящего изобретения можно достичь тех же характеристик при использовании только одной четверти от общего количества устройств, собранных в стопу с формированием объемного устройства. Таким образом, можно будет избежать проблем, неизбежно возникающих при сборке в стопу большого количества устройств, что необходимо в случае применения традиционной технологии для получения такого же объема памяти.

Важно отметить, что процессы планаризации, применяемые на последней стадии формирования электродного слоя, могут выполняться с очень высокой точностью. Благодаря этому отклонение от плоскостности может быть сведено до уровня нанометров, даже в случае значительной площади поверхности электродной решетки по изобретению. Например, как уже упоминалось, для этой цели может быть применено химико-механическое полирование, позволяющее произвести финишную обработку без оставления каких-либо локальных дефектов или неровностей, ограничивающих возможности обычных электродных решеток, наносимых на функциональную среду посредством прямой металлизации.

Как следствие, в известных решениях нельзя избежать нарастания локальных неровностей по мере увеличения количества устройств, собираемых в стопу. Кроме того, использование изобретения позволяет избежать проблем, связанных с термическими или механическими напряжениями, возникающими при приложении напряжения для осуществления операций записи и считывания данных из ячеек функциональной среды в каждом отдельном запоминающем устройстве.

Применение электродных решеток ЕМ согласно изобретению ни в коей мере не ограничено устройствами хранения данных, хотя оно и придает особые преимущества устройствам этого типа, независимо от того, используется ли сборка их в стопу или нет. Общие сведения о конструкции и структуре подобных устройств, а также о различных материалах или комбинациях материалов для формирования функциональной среды, могут быть получены из уже упоминавшейся международной заявки WO 98/58383 (на изобретение, раскрытое в данной заявке, выданы патенты США №6055180 и РФ №2182732 С2, МПК G 11 C 11/21, 2002, принадлежащие заявителю настоящего изобретения). В указанных документах описаны варианты архитектуры для устройств обработки данных, в частности, запоминающих устройств, которые не ориентированы специально на ферроэлектрические запоминающие устройства. Кроме того, в них описаны и аналогичные варианты архитектуры, применимые, например, к дисплейным устройствам.

Что касается материалов для электродов применительно к электродным решеткам ЕМ по настоящему изобретению, предназначенных для различных устройств, включая запоминающие устройства, может быть использован любой подходящий материал, например, такие металлы, как титан или алюминий, которые широко применяются в электронной промышленности. Для изготовления электродов могут применяться и органические материалы, в частности электропроводные полимеры. Однако такие материалы должны быть совместимы с процессом, применяемым для формирования слоя изолирующей тонкой пленки, или с любым процессом, применяемым для удаления частей этой пленки.

Хотя должно быть понятно, что ширина w электродов электродного слоя ЕМ согласно изобретению будет иметь некоторое минимальное значение, определяемое минимальным технологически достижимым размером f, это ограничение, в первую очередь, касается ширины электродов εa первого набора электродов, которые должны изготавливаться с использованием профилирования, а также расстояния между этими электродами. Электроды εb могут наноситься с использованием процессов, которые не накладывают конструктивных ограничений, свойственных процессам профилирования. Это означает, что для таких электродов минимальные достижимые размеры могут быть существенно меньшими, чем размер f. То же самое, разумеется, относится и к нанесению изолирующей тонкой пленки, которое может производиться, например, путем оксидирования, осаждения из паров или распыления из жидкой или твердой фазы с получением размеров, соответствующих почти моноатомным слоям.

Единственное требование, которому должна удовлетворять данная пленка, - это создание необходимой электрической изоляции между смежными электродами εа и εb, входящими в соответствующие наборы Еа, Еb электродов в электродном слое L. В обычных фотолитографических технологиях значение f обычно лежит у 0,2 мкм или имеет несколько меньшее значение, причем в настоящее время идет освоение или разработка других технологий, соответствующих диапазону нанометров. Эти технологии, в частности, направлены на получение электродов с шириной порядка нескольких десятков нанометров, а также на использование химико-механического полирования в диапазоне нанометров для достижения необходимой планаризации, которая обеспечит высокую степень плоскостности верхней поверхности электродного слоя L при том, что все компоненты, т.е. электроды εа и εb, а также изолирующая тонкая пленка 6 будут находиться на одном уровне, соответствующем верхней поверхности электродного слоя L.

Итак, в общем случае использование электродных решеток в устройстве по настоящему изобретению, в котором функциональная среда расположена между двумя электродными слоями на основе параллельных полосковых электродов, расположенных под углом друг к другу (предпочтительно взаимно перпендикулярно) с образованием устройства с матричной адресацией, позволяет получить коэффициент заполнения, близкий к 1, и максимальное количество задаваемых функциональных элементов (т.е. ячеек). Количество этих элементов ограничивается только конструктивными ограничениями, накладываемыми технологическим процессом формирования заданного рисунка электродов.

Особенно привлекательной представляется возможность изготавливать электродные слои согласно изобретению в непрерывном процессе ("с рулона на рулон"), с получением отдельных электродных слоев путем разрезания непрерывной ленты с электродами в соответствии с требуемыми размерами. После этого на один из электродных слоев, со стороны расположения электродов можно нанести функциональную среду. Затем второй электродный слой, ориентированный таким образом, что его индивидуальные электроды перпендикулярны электродам первого электродного слоя, приводят в положение, в котором он связывается с функциональной средой, нанесенной на первый электродный слой. В результате формируется электродная решетка согласно изобретению, причем без необходимости наносить, по меньшей мере, электроды второго электродного слоя путем металлизации непосредственно поверхности функциональной среды. Как уже упоминалось, подобная операция может быть вредной для материала функциональной среды, особенно в случае, когда для создания ферроэлектрического устройства с матричной адресацией в качестве такой среды используют органические материалы, такие как полимеры или сополимеры.

Следует отметить, что описанный производственный процесс не может быть легко реализован применительно к активным устройствам с матричной адресацией. Вместе с тем, с учетом последних достижений в данной области устройства подобного типа представляются особенно привлекательными для построения ферроэлектрических устройств с матричной адресацией. Однако ферроэлектрические запоминающие устройства с активной матричной адресацией не только сами по себе являются более сложными и более энергоемкими, но даже в случае использования при их изготовлении электродных слоев согласно изобретению, их коэффициент заполнения будет существенно ниже 1. Например, применительно к активным ферроэлектрическим ячейкам типа 1Т, 1C (один транзистор, один конденсатор), предельно достижимый коэффициент заполнения не превысит 0,67.

В альтернативном варианте функциональную среду можно наносить на завершающей операции, после выполнения планаризации электродных решеток, в непрерывном режиме "с катушки на катушку", либо в условиях тщательно контролируемой толщины слоя, либо с повторной планаризацией. После этого отдельные электродные слои разрезают в соответствии с требуемыми размерами и взаимно ориентируют смежные электродные слои, которые связывают с функциональной средой в режиме in situ. В результате формируется электродная решетка в соответствии с изобретением. Данная процедура может быть повторена с целью создания объемного устройства хранения данных, содержащего множество электродных решеток, собираемых в стопу до достижения требуемого количества слоев, т.е. до построения устройства по настоящему изобретению в объемной конфигурации.

Электродные решетки, выполненные согласно изобретению, т.е. содержащие электродные слои с высокой степенью планаризации, позволяют также с высокой точностью контролировать размеры электродов, т.е. площади их поперечных сечений, которые должны быть одинаковыми для обеспечения однородности проводимости электродов. В свою очередь, данное требование связано с необходимостью подачи на каждый функциональный элемент в составе функциональной среды одной и той же разности потенциалов при необходимости приведения или поддержания данного элемента в состоянии, соответствующем требуемому импедансу (резистивному или емкостному). Кроме того, при реализации протоколов записи или считывания с подачей напряжений, которые составляют доли от напряжения переключения, например, ферроэлектрического запоминающего материала, достигается повышенная надежность. Одновременно становится возможным точный контроль потенциала покоя применительно к неактивным числовым (управляющим) шинам и разрядным шинам (шинам данных) в схемах с пассивной матричной адресацией. Благодаря этому устраняются паразитные емкостные связи и помехи, наводимые на неадресуемые ячейки памяти в составе матрицы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО С МАТРИЧНОЙ АДРЕСАЦИЕЙ И ЭЛЕКТРОДНАЯ РЕШЕТКА ДЛЯ ЭТОГО УСТРОЙСТВА | 2002 |

|

RU2272336C2 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ЭЛЕКТРОДОВ С БОЛЬШИМ КОЭФФИЦИЕНТОМ ФОРМЫ | 2002 |

|

RU2271591C2 |

| ФЕРРОЭЛЕКТРИЧЕСКИЙ ИЛИ ЭЛЕКТРЕТНЫЙ ЗАПОМИНАЮЩИЙ КОНТУР | 2002 |

|

RU2269830C1 |

| УСТРОЙСТВО ОБЪЕМНОГО ХРАНЕНИЯ ДАННЫХ, СОДЕРЖАЩЕЕ МНОЖЕСТВО СОБРАННЫХ В ПАКЕТ ЗАПОМИНАЮЩИХ УСТРОЙСТВ С МАТРИЧНОЙ АДРЕСАЦИЕЙ | 2003 |

|

RU2275699C2 |

| УСТРОЙСТВО ПАМЯТИ И/ИЛИ ОБРАБОТКИ ДАННЫХ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 2001 |

|

RU2237948C2 |

| ТРЕХМЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2002 |

|

RU2274913C2 |

| ПРИБОР С МАТРИЧНОЙ АДРЕСАЦИЕЙ, СОДЕРЖАЩИЙ ОДНО ИЛИ НЕСКОЛЬКО ЗАПОМИНАЮЩИХ УСТРОЙСТВ | 2002 |

|

RU2261500C2 |

| МАСШТАБИРУЕМОЕ УСТРОЙСТВО ОБРАБОТКИ ДАННЫХ | 1999 |

|

RU2201639C1 |

| МНОГОМЕРНАЯ СТРУКТУРА АДРЕСАЦИИ ДЛЯ ЭЛЕКТРОННЫХ УСТРОЙСТВ | 2001 |

|

RU2248626C2 |

| УСТРОЙСТВО ХРАНЕНИЯ И ОБРАБОТКИ ДАННЫХ И СПОСОБ ЕГО ИЗГОТОВЛЕНИЯ | 1999 |

|

RU2208267C2 |

Настоящее изобретение относится к устройствам, содержащим функциональные элементы, образующие планарный набор. В электродной решетке, содержащей первый и второй тонкопленочные электродные слои (L1, L2) с электродами (ε) в форме полосковых электрических проводников в каждом слое, электроды (ε) отделены друг от друга только тонкой пленкой (6) из электрически изолирующего материала, толщина которой составляет небольшую долю ширины электродов и которая проходит, по меньшей мере, вдоль боковых краев электродов, образуя изолирующие стенки (6а) между ними. Электродные слои (L1, L2) подвергают планаризации для того, чтобы обеспечить высокую степень плоскостности слоев. В устройстве, содержащем одну или более электродных решеток (ЕМ), электродные слои (L1, L2) каждой решетки взаимно ориентированы таким образом, что их электроды (1, 2) скрещиваются или располагаются взаимно перпендикулярно. Между электродами (1, 2) заключена в виде цельного слоя функциональная среда (3), в результате чего формируется устройство с матричной адресацией (предпочтительно пассивной), которое может быть использовано, например, в качестве устройства обработки или хранения данных с матричной адресацией, содержащего индивидуально адресуемые функциональные элементы (5), соответственно в форме логических ячеек или ячеек памяти. При этом коэффициент заполнения цельного слоя функциональной среды (3) указанными ячейками близок к 1, а максимальное количество ячеек в устройстве приближается к А/f2, где А - площадь поверхности функциональной среды, заключенной между электродными слоями (L1, L2), a f - минимальный технологически достижимый размер. Техническим результатом является обеспечение более эффективной адресации и обеспечение более высокой плотности записи сохраняемых данных. 3 н. и 19 з.п. ф-лы, 12 ил.

обеспечивающему одинаковость электропроводных свойств электродов (εа, εb) первого и второго наборов (Еа, Еb) электродов.

| US 5017515, 21.05.1991 | |||

| RU 94016378 A1, 27.08.1996 | |||

| EP 0902465 A1, 17.03.1999 | |||

| US 4952031 A, 28.08.1990 | |||

| US 6072716 A, 06.06.2000. |

Авторы

Даты

2006-04-27—Публикация

2002-11-08—Подача