Изобретение относится к цифровой информационно-измерительной и управляющей технике и может быть использовано в информационно-измерительных и управляющих системах и устройствах для преобразования напряжения постоянного тока в цифровой двоичный код.

Известен аналого-цифровой преобразователь (АЦП) последовательного приближения с изменяющимся опорным напряжением (патент США 5028926).

К недостаткам преобразователя следует отнести наличие двух регистров и относительную сложность технического построения узлов преобразователя.

Известен аналого-цифровой преобразователь для М- и Н-разрядного преобразования (патент США 5898396).

К недостаткам преобразователя следует отнести наличие двух регистров результата преобразования и схемы обмена данными между ними, что снижает быстродействия преобразователя и уменьшает надежность функционирования преобразователя.

Наиболее близким к предлагаемому изобретению по своей технической сущности является аналого-цифровой преобразователь последовательного приближения с повторяющимися циклами преобразования (патент США 5870052).

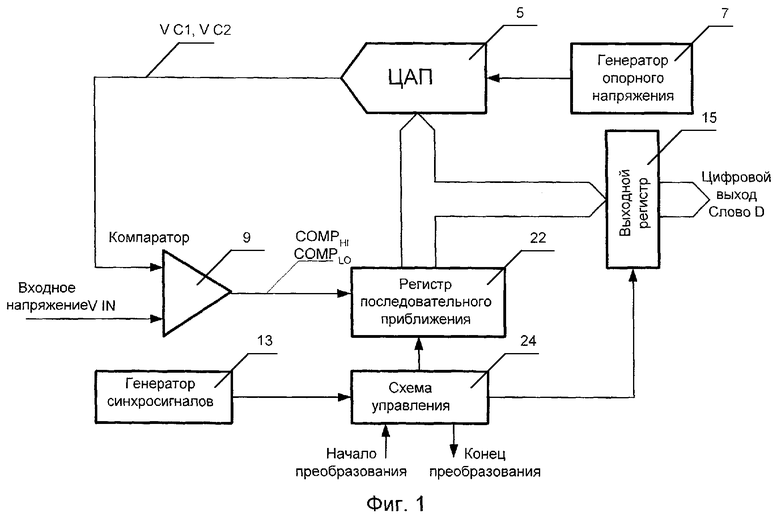

Блок-схема преобразователя последовательного приближения с повторяющимися циклами преобразования представлена на Фиг.1. Преобразователь состоит из компаратора 9, на один вход которого поступает входное напряжение постоянного тока V IN, на второй вход которого в последовательных циклах преобразования поступает выходное напряжение V С1, V С2 цифро-аналогового преобразователя (ЦАП) 5. Выходное напряжение компаратора 9 поступает на первый вход регистра последовательного приближения 22, на второй вход регистра последовательного приближения 22 поступают тактовые сигналы со схемы управления 24. Кодированные сигналы уравновешивания регистра последовательного приближения 22 передаются в ЦАП и в выходной регистр 15. Генератор опорного напряжения 7 формирует опорное напряжение для ЦАП. Генератор синхросигналов 13 через схему управления 24 обеспечивает функционирование аналого-цифрового преобразователя 22 с момента поступления на схему управления 24 сигнала «начало преобразования». Формируемый схемой управления 24 сигнал «конец преобразования» ставит в известность об окончании процесса преобразования.

Аналого-цифровой преобразователь входного напряжения V IN работает следующим образом.

Процесс преобразования входного напряжения в цифровой выходной сигнал начинается с установки первоначального кода соответствующего 1/2 значения полномасштабного входного сигнала преобразования и формирования на выходе ЦАП пробного значения сигнала, эквивалентного значению данного кода V TRIAL. В последующих циклах преобразования в зависимости от результата сравнения аналогового входного напряжения с двумя различными напряжениями сравнения V С1 и V С2 бит регистра последовательного приближения может быть настроен на одно из трех различных цифровых значений, например +1, -1 и 0. Одно из этих напряжений сравнения V С1 превышает напряжение испытания V TRIAL на первую величину ΔV1, и другое из двух напряжений сравнения V С2 меньше напряжения испытаний V TRIAL на вторую величину ΔV2.

После этого производится избирательная настройка напряжения испытания (увеличивается с помощью повышающей величины V ADJ1 или уменьшается с помощью понижающей величины V ADJ2) в конце каждого цикла преобразования в зависимости от результатов сравнения между входным напряжением V IN и двумя напряжениями сравнения V С1 и V С2. Целесообразно разницы А V1 и А V2 между напряжениями сравнений V С1 и V С2 и напряжением испытания V TRIAL сделать равными в каждом цикле, т.е. ΔV1=ΔV2. Повышающая и понижающая величины настройки в каждом цикле преобразования целесообразно сделать равными удвоенному значению разницы между напряжением сравнения и напряжением испытания, т.е. V ADJ1=V ADJ2=2ΔV. В последующих циклах величины ΔV и V ADJ уменьшаются в два раза по сравнению с величинами, используемыми в предыдущем цикле. В таблице 1 показаны операции, производимые в каждом цикле преобразования исходя из того, что цифровые пороги квантования для каждого бита регистра последовательного приближения составляют +1, -1 и 0.

В таблице 2 приведены примеры величин ΔV. и V ADJ, используемых в последовательных циклах для 16-битового АЦП, в котором внутренний ЦАП 5 имеет полномасштабное значение выходного напряжения V FSC.

В двух последних циклах преобразования (циклы 15 и 16 в Таблице 2) рассмотренный алгоритм не используется, поскольку в этих циклах (2-17) и (2-18) требуемые величины ΔV/V FSC и V ADJ./V FSC слишком малы для цифрового обозначения (менее единицы младшего значащего бита) на входе ЦАП. По этой причине в циклах 15 и 16 используется другой алгоритм.

В цикле 15 код ЦАП устанавливается на 32768+POS-NEG для получения пробного напряжения V TRIAL с входным напряжением V IN. Если результат сравнения равен 1 (V IN>V TRIAL), POS увеличивается на 1 (чтобы установить более высокое значение V TRIAL для цикла 16). Если результат сравнения равен 0, то NEG увеличивается на 1.

В цикле 16 код ЦАП установлен на 32768+POS-NEG для получения окончательного пробного напряжения V TRIAL, соответствующего 32768+POS-NEG, затем производится сравнение этого окончательного пробного напряжения V TRIAL с входным напряжением V IN. В этом случае, если результат сравнения равен 1 (VIN>V TRIAL), изменений POS или NEG не производится, в противном случае NEG увеличивается на 1.

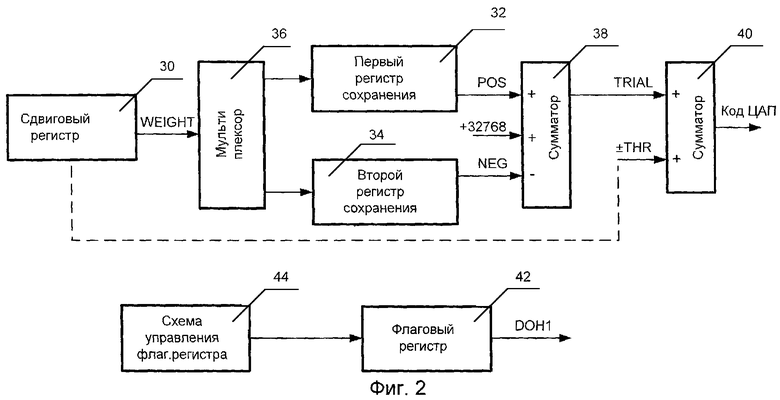

На Фиг.2 показана схема регистра последовательного приближения 22. Регистр включает 15-битовый регистр сдвига 30, первый и второй регистры сохранения 32 и 34, мультиплексор 36 и первый и второй сумматоры 38 и 40. Регистр последовательного приближения содержит также однобитовый флаговый регистр (регистр признака) 42 и связанную с ним схему управления 44.

Сдвиговый регистр 30 используется для сохранения цифрового значения WEIGHT, соответствующего вышеупомянутой величине настройки V ADJ. Первый и второй регистры сохранения 32 и 34 используются для сохранения соответствующих значений POS и HEG, применяемых для определения текущего напряжения испытания V TRIAL. Флаговый регистр 42 сохраняет флаг DOH1. Настройка флага DOH1 осуществляется схемой управления 44.

На свои разные входы сумматор 38 получает цифровые значения POS и HEG, которые сохраняются соответственно в первом и втором регистрах сохранения 32 и 34, и постоянное цифровое значение +32768 (=215). Таким образом, цифровое пробное значение TRIAL, выданное на выходе сумматора 38, равняется 32768+POS-NEG. Сумматор 40 получает на один свой вход цифровое значение TRIAL, а на другой свой вход - одну из двух последующих величин ±THR. Эти цифровые значения соответствуют вышеупомянутому ±ΔV. Значение +THR подается в сумматор 40, когда настраивается флаг DOH1, сохраняемый во флаговом регистре 42 (=1), а значение - THR подается в сумматор 40, когда флаг DOH1 возвращается в исходное положение (=0).

Сумматор 40 и сдвиговый регистр соединены прерывистой линией. Это сделано для того, чтобы показать, что из значения WEIGHT, сохраняемого в сдвиговом регистре 30, можно вывести два значения ±THR. Например, когда в вышеприведенном V ADJ=2ΔV, ±THR=WEIGHT/2.

Соответственно, выход сумматора 40 можно установить на TRIAL +THR или TRIAL-THR в зависимости от флага DOH1. Эти два цифровых значения соответствуют двум напряжениям сравнения V С1 и V С2.

Схема мультиплексора 36 позволяет прибавить значение WEIGHT, сохраняемое в регистре сдвига 30, к содержимому POS первого регистра сохранения 32 или к содержимому NEG второго регистра сохранения 34.

К числу недостатков преобразователя по патенту № 5870052 можно отнести следующие признаки.

Используемый в преобразователе регистр последовательного приближения, работающий в повторяющемся режиме, отличается сложностью технического построения.

Наличие в преобразователе выходного параллельного регистра кодового эквивалента преобразованного входного сигнала практически исключает использование гальванической развязки при передаче кодированного значения преобразованного сигнала в устройства связи с объектом управления.

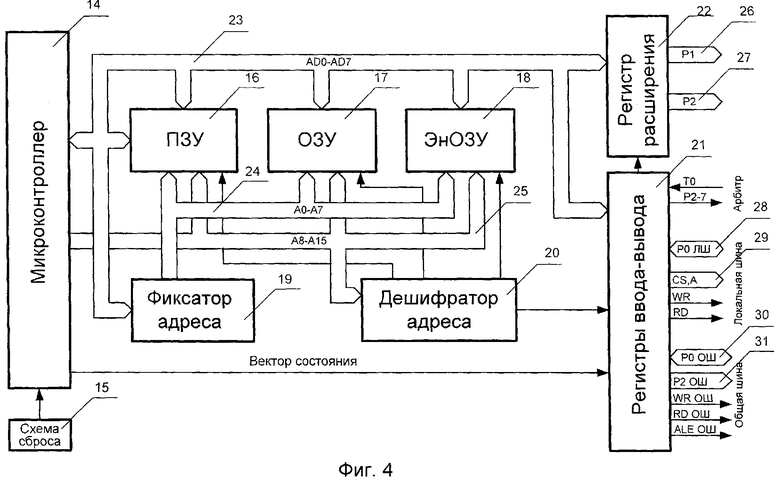

Цель изобретения - повышение надежности процесса преобразования, упрощение схемы преобразователя, увеличение диапазона преобразуемых входных напряжений и увеличение числа каналов преобразуемых сигналов. Схема преобразователя изображена на Фиг.3.

Аналого-цифровой преобразователь последовательного приближения состоит из компаратора 1, цифроаналогового преобразователя (ЦАП) 2, генератора опорного напряжения 3, регистра данных 4, масштабирующего усилителя входного сигнала 5, регистра коэффициента усиления 6, мультиплексора входных сигналов 7, регистра выбора канала входного сигнала 8 и элементов гальванической развязки сигнала выбора адреса 9, выбора коэффициента усиления 10, выбора данных 11, выходного сигнала компаратора 12 и микроЭВМ 13.

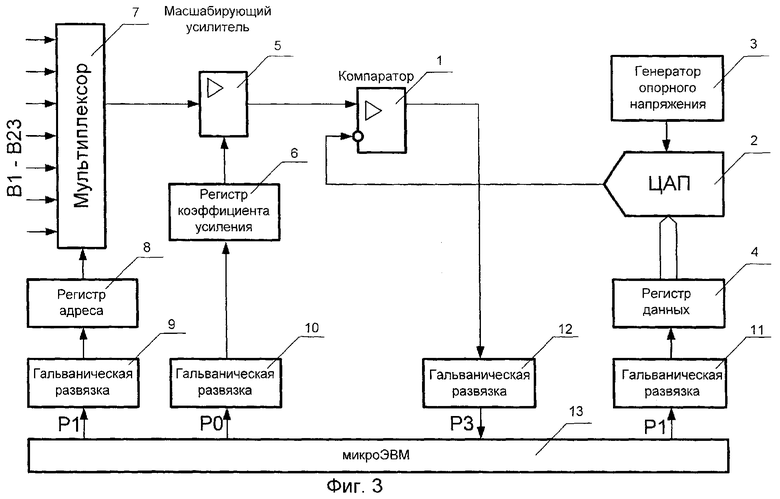

На Фиг.4 изображена схема микроЭВМ, в комплекте с которой осуществляется работа аналого-цифрового преобразователя последовательного приближения.

МикроЭВМ состоит из однокристального микроконтроллера 14, схемы сброса 15, памяти программ (ПЗУ) 16, оперативной памяти (ОЗУ) 17, энергонезависимой оперативной памяти (ЭнОЗУ) 18, регистра младших адресов 19, дешифратора старших адресов 20, регистров ввода-вывода 21, регистра расширения 22, восьмиразрядной шины адреса-данных 23, шины младших адресов 24, шины старших адресов 25, шины Р1 26, шины Р2 27, локальной шины РОЛШ 28, шины CS, A 29, общей шины Р0ОШ 30 и общей шины Р2OШ 31.

Аналого-цифровой преобразователь последовательного приближения работает следующим образом.

После включения электропитания микроЭВМ 13 через элементы гальванической развязки 9, 10 и 11 записывает в регистры адреса 8, регистр коэффициента усиления 6 и регистр данных 4 соответственно адрес входного сигнала, максимальный коэффициент усиления и код числа, соответствующий максимальному положительному значению входного сигнала. К входу масштабирующего усилителя 5 подключается сигнал выбранного мультиплексором 7 канала. ЦАП 2 преобразует записанный в регистр данных 4 код в напряжение постоянного тока, которое передается на первый вход компаратора 1. На второй вход компаратора поступает напряжение с выхода масштабирующего усилителя 5. Выходной сигнал компаратора 1 передается через элемент гальванической развязки 12 в микроЭВМ 13 для анализа.

Если выходной сигнал масштабирующего усилителя оказался больше напряжения, сформированного ЦАП 2 (зашкаливание), микроЭВМ через элемент развязки 10 вводит в регистр 6 меньший коэффициент усиления и выполняет переход к последовательному подбору эквивалентного кода путем записи в регистр данных 4 двухполярного смещенного цифрового кода.

Если выходной сигнал масштабирующего усилителя оказался меньше напряжения, сформированного ЦАП 2 (нет зашкаливания), для проверки входного сигнала на зануливание, микроЭВМ записывает в регистр данных 4 значение кода, соответствующее минимальному отрицательному значению входного сигнала, и производит анализ выходного сигнала компаратора. Если выходной сигнал масштабирующего усилителя оказался меньше напряжения, сформированного ЦАП 2 (зануливание), микроЭВМ 13 через элемент развязки 10 вводит в регистр 6 меньший коэффициент усиления и выполняет переход к последовательному подбору эквивалентного кода путем записи в регистр данных 4 двухполярного смещенного кода.

Если выходной сигнал масштабирующего усилителя оказался больше напряжения, сформированного ЦАП 2 (нет зануливания), микроЭВМ выполняет переход к последовательному подбору эквивалентного кода путем записи в регистр данных 4 двухполярного смещенного кода.

Описанный аналого-цифровой преобразователь был реализован на основе микроЭВМ типа 1816ВЕ31. Было изготовлено и включено в промышленную эксплуатацию свыше 480 преобразователей. За время эксплуатации в непрерывном режиме работы в течение 45000 часов принципиальных отказов не зафиксировано. Данное обстоятельство позволяет утверждать, что использование в системе управления технологическим оборудованием аналого-цифрового преобразователя последовательного приближения по данной схеме обеспечивает функционирование системы управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ИМИТАЦИИ ХОДЬБЫ И БЕГА ЧЕЛОВЕКА ДЛЯ РЕАБИЛИТАЦИИ БОЛЬНЫХ С РАЗЛИЧНЫМИ ДВИГАТЕЛЬНЫМИ НАРУШЕНИЯМИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2082378C1 |

| СПОСОБ ГЕОЭЛЕКТРОРАЗВЕДКИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2006886C1 |

| УСТРОЙСТВО ДЛЯ СЪЕМА, РЕГИСТРАЦИИ И АНАЛИЗА ЭЛЕКТРОФИЗИОЛОГИЧЕСКИХ СИГНАЛОВ И БЛОК ЗАЩИТЫ ОТ АВАРИЙНЫХ ТОКОВ ПАЦИЕНТА | 1995 |

|

RU2102004C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2017203C1 |

| Устройство для измерения электрической энергии | 1985 |

|

SU1257542A1 |

| ЦИФРОВОЙ РЕГУЛЯТОР ДЛЯ МНОГОДВИГАТЕЛЬНОГО ЭЛЕКТРОПРИВОДА | 1992 |

|

RU2071635C1 |

| Устройство для измерения электрической энергии | 1988 |

|

SU1596264A2 |

| УСТРОЙСТВО ДЛЯ ВВОДА АНАЛОГОВЫХ СИГНАЛОВ | 1991 |

|

RU2012036C1 |

| ИНФОРМАЦИОННАЯ СИСТЕМА СВЯЗИ | 1991 |

|

RU2019851C1 |

| УСТРОЙСТВО СБОРА, ПРЕОБРАЗОВАНИЯ И ПЕРЕДАЧИ РЕЗУЛЬТАТОВ ИЗМЕРЕНИЯ ПАРАМЕТРОВ ФИЗИЧЕСКОЙ СРЕДЫ | 1994 |

|

RU2079882C1 |

Изобретение относится к цифровой информационно-измерительной и управляющей технике и может быть использовано в информационно-измерительных и управляющих системах и устройствах для преобразования напряжения постоянного тока в цифровой двоичный код. Техническим результатом является повышение надежности процесса преобразования, упрощение схемы преобразователя, увеличение диапазона преобразуемых входных напряжений и увеличение числа каналов преобразуемых сигналов. Устройство содержит компаратор, цифроаналоговый преобразователь, генератор опорного напряжения, аналоговый мультиплексор, масштабирующий усилитель, регистр адреса, регистр коэффициента усиления, элементы гальванической развязки, микроЭВМ. 2 табл., 4 ил.

Аналого-цифровой преобразователь последовательного приближения, содержащий компаратор, первый вход которого соединен с выходом цифроаналогового преобразователя, аналоговый вход которого соединен с выходом генератора опорного напряжения, и цифровые входы соединены с выходом регистра данных, отличающийся тем, что в него введены четыре элемента гальванической развязки, регистр адреса, регистр коэффициента усиления, микроЭВМ, предназначенная для записи начальных данных в регистры устройства, проведения анализа по результатам преобразования и изменения указанных данных на основе проведенного анализа, масштабирующий усилитель, мультиплексор, при этом первый, второй, третий выходы микроЭВМ через соответствующие элементы гальванической развязки соединены соответственно с входами регистра адреса, регистра коэффициента усиления, регистра данных, вход микроЭВМ через четвертый элемент гальванической развязки соединен с выходом компаратора, второй вход которого соединен с выходом масштабирующего усилителя, цифровой вход которого соединен с выходом регистра коэффициента усиления, аналоговый вход масштабирующего усилителя соединен с выходом мультиплексора, на аналоговый вход которого включено множество входных сигналов постоянного напряжения разного уровня и полярности, цифровые входы мультиплексора соединены с выходом регистра адреса.

| US 5870052 А, 09.02.1999 | |||

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 2001 |

|

RU2183381C1 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1996 |

|

RU2114501C1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1985 |

|

SU1248067A1 |

| US 5898396 A, 27.04.1999. | |||

Авторы

Даты

2006-04-27—Публикация

2004-07-23—Подача