Изобретение относится к контрольно-измерительной и информационной технике и может быть использовано для приема и передачи дискретной информации при контроле полупроводниковых приборов, в том числе дистанционном контроле, например для контроля высокочастотных транзисторов, вмонтированных в схему, а также для информационного обмена между объектами.

Известна информационная система для контроля полупроводниковых приборов, содержащая блок задания режима, ЭВМ, канал связи (линию), клеммы для подключения объекта контроля (интегрального стабилизатора напряжения), регулятор, измерительный блок с источником опорного напряжения, коммутатором, АЦП и клеммой для подключения регулирующего входа объекта контроля, а также источники напряжения и тока, входящие в состав блока задания режима.

Недостатком известной системы является низкая надежность, обусловленная тем, что при значительной напряженности канала связи с ЭВМ информация, передаваемая по каналу в импульсном виде, искажается из-за падения напряжения в линии, нелинейности коэффициента передачи.

Наиболее близким к предложенному является устройство (информационная система) для контроля полупроводниковых приборов, содержащее управляемый источник греющего тока, управляемый источник измерительного тока, блок АЦП, выход которого подключен к шине данных системы, усилитель, блок выборки-хранения, разностный усилитель, ЦАП, микроЭВМ, контактное устройство, а также магистраль или линию связи.

Этому устройств пpисущ тот же недостаток, что и предыдущему.

Целью изобретения является повышение надежности, расширение области применения информационной системы.

С этой целью система включает регистр, ЦАП и сглаживающий фильтр, соединенные последовательно, блок гальванической развязки и согласования, ключ, усилитель, блок АЦП и дешифратор адреса, причем регистр, блок АЦП и дешифратор адреса подключены к магистрали (шине данных или шинам данных и адреса системы), на вход дешифратора подаются также сигналы управления. Выходы дешифратора адреса соединены с входом синхронизации регистра и входом разрешения блока АЦП, первый и второй входы которого соединены с выходом усилителя и вторым выводом блока гальванической развязки и согласования, первый вывод которого соединен с выходом фильтра и входом усилителя. Выходы регистра соединены с входами ЦАП и управляющим входом ключа, первый вывод которого подключен к линии и третьему выводу блока гальванической развязки и согласования, четвертый вывод которого соединен с вторым выводом ключа.

При этом система может быть снабжена блоком формирования параллельного гармонического кода и цифровой обработки, подключенными к шине данных или шинам данных и адреса системы.

В частном случае блок формирования параллельного гармонического кода и цифровой обработки может быть выполнен в виде блока формирования кода, цифрового дискриминатора и контролера, при этом шина данных контролера, цифрового дискриминатора и блока формирования кода объединены и соединены с шиной данных блока формирования параллельного гармонического кода и цифровой обработки, шина адреса и управления которого соединены с соответствующей шиной контролера.

Кроме того, информационная система может быть снабжена блоком задания режима и измерительным блоком, вход и выход которых подключен к шине данных и шине адреса и управления системы.

В отличие от известной системы блок АЦП выполнен в виде АЦП и блока элементов совпадения, первая группа входов которого соединена с выходом АЦП, а вторая группа входов объединена и подключена к входу разрешения блока АЦП, первый и второй входы которого соединены с входом АЦП и третьим входом блока элементов совпадения соответственно, выход которого соединен с выходом блока АЦП.

В простейшем случае блок АЦП может быть выполнен в виде двух элементов И, первые входы которых соединены с первым и вторым входами блока АЦП, а вторые входы объединены и соединены с входом разрешения блока АЦП, выход которого соединен с выходами элементов И.

Кроме того, блок формирования кода выполнен в виде селектора адреса, генератора пачки импульсов, элемента задержки, счетчика и дешифратора, выход которого соединен с выходом блока формирования кода, входная шина данных которого соединена с управляющим входом генератора пачки импульсов и информационным входом счетчика, вход записи которого соединен с входом элемента задержки и выходом селектора адреса, вход которого соединен с входной шиной адреса блока формирования кода, при этом выход элемента задержки соединен с входом запуска генератора пачки импульсов, выход которого соединен со счетным входом счетчика, выход которого соединен с входом дешифратора.

Цифровой детектор может быть выполнен в виде селектора адреса, элемента задержки, генератора пачки импульсов, счетчика, двух регистров, блока сравнения кодов и формирователя импульсов, при этом входная шина адреса цифрового дискриминатора соединена с входом селектора адреса, выход которого соединен с входом синхронизации первого регистра, установочным входом счетчика и входом запуска генератора пачки импульсов, выход которого соединен со счетным входом счетчика, выход которого соединен с информационным входом второго регистра и первым входом блока сравнения кодов, второй вход которого соединен с выходом первого регистра, информационный вход которого соединен с входной шиной данных цифрового дискриминатора, причем выход блока сравнения кодов соединен с входом формирователя импульсов, выход которого соединен с входом синхронизации второго регистра и входом элемента задержки, выход которого вместе с выходом второго регистра образует выходную шину цифрового дискриминатора.

Цифровой дискриминатор может быть также выполнен в виде высокочастотного генератора, элемента И, счетчика, двух регистров, селектора адреса, блока сравнения кодов, двух элементов задержки и D-триггера, при этом выход высокочастотного генератора соединен с первым входом элемента И, второй вход которого соединен с информационным входом и инверсным выходом D-триггера, установочный вход которого соединен с установочным входом счетчика, входом синхронизации первого регистра и выходом селектора адреса, вход которого соединен с входной шиной адреса цифрового дискриминатора, входная шина данных которого соединена с информационным входом первого регистра и первым входом блока сравнения кодов, второй вход которого соединен с выходом первого регистра, причем выход блока сравнения кодов соединен с тактовым входом D-триггера и входом первого элемента задержки, выход которого соединен с входом второго элемента задержки и входом синхронизации второго регистра, информационный вход которого соединен с выходом счетчика, счетный вход которого соединен с выходом элемента И, а выход второго регистра и выход второго элемента задержки образуют выходную шину цифрового дискриминатора.

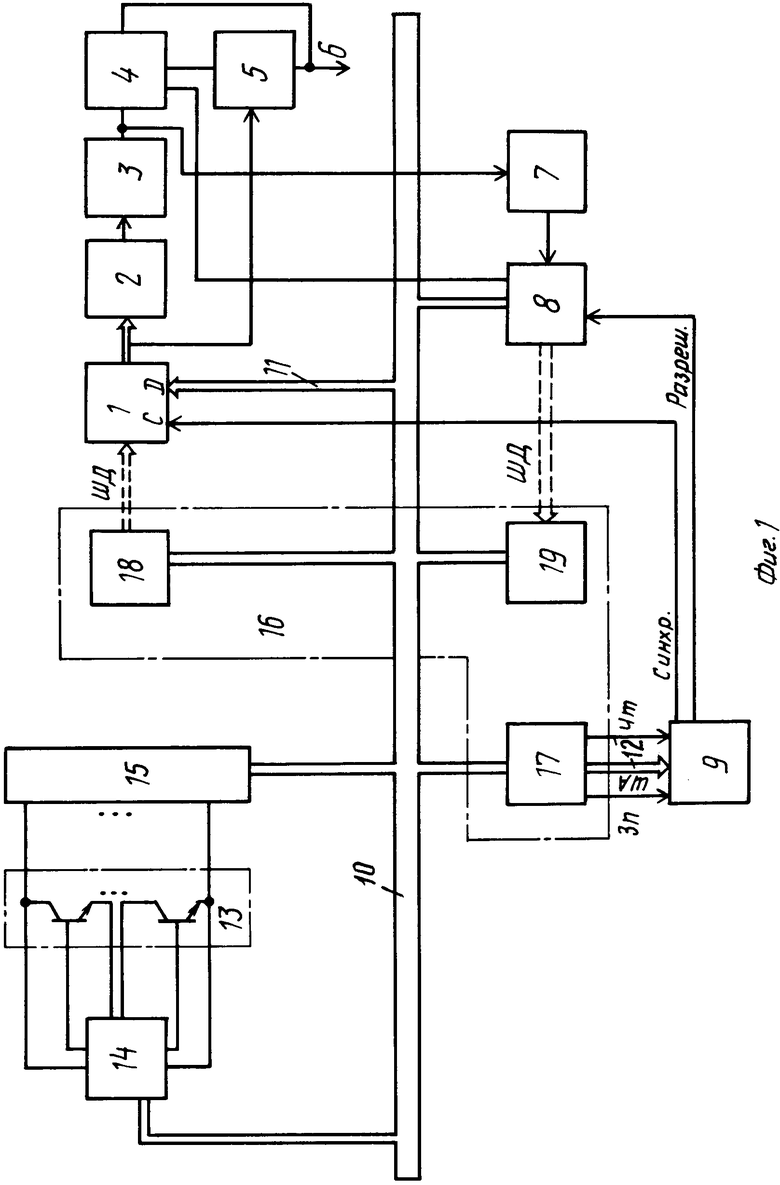

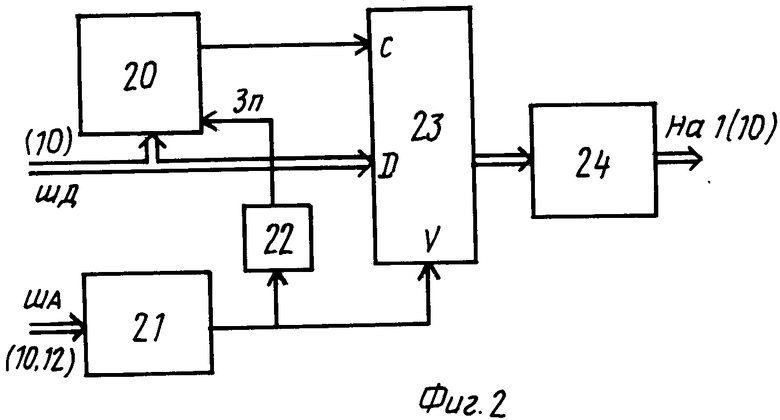

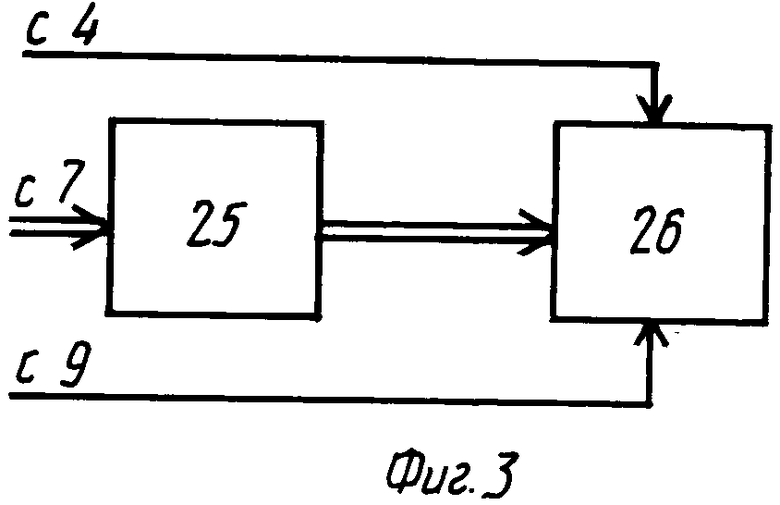

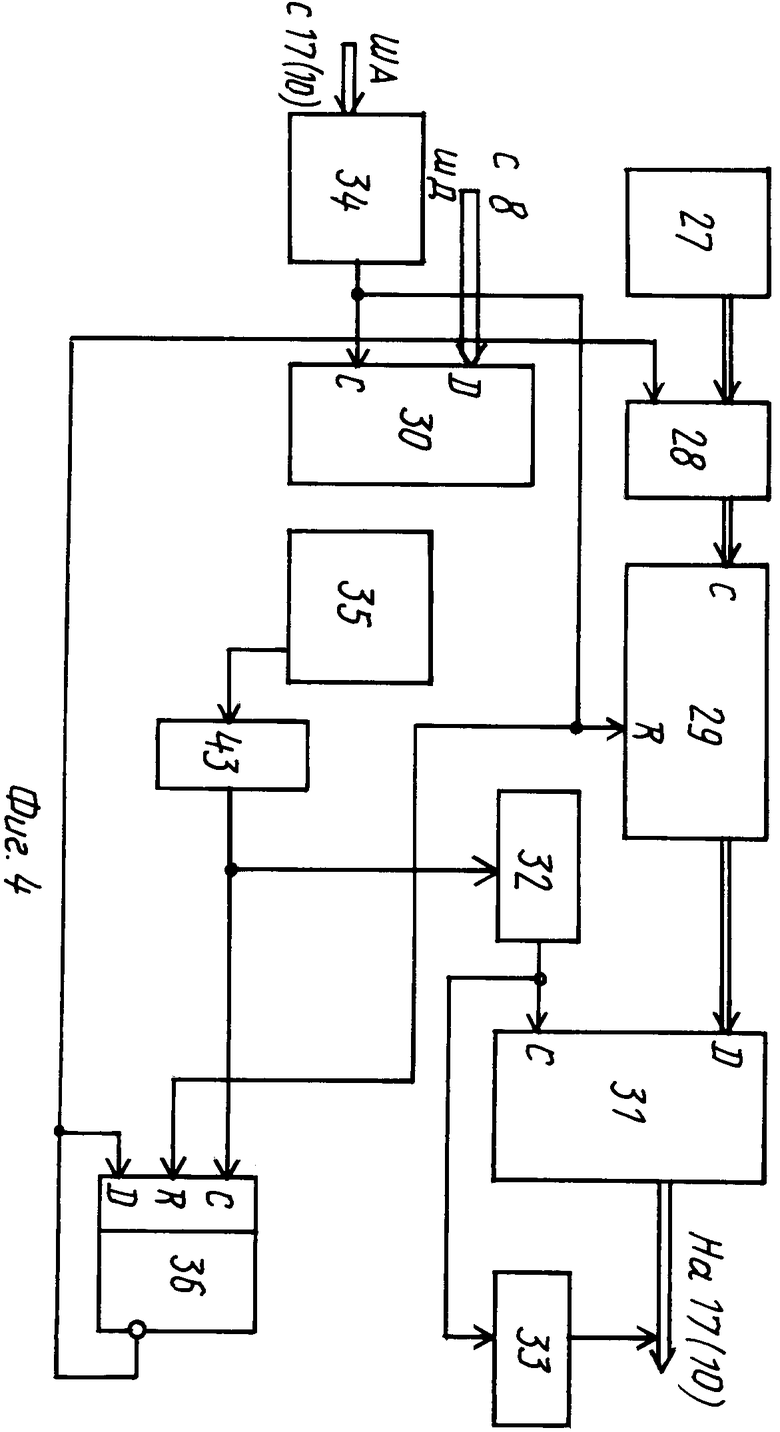

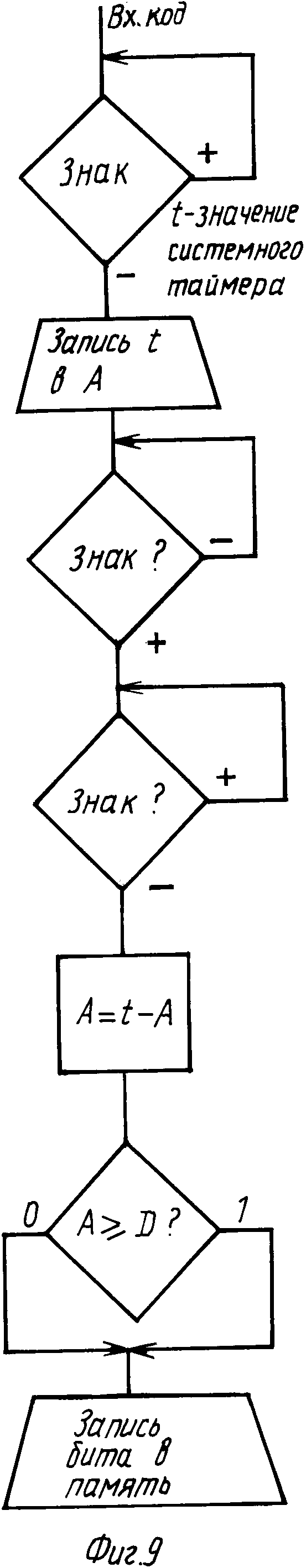

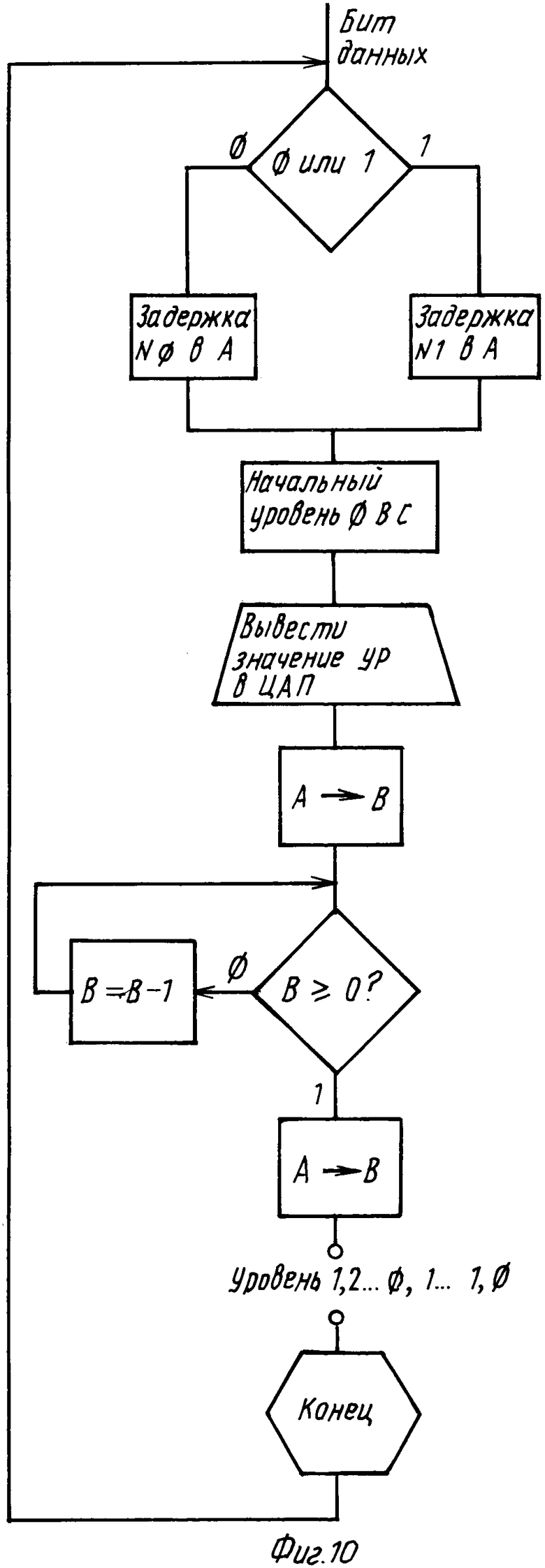

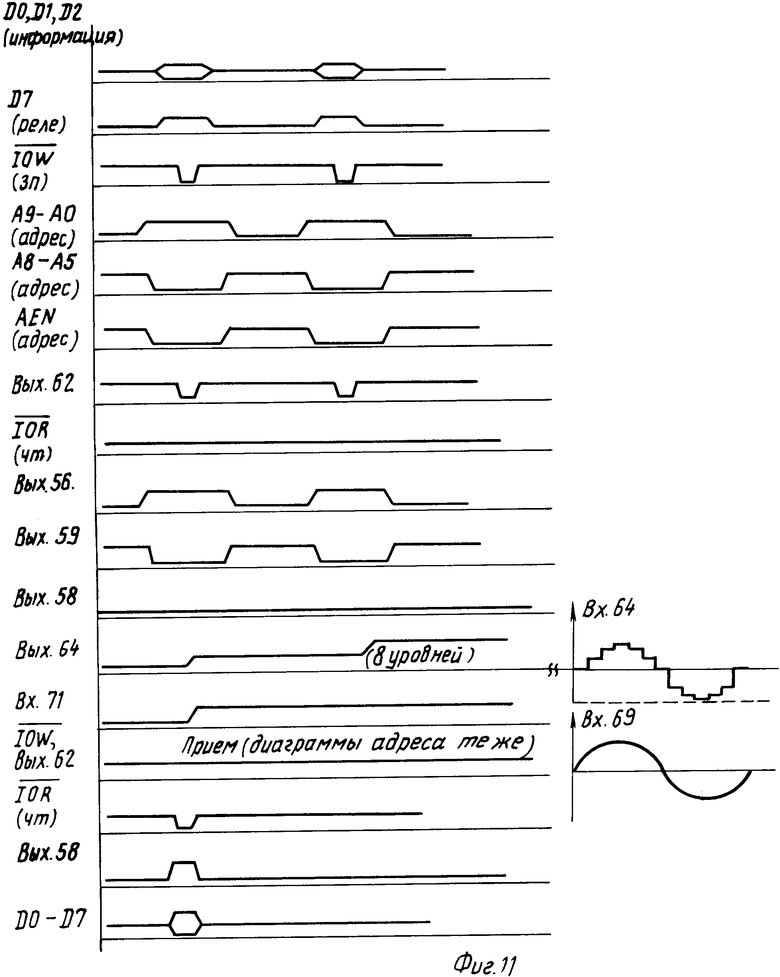

На фиг.1 приведена блок-схема предлагаемой системы; на фиг.2-7 - схемы блока формирования кодов, блока АЦП, двух вариантов выполнения цифрового дискриминатора, схема, поясняющая подключение контролируемых полупроводниковых приборов к блоку задания режима и входных воздействий и измерительному блоку и схема дешифратора адреса соответственно; на фиг.8 - электрическая схема системы; на фиг.9 и 10 - алгоритм работы блока формирования параллельного гармонического кода и цифровой обработки в случае программной реализации данного блока (приведенные алгоритмы могут быть использованы раздельно, в случае программной реализации блока формирования кода и цифрового дискриминатора); на фиг.11 - временная диаграмма работы устройства, показанного на фиг.8.

Информационная система содержит последовательно соединенные регистр 1, цифроаналоговый преобразователь (ЦАП) 2 и сглаживающий фильтр 3 с частотой среза порядка 20 Гц, а также блок 4 гальванической развязки и согласования, ключ (переключатель) 5, обеспечивающий разрыв линии 6 связи, усилитель 7, блок 8 аналого-цифрового преобразования (АЦП) и дешифратор 9 адреса. Управление системой осуществляется по магистрали 10, которая может подразделяться на шину 11 данных и шину 12 адреса и управления. Блок 13 испытуемых приборов подключается к блоку 14 задания режима и входных воздействий к измерительному блоку 15. К магистрали 10 подключается также блок 16 формирования параллельного гармонического кода и цифровой обработки, выполняющий функции системного контролера и в частном случае выполненный в виде контролера 17, блока 18 формирования кода и цифрового дискриминатора 19.

Блок формирования кода содержит генератор 20 пачки импульсов, селектор 21 адреса, элемент 22 задержки, счетчик 23, дешифратор 24.

Блок 8 (фиг.3) включает АЦП 25 и блок 26 элементов совпадения.

Цифровой дискриминатор 19 (фиг.4) включает высокочастотный генератор 27, элемент И 28, счетчик 29, регистры 30 и 31, элементы 32 и 33 задержки, селектор 34 адреса, блок 35 сравнения кодов и D-триггер 36.

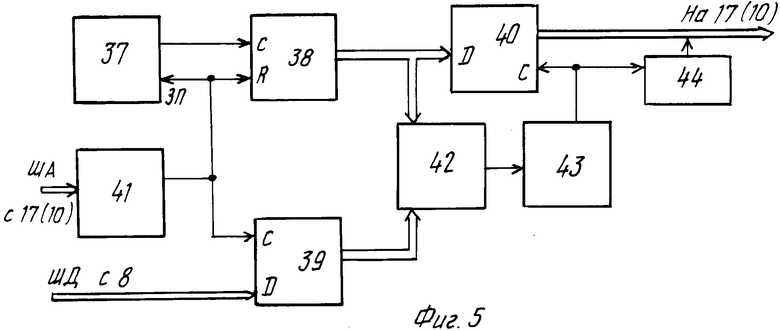

Дискриминатор 19 (фиг.5) содержит генератор 37 пачки импульсов, счетчик 38, регистры 39 и 40, селектор 41 адреса, блок 42 сравнения кодов, формирователь 43 импульсов и элемент 44 задержки.

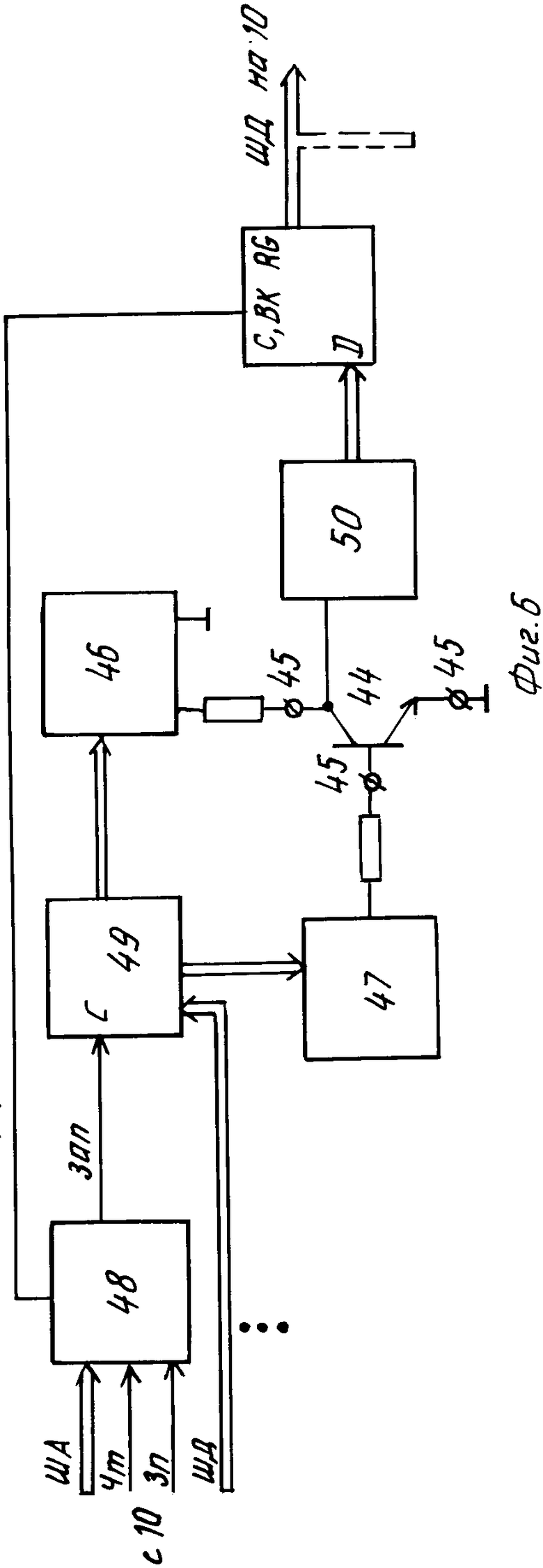

Испытуемый прибор (транзистор) (фиг.6) с помощью клемм или зажимов 45 включается в цепь управляемых источника 46 напряжения или тока и генератора 47 входных воздействий и содержит дешифратор 48 адреса, регистр 49, АЦП 50, регистр 51.

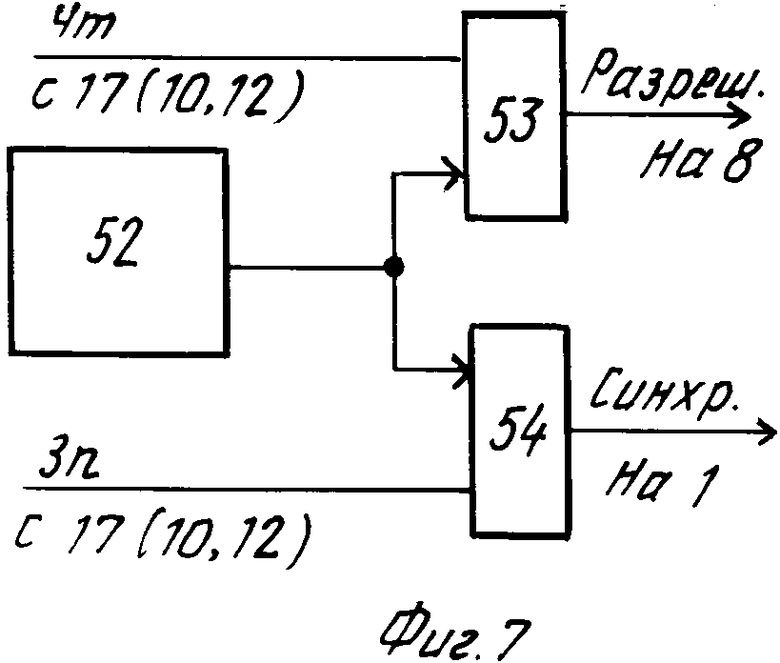

Дешифратор 9 может включать (фиг.7) селектор 52 адреса и два элемента И 53 и 54.

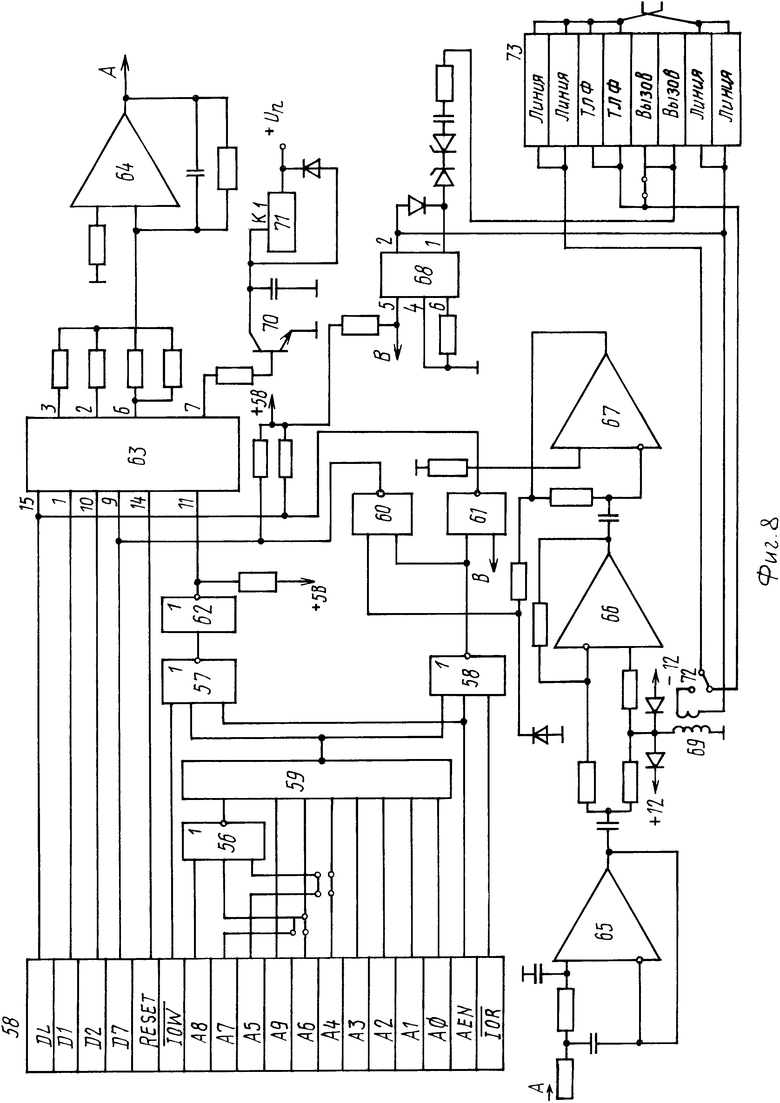

Электрическая схема системы содержит входной разъем 55, элементы ИЛИ-НЕ 56-58, элементы И-НЕ 59-61, инвертор 62, счетчик 63, операционные усилители 64-67 (использован счетверенный ОУ), оптопару 68, согласующий трансформатор 69, ключ 70, обмотку 71 и контакты 72 реле и выходной разъем 73.

Блок 16 может быть реализован программно, в виде микропроцессора, ЭВМ или микроЭВМ, алгоритм работы которых приведен на фиг.9 и 10. Алгоритм работы контролера 17 ясен из последующего описания работы системы. Данный алгоритм всецело определяется набором контролируемых параметров, т.е. передаваемой и принимаемой информацией, как впрочем, и алгоритм работы блока 16. Блоки 18 и 19 также могут быть реализованы программно по алгоритмам фиг.9 и 10.

В процессе анализа последующего описания работы устройства и выполнения отдельных блоков следует учитывать возможные варианты организации магистрали 10. Так в ряде случаев сигналы управления и адрес передаются по той же шине (или ее части), что и данные с использованием служебных слов или без них. Поэтому шины 11 и 12 могут выполняться как совместно, так и раздельно. То же относится ко всем шинам адреса и данных, показанных на фиг.1-7. Поскольку организация магистралей и шин определяется ГОСТ для каждого типа используемых микросхем, в дальнейшем предполагается, что объединение или наоборот, разделение шин управления, адреса и данных носит условный характер.

Информационная система работает следующим образом.

В регистр 1 последовательно заносится код, изменяющийся по гармоническому закону. Код заносится в режиме записи (передачи) по синхроимпульсу на выходе дешифратора 9. ЦАП 2 преобразует значение кода в напряжение (без постоянной составляющей), при этом коммутационные выбросы и ступеньки напряжения сглаживаются фильтром 3. Такой способ формирования синусоидального напряжения, показанного на диаграмме фиг.11, является важной особенностью предлагаемого устройства, так как позволяет легко варьировать амплитуду, фазу и частоту синусоидального сигнала и не требует использования активных фильтров высокого порядка. Сформированный сигнал через блок 4 и замкнутый ключ 5 поступает в линию 6. В свою очередь, синусоидальный сигнал из линии в виде набора импульсов или "пакетов" колебаний (импульсов) с амплитудой, фазой или частотой, соответствующими принимаемой цифровой или иной информации через ключ 5 и блок 4 поступает на вход усилителя 7, выходной сигнал которого преобразуется в код в блоке 8. Если предварительно был получен сигнал вызова, поступивший через блоки 4 и 8 в магистраль 10, на входе дешифратора 9 выставляется сигнал чтения (прием) и соответствующий ему сигнал разрешения на выходе дешифратора 9 производит передачу кода из блока 8 в магистраль 10 (или на иную исходную шину устройства, входной шиной которого служит входная шина регистра 1).

Назначением блока 16 является формирование кодов, изменяющихся по гармоническому закону, т.е. кодирование информации, и цифровая обработка, фильтрация, декодирование информации, представленной в виде кодов, изменяющихся по гармоническому закону. При этом в зависимости от вида используемой модуляции используется тот или иной алгоритм работы блока 16, та или иная аппаратная реализация блока 19 (дискриминатора). В качестве примера на фиг. 9 дан алгоритм частотной дискриминации. При амплитудной модуляции в память заносится тот или иной бит в зависимости от значения максимального кода в данном импульсе или пакете, а при фазовой - в зависимости от величины первого кода импульса или пакета.

Блок 16 производит также управление блоком 14 и прием информации от блока 15 по программе испытаний приборов 13. При этом сигналы сопровождения (адрес, сигналы управления, служебные сигналы) передаются по магистрали 10 или по образующим ее раздельным шинам управления, адреса и данных.

Более детально рассмотрим работу системы на примере реализации отдельных ее блоков. Адресация блока 18 может производиться через селектор 21, по шине данных, по части шины данных или с помощью входного сигнала записи дешифратора 9. Предварительно на входной шине данных блока 18 (в частности, шине данных системы и/или контролера 17) выставляется информация о частоте и фазе посылки, записывающаяся в (управляющая работой) генератор 20 и счетчик 23, запись кода в генератор 20 (входной регистр генератора) может осуществляться по сигналу запуска или выходному сигналу селектора 21. Генератор 20 может быть выполнен в виде последовательно соединенных регистра, ЦАП и управляемого напряжением генератора импульсов, элемента И и реверсивного счетчика, работающего на вычитание. Выход переполнения счетчика подключен к второму входу элемента И, информационные входы - к выходу задатчика кода, а вход записи - к входу запуска генератора 20. В результате выходной код счетчика изменяется в течение времени, заданного генератором 20, а дешифратор 24 формирует при этом последовательность кодов, значение которых изменяется по синусоидальному закону. В качестве дешифратора 24 может быть использована серийно выпускаемая интегральная микросхема или логическая структура, синтезированная по заданной входной и выходной последовательностям (это относится ко всем дешифраторам предлагаемого устройства).

Блок 16 осуществляет периодический опрос системы или набора систем в случае, если в качестве блока 16 использована центральная ЭВМ, а системы являются ее абонентами путем формирования адреса данной системы и сигнала "чтение" на шине 12. Если при этом на втором входе блока 8 присутствует сигнал "Вызов", он поступает на шину 10 и блок 16 (контролер 17) не снимает или через небольшой интервал времени восстанавливает сигнал "Чтение" и адрес системы. При этом через регистр 1 замыкается ключ 5 и блок 16 (дискриминатор 19, который может быть связан с блоком 8 и отдельной шиной данных) осуществляют прием информации с выхода блока 26. Последний представляет собой набор элементов И по числу выходных сигналов АЦП 25 плюс элемент И для сигнала "Вызов", причем вторые входы элементов И соединены с входом разрешения блока 8.

На фиг.4 представлен частотный дискриминатор, в качестве которого может быть использован и частотомер. В режиме приема контролер 17 активизирует дискриминатор 19 путем подачи соответствующего адреса на шину адреса дискриминатора 19 (отдельную или входящую в состав магистрали 10) или просто сигналом "Чтение". Для этой цели может использоваться также сигнал разрешения с выхода дешифратора 9. При появлении указанных сигналов обнуляются триггер 36 и счетчик 29, после чего начинается заполнение счетчика 29 частотой генератора 27. В этот момент код на шине данных записывается также в регистр 30. Через половину периода колебания код на первом входе блока 35 оказывается равным (больше или меньше) кода на входной шине. При этом по выходному сигналу блока 35 изменяется состояние триггера 36 и код из счетчика 29 переписывается в выходной регистр 31. Блок 35 может быть реализован программно или в виде мажоритарного блока (мажоритарные схемы выпускаются серийно), выходной сигнал которого через дешифратор, например элемент И, или непосредственно поступает на вход формирователя 43 выходного импульса.

Представленный на фиг. 5 фазовый дискриминатор работает аналогично (в этом случае также можно воспользоваться стандартным фазометром). Генератор 37 формирует пачку импульсов постоянной частоты, поэтому его можно реализовать в виде неуправляемого генератора, элемента И и реверсивного счетчика. Счетчик 38 предназначен для формирования линейно изменяющегося кода, пробегающего все возможные значения, для чего может выполняться с выходным дешифратором. Подача адреса или сигнала запуска дискриминатора 19 производится котролером 17 в момент появления данных на выходе блока 8 или с фиксированной задержкой относительно этого момента. Фиксация упомянутого момента может осуществляться и в блоке 19, для чего селектор 41 выполняется в виде дешифратора, в простейшем случае элемента ИЛИ, и подключается к шине данных: в момент появления на ней значащего кода производится запись первого значения колебания в регистр 39. В момент, когда выходной код счетчика 38 сравнивается с кодом в регистре 39, это значение кода заносится в регистр 40. В результате выходной сигнал элемента 44 является не только сигналом готовности кода, определяющего фазу пришедшего импульса, но и сигналом неисправности линии и аппаратуры. Разумеется, блок 19 можно упростить, выполняя его в виде элемента И 41, регистра 39 и элемента 44, вход которого подключен к выходу селектора 41, однако в этом случае отсутствует указанный эффект.

Указанного эффекта можно добиться и в схеме фиг.4, если между выходом селектора 34 и установочными входами счетчика 29 и триггера 36 установить элемент ИЛИ, второй вход которого соединить с выходом элемента 33 (длительность выходного сигнала которого должна быть достаточной для приема контролером 17 сигнала "готовность информации"). В этом случае коды на выходной шине при исправности аппаратуры и линии повторяются, что и является для контролера 17 сигналом исправности.

Схема, приведенная на фиг.6 и 7, не нуждается в пояснениях, если учесть, что регистры 49 и 51 удобно выполнять с тремя состояниями выходов, а сигнал записи совмещать с сигналом выбора кристалла.

На фиг. 8 дешифратор 9 образован элементами 56, 59, 57, 58 и 62. Элементы 60 и 61 образуют блок 8. При этом существенно, что подобное выполнение блока 8 наряду с его значительным упрощением, обеспечивает надежность работы блока 8. Более того, при использовании КМОП элементов система может отключаться от питания контролером 17 или блоком 16. При поступлении же сигнала вызова благодаря запитке микросхем элементов 60 и 61 от входного сигнала (между входами может быть установлен резистор порядка 10 кОм) блок 17 (16) получает информацию о наличии вызова и перед формированием сигнала "Чтение" включает блок питания системы, что позволяет экономить энергию.

Выполнение блока 8 в виде элементов 60 и 61 показывает также, что в этом блоке можно использовать малоразрядный в простейшем случае одноразрядный АЦП.

Регистр 1 образован счетчиком 63, ЦАП 2 собран на ОУ 64. Блок 4 образован элементами 68 и 69, а ОУ 65-67 служат для фильтрации и усиления. И, наконец, элементы 70-72 образуют коммутатор линии 6 (ключ 5).

П р и м е р. С помощью информационной системы испытывалась партия транзисторов КТЗ12М. Режим испытаний соответствовал ТУ, транзисторы размещались на 20 испытательных пунктах, удаленных от центрального пункта, где располагалась ЭВМ. На части испытательных пунктов были установлены периферийные системы без блоков 16, а на части - с блоками 16. На каждом пункте испытывалось 20 транзисторов. Испытания проводились в течение 8 ч, при этом периферийные и центральный блоки отслеживали дрейф напряжения коллектор-эмиттер в режиме большого сигнала. В случае появления дрейфа, превышающего браковочную норму, транзистор испытывался с помощью независимых средств. Испытания не выявили ни одного случая передачи искаженной информации - все проверенные транзисторы показали превышающее норму значение дрейфа.

При реализации системы следует учитывать, что назначением блока 16, определяющим алгоритм его работы или аппаратную реализацию, является при передаче: в линию: прием или формирование, выработка параллельного кода сообщения, преобразование его в последовательный код и преобразование каждого бита последовательность параллельных кодов, изменяющихся по гармоническому закону. В процессе приема с линии алгоритм обратный. Необходимо учесть также, что возможно перераспределение функций между блоками 17-19, однако дискриминатор 19 в любом случае должен обеспечивать чтение очередного бита информации и его трансляцию, а блок 18 наоборот, прием бита и формирование импульса, показанного на диаграмме фиг.11.

Предлагаемое устройство характеризуется высокой надежностью благодаря отсутствию потерь в линии. В то же время передача и прием гармонических сигналов, обеспечивающие данный эффект, достигаются простыми средствами: использованием фильтра низкого порядка, малоразрядного АЦП. Использование в качестве управляющих элементов разрешающих входов элементов 2И-НЕ и синхровхода регистра данных для управления работой реле коммутатора, который может обеспечивать и набор номера абонента при работе на телефонную линию связи, позволяет оперативно включить тракт приема или передачи системы, благодаря этому последняя обладает широкой областью применения и может быть использована в других областях техники, например, при создании информационно-измерительных комплексов, приемо-передающих систем, модемов и т.п.

Предлагаемая система может использоваться при контроле полупроводниковых приборов всех типов, поскольку установка блоков формирования параллельного гармонического кода и цифровой обработки на обоих концах линии обеспечивает буферизацию данных при любой скорости их накопления. Существенным достоинством предлагаемой информационной системы является ее универсальность: система может использоваться как на стороне испытуемого прибора, т.е. передающей, так и на стороне центрального процессора, осуществляющего обработку испытательной информации, т.е. приемной. При этом система допускает любой вид кодирования информации, использование всех видов модуляции, что также способствует надежности системы, достоверности информации, полученной с ее помощью.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| УСТРОЙСТВО МОНИТОРИНГА ПАРАМЕТРОВ ЗАДЫМЛЕННОСТИ И ИХ ДОСТОВЕРНОСТИ | 2011 |

|

RU2457541C1 |

| Устройство для ввода информации | 1982 |

|

SU1062683A1 |

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| ТЕЛЕВИЗИОННАЯ СИСТЕМА ВЫСОКОГО РАЗРЕШЕНИЯ | 1996 |

|

RU2127961C1 |

| СПОСОБ ДЛЯ ЦИФРОВОЙ СУБСТРАКЦИОННОЙ АНГИОГРАФИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2043073C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ | 1990 |

|

RU2018142C1 |

| СПОСОБ ПРЕОБРАЗОВАНИЯ УГЛА ПОВОРОТА ВАЛА В КОД | 1993 |

|

RU2108663C1 |

Использование: контроль всех типов полупроводниковых приборов, информационно-измерительные комплексы, диагностическая аппаратура, связь. Сущность изобретения: информация в линию поступает в виде пакетов гармонических колебаний, которые формируются цепью последовательно соединенных регистра, цифроаналогового преобразователя и фильтра низкой частоты. Информация, поступающая из линии в том же виде, преобразуется (дешифрируется) малоразрядным аналого-цифровым преобразователем. 9 з.п. ф-лы, 11 ил.

| Устройство для неразрушающего контроля качества присоединения полупроводникового кристалла к корпусу | 1989 |

|

SU1649473A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1994-09-15—Публикация

1991-12-04—Подача