Изобретение относится к технике радиосвязи и может использоваться для цифрового телевещания.

За прототип принята цифровая система стереотелевидения [1], содержащая на передающей стороне фотоэлектрический преобразователь, формирующий два изображения одного объекта, шесть АЦП видеосигнала, два АЦП сигнала звука, генератор синусоидальных колебаний и синтезатор частот, три формирователя кодов, первый и второй самоходные распределители импульсов, счетчик импульсов, триггер, два ключа и передатчик радиосигналов из трех каналов, на приемной стороне содержащая антенну, блок управления, три тракта приема и обработки кодов видеосигнала, шесть блоков импульсных усилителей, блок модуляции излучений, делитель частоты, блок строчной развертки, первый усилитель и первый пьезодефлектор, блок кадровой развертки, второй усилитель и второй пьезодефлектор, матовый экран и блок раздельного наблюдения кадров, включающий очки, на корпусе которых закреплены последовательно соединенные фотоприемник ИК-излучения, формирователь импульса и пьезоэлектрический двигатель с валом, на котором закреплены две цилиндрические оправы с двумя нейтральными светофильтрами в каждой плотностью 4х из сеточек, и включающая канал формирования управляющих сигналов, два канала воспроизведения звука. Коды видеосигналов правого и левого кадров стереопары передаются по трем радиоканалам боковыми частотами двух несущих. Тактовая частота в системе 48 МГц. Передающая сторона формирует видеорежим 400строк×600отсч×50 Гц. На приемной стороне принимаются коды стереопар, выполняется удвоение отсчетов в строке и удвоение строк в кадре. На матовом экране электронно-оптической разверткой формируется видеорежим 800 строк×1200отсчетов×50 Гц. Частота правого и левого изображений по 25 Гц. Для получения стереоэффекта кадры стереопары рассматриваются зрителем раздельно. Поочередное перекрытие поля зрения глаз выполняется блоком раздельного наблюдения кадров механическим поворотом нейтральных светофильтров плотностью 4х, закрепленных в цилиндрических оправах, которые поворачиваются с дискретностью 90° и вращаются с частотой 3,125 об/с /187,5 об/мин/. Недостатками прототипа являются: формирование изображения проекцией на экран приводит к значительному снижению его яркости, раздельное наблюдение кадров через механически вращающиеся светофильтры ограничивают частоту следования стереопар 12,5 Гц и опасно для глаз.

Цель изобретения - исключить снижение яркости изображения от проекции и безынерционное управление раздельным наблюдением кадров стереопар.

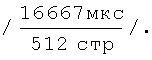

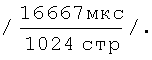

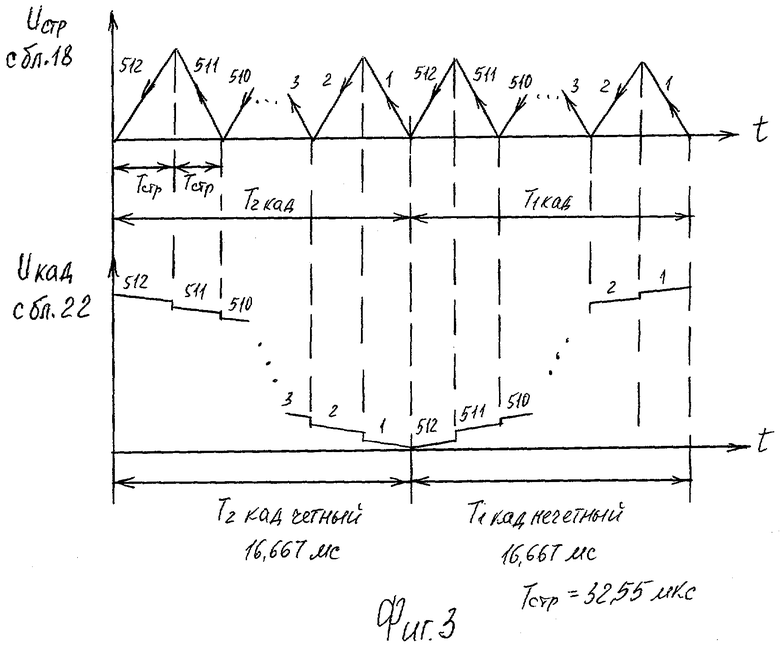

Техническим результатом является исключение снижения яркости изображения от проекции и электронное /безынерционное/ управление раздельным наблюдением кадров стереопар. Результат не снижения яркости изображения достигается применением в качестве экрана плоскопанельных дисплеев, основанных на технологиях жидких кристаллов /LСД/, плазменных /РДР/ или светодиодных элементах /LЕД/ [3, с.486], электронное управление достигается применением 3Д-очков с ИК-приемником на их оправе и ИК-передатчика [2, c.563-566]. В качестве плоскопанельного дисплея применяется /вариант/ ЖК-монитор с разрешением 1280×1024 точек [2, с.487, табл.14.5]. Передающая сторона формирует правый и левый кадры стереопары, коды которых передаются по трем радиоканалам боковыми частотами двух несущих частот. На передающей стороне в кадре кодируются 512 строк с 640 отсчетами. Тактовая частота 78,6432 МГц. Развертка строк построчная без обратных ходов, частота строк 30,72 кГц. Развертка кадров без обратных ходов, частота кадров 60 Гц, 30 правых и 30 левых. Частота стереопар 30 Гц. Дискретизация видеосигнала 19,6608 МГц, длительность кадра на передающей стороне и приемной 16,667 мс / /. Длительность строки на передающей стороне 32,55 мкс

/. Длительность строки на передающей стороне 32,55 мкс  На приемной стороне строк в кадре 1024, число отсчетов в строке 1280, длительность строки 16,28 мкс

На приемной стороне строк в кадре 1024, число отсчетов в строке 1280, длительность строки 16,28 мкс  Приемная сторона принимает три радиосигнала тремя трактами приема и обработки кодов, детектирует их, выделяет строчные синхроимпульсы ССИ и синхроимпульсы стереопар СИС, удваивает число отсчетов в строке и число строк в кадре, ЖК-монитор воспроизводит кадры стереопар, рассматриваемые зрителем раздельно. Между глазами и экраном ЖК-монитора размещаются электронно-управляемые 3Д-очки [2, с.558-566], в которых синхронно и синфазно со сменой кадров перекрывается поле зрения тому из глаз, кадр которого отсутствует.

Приемная сторона принимает три радиосигнала тремя трактами приема и обработки кодов, детектирует их, выделяет строчные синхроимпульсы ССИ и синхроимпульсы стереопар СИС, удваивает число отсчетов в строке и число строк в кадре, ЖК-монитор воспроизводит кадры стереопар, рассматриваемые зрителем раздельно. Между глазами и экраном ЖК-монитора размещаются электронно-управляемые 3Д-очки [2, с.558-566], в которых синхронно и синфазно со сменой кадров перекрывается поле зрения тому из глаз, кадр которого отсутствует.

Сущность изобретения в том, что в систему стереотелевидения, содержащую на передающей стороне фотоэлектрический преобразователь, 1-6 АЦП видеосигнала, 1-2 АЦП сигнала звука, генератор синусоидальных колебаний и синтезатор частот, три формирователя кодов, два самоходных распределителя импульсов, счетчик импульсов, триггер, два ключа и передатчик радиосигналов из трех каналов, на приемной стороне антенну, блок управления, 1-3 тракты приема и обработки кодов видеосигналов, 1-3 блоки импульсных усилителей, канал формирования управляющих сигналов и два канала воспроизведения звука, введены на передающей стороне второй счетчик импульсов, на приемной стороне ЖК-монитор, 3Д-очки с ИК-приемником на оправе очков и ИК-передатчик, расположенный над ЖК-монитором, в каждый канал видеосигнала введены первый и второй накопители кодов строки.

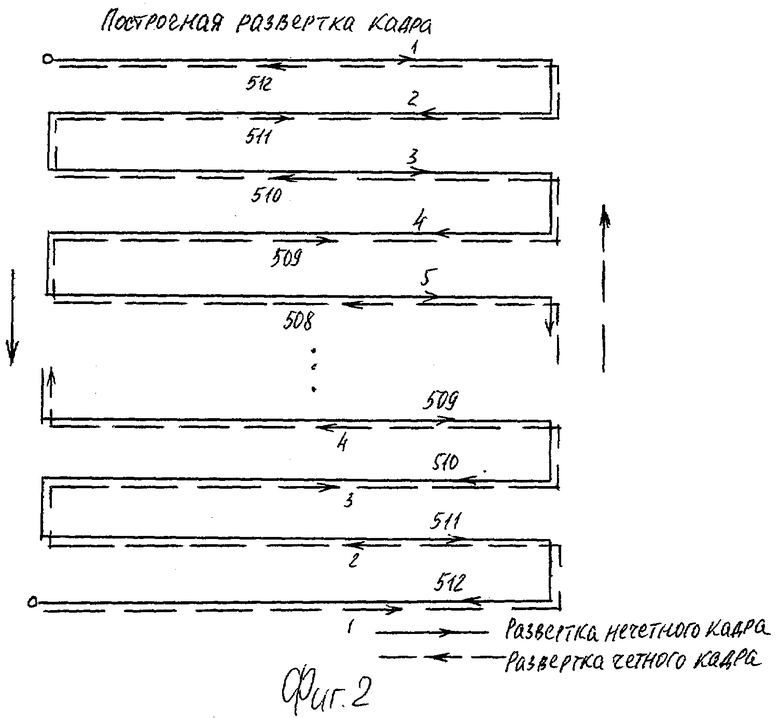

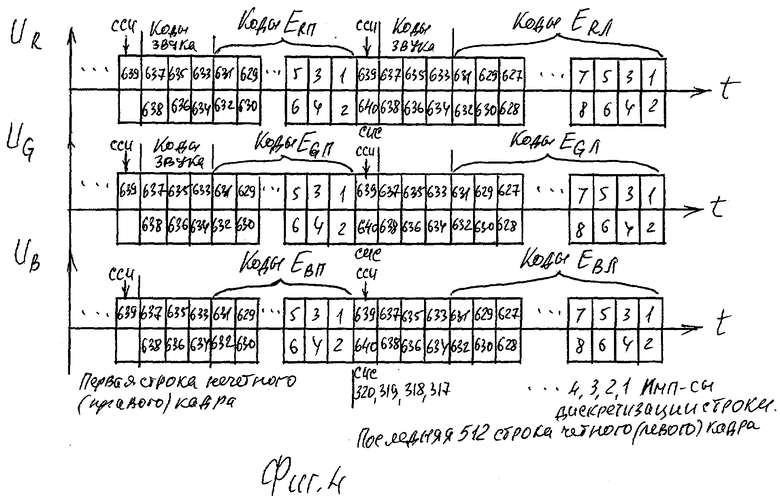

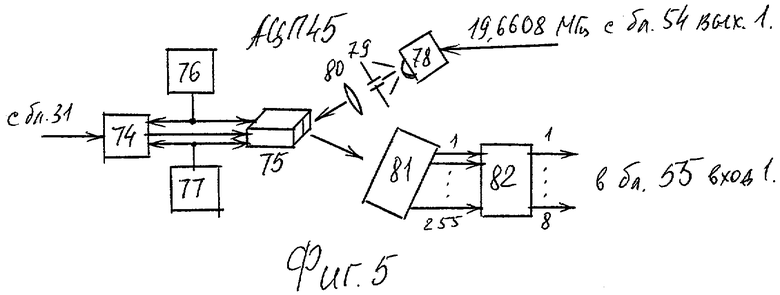

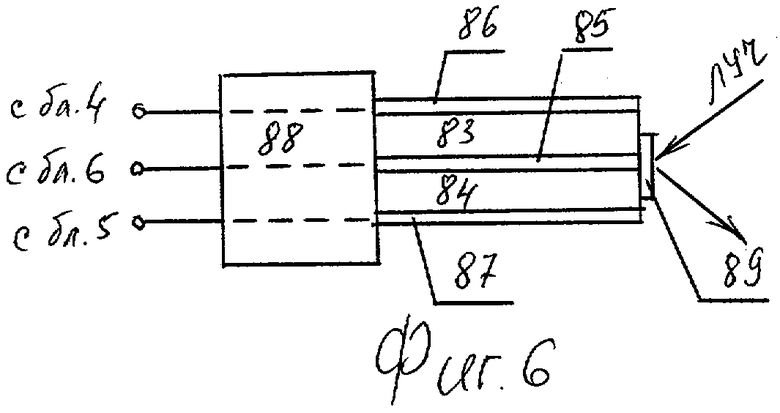

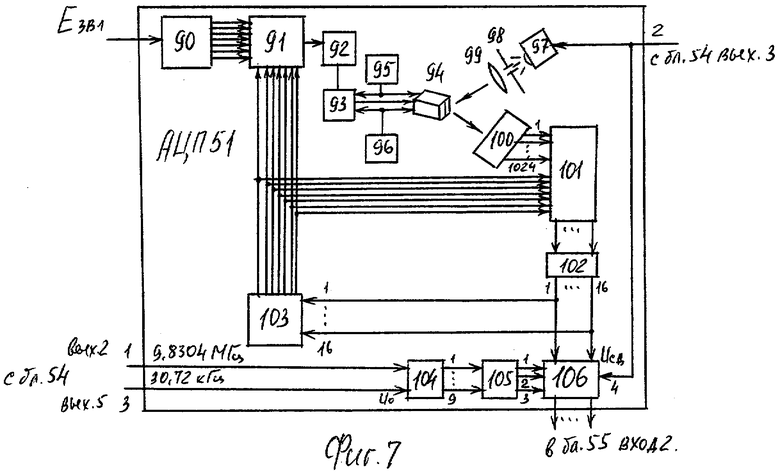

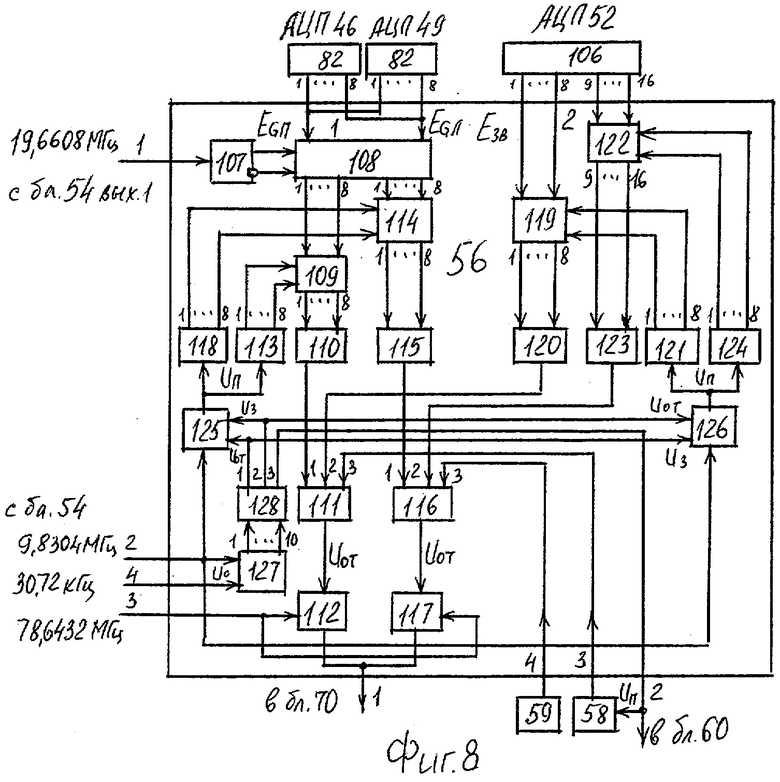

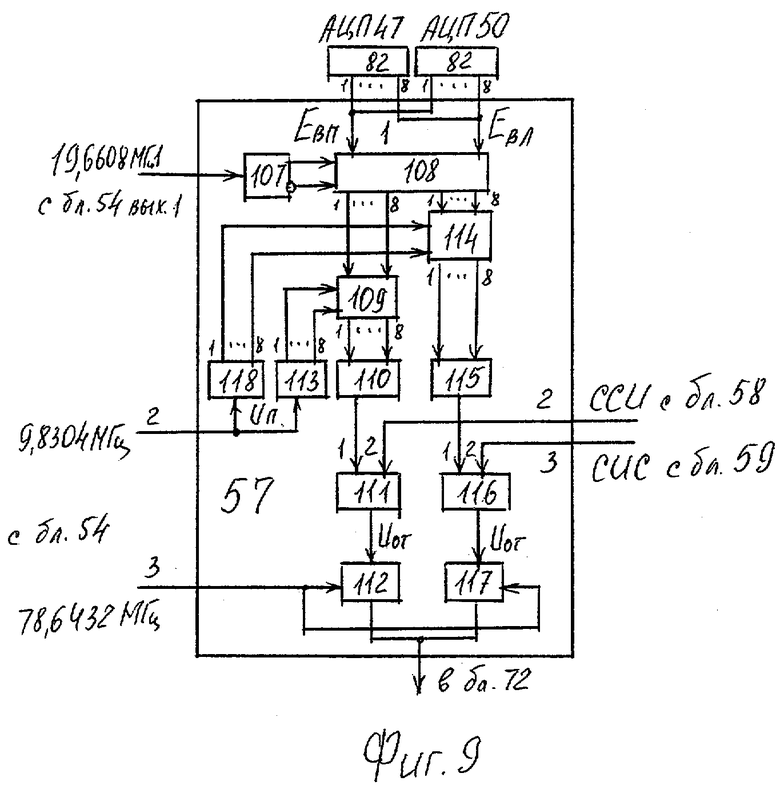

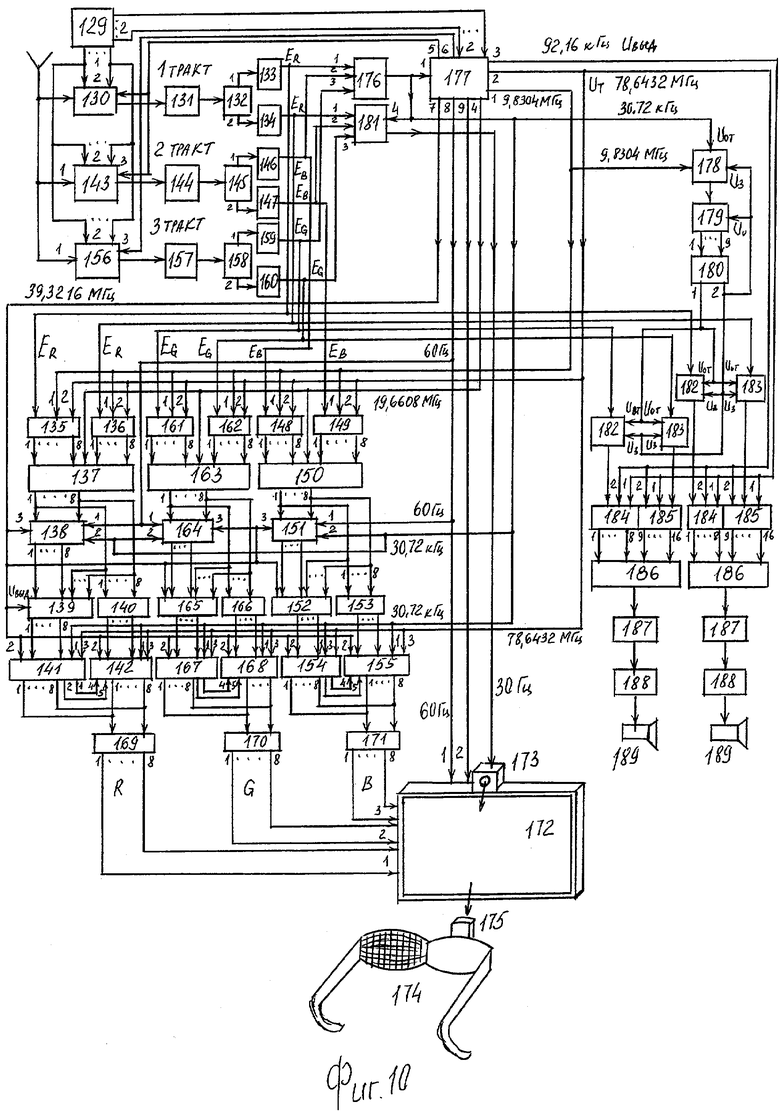

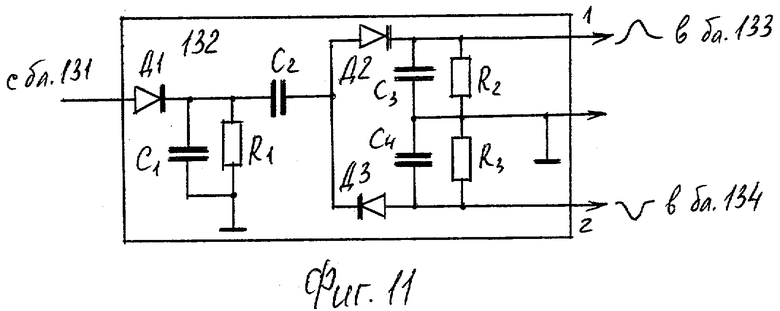

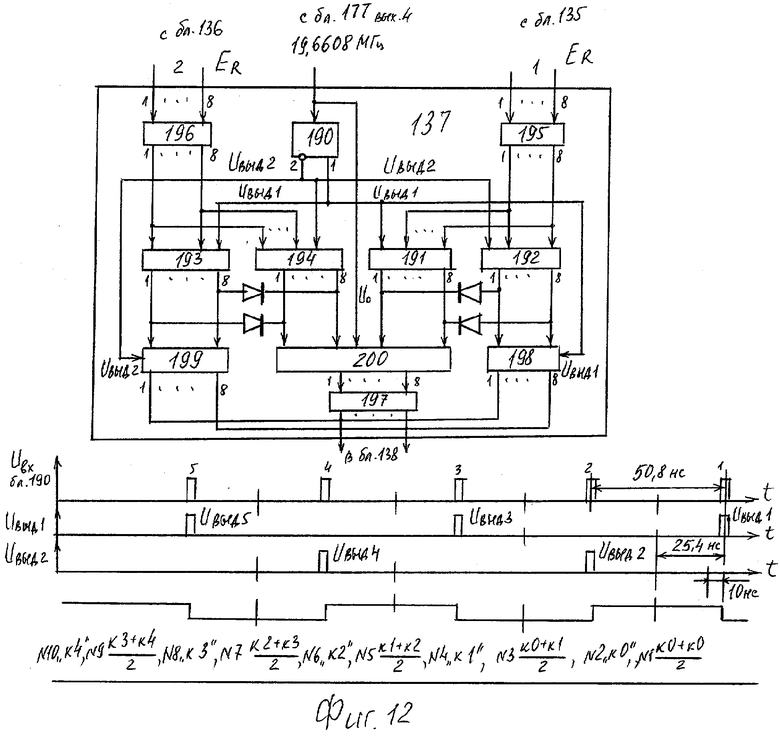

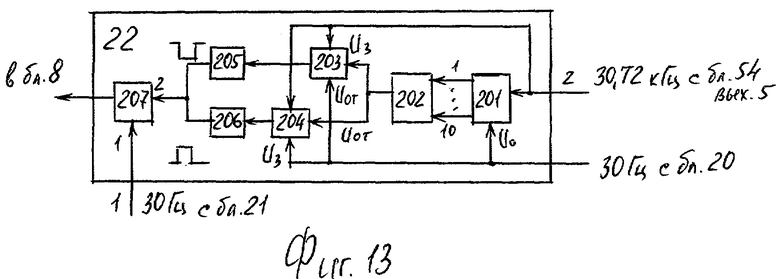

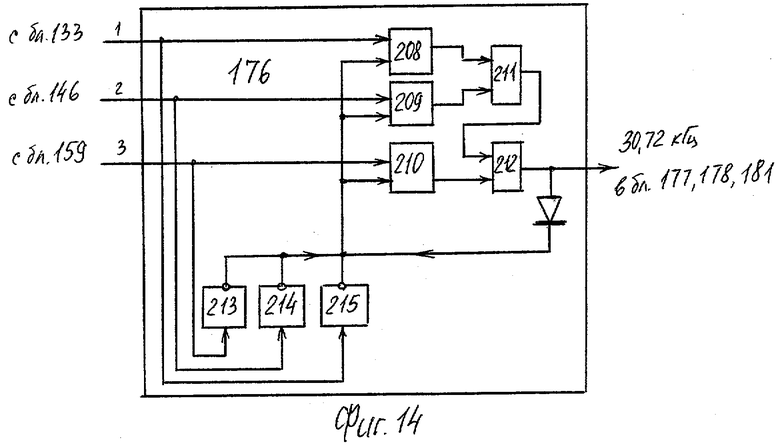

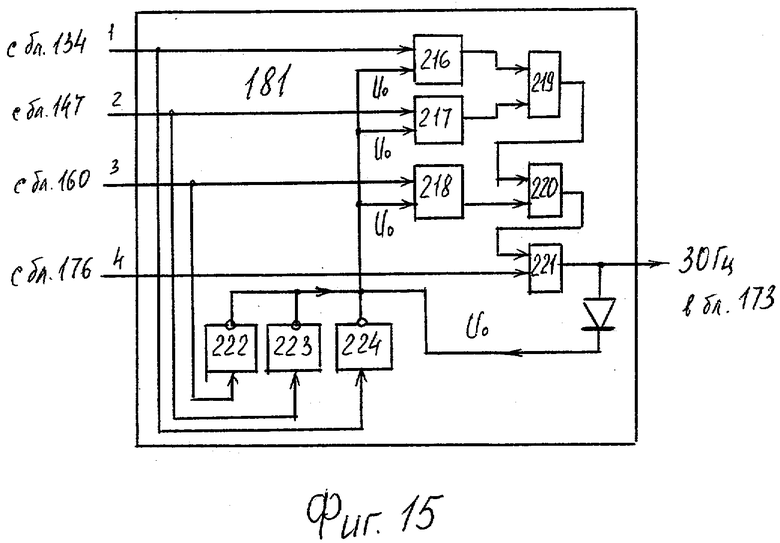

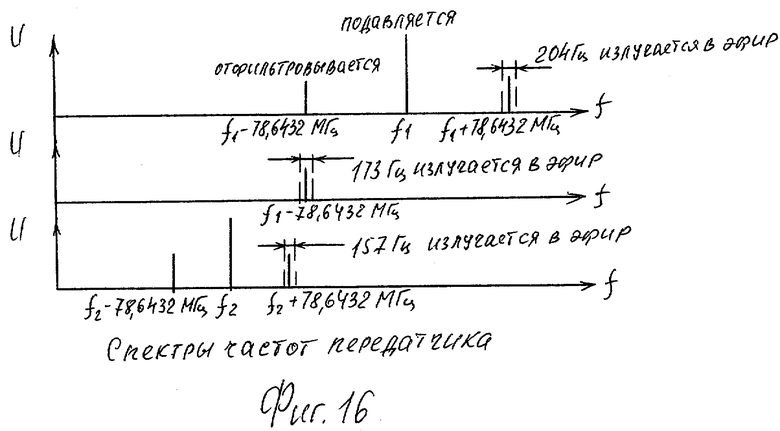

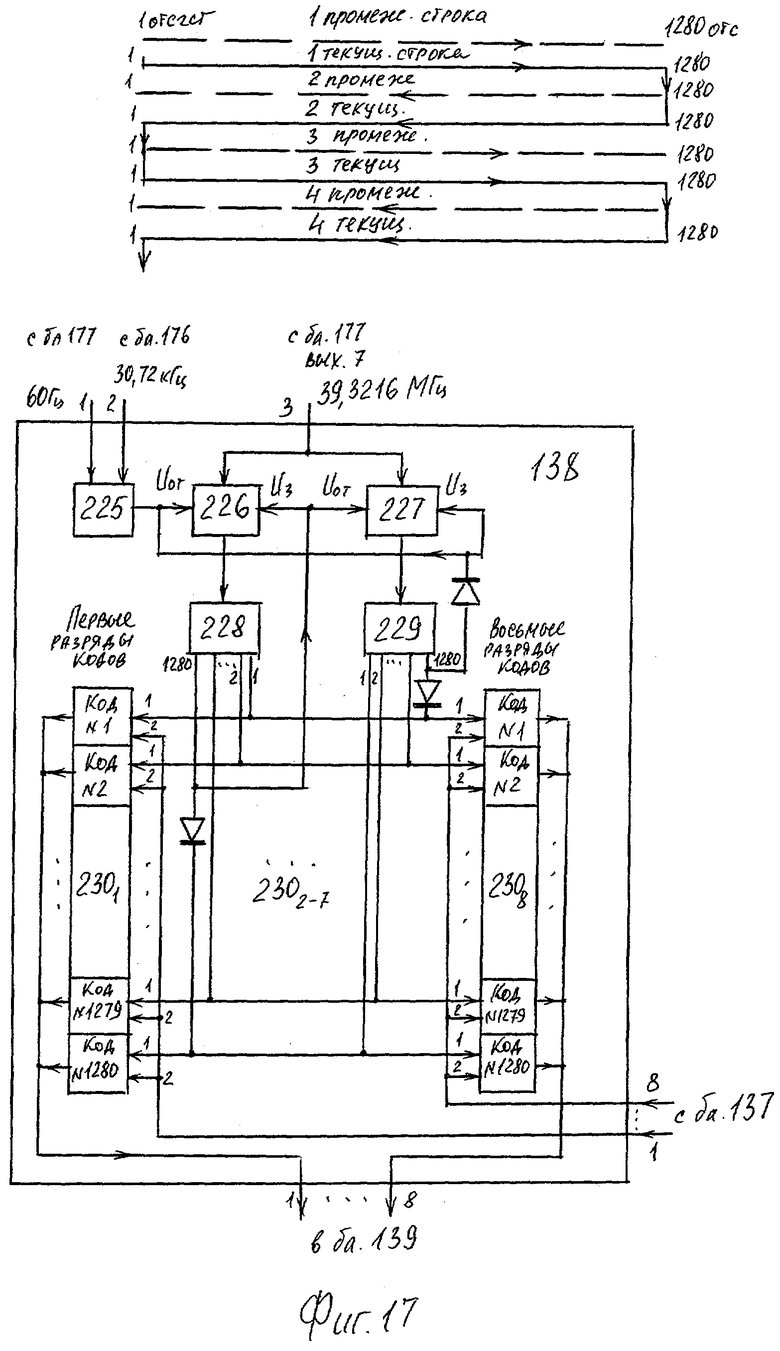

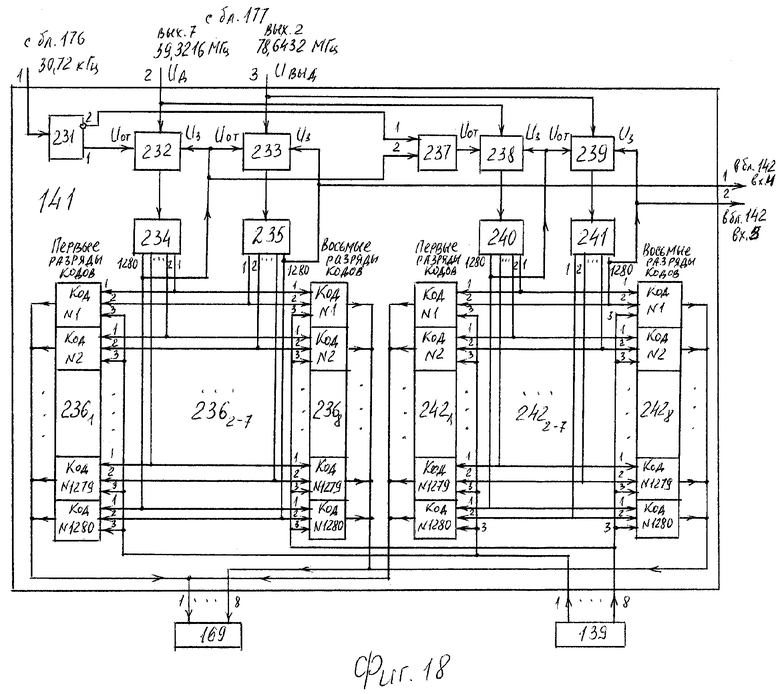

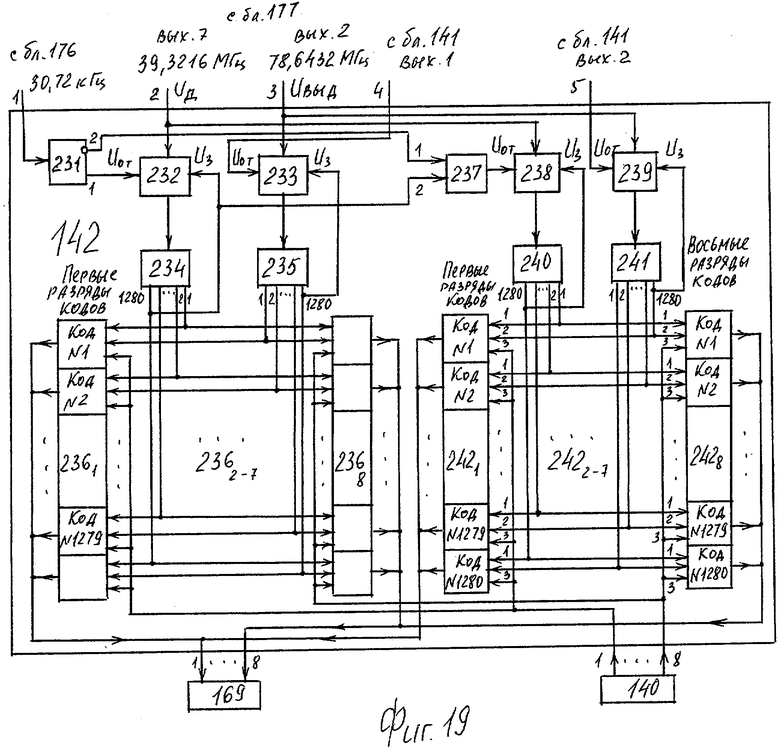

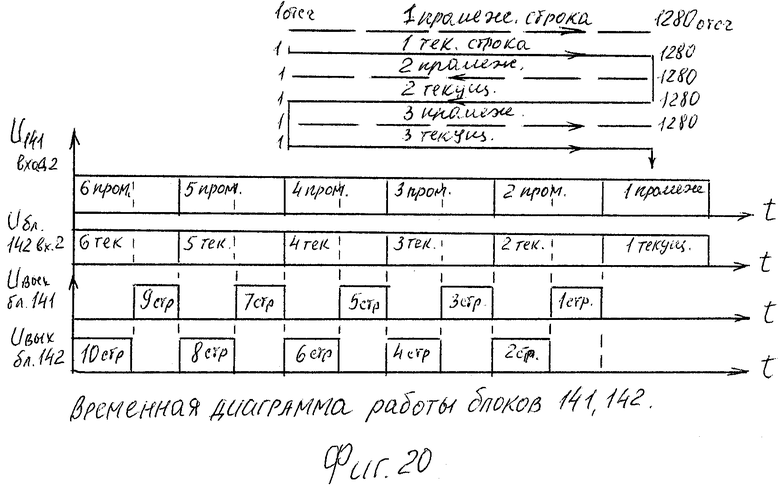

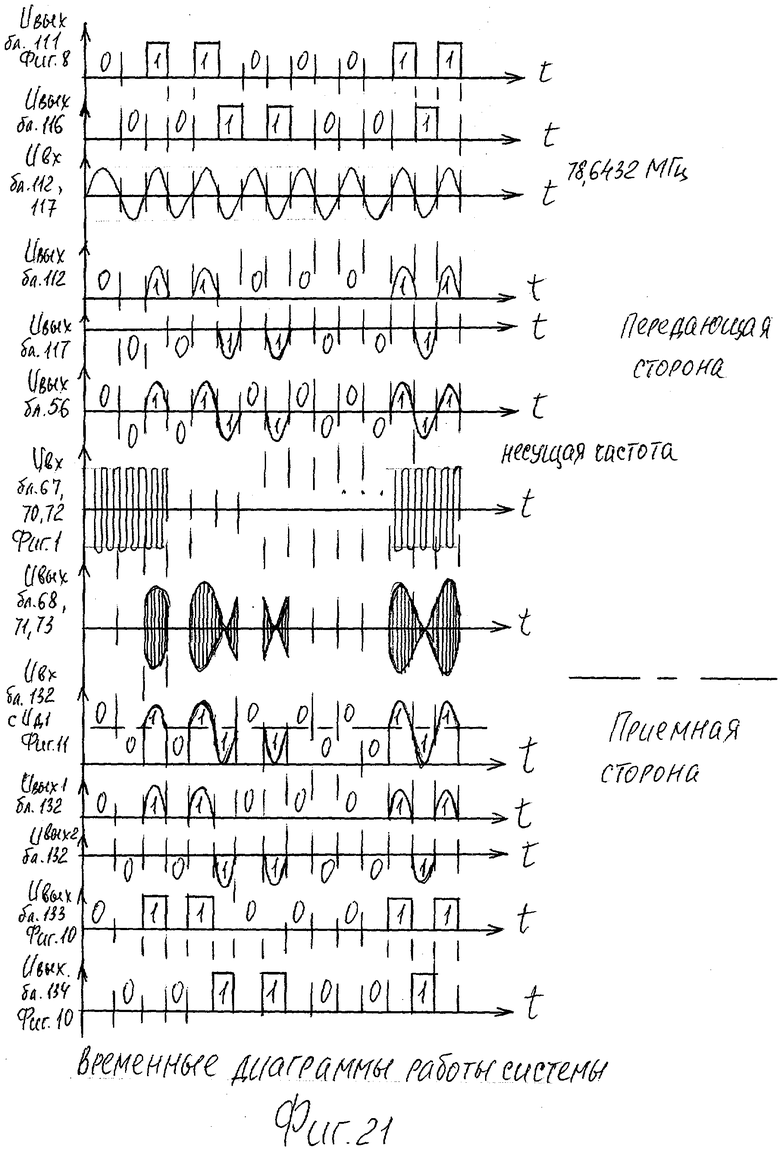

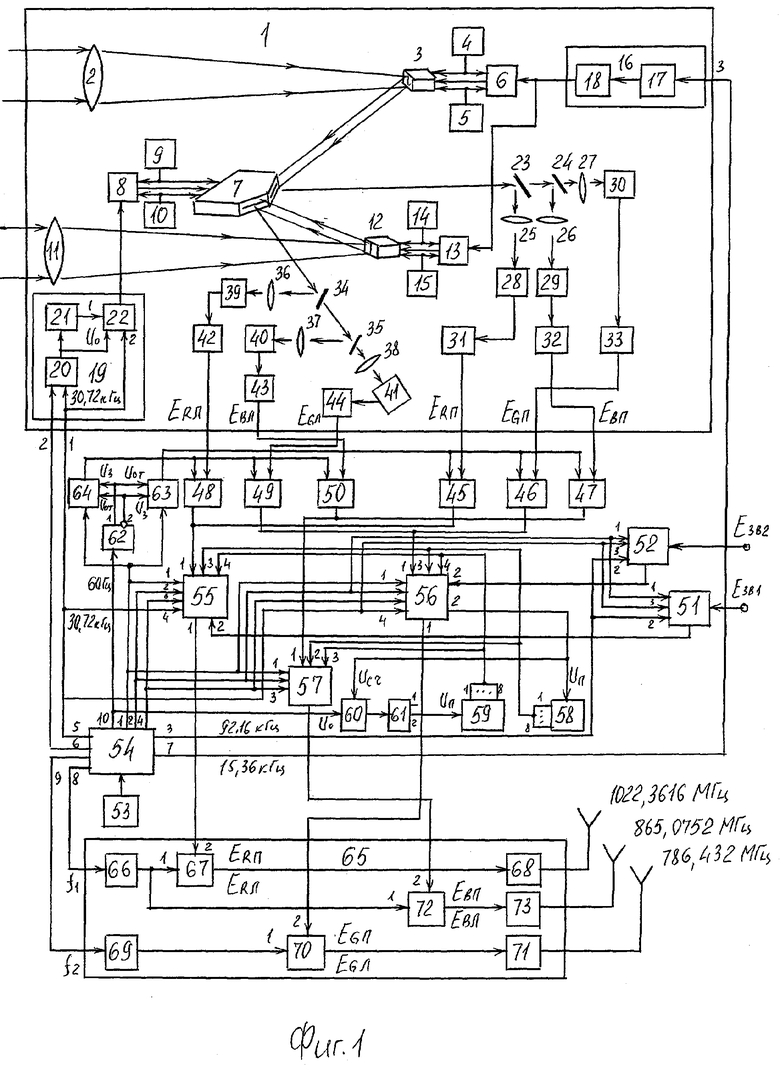

Передающая сторона на фиг.1, формирование растра кадра на фиг.2, формы управляющих напряжений разверток на фиг.3, структура цифровых потоков на фиг.4, АЦП видеосигнала на фиг.5, конструкция пьезодефлектора на фиг.6, АЦП сигнала звука на фиг.7, формирователь кодов ЕG и ЕR на фиг.8, формирователь кодов EB на фиг.9, приемная сторона на фиг.10, принципиальная схема двухполярного амплитудного детектора на фиг.11, блок обработки кодов на фиг.12, суммирующий усилитель на фиг.13, блок выделения строчных синхроимпульсов на фиг.14, блок выделения синхроимпульсов стереопар на фиг.15, спектры частот сигналов передатчика на фиг.16, первый блок задержек на фиг.17, накопители кодов строки на фиг.18 и 19, временная диаграмма удвоения строк на фиг.20, временная диаграмма работы системы на фиг.21.

Передающая сторона включает /фиг.1/ фотоэлектрический преобразователь 1, являющийся датчиком видеосигналов двух изображений одного объекта: правого /ЕRП, ЕGП, ЕВП/ и левого /ЕRЛ, ЕGЛ, ЕВЛ/, включающий первый объектив 2 /правый/, первый пьезодефлектор 3 с отражателем на торце, расположенный в фокальной плоскости правого объектива 2, первый источник 4 положительного опорного напряжения, второй источник 5 отрицательного опорного напряжения, первый усилитель 6, второй пьезодефлектор 7, передний торец которого имеет две грани, расположенные под соответствующим углом друг к другу и с отражателем на каждой грани, второй усилитель 8, третий источник 9 положительного опорного напряжения, четвертый источник 10 отрицательного опорного напряжения, второй объектив 11 /левый/, третий пьезодефлектор 12 с отражателем на торце, расположенный в фокальной плоскости второго объектива 11, третий усилитель 13, пятый источник 14 положительного опорного напряжения, шестой источник 15 отрицательного опорного напряжения, блок 16 строчной развертки из задающего генератора 17 и выходного каскада 18, блок 19 кадровой развертки, включающий элемент И 20, задающий генератор 21 и суммирующий усилитель 22, первое 23 и второе 24 дихроичные зеркала; первый 25, второй 26, третий 27 микрообъективы, первый 28, второй 29, третий 30 фотоприемники, первый 31, второй 32, третий 33 предварительные усилители, третье 34 и четвертое 35 дихроичные зеркала, четвертый 36, пятый 37, шестой 38 микрообъективы, четвертый 39, пятый 40, шестой 41 фотоприемники, четвертый 42, пятый 43 и шестой 44 предварительные усилители. Фотоэлектрический преобразователь 1 входит в состав передающей телевизионной камеры, в которую входят первый АЦП 45 /видеосигнал ЕRП/, второй АЦП 46 /видеосигнал EGП/, третий АЦП 47 /видеосигнал ЕВП /, четвертый АЦП 48 /видеосигнал ЕRЛ/, пятый АЦП 49 /видеосигнал ЕGЛ/, шестой АЦП 50 /видеосигнал ЕВЛ/. Второй объектив 11 расположен слева от первого объектива 2, оптическая ось его параллельна оптической оси объектива 2, расстояние между ними соответствует оптимальному получению стереоскопического эффекта, передающая сторона включает первый АЦП 51 и второй АЦП 52 сигнала звука, на входы которых поданы сигналы звукового сопровождения EЗВ1, ЕЗВ2, задающий генератор 53 синусоидальных колебаний, синтезатор 54 частот, первый 55, второй 56, третий 57 формирователи кодов соответственно ЕRП и ЕRЛ, ЕGП и ЕGЛ, ЕВП и ЕВЛ, первый 58 и второй 59 самоходные распределители импульсов, первый счетчик 61 импульсов, второй счетчик 60 импульсов, триггер 62, первый 63, второй 64 ключи, передатчик 65 радиосигналов, включающий три канала, первый канал включает последовательно соединенные усилитель 66 первой несущей частоты, амплитудный модулятор 67 и выходной усилитель 68, второй канал включает амплитудный модулятор 72 и выходной усилитель 73, третий канал включает последовательно соединенные усилитель 69 второй несущей частоты, амплитудный модулятор 70 и выходной усилитель 71. Каждый из амплитудных модуляторов 67, 70, 72 состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [4, с.234], отфильтровывающего одну из боковых частот в спектре амплитудно-модулированной несущей. Шесть АЦП 45-50 выполнены идентично /фиг.5/, каждый включает усилитель 74 и пьезодефлектор 75 с отражателем на торце, источник 76 положительного опорного напряжения, источник 77 отрицательного опорного напряжения, излучатель из импульсного светодиода 78, щелевой диафрагмы 79 и микрообъектива 80, линейку 81 многоэлементного фотоприемника и шифратор 82. Все пьезодефлекторы /3, 7, 12, 75, 94/ являются торцевыми биморфными пьезоэлементами со световым отражателем на свободном торце, конструктивно выполнены [5, c.118] одинаково /фиг.6/ из первой 83 и второй 84 пьезопластин, внутреннего электрода 85, первого 86 и второго 87 внешних электродов. Один конец пьезопластин закреплен в держателе 88, на свободном торце расположен световой отражатель 89. Свободный торец пьезодефлектора 7 выполнен из двух граней под соответствующим углом друг к другу, каждая грань имеет свой отражатель для разведения отраженных лучей в разные направления. АЦП 51, 52 выполнены идентично /фиг.7/, каждый содержит последовательно соединенные делитель 90 напряжения, блок 91 ключей, согласующий усилитель 92, усилитель 93 и пьезодефлектор 94 с отражателем на торце, источник 95 положительного опорного напряжения, источник 96 отрицательного опорного напряжения, излучатель из импульсного светодиода 97, щелевой диафрагмы 98 и микрообъектива 99, линейку 100 многоэлементного фотоприемника, первый дешифратор 101, шифратор 102 и второй дешифратор 103, последовательно соединенные счетчик 104 импульсов, третий дешифратор 105 и блок 106 регистров. Первый 55 и второй 56 формирователи кодов выполнены одинаково /фиг.8/, каждый включает последовательно соединенные триггер 107 и блок 108 коммутации и три канала, первый и второй каналы идентичны, первый включает последовательно соединенные блок 109 элементов И, первый 110, второй 111 элементы ИЛИ, выходной ключ 112 и самоходный распределитель 113 импульсов, второй канал включает блок 114 элементов И, третий 115, четвертый 116 элементы ИЛИ, выходной ключ 117 и самоходный распределитель 118 импульсов, третий канал включает два блока 119 и 122 элементов И, пятый 120 и шестой 123 элементы ИЛИ и два самоходных распределителя 121, 124 импульсов, включает первый 125, второй 126 ключи, последовательно соединенные счетчик 127 импульсов и дешифратор 128. В первом формирователе 55 кодов дешифратор 128 имеет первый и второй выходы, подключенные к соответствующим входам ключей 125, 126. Во втором формирователе 56 кодов дешифратор 128 также имеет первый и второй выходы, подключенные к входам ключей 125, 126, но имеет и третий выход, являющийся вторым выходом формирователя 56 кодов, подключенный к входу первого самоходного распределителя 58 импульсов и к счетному входу второго счетчика 60 импульсов. Первым и вторым информационными входами являются входы блока 108 коммутации и входы блоков 119, 122 элементов И, третьим и четвертым информационными входами являются третьи входы второго и четвертого элементов ИЛИ 111, 116. Управляющими входами являются: первым - вход триггера 107 /19,6608 МГЦ/, вторым - объединенные входы счетчика 127 импульсов и ключей 125, 126 /9,8304 МГЦ/, третьим - сигнальные входы выходных ключей 112, 117 /78,6432 МГц/, четвертым - управляющий вход счетчика 127 импульсов /30,72 кГц/. Выходом являются объединенные выходы выходных ключей 112, 117. Во втором формирователе 56 кодов вторым выходом является третий выход дешифратора 128. Третий формирователь 57 кодов содержит /фиг.9/ триггер 107, блок 108 коммутации и два канала. Каналы идентичны, первый включает блок 109 элементов И, первый 110, второй 111 элементы ИЛИ, выходной ключ 112 и самоходный распределитель 113 импульсов, второй канал включает блок 114 элементов И, третий 115 и четвертый 116 элементы ИЛИ, выходной ключ 117 и самоходный распределитель 118 импульсов. Первым информационным входом являются входы блока 108 коммутации, вторым и третьим информационными входами являются вторые входы второго 111 и четвертого 116 элементов ИЛИ. Первым управляющим входом является вход триггера 107 /19,6608 МГц/, вторым - объединенные входы самоходных распределителей 113, 118 импульсов /9,8304 МГЦ/, третьим - сигнальные входы выходных ключей 112, 117 /78,6432 МГЦ/, выходом являются объединенные выходы выходных ключей 112, 117.

Приемная сторона /фиг.10/ содержит антенну, блок 129 управления, первый, второй и третий тракты приема и обработки кодов видеосигналов, канал формирования управляющих сигналов, два канала воспроизведения звука и плоскопанельный дисплей - ЖК-монитор с активной матрицей, первый тракт приема и обработки кодов видеосигналов производит прием и обработку кодов видеосигналов ЕRП и ЕRЛ и включает последовательно соединенные блок 130 приема радиосигнала, усилитель 131 радиочастоты и двухполярный амплитудный детектор 132, первый 133 и второй 134 формирователи импульсов и канал видеосигнала ЕR, включающий первый 135 и второй 136 регистры видеосигнала ЕR, блок 137 обработки кодов, первый блок 138 задержек и сумматор 139, второй блок 140 задержек, первый 141 накопитель кодов строки и второй 142 накопитель кодов строки. Второй тракт приема и обработки кодов видеосигналов производит прием и обработку кодов видеосигналов ЕВП и BВЛ и включает последовательно соединенные блок 143 приема радиосигнала, усилитель 144 радиочастоты и двухполярный амплитудный детектор 145, первый 146 и второй 147 формирователи импульсов и канал видеосигнала BВ, включающий первый 148 и второй 149 регистры видеосигнала ЕВ, блок 150 обработки кодов, первый блок 151 задержек и сумматор 152, второй блок 153 задержек, первый 154 и второй 155 накопители кодов строки. Третий тракт приема и обработки кодов видеосигналов производит прием и обработку кодов видеосигналов ЕGП и ЕGЛ и включает последовательно соединенные блок 156 приема радиосигнала, усилитель 157 радиочастоты и двухполярный амплитудный детектор 158, первый 159, второй 160 формирователи импульсов и канал видеосигнала ЕG, включающий первый 161, второй 162 регистры видеосигнала EG, блок 163 обработки кодов, первый блок 164 задержек и сумматор 165, второй блок 166 задержек, первый 167 накопитель кодов строки и второй 168 накопитель кодов строки, приемная сторона включает первый 169, второй 170, третий 171 блоки импульсных усилителей, плоскопанельный ЖК-монитор 172 с расположенным на его корпусе ИК-передатчиком 173, 3Д-очки 174 и ИК-приемник 175, расположенный на оправе 3Д-очков. Входное окно ИК-приемника 175 расположено против выходного окна ИК-передатчика 173. Согласованный порядок работы приемной стороны выполняет канал формирования управляющих сигналов, содержащий последовательно соединенные блок 176 выделения строчных синхроимпульсов /ССИ/, синтезатор 177 частот, ключ 178, счетчик 179 импульсов и дешифратор 180 и блок 181 выделения синхроимпульсов стереопар /СИС/. Первый и второй каналы воспроизведения звука идентичны, каждый включает первый 182, второй 183 ключи, первый 184, второй 185 блоки регистров звука и последовательно соединенные цифроаналоговый преобразователь 186 /ЦАП/, фильтр 187 низкой частоты, усилитель 188 мощности и громкоговоритель 189.

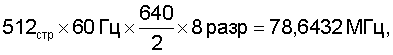

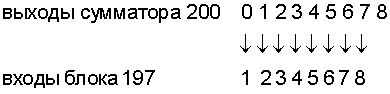

Блоки 137, 163, 150 обработки кодов идентичны, каждый включает /фиг.12/ триггер 190, первый 191, второй 192, третий 193, четвертый 194 регистры, первый 195, второй 196, третий 197 блоки элементов задержек, пятый 198 и шестой 199 регистры, сумматор 200 и 16 диодов. Блок 195 задерживает коды на 10 нс, блок 196 задерживает коды на 60,8 нс /50,8 нс+10 нс/, блок 197 задерживает коды на 1,4 нс. Регистры 198, 199 выполняют хранение кодов 50,8 нс и выдают их по сигналу UВЫД выдачи. Первым и вторым информационными входами являются входы блоков 195, 196 элементов задержек, выходом являются поразрядно объединенные выходы регистров 198, 199 и блока 197 элементов задержек. Управляющим входом является вход триггера 190. Суммирующий усилитель 22 /фиг.13/ включает 10-и разрядный счетчик 201 импульсов, дешифратор 202, первый 203, второй 204 ключи, первый 205, второй 206 формирователи импульсов и выходной усилитель 207. Первым информационным входом является первый вход выходного усилителя 207, вторым - счетный вход счетчика 201 импульсов. Управляющим входом являются объединенные входы управляющих входов ключей 203, 204 и управляющий вход счетчика 201 импульсов. Выходом суммирующего усилителя 22 является выход выходного усилителя 207. Блок 176 выделения строчных синхроимпульсов /фиг.14/ включает первый 208, второй 209, третий 210 счетчики импульсов, первый 211, второй 212 элементы И, первый 213, второй 214, третий 215 элементы НЕ и диод. Информационными 1-3 входами являются счетные входы счетчиков импульсов. Выходом является выход второго элемента И 212. С приходом на информационные входы трех кодов из одних единиц 11111111 на выходе блока 176 появляется строчный синхроимпульс ССИ, частота 30,72 кГц. Блок 181 выделения синхроимпульсов стереопар СИС /фиг.15/ содержит первый 216, второй 217, третий 218 счетчики импульсов, первый 219, второй 220, третий 221 элементы И, первый 222, второй 223, третий 224 элементы НЕ и диод. С приходом на счетные входы счетчиков 216, 217, 218 импульсов трех кодов 11111111 и строчного синхроимпульса на второй вход элемента И 221 на выходе блока 181 появляется синхроимпульс стереопары СИС, это 640-й отсчет в последней строке каждого четного /левого/ кадра на передающей стороне, частота СИС 30 Гц, предназначены для управления излучением ИК-передатчика 173. Первые блоки задержек 138, 151, 164 идентичны, каждый включает /фиг.17/ элемент И 225, первый 226, второй 227 ключи, первый 228 и второй 229 распределители импульсов и восемь регистров 2301-8 каждый из которых содержит 1280 разрядов для размещения в них по одному сигналу каждого разряда из 8-и разрядного кода отсчетов строки. Блоки 138, 151, 164 производят задержку кодов каждой строки на длительность отроки 32,55 мкс. Накопители 141, 142, 154, 155, 167, 168 кодов строки идентичны /фиг.18 и 19/, каждый включает триггер 231, первый 232 и второй 233 ключи, первый 234 и второй 235 распределители импульсов и первые восемь регистров 2361-8, каждый из которых содержит 1280 разрядов для размещения в них по одному сигналу каждого разряда из 8-и разрядного кода 1280 отсчетов строки, элемент И 237, третий 238 и четвертый 239 ключи, третий 240 и четвертый 241 распределители импульсов и вторые восемь регистров 2421-8, каждый содержит 1280 разрядов для размещения в них 1280 отсчетов отроки. Накопление кодов строки выполняют с частотой 39,3216 МГц при длительности строки 32,55 мкс, выдача кодов строки с регистров выполняется с частотой, в два раза большей 78,6432 МГц при длительности строки 16,28 мкс. Тактовая частота в системе:

где: 512 - число строк, кодируемых на передающей стороне,

60 Гц - частота кадров, 512×60 Гц=30,72 кГц - частота строк,  число кодируемых пар отсчетов в строке при двухполярной передаче кодов /фиг.4/.

число кодируемых пар отсчетов в строке при двухполярной передаче кодов /фиг.4/.

Фотоэлектрический преобразователь 1 формирует шесть аналоговых видеосигналов двух изображений, которые поступают с предварительных усилителей 31, 32, 33 в АЦП 45-47, с предварительных усилителей 42, 43, 44 в АЦП 48-50. Фотоэлектрический преобразователь 1 и шесть АЦП конструктивно размещены в передающей камере, с выходов которой следуют шесть двоичных кодов. АЦП преобразуют аналоговые видеосигналы в 8-и разрядные коды. Поочередная выдача кодов видеосигналов с АЦП 45-47 и с АЦП 48-50 выполняется триггером 62 и ключами 63, 64. Импульсы 60 Гц с десятого выхода синтезатора 54 частот поступают на вход триггера 62, сигнал с первого выхода которого открывает первый ключ 63, пропускающий в течение длительности одного кадра /16,667 мс/ импульсы дискретизации частотой 19,6608 МГц на тактовые входы АЦП 45, 46, 47, коды с которых поступают в формирователи 55, 56, 57 кодов. АЦП 48, 49, 50 в это время коды не выдают, на их тактовые входы импульсы не поступают. С приходом второго импульса 60 Гц в триггер 62 ключ 63 закрывается, открывается второй ключ 64, пропускающий импульсы дискретизации 19,6608 МГц на тактовые входы АЦП 48, 49, 50, коды с которых поступают и формирователи 55, 56, 57 кодов. Формирователи 55, 56, 57 кодов преобразуют параллельные коды с АЦП 45-50 и АЦП 51, 52 в последовательные и заменяют в них представление единиц с импульсов на положительные и отрицательные полусинусоиды моночастоты 78,6432 МГц с четвертого выхода синтезатора 54 частот. Задающий генератор 53 генерирует синусоидальные колебания со стабильностью 10-7.

Синтезатор 54 частот выдает с первого выхода импульсы дискретизации 19,6608 МГц на управляющие /тактовые/ входы АЦП 45-50 и на первые управляющие входы формирователей 55, 56, 57 кодов, со второго выхода импульсы 9,8304 МГц на вторые управляющие входы блоков 55, 56, 57 и на первые управляющие входы АЦП 51,52, с третьего выхода импульсы дискретизации сигналов звука 92,16 кГц на вторые входы АЦП 51, 52, с четвертого выхода синусоидальные колебания 78,6432 МГц на третьи управляющие входы блоков 55, 56, 57, с пятого выхода импульсы частоты строк 30,72 кГц на четвертые управляющие входы формирователей 55, 56 кодов, на первый вход блока 19 кадровой развертки и на третьи управляющие входы АЦП 51, 52, с шестого выхода импульсы 30 Гц на второй вход блока 19, с седьмого выхода импульсы 15,36 КГц на вход блока 16 строчной развертки, с восьмого выхода синусоидальные колебания 943,7184 МГЦ первой несущей частоты в усилитель 66 первой несущей частоты, с девятого выхода синусоидальные колебания 707,7888 МГц второй несущей частоты в усилитель 69 второй несущей частоты, с десятого выхода импульсы 60 Гц частоты кадров на вход триггера 62 и на управляющий вход второго счетчика 60 импульсов /UО/. АЦП 51, 52 преобразуют три сигнала звука в 16-и разрядные коды, которые поступают на вторые информационные входы формирователей 55, 56 кодов. Самоходный распределитель 58 импульсов с приходом сигнала UП пуска со второго выхода блока 56 /в момент 319 импульса дискретизации строки/ выдает код из восьми единиц 11111111, являющийся кодом строчного синхроимпульса ССИ на третьи информационные входы блоков 55, 56 и на второй информационный вход блока 57 /639-й отсчет в каждой строке/. Самоходный распределитель 59 импульсов с приходом сигнала UП пуска со второго выхода первого счетчика 61 импульсов выдает код из восьми единиц 11111111, являющийся кодом синхроимпульса стереопар /СИС/, 640-й отсчет последней строки каждого четного /левого/ кадра, фиг.4, на четвертые информационные входы формирователей 56, 56 кодов и на третий информационный вход третьего формирователя кодов 57. Счетчик 61 импульсов двухразрядный, выдает сигнал UП с второго выхода второго разряда в самоходный распределитель 59 импульсов с приходом в него второго счетного импульса с второго счетчика 60 импульсов. Второй счетчик 60 10-и разрядный производит счет 512 синхроимпульсов ССИ с блока 56, которых за кадр 512 штук. Двоичный код числа 512 представляет 1000000000. За время первого /правого/ кадра в счетчик 60 поступает 512 ССИ, со старшего разряда счетчика 60 в первый счетчик 61 поступает первый счетный импульс. Затем счетчик 60 обнуляется сигналом UО /60 Гц/. За второй /левый/ кадр в счетчик 60 поступают еще 512 ССИ, с его выхода следует второй счетный импульс на вход первого счетчика 61, который выдает со своего выхода сигнал UП пуска в самоходный распределитель 59 импульсов.

Спектр амплитудно-модулированного сигнала /фиг.16/ состоит из несущей и двух боковых частот. Одна из боковых частот и сама несущая в информационном смысле являются избыточными, поэтому в каждом амплитудном модуляторе 67, 70, 72 подавляется несущая частота [4, с.234) и отфильтровывается одна из боковых частот. Амплитудный модулятор 67 выдает в выходной усилитель 68 верхнюю боковую частоту 1022,3616 МГц от первой несущей. Амплитудный модулятор 72 выдает в выходной усилитель 73 нижнюю боковую частоту 865,0752 МГц от первой несущей. Амплитудный модулятор 70 выдает в выходной усилитель 71 верхнюю боковую частоту 786,432 МГц от второй несущей частоты.

Приемная сторона производит /фиг.10/ прием трех радиосигналов, усиливает их, детектирует по признаку полярности полусинусоид, разделяет коды по каналам, выделяет строчные синхроимпульсы ССИ и синхроимпульсы стереопар СИС, генерирует две несущие частоты, отделяет коды звуковых сигналов от кодов видеосигналов, удваивает число отсчетов в каждой строке с 640 до 1280, удваивает число строк в кадре с 512 до 1024 и воспроизводит правое и левое цветные изображения стереопар на экране ЖК-монитора со стереозвуковым сопровождением.

Объектив 2 /фиг.1/ создает правое цветное изображение в фокальной плоскости, в которой расположен отражатель первого пьезодефлектора 3. Ширина отражателя 0,02 мм, длина не менее 10,24 мм /0,02 мм×512 строк/. Размер разрешающего элемента в развертке строки 0,02×0,02 мм. По управляющим напряжениям /фиг.3/ с усилителя 6 пьезодефлектор 3 производит колебания торца с отражателем относительно первого отражателя на торце второго пьезодефлектора 7 с частотой 15,36 кГц, выполняя сканирование строки правого изображения. Объектив 11 создает левое цветное изображение в фокальной плоскости, в которой расположен отражатель третьего пьезодефлектора 12. Отражатель его имеет размеры, идентичные размерам отражателя пьезодефлектора 3. По управляющим напряжениям с усилителя 13 пьезодефлектор 12 производит колебания торца с отражателем относительно второго отражателя на торце второго пьезодефлектора 7 с частотой 15,36 кГц, выполняя сканирование строки левого изображения. Блок 16 строчной развертки выдает линейно изменяющееся напряжение /фиг.3/ в виде равнобедренного треугольника: напряжение сначала растет пропорционально времени, отражатели пьезодефлекторов 3 и 12 с равномерной скоростью синхронно и синфазно поворачиваются слева направо. По достижении края растра напряжение развертки уменьшается пропорционально времени, отражатели с той же скоростью возвращаются обратно. Период управляющего напряжения равен длительности двух строк, поэтому для построения растра в 512 строк при 60 кадрах в секунду пьезодефлекторы колеблются с частотой 15,36 кГц, а частота строк 30,72 кГц. За период колебания развертываются две строки. Развертка строк построчная /прогрессивная/ без обратных ходов /фиг.2/. Частота 15,36 кГц поступает в блок 16 с седьмого выхода блока 54. Блок 16 из задающего генератора 17 и выходного каскада 18. Сигнал с усилителя 6 /13/ поступает на внутренний электрод 85 пьезодефлектора /фиг.6/, к внешним электродам 86, 87 приложено напряжение с источников 4 и 5 /14 и 15/. При подаче управляющего напряжения на внутренний электрод 85 происходит деформация пьезопластин 83, 84 [5, с.122], торец со световым отражателем 89 приходит в колебательное движение. Изображения двух вертикальных строк поступают на два отражателя второго пьезодефлектора 7, выполняющего кадровую развертку, по вертикали, при развертке кадра вниз идут нечетные /правые/ кадры, при развертке кадра вверх идут четные /левые/ кадры. Ширина отражателей пьезодефлектора 7 по 0,02 мм, длина каждого не менее 12,8 мм /640 отсчетов×0,02 мм/. Пьезодефлектор 7 колеблется с частотой 30 Гц, что соответствует выполнению 60 кадров в секунду. Кадровая развертка также без обратных ходов /фиг.2/. С выхода суммирующего усилителя 22 выдается линейно изменяющееся и ступенчатое напряжение /фиг.3/, усиливаемое до необходимой величины усилителем 8. Суммирующий усилитель 22 суммирует /фиг.13/ линейное напряжение с задающего генератора 21 с импульсами строк 30,72 кГц. Каждый импульс строки перемещает строку в конце ее хода на шаг в одну строку в момент захода луча за край растра, получаются 512 строк в кадре. Назначение блоков с 201 по 206 подавать на второй вход выходного усилителя 207 в нужное время отрицательные при правых кадрах и положительные при левых кадрах импульсы нужной амплитуды и длительности, перед началом развертки стереопары счетчик 201 обнуляется. Счетчик 201 10-и разрядный производит счет строчных ССИ 30,72 кГц, цикл счета 1024 импульса. Сигнал UО при обнулении счетчика 201 открывает первый ключ 203, пропускающий строчные импульсы на вход первого формирователя 205 импульсов, выдающего отрицательные импульсы соответствующей амплитуды и длительности на второй вход выходного усилителя 207, следует развертка правого кадра стереопары. С приходом 512 импульса строки дешифратор 202 дешифрирует код числа 512 /1000000000/ и выходным сигналом закрывает ключ 203 и открывает ключ 204, пропускающий строчные импульсы во второй формирователь 206 импульсов, выдающий положительные импульсы на второй вход усилителя 207. Следует развертка левого кадра стереопары. С приходом сигнала UО процесс повторяется. Отраженные от первого отражателя пьезодефлектора 7 смешанные цветовые лучи направляются: красного цвета отражаются от первого дихроичного зеркала 23, объективом 25 собираются в фотоприемник 28, синего цвета проходят первое дихроичное зеркало 23, отражаются от второго 24 и объективом 26 собираются в фотоприемнике 29, зеленого цвета проходят сквозь оба зеркала 23, 24 и объективом 27 собираются в фотоприемнике 30. С фотоприемников видеосигналы поступают в свои предварительные усилители 31, 32, 33. Аналогичные процессы проходят цветовые лучи от второго отражателя пьезодефлектора 7, и аналоговые видеосигналы поступают в предварительные усилители 42, 43, 44. С них аналоговые видеосигналы поступают соответственно в АЦП 45-50, имеющие один принцип преобразования, заключающийся в развертке луча /фиг.5/ от светодиода 78 отражателем пьезодефлектора 75 по плоскости входных зрачков фотоприемников линейки 81 многоэлементного фотоприемника, световой импульс преобразуется в электрический сигнал, возбуждающий одну из входных шин шифратора 82, который выдает код мгновенного значения входного сигнала. Преобразование выполняется с дискретизацией 19,6608 МГц, импульсы дискретизации поступают на вход светодиода 78 с блока 54. Щелевая диафрагма 79 и микрообъектив 80 формируют луч апертурой, равной размерам одного входного окна фотоприемника линейки 81. Источником излучения принят импульсный светодиод АЛ402А с временем срабатывания 25 нс, с запасом, удовлетворяющим дискретизации 19,6608 МГц /52 нс/. Фотоприемниками в линейке являются лавинные фотодиоды ЛФД с временем срабатывания 10 нс. Линейка 81 содержит 255 фотоприемников для кодирования видеосигналов 8-и разрядным кодом. Выход каждого фотоприемника подключен к соответствующему входу шифратора 82. Шифратор представлен микросхемами К155ИВ1 с временем срабатывания 20 нс [6, с.231). Шифратор формирует коды с 00000001 по 11111111. Первому фотоприемнику в линейке соответствует код 00000001, второму - код 00000010, третьему - 00000011 и т.д. 255-у - код 11111111. Время преобразования 30 нс /10 нс+20 нс/ или 33·106 преоб/с, удовлетворяющее частоте 19,6608 МГц /52 нс/. АЦП 45-47 и АЦП 48-50, чередуясь, выдают правый и левый кадр. В период первого /правого/ кадра импульсы с выхода ключа 63 поступают на управляющие /тактовые/ входы АЦП 45-47, с них выдаются коды правого кадра стереопары, в период второго /левого/ кадра тактовые импульсы с ключа 64 поступают на управляющие входы АЦП 48-50, с них выдаются коды левого кадра стереопары. Скорость создания информации каждым АЦП составляет:

512строк×30 Гц×640отсч=9,8304 Мбайт/с.

АЦП 51, 52 преобразуют два сигнала звука в 16-и разрядные коды. За время одной строки каждый АЦП формирует три кода с дискретизацией 92,16 кГц. Для получения кодов с 16-ю разрядами изменяется коэффициент передачи делителя 90 напряжения. Делитель 90 /фиг.7/ представлен семиступенчатым резистивным делителем. Блок 91 ключей имеет семь ключей для подключения ступеней делителя 90 к согласующему усилителю 92. Линейка 100 многоэлементного фотоприемника содержит 1024 фотоприемника и преобразует сигнал звука в 10-и разрядный код 210. Разрешающая способность линейки принята 10 мкВ. Диапазон кодирования только линейкой составляет 0-0,01024 В. Преобразование в код сигналов, превышающих 210, выполняют первый дешифратор 101, шифратор 102, второй дешифратор 103, делитель 90 напряжения и блок 91 ключей, с их применением диапазон кодирования сигналов звука составляет 0-0,65536 В, т.е. 216. Импульс с каждого фотоприемника поступает в дешифратор 101, с него в шифратор 102. При отсутствии сигнала на входе делителя 90 на вход дешифратора 103 приходит код из одних нулей, сигнал с первого выхода дешифратора 103 открывает первый ключ в блоке 91, определяя этим коэффициент передачи 1,0 делителя 90. По достижении сигналом значения кода 210 появляется сигнал на втором выходе второго дешифратора 103, открывающий второй ключ в блоке 91 и закрывающий первый ключ, коэффициент становится 0,5, при коде 211 - коэффициент 0,25, при коде 212 - 0,125, при 213 - 0,0625, при 214 - 0,03125, при 215 - 0,015625, который остается до кода 216. При уменьшении амплитуды сигнала процесс обратный по возрастанию коэффициента передачи. Единицы в кодах представляются наличием импульса, нули - их отсутствием. За время одной строки шифратор 102 выдает три кода, поступающие друг за другом в блок 106, включающий три 16-и разрядных регистра. В процессе поступления коды сдвигаются из регистра в регистр сигналами UСД сдвига. В блоке 106 накапливаются три кода, которые друг за другом в моменты импульсов 317, 318, 319 дискретизации строки /фиг.4/ выдаются в первый 55 и второй 56 формирователи кодов. Сигналы выдачи приходят с третьего дешифратора 105 в моменты 317, 318, 319 импульсов дискретизации строки /9,8304 МГц/ с блока 54 выход 2. Сигналы выдачи формируют счетчик 104 импульсов и третий дешифратор 105. Счетчик 104 9-и разрядный, ведет счет 9,8304 МГц, цикл счета 320 импульсов дискретизации строки на передающей стороне. Обнуляется счетчик 104 импульсом U0 частоты строк 30,72 кГц в момент 320-го импульса дискретизации строки, первый формирователь 55 кодов выдает с 1 по 632 коды видеосигналов ЕRП и ERЛ, три кода звука, код ССИ /639-й отсчет строки/ и в последней 512 строке каждого четного кадра код СИС /640-й отсчет строки/, фиг.4. Единицы в кодах нечетных отсчетов строки представляются положительными полусинусоидами моночастоты 78,6432 МГц со стабильностью 10-7. Единицы в кодах четных отсчетов строки представляются отрицательными полусинусоидами той же частоты. Второй формирователь 56 кодов выдает с 1 по 632 коды видеосигналов ЕGП и ЕGЛ, три кода звука, код ССИ и в последней 512-й строке каждого четного /левого/ кадра код СИС /640-й отсчет строки/. Третий формирователь 57 кодов выдает с 1 по 632 коды видеосигналов EВП и EВЛ, код ССИ и код СИС, фиг.4.

Работа формирователей 56, 55 кодов /фиг.8/.

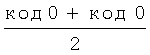

Коды с АЦП 45, 48 /46, 49/ поступают в параллельном виде с частотой 19,6608 МГц на входы блока 106 коммутации, разделяющего поток кодов 19,6608 МГц на два по 9,8304 МГц: первый поток - коды нечетных отсчетов, второй - коды четных отсчетов отроки. Блок 108 включает четыре микросхемы К176КТ1, являющиеся 4-х канальными коммутаторами с временем срабатывания 25 нс [7, с.222]. Выходы первых двух микросхем подключены к первым входам элементов И блока 109, выходы двух других микросхем подключены к первым входам элементов И блока 114. Поочередное подключение каналов к выходам блока 108 выполняет триггер 107, на вход которого поступают управляющие импульсы 19,6608 МГц с выхода 1 блока 54. На вторые входы элементов И блоков 109, 114 поступают последовательно восемь импульсов с первого 113 и второго 118 самоходных распределителей импульсов, имеющих по восемь разрядов, пусковыми импульсами для них являются 9,8304 МГц с выхода 2 блока 54, поступающие на второй управляющий вход. С выходов элементов И блоков 109, 114 импульсы кодов последовательно через элементы ИЛИ 110, 111 и 115, 116 открывают на время своей длительности 12,7 нс /109: 78,6432 МГц/ выходные ключи 112, 117. На сигнальные входы выходных ключей поступают синусоиды 78,6432 МГц. Первый выходной ключ 112 в открытом состоянии пропускает одну положительную полусинусоиду, второй выходной ключ 117 в открытом состоянии пропускает одну отрицательную полусинусоиду. На выходе формирователя кодов единицы в кодах нечетных отсчетах строки представляются положительными полусинусоидами, в кодах четных отсчетов строки представляются отрицательными полусинусоидами. Нули представляются отсутствием и тех и других. Выходной сигнал на выходе формирователей 55, 56 кодов представляются либо полными синусоидами частоты 78,6432 МГц, либо неполными синусоидами той же частоты, эти сигналы и модулируют несущие частоты: с формирователя 55 кодов модулируют первую несущую частоту в блоке 67, с формирователя 56 кодов - вторую несущую частоту в блоке 70 передатчика 65. Временные диаграммы процесса на фиг.21. Каждый код звука состоит из двух посылок по 8 разрядов. Первая посылка /половина кода звука/ 1-8 разряды поступает на первые входы элементов И блока 119 и через элементы ИЛИ 120, 111 поступает на вход первого выходного ключа 112, вторая посылка /вторая половина кода звука/ 9-16 разряды поступает на первые входы элементов И блока 122 и через элементы ИЛИ 123, 116 поступает на вход второго выходного ключа 117. Ключи 125, 126 предназначены для отделения кодов видеосигналов от кодов звука. Ключ 125 открывается сигналом с первого выхода дешифратора 128 в момент 320-го импульса дискретизации строки /фиг.4/ и остается открытым с 1-го по 316 импульс дискретизации строки /с 1-го по 632 отсчеты строки/. В момент 316 импульса дискретизации импульс со второго выхода дешифратора 128 закрывает ключ 125 и открывает ключ 126. В моменты 317, 318, 319 импульсов дискретизации строки три кода звука поступают на входы выходных ключей 112, 117. В момент 319 импульса дискретизации с 3-го выхода дешифратора 128 /в блоке 56/ выдается сигнал UП пуска в самоходный распределитель 58 импульсов, выдающий код ССИ на 3-й вход элементов ИЛИ 111. Каждый сигнал пуска поступает и как счетный импульс на вход второго счетчика 60 импульсов, по окончании первого /правого/ кадра счетчик 60 подсчитывает 512 сигналов UП и с выхода выдает импульс на счетный вход первого счетчика 61 импульсов, при подсчете 512 сигналов пуска во втором /левом/ кадре счетчик 60 выдает второй импульс в счетчик 61, который со второго выхода выдает сигнал UП в самоходный распределитель 59 импульсов, выдающий код СИС /11111111/ на третьи входы элементов ИЛИ 116 в блоках 55, 56, 57. Обнуляется счетчик 60 импульсов сигналом UО 60 Гц с десятого выхода блока 54. Самоходные распределители импульсов выполнены по [8, c.274]. Процесс работы формирователя 57 кодов аналогичен работе формирователя 55 кодов, но в нем не формируются коды звука, первый канал передатчика 65 радиосигналов излучает верхнюю боковую частоту 1022,3616 МГц от первой несущей с информацией кодов ЕRП и ЕRЛ, при стабильности несущей 10-7 занимает в эфире полосу ±102,2 Гц или 204,4 Гц. Второй канал излучает нижнюю боковую частоту 865,0752 МГц от первой несущей с информацией кодов EВП и ЕВЛ, занимаемая полоса в эфире ±86,5 Гц или 173 Гц. Третий канал излучает верхнюю боковую частоту 786,432 МГц от второй несущей с информацией кодов ЕGП и ЕGЛ, занимаемая полоса в эфире ±78,6 Гц или 157 Гц. В сумме занимаемая полоса 534,4 Гц. Три радиосигнала принимаются /фиг.10/ блоками 130, 143, 156 приема радиосигнала, являющиеся селекторами каналов дециметрового диапазона с электронной настройкой. Каждый блок включает входную цепь, усилитель радиочастоты и смеситель [9, с.86, рис.4.2]. Полосовой фильтр усилителя радиочастот в каждом диапазоне перестраивается подачей напряжения смещения на варикапы с электронного коммутатора блока 129 управления, являющегося блоком выбора программ. Усиленный радиочастотный сигнал поступает на смеситель, сюда же с синтезатора 177 частот подается частота, равная несущей на передающей стороне, необходимая для детектирования однополосного сигнала [10, с.146]. Выходной сигнал со смесителя является выходным сигналом с блоков 130, 143, 156, которые поступают на входы усилителей 131, 144, 157 радиочастоты, где усиливаются до необходимой величины и поступают на вход своего двухполярного амплитудного детектора 132, 145, 158. Вторые входы синтезатора 177 частот подключены к второй группе выходов блока 129. При включении канала передачи импульс с соответствующего выхода блока 129 определяет выход двух частот на третьи входы блоков 130, 143, первая несущая частота с выхода 5 блока 177, и третий вход блока 156, вторая несущая частота с выхода 6 блока 177. Двухполярные амплитудные детекторы 132, 145, 158 выполнены по принципиальной схеме фиг.11. Диод Д1 выделяет положительную огибающую модулирующего сигнала. Диод Д2 из модулирующей выделяет огибающие положительных полусинуиоид /символы единиц в кодах нечетных отсчетов/, диод Д3 из модулирующей выделяет огибающие отрицательных полуоинусоид /символы единиц в кодах четных отсчетах/. С первого выхода продетектированные положительные полусинусоиды частотой 78,6432 МГц поступают на вход первого формирователя 133 /146, 159/ импульсов, со второго выхода блока 132 /145, 158/ продетектированные отрицательные полусинусоиды поступают на вход второго формирователя 134 /147, 160/ импульсов. Формирователи импульсов выполнены по схеме несимметричного триггера с эмиттерной связью [11, с.209], формирующего прямоугольные импульсы из гармонически изменяющихся сигналов. Импульсы с формирователей импульсов имеют одну полярность и длительность, равную длительности импульсов в кодах на передающей стороне. Единицы в кодах представляются наличием импульса, нули - их отсутствием. После включения питания в приемной стороне ключи в закрытом состоянии. Порядок работы определяется сигналами управления с канала формирования управляющих сигналов. Задающая роль принадлежит блоку 176 выделения строчных синхроимпульсов ССИ. Условием "появления ССИ с блока 176 является одновременный приход в него с трех формирователей 133, 146, 159 кодов из восьми единиц. Во всех кодах, кроме ССИ, будут присутствовать один и более нулей, тем более в трех кодах одновременно, по каждому нулю в коде элементы НЕ /фиг.14/ будут обнулять счетчики импульсов в блоке 176. С приходом трех кодов 11111111 блок 176 выдает импульс, являющийся импульсом ССИ, частота их 30,72 кГц /частота строк/. ССИ открывает ключ 178, поступает на 4-й вход блока 181 выделения импульсов СИС и на первый вход синтезатора 177 частот. По синхроимпульсу ССИ выполняется синхронизация частоты в синтезаторе 177 частот. Собственная стабильность частоты синтезатора 177 частот 10-6. Подстройка под частоту и фазу задающего генератора передающей стороны производится по переднему фронту ССИ. Синтезатор 177 частот выдает с первого выхода импульсы дискретизации строки 9,8304 МГц, со второго выхода тактовые импульсы 78,6432 МГц, с третьего - импульсы 92,16 кГц выдачи кодов звука из блоков 184, 185 регистров, с четвертого - импульсы дискретизации видеосигналов 19,6608 МГц на управляющие входы блоков 137, 150, 163 обработки кодов, с пятого и шестого выходов синусоидальные колебания двух несущих частот на третьи входы блоков 130, 143, 156, с седьмого - импульсы 39,3216 МГц двойной частоты дискретизации видеосигналов, с восьмого выхода импульсы частоты кадров 60 Гц, с девятого - импульсы частоты строк 61,44 кГц для ЖК-монитора 172. Код нечетного отсчета ЕR с формирователя 133 импульсов поступает в последовательном виде в первый, регистр 135 видеосигнала ЕR, заполняя его разряды, код принимает параллельный вид. Код четного отсчета видеосигнала ЕR с формирователя 134 импульсов поступает во второй регистр 136 видеосигнала ЕR, заполняя его разряды, принимает параллельный вид. Аналогичные процессы проходят коды ЕG и ЕВ, заполняя регистры 161, 162 и 148, 149. Выдачу кодов из регистров выполняют импульсы 9,8304 МГц, они же и обнуляют регистры. Блоки 137, 150, 163 обработки кодов идентичны, производят удвоение числа отсчетов в каждой строке получением промежуточных /средних/ значений отсчетов между каждым прошедшим и следующим за ним кодами. Блоки выполняют сложение предыдущего и последующего кодов и деление кода суммы пополам. Работа блока 137 /150, 163/ на фиг.12. Коды нечетных отсчетов строки с регистра 135 через блок 195 элементов задержек /10 нс/ поступают параллельно в регистры 191, 192, коды четных отсчетов строки со второго регистра 136 через блок 196 элементов задержек /60,8 нс/ поступают параллельно в регистры 193, 194. Каждый код используется дважды: первый раз как предыдущий, второй раз как последующий, поэтому применяются четыре регистра 191-194. Перед началом работы в разрядах регистров нули. С приходом первого импульса /19,6608 МГц/ в триггер 190 с его первого выхода 1 сигнал Uвыд1 выдает из регистра 191 "код 0" /из одних нулей/ на первые входы сумматора 200, из регистра 193 "код 0" из нулей напрямую в шестой регистр 199 /для хранения/ и через диоды на вторые входы сумматора 200. Сигнал выдачи и обнуляют разряды регистров. Через 10 нс после выдачи кода из регистра 191 в регистры 191, 192 поступает первый код "код 1". Блок 195 задерживает коды на 10 нс для исключения наложения поступающего кода на выдаваемый. Блок 196 выполняет задержку кодов на 60,8 нс: задержка на 50,8 нс восстанавливает последовательность следования четного /второго/ кода за нечетным /первым/, из регистров 135, 136 они выдаются параллельно, и 10 нс для исключения наложения поступающего кода на выдаваемый. Сумматор 200 выполняет сложение кодов: код 0+код 0. В качестве сумматора применены микросхемы К555ИМ6 [6, с.258] с временем сложения 24 нс. При поступлении второго импульса на вход триггера 190 сигнал U0 выдает код суммы в блок 197 элементов задержек, который выполняет задержку кода на 1,4 нс, и обнуляет схемы сумматора 200. Деление кода суммы на 2 выполняется сдвигом кода суммы на один разряд так, чтобы отбрасывался младший разряд кода суммы /как при делении десятичного числа на десять/. Сдвиг выполняется подключением выходов сумматора к входам блока 197:

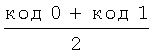

Разряд 0 означает перенос в него при суммировании кодов в сумматоре. При удвоении отсчетов в строке с 640 до 1280 период их следования составляет 25,4 нс /50,8 нс: 2/. Процесс сложения занимает 24 нс, следовательно, блок 197 должен задержать коды еще на 1,4 нс: 25,4 нс-24 нс. После поступления кодов в сумматор 200 на выход с блока 197 код следует через 25,4 нс. Код №1 представляет  . С поступлением второго импульса на вход триггера 190 с его второго выхода сигнал Uвыд2 одновременно выдает "код 0" из регистра 192 напрямую в пятый регистр /для хранения/ 198 и через диоды в сумматор 200, выдает "код 0" с шестого регистра 199 на выход, который является кодом №2 "код 0", и выдает из регистра 194 "код 0" в сумматор. Через 10 нс в регистры 193, 194 поступает "код 2". Регистры 198 и 199 хранят коды 50,8 нс, но первая половина хранения 25,4 нс приходится на процесс сложения в сумматоре 200 и задержку в блоке 197, поэтому код №2 следует за кодом №1 через 25,4 нс. Сумматор 200 выполняет сложение код 0+код 1, при выдаче кода суммы в блок 197 идет деление на два, и код №3

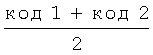

. С поступлением второго импульса на вход триггера 190 с его второго выхода сигнал Uвыд2 одновременно выдает "код 0" из регистра 192 напрямую в пятый регистр /для хранения/ 198 и через диоды в сумматор 200, выдает "код 0" с шестого регистра 199 на выход, который является кодом №2 "код 0", и выдает из регистра 194 "код 0" в сумматор. Через 10 нс в регистры 193, 194 поступает "код 2". Регистры 198 и 199 хранят коды 50,8 нс, но первая половина хранения 25,4 нс приходится на процесс сложения в сумматоре 200 и задержку в блоке 197, поэтому код №2 следует за кодом №1 через 25,4 нс. Сумматор 200 выполняет сложение код 0+код 1, при выдаче кода суммы в блок 197 идет деление на два, и код №3  выдается с блока 137. С приходом в триггер 190 третьего импульса сигнал Uвыд3 с его первого выхода одновременно выдает код №4 "код 1" с пятого регистра 198, выдает "код 1" с регистра 191 в сумматор и выдает "код 2" с регистра 193 в шестой регистр 199 и через диоды в сумматор 200. Следующий "код 3" заполняет регистры 191, 192. Сумматор выполняет сложение код 1+код 2, затем идет деление на 2, и код №5

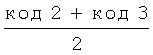

выдается с блока 137. С приходом в триггер 190 третьего импульса сигнал Uвыд3 с его первого выхода одновременно выдает код №4 "код 1" с пятого регистра 198, выдает "код 1" с регистра 191 в сумматор и выдает "код 2" с регистра 193 в шестой регистр 199 и через диоды в сумматор 200. Следующий "код 3" заполняет регистры 191, 192. Сумматор выполняет сложение код 1+код 2, затем идет деление на 2, и код №5  идет на выход. С приходом четвертого импульса в триггер 190 с его второго выхода сигнал Uвыд4 одновременно выдает код №6 "код 2" с регистра 199, выдает "код 2" с регистра 194 в сумматор и "код 3" с регистра 192 в регистр 198 и через диоды в сумматор 200. Следующий "код 4" заполняет регистры 193, 194. Сумматор выполняет сложение код 2+код 3, затем деление на 2, и код №7

идет на выход. С приходом четвертого импульса в триггер 190 с его второго выхода сигнал Uвыд4 одновременно выдает код №6 "код 2" с регистра 199, выдает "код 2" с регистра 194 в сумматор и "код 3" с регистра 192 в регистр 198 и через диоды в сумматор 200. Следующий "код 4" заполняет регистры 193, 194. Сумматор выполняет сложение код 2+код 3, затем деление на 2, и код №7  идет на выход. С приходом пятого импульса в триггер 190 с его первого выхода сигнал Uвыд5 одновременно выдает код №8 "код 3" с регистра 198, выдает "код 3" в сумматор, выдает "код 4" в регистр 199 и через диоды в сумматор 200. Следующий "код 5" заполняет регистры 191, 192, идет сложение в сумматоре "код 3+код 4", деление на 2, и код №9

идет на выход. С приходом пятого импульса в триггер 190 с его первого выхода сигнал Uвыд5 одновременно выдает код №8 "код 3" с регистра 198, выдает "код 3" в сумматор, выдает "код 4" в регистр 199 и через диоды в сумматор 200. Следующий "код 5" заполняет регистры 191, 192, идет сложение в сумматоре "код 3+код 4", деление на 2, и код №9  идет на выход. С приходом шестого и следующих импульсов в триггер 190 процессы повторяются. Выходы регистров 198, 199 и блока 197 поразрядно объединены, с их выходов коды в параллельном виде и с частотой следования 39,3216 МГц поступают в первый блок 138 задержек и во второй блок 140 задержек и на первые входы сумматора 139. Для удвоения строк в кадре необходимым условием является задержка кодов текущей строки относительно кодов следующей строки на ее длительность 32,55 мкс. Этот процесс решался бы просто при развертке всех строк кадра в одном направлении. В заявляемой системе направление разверток строк нечетных относительно четных строк встречное /фиг.17/. Первые блоки 138, 151, 164 задержек выполняют задержку кодов текущей строки на 32,55 мкс. С приходом с блока 177 импульса 60 Гц и импульса ССИ с блока 176 в элемент И 225 с его выхода сигнал UОТ открывает ключ 226, пропускающий импульсы 39,3216 МГц в распределитель 228 импульсов. Тактовые импульсы с распределителя 228 с 1-го по 1280 выходы последовательно поступают на первые /тактовые/ входы с 1-го по 1280 разряды восьми регистров 2301-8. На 1-8 информационные входы блока 138 /151, 164/ поступают сигналы кодов с 1 по 1280 отсчетов первой строки /нечетной/ с блока 137. Сигналы первого разряда кода поступают на вторые /информационные/ входы разрядов первого регистра 2301, сигналы 2-го разряда кода поступают на вторые входы разрядов второго регистра 2302 и т.д., сигналы восьмого разряда кодов поступают на вторые входы разрядов восьмого регистра 2308. По окончании первой строки 1280 разрядов регистров 2301-8 заполнены сигналами 1280 кодов строки. В период второй строки идет последовательная выдача 1280 кодов из восьми регистров 230 в сумматор 139 /152, 165/ при одновременном заполнении освобождающихся разрядов регистров сигналами кодов второй строки. Выдача сигналов выполняется передним фронтом тактового импульса, занесение сигналов поступающего кода производится этим же тактовым импульсом. В связи с тем что развертка второй строки идет встречно к первой строке, выдача кодов с регистров 230 производится в обратном порядке: не с 1-го разряда регистров, а с 1280-х разрядов регистров 2301-8. Заполнение освобождающихся разрядов регистров кодами второй строки также начинается с 1280-х разрядов. Осуществляется это вторым распределителем 229 импульсов, выходы которого подключены к тактовым /первым/ входам разрядов регистров в обратном порядке: первый выход подключен к 1280-м разрядам регистров, а 1280 выход подключен к первым разрядам регистров 230. При развертке третьей строки выдача кодов с регистров выполняется импульсами с распределителя 228, начиная с 1-го разряда регистров 2301-8, таким образом и осуществляется сложение кодов одноименных отсчетов строк, текущей и задержанной. На первые входы сумматора 139 /152, 165/ приходят коды текущей строки с блока 137, на вторые входы сумматора 139 приходят с блока 138 задержанные коды тех же отсчетов предыдущей строки. Сумматоры 139, 152, 165 идентичны, выполнены из микросхем К555ИМ6 с временем сложения 24 нс. Деление кода суммы на 2 выполняется подключением выхода сумматора к входам своего накопителя 141 /154, 167/ кодов строки так, что отбрасывается младший разряд в коде суммы, аналогично подключению сумматора 200 к блоку 197 на фиг.12. Вторые блоки задержек 140, 153, 166 выполняют задержку кодов на 24 нс, на время срабатывания сумматоров 139, 152, 165, чтобы коды промежуточной строки и коды текущей строки приходили на входы своих накопителей 141 и 142 /154, 155 и 167, 168/ кодов строки синхронно. Накопители 141, 142, 154, 155, 167, 168 работают синхронно, фиг.18. Синхроимпульс ССИ строки с блока 176 /30,72 кГц/ поступает на вход триггера 231, сигнал с первого выхода которого открывает первый ключ 232, пропускающий на вход первого распределителя 234 импульсов частоту 39,3216 МГц импульсов дискретизации. Тактовые импульсы с 1280 выходов распределителя 234 последовательно с 1-го по 1280 выходы поступают на первые /тактовые/ входы разрядов первых восьми регистров 2361-8 /фиг.18/. На 1-8 информационные входы блока 141 поступают коды первой промежуточной строки с сумматора 139. С 1-8 входов на третьи /информационные/ входы разрядов регистров 2361-8 поступают коды отсчетов промежуточной строки. В момент заполнения последнего разряда в регистрах 236 сигнал с 1280-го выхода блока 234 закрывает ключ 232, открывает ключ 233 и поступает на второй вход элемента И 237. С выходов распределителя 235 импульсы 78,6432 МГц Uвыд последовательно, начиная с 1-го выхода, поступают на вторые управляющие входы разрядов регистров 2361-8 и выдают с 1-го по 1280 коды с регистров в блок 169 импульсных усилителей. Частота выдачи кодов импульсами с распределителя 235 в два раза выше частоты тактовых импульсов с распределителя 234: длительность строки при заполнении регистров 2361-8 32,55 мкс, при выдаче кодов в блок 169 длительность строки составляет 16,28 мкс /фиг.20/. В момент выдачи 1280-го кода сигнал с 1280-го выхода блока 235 закрывает ключ 233, он же является первым управляющим выходом блока 141. По заполнению регистров 236 /окончание первой строки/ на вход триггера 231 поступает второй импульс ССИ. На первый и второй входы элемента И 237 поступают два импульса: с второго выхода триггера 231 и с 1280 выхода блока 234. Сигнал с элемента И 237 открывает ключ 238, пропускающий в распределитель 240 импульсы дискретизации 39,3216 МГц. С сумматора 139 на входы блока 141 в это время поступают коды второй промежуточной строки, идет заполнение разрядов вторых восьми регистров 2421-8. По заполнении регистров 242 импульс с 1280-го выхода блока 240 закрывает ключ 238 и открывает ключ 239, пропускающий импульсы 78,6432 МГц в распределитель 241 импульсов, сигналы с выходов которого выдают коды второй промежуточной строки в блок 169, причем выдача идет с последнего 1280-го кода строки к первому, что выполняется подключением выходов блока 241 к вторым входам разрядов регистров 2421-8 в обратном порядке, начиная с последнего разряда регистров к первому выходу блока 241, по выдаче первого кода с регистров 2421-8 сигнал с 1280 выхода блока 241 закрывает ключ 239 и является вторым управляющим выходом с блока 141. При поступлении на вход триггера 231 третьего импульса ССИ импульс с первого его выхода открывает ключ 232, следует аналогичный процесс заполнения регистров 236 кодами третьими промежуточной строки, затем регистров 242 кодами четвертой промежуточной строки и выдачи кодов этих отрок с регистров соответственно 236, 242 в блок 169. Параллельно идут такие же процессы в блоке 142 /155, 168/ заполнения регистров 236 и 242 кодами первой и второй текущих строк /фиг.19/ с той разницей, что ключ 233 открывается для выдачи кодов первой строки управляющим сигналом с входа 4, на который управляющий сигнал приходит с первого управляющего выхода блока 141, а ключ 239 для выдачи кодов второй строки открывается управляющим сигналом с входа 5, на который сигнал приходит с второго управляющего выхода блока 141. Процессы работы накопителей 141, 142 представлены временной диаграммой на фиг.20.

идет на выход. С приходом шестого и следующих импульсов в триггер 190 процессы повторяются. Выходы регистров 198, 199 и блока 197 поразрядно объединены, с их выходов коды в параллельном виде и с частотой следования 39,3216 МГц поступают в первый блок 138 задержек и во второй блок 140 задержек и на первые входы сумматора 139. Для удвоения строк в кадре необходимым условием является задержка кодов текущей строки относительно кодов следующей строки на ее длительность 32,55 мкс. Этот процесс решался бы просто при развертке всех строк кадра в одном направлении. В заявляемой системе направление разверток строк нечетных относительно четных строк встречное /фиг.17/. Первые блоки 138, 151, 164 задержек выполняют задержку кодов текущей строки на 32,55 мкс. С приходом с блока 177 импульса 60 Гц и импульса ССИ с блока 176 в элемент И 225 с его выхода сигнал UОТ открывает ключ 226, пропускающий импульсы 39,3216 МГц в распределитель 228 импульсов. Тактовые импульсы с распределителя 228 с 1-го по 1280 выходы последовательно поступают на первые /тактовые/ входы с 1-го по 1280 разряды восьми регистров 2301-8. На 1-8 информационные входы блока 138 /151, 164/ поступают сигналы кодов с 1 по 1280 отсчетов первой строки /нечетной/ с блока 137. Сигналы первого разряда кода поступают на вторые /информационные/ входы разрядов первого регистра 2301, сигналы 2-го разряда кода поступают на вторые входы разрядов второго регистра 2302 и т.д., сигналы восьмого разряда кодов поступают на вторые входы разрядов восьмого регистра 2308. По окончании первой строки 1280 разрядов регистров 2301-8 заполнены сигналами 1280 кодов строки. В период второй строки идет последовательная выдача 1280 кодов из восьми регистров 230 в сумматор 139 /152, 165/ при одновременном заполнении освобождающихся разрядов регистров сигналами кодов второй строки. Выдача сигналов выполняется передним фронтом тактового импульса, занесение сигналов поступающего кода производится этим же тактовым импульсом. В связи с тем что развертка второй строки идет встречно к первой строке, выдача кодов с регистров 230 производится в обратном порядке: не с 1-го разряда регистров, а с 1280-х разрядов регистров 2301-8. Заполнение освобождающихся разрядов регистров кодами второй строки также начинается с 1280-х разрядов. Осуществляется это вторым распределителем 229 импульсов, выходы которого подключены к тактовым /первым/ входам разрядов регистров в обратном порядке: первый выход подключен к 1280-м разрядам регистров, а 1280 выход подключен к первым разрядам регистров 230. При развертке третьей строки выдача кодов с регистров выполняется импульсами с распределителя 228, начиная с 1-го разряда регистров 2301-8, таким образом и осуществляется сложение кодов одноименных отсчетов строк, текущей и задержанной. На первые входы сумматора 139 /152, 165/ приходят коды текущей строки с блока 137, на вторые входы сумматора 139 приходят с блока 138 задержанные коды тех же отсчетов предыдущей строки. Сумматоры 139, 152, 165 идентичны, выполнены из микросхем К555ИМ6 с временем сложения 24 нс. Деление кода суммы на 2 выполняется подключением выхода сумматора к входам своего накопителя 141 /154, 167/ кодов строки так, что отбрасывается младший разряд в коде суммы, аналогично подключению сумматора 200 к блоку 197 на фиг.12. Вторые блоки задержек 140, 153, 166 выполняют задержку кодов на 24 нс, на время срабатывания сумматоров 139, 152, 165, чтобы коды промежуточной строки и коды текущей строки приходили на входы своих накопителей 141 и 142 /154, 155 и 167, 168/ кодов строки синхронно. Накопители 141, 142, 154, 155, 167, 168 работают синхронно, фиг.18. Синхроимпульс ССИ строки с блока 176 /30,72 кГц/ поступает на вход триггера 231, сигнал с первого выхода которого открывает первый ключ 232, пропускающий на вход первого распределителя 234 импульсов частоту 39,3216 МГц импульсов дискретизации. Тактовые импульсы с 1280 выходов распределителя 234 последовательно с 1-го по 1280 выходы поступают на первые /тактовые/ входы разрядов первых восьми регистров 2361-8 /фиг.18/. На 1-8 информационные входы блока 141 поступают коды первой промежуточной строки с сумматора 139. С 1-8 входов на третьи /информационные/ входы разрядов регистров 2361-8 поступают коды отсчетов промежуточной строки. В момент заполнения последнего разряда в регистрах 236 сигнал с 1280-го выхода блока 234 закрывает ключ 232, открывает ключ 233 и поступает на второй вход элемента И 237. С выходов распределителя 235 импульсы 78,6432 МГц Uвыд последовательно, начиная с 1-го выхода, поступают на вторые управляющие входы разрядов регистров 2361-8 и выдают с 1-го по 1280 коды с регистров в блок 169 импульсных усилителей. Частота выдачи кодов импульсами с распределителя 235 в два раза выше частоты тактовых импульсов с распределителя 234: длительность строки при заполнении регистров 2361-8 32,55 мкс, при выдаче кодов в блок 169 длительность строки составляет 16,28 мкс /фиг.20/. В момент выдачи 1280-го кода сигнал с 1280-го выхода блока 235 закрывает ключ 233, он же является первым управляющим выходом блока 141. По заполнению регистров 236 /окончание первой строки/ на вход триггера 231 поступает второй импульс ССИ. На первый и второй входы элемента И 237 поступают два импульса: с второго выхода триггера 231 и с 1280 выхода блока 234. Сигнал с элемента И 237 открывает ключ 238, пропускающий в распределитель 240 импульсы дискретизации 39,3216 МГц. С сумматора 139 на входы блока 141 в это время поступают коды второй промежуточной строки, идет заполнение разрядов вторых восьми регистров 2421-8. По заполнении регистров 242 импульс с 1280-го выхода блока 240 закрывает ключ 238 и открывает ключ 239, пропускающий импульсы 78,6432 МГц в распределитель 241 импульсов, сигналы с выходов которого выдают коды второй промежуточной строки в блок 169, причем выдача идет с последнего 1280-го кода строки к первому, что выполняется подключением выходов блока 241 к вторым входам разрядов регистров 2421-8 в обратном порядке, начиная с последнего разряда регистров к первому выходу блока 241, по выдаче первого кода с регистров 2421-8 сигнал с 1280 выхода блока 241 закрывает ключ 239 и является вторым управляющим выходом с блока 141. При поступлении на вход триггера 231 третьего импульса ССИ импульс с первого его выхода открывает ключ 232, следует аналогичный процесс заполнения регистров 236 кодами третьими промежуточной строки, затем регистров 242 кодами четвертой промежуточной строки и выдачи кодов этих отрок с регистров соответственно 236, 242 в блок 169. Параллельно идут такие же процессы в блоке 142 /155, 168/ заполнения регистров 236 и 242 кодами первой и второй текущих строк /фиг.19/ с той разницей, что ключ 233 открывается для выдачи кодов первой строки управляющим сигналом с входа 4, на который управляющий сигнал приходит с первого управляющего выхода блока 141, а ключ 239 для выдачи кодов второй строки открывается управляющим сигналом с входа 5, на который сигнал приходит с второго управляющего выхода блока 141. Процессы работы накопителей 141, 142 представлены временной диаграммой на фиг.20.

Выходы накопителей 141, 142 /154, 155 и 167, 168/ кодов строки поразрядно объединены и подключены к входам блока 169 /170, 171/ импульсных усилителей, каждый из блоков 169, 170, 171 включает по 8 импульсных усилителей /по числу разрядов в коде/, которые представлены микросхемами 533 АП6 с временем срабатывания 18 нс [6, с.128]. С выходов блоков 169, 170, 171 коды видеосигналов R, G, В поступают на цифровой вход /разъем ДV1/ ЖК-монитора 172, на первый и второй управляющие входы ЖК-монитора поступают кадровые синхроимпульсы 60 Гц /с 8-го выхода блока 177/ и импульсы частоты строк 61,44 кГц /с 9-го выхода блока 177/. В качестве плоскопанельного дисплея применен ЖК-монитор с разрешением 1280х1024 точек по технологии TFT [2, с.477, 487, табл.14.5]. Наряду с ЖК-монитором могут применяться плоскопанельные дисплеи по технологии плазменных /РДР/ или светодиодных элементов /LЕД/, электролюминесцентные мониторы [2, с.488], имеющие цифровой вход для раздельного приема кодов видеосигналов R, G, В. Изображение с экрана блока 172 воспринимается зрителем объемным через 3Д-очки 174 /фиг.10/. При воспроизведении правого и левого кадров стереопары стекла 3Д-очков поочередно [2, с.558-566] теряют прозрачность, каждый глаз видит свой кадр, что и дает стереоэффект. Стекла 3Д-очков выполнены по технологии ЖК-ячеек просветного типа, используемые как электронно-управляемые фильтры /затворы/. С приходом импульса СИС 30 Гц с блока 181 на ИК-передатчик 173 он излучает ИК-импульс, принимаемый ИК-приемником 175, расположенным на оправе 3Д-очков. ИК-приемник выдает управляющий сигнал в ЖК-ячейку левого стекла, затемняя его на 16,667 мс, затем выдает второй, управляющий сигнал в ЖК-ячейку правого стекла, затемняя его на 16,667 мс. Каждый глаз видит свой кадр. Ключ 178 открывается импульсом ССИ, счетчик 179 импульсов 9-и разрядный, ведет счет импульсов 9,8304 МГЦ, цикл счета 320 импульсов. С приходом 316 импульса дискретизации строки дешифратор 180 дешифрирует двоичный код 316 импульса и сигналом с 1-го выхода открывает ключи 182, 183 в первом и втором каналах воспроизведения звука, которые пропускают по три кода звука, поступающие в блок 184, 185 регистров звука, содержащие по три 8-и разрядных регистра. В блоке 184 принимаются 1-8 разряды кода звука, в блоке 185 принимаются 9-16 разряды кодой звука. С регистров блоков 184, 185 коды звука сигналами Uвыд 92,16 кГц выдаются в ЦАП 186, которые преобразуют коды звука в аналоговые сигналы, проходящие фильтры 187, усиливаемые в усилителях 188 мощности и воспроизводимые громкоговорителями 189. С приходом в счетчик 179 импульсов 320 импульса дискретизации строки дешифратор 180 выдает сигнал со второго выхода, закрывающий ключи 182, 183, обнуляющий счетчик 179 и закрывающий ключ 178. С приходом следующего импульса ССИ на вход ключа 178 процесс повторяется.

Работа системы

С фотоприемников 28-30 и 39-41 шесть аналоговых видеосигналов после усиления предварительными усилителями поступают в АЦП 45-47 и 48-50. Два звуковых сигнала подаются на входы АЦП 51,52. Видеосигналы преобразуются в 8-и разрядные коды с дискретизацией 19,6608 МГц. Звуковые сигналы преобразуются в 16-и разрядные коды с дискретизацией 92,16 кГц. Формирователи 55, 56, 57 кодов формируют из параллельных кодов последовательные и заменяют в них представление единиц с импульсов на положительные и отрицательные полусинусоиды моночастоты 78,6432 МГц. На передающей стороне кодируются 512 строк в кадре по 640 отсчетов в каждой. Развертка строк в растре построчная без обратных ходов, кадровая развертка тоже без обратных ходов. Частота строк 30,72 кГц, частота кадров 60 Гц: 30 кадров правого изображения и 30 кадров левого изображения. Информация передается тремя каналами передатчика 65. Первый канал передает коды ЕRП и ЕRЛ, верхней боковой частотой первой несущей, второй канал передает коды EВП и EВЛ нижней боковой частотой первой несущей, третий канал передает коды ЕGП и ВGЛ верхней боковой частотой второй несущей. Занимаемая полоса в эфире в сумме по трем каналам 534 Гц. Приемная сторона принимает три радиосигнала параллельно тремя трактами приема и обработки кодов видеосигналов, производит их усиление, детектирование, удвоение отсчетов в строке с 640 до 1280, удвоение числа строк с 512 до 1024, выделяет строчные ССИ и синхроимпульсы стереопар СИС, синтезатор 177 частот воспроизводит две несущие частоты. Коды удвоенных строк поступают в накопители кодов строк 141, 142, 154, 155, 167, 168, с них после усиления сигналов кодов импульсными усилителями в блоках 169, 170, 171 поступают на цифровой вход ЖК-монитора 172. С экрана ЖК-монитора изображение воспринимается зрителем объемным через 3Д-очки 174. При воспроизведении правого и левого кадров на экране монитора стекла 3Д-очков соответственно поочередно теряют прозрачность, и каждый глаз видит свой кадр. С приходом импульса СИС 30 Гц в ИК-передатчик 173 он излучает ИК-импульс, принимаемый ИК-приемником 175, который управляющими сигналами затемняет поочередно стекла 3Д-очков соответственно для правого и для левого кадров. Стереозвуковое сопровождение осуществляется двумя каналами звука, положительные эффекты применения заявляемой системы: незначительная занимаемая полоса в эфире 534 Гц, высокая помехозащищенность /на долю полосы 534 Гц придется мизерная часть энергии помехи/, низкое напряжение питания в приемной части определяет безопасные условия ее эксплуатации, в качестве устройства, воспроизводящего цветные изображения, можно применять мониторы, выполненные по любой существующей технологии и имеющие цифровой вход для раздельного приема кодов видеосигналов R, G, В, возможна двухсторонняя развертка кадра на экране мониторов при наличии в них двух цифровых входов для раздельного приема кодов R, G, В параллельно двух строк: одной с блоков 141, 154, 167, второй с блоков 142, 155, 168.

Использованные источники

1. Патент №2246801, кл. Н04N 15/00, бюл. №5 от 20.02.05, прототип.

2. Колесниченко О.В., Шишигин И.В. Аппаратные средства PC. 5-е изд, СПб, 2004, с.473-487, 558-566.

3. В.И.Мураховский. Устройство компьютера. М., "АСТ-ПРЕСС КНИГА", 2003, с.486-490.

4. Радиопередающие устройства. М.С.Шумилин, М., 1981, с.234, 235.

5. Фридлянд М.В, Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118, рис.5.5, с.122, рис.5.10.

6. Цифровые интегральные микросхемы. Справочник, Минск, 1991, c.128, 231, 258.

7. Шило В.А. Популярные цифровые микросхемы. Справочник, Челябинск, 1989, с.222.

8. Ильин В.А. Телеуправление и телеизмерение. М., 1982, с.274.

9. Бродский М.А. Телевизоры цветного изображения. Минск, 1988, с.86, рис.2.55, с.132 рис.4.2.

10. Радиосвязь, вещание и телевидение. Под ред. А.Д.Формушенко, М., 1981, с.146.

/

/ /

/ /

/

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2000 |

|

RU2194370C2 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2007 |

|

RU2339183C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2316142C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2334369C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2326508C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2001 |

|

RU2214693C2 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 1999 |

|

RU2165681C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2351094C1 |

Изобретение относится к технике радиосвязи и может использоваться для цифрового телевещания. Технический результат - исключение снижения яркости изображения от проекции и электронное управление раздельным наблюдением кадров стереопар, достигается тем, что в систему стереотелевидения на приемной стороне вводятся ЖК-монитор, 3Д-очки с ИК-приемником на оправе очков и ИК-передатчик на корпусе ЖК-монитора и в каждый канал видеосигнала введены по два накопителя кодов строки. На приемной стороне воспроизводятся правый и левый кадры стереопар с частотою 60 Гц, разрешение кадра 1280×1024 точек. 21 ил., 1 табл.