Изобретение относится к технике радиосвязи и может использоваться для цифрового телевещания.

Прототипом принята "Система стереотелевидения" [1], содержащая на передающей стороне фотоэлектрический преобразователь /ФЭП/, формирующий два изображения одного пространства, шесть АЦП видеосигнала, два АЦП сигнала звука, генератор синусоидальных колебаний и синтезатор частот, три формирователя кодов, два самоходных распределителя импульсов, счетчик импульсов, триггер, два ключа и передатчик из трех каналов, на приемной стороне содержащая антенну, блок управления, три тракта приема и обработки кодов видеосигналов, канал формирования управляющих сигналов, два канала воспроизведения звука и плоскопанельный ЖК-монитор. Каждый тракт приема и обработки кодов видеосигналов включает последовательно соединенные блок приема радиосигнала, усилитель радиочастоты и двухполярный амплитудный детектор, первый и второй формирователи импульсов и канал одного из трех сигналов R, G, В, каждый из которых включает первый и второй регистры сигнала /R, G, В/, блок обработки кодов /удвоения отсчетов/, первый блок задержек и сумматор, второй блок задержек, первый и второй накопители кодов строк. Приемная сторона содержит на корпусе ЖК-монитора ИК-передатчик и включает ЗД-очки с ИК-приемником на их оправе. Передающая сторона производит фотоэлектрическое преобразование параллельно правого и левого кадров стереопары, кодирует их сигналы в 8-I, разрядные коды и передает информацию кодов тремя радиоканалами передатчика. Видеорежим на передающей стороне 512строк×640отсчетов×60 Гц. Приемная сторона принимает параллельно тремя трактами приема три радиосигнала, производит их усиление, детектирование, удвоение отсчетов в строках с 640 до 1280, удвоение числа строк с 512 до 1024, выделяет строчные синхроимпульсы /ССИ/, синхроимпульсы стереопар /СИС/ и воспроизводит на экране ЖК-монитора последовательно правый и левый кадры стереопары с частотой 60 Гц /30+30/. Зритель воспринимает изображение объемным через ЗД-очки. Видеорежим на экране ЖК-монитора 1024×1280×60 Гц. Недостатками прототипа являются: параллельное преобразование сигналов правого и левого кадров усложняет ФЭП, передача информации тремя радиоканалами и двумя несущими увеличивает энергопотребление системы, использование ЖК-монитора уменьшает достоверность цветопередачи и вносит инерционность в управление изображением на экране.

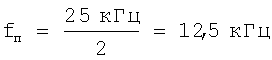

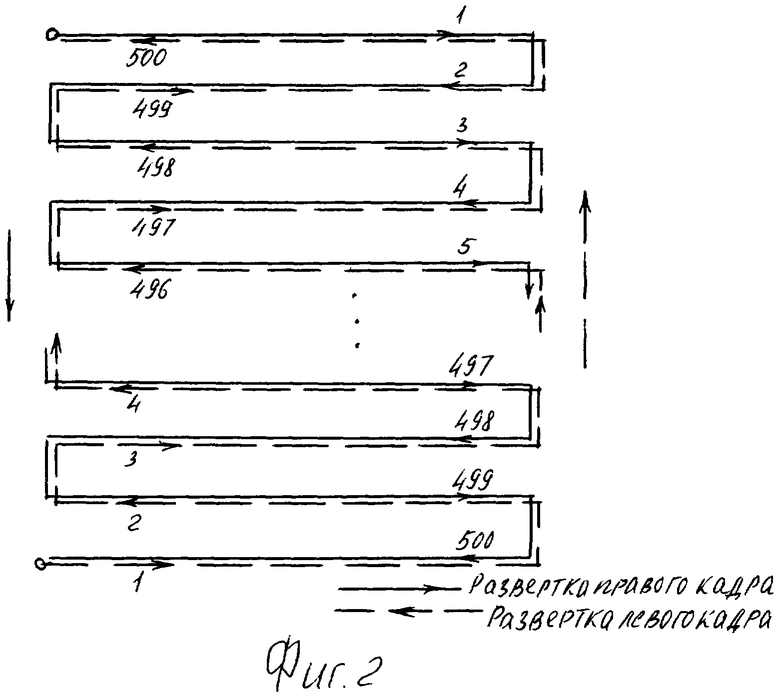

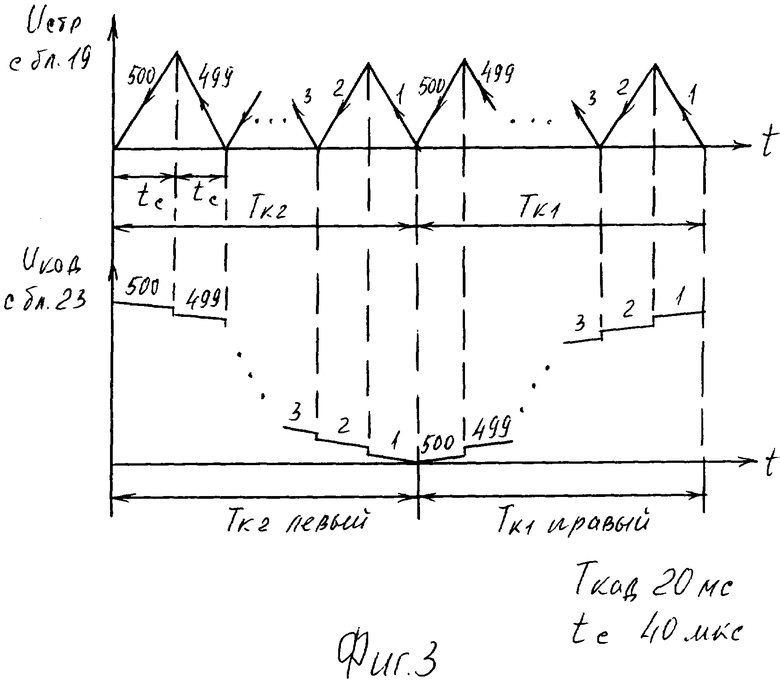

Цель изобретения - упрощение ФЭП, снижение энергоемкости системы, повышение яркости воспроизводимого изображения и достоверности цветопередачи. Техническими результатами являются сокращение в ФЭП второго канала преобразования, сокращение третьего канала передачи и приема в системе, увеличение яркости изображения на приемной стороне и достоверности цветопередачи. Результаты достигаются последовательным фотоэлектрическим преобразованием правого, затем левого кадров стереопары, передачей информации кодов кадров двумя каналами передатчика радиосигналов и на одной несущей частоте, увеличение яркости изображения и достоверности цветопередачи введением плоскопанельного светодиодного экрана /СД-экрана/ и блоков управляющих сигналов на приемной стороне. На передающей стороне применяется видеорежим 500стр×800отсч×50 Гц, где 500 - число кодируемых строк в кадре на передающей стороне, 800 - число кодируемых отсчетов в строке, 50 Гц - частота кадров. Каждая стереопара включает последовательно следующие правый и левый кадры /25 Гц+25 Гц/, частота стереопар 25 Гц. Информация передается верхней и нижней боковыми частотами одной несущей частоты. Развертка строк прогрессивная без обратных ходов и по строкам и по кадрам. Частота дискретизации в АЦП составляет

fд=500строк×500 Гц×800отсч=20 МГц.

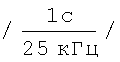

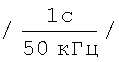

Частота строк fc=500×50 Гц=25 кГц, длительность строки 40 мск  , длительность кадра 20 мск

, длительность кадра 20 мск  . Частота колебания пьезодефлектора при развертке строк

. Частота колебания пьезодефлектора при развертке строк  . За один период колебания развертывается две строки. Период следования кодов видеосигнала

. За один период колебания развертывается две строки. Период следования кодов видеосигнала  . Частота колебаний пьезодефлектора при развертке кадров 25 Гц: за один период развертываются два кадра: вниз - правый кадр, вверх - левый кадр. Тактовая частота на передающей стороне

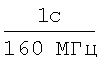

. Частота колебаний пьезодефлектора при развертке кадров 25 Гц: за один период развертываются два кадра: вниз - правый кадр, вверх - левый кадр. Тактовая частота на передающей стороне

fт=20 МГц×8 разр=160 МГц,

8 разр - число разрядов в коде. Несущая частота передатчика принимается fнес=160 МГц×15=2400 МГц, верхняя боковая частота fв.б.=2400+160=2560 МГц, нижняя бокая частота

fн.б.=2400-160=2240 МГц. Воспроизводимый на приемной стороне видеорежим 1000стр×1600отсч×50 Гц. Разрешение воспроизводимого кадра 1000×1600=1600000 пикселей.

Сущность изобретения в том, что в систему стереотелевидения, содержащую на передающей стороне ФЭП, три АЦП, синтезатор частот, два формирователя кодов, два самоходных распределителя импульсов и передатчик радиосигналов, на приемной стороне, включающую два тракта приема и обработки кодов видеосигналов, устройство отображения видеоинформации с ИК-передатчиком на его корпусе, ЗД-очки с ИК-приемником на оправе, канал формирования управляющих сигналов и два канала воспроизведения звука, на передающей стороне в ФЭП введены две отражательные призмы, подвижное плоское зеркало, ключ, триггер и исполнительный механизм, передатчик радиосигналов выполнен двухканальным, а на приемной стороне устройство отображения видеоинформации представлено плоскопанельным светодиодным экраном и в каждый канал сигнала R, G, В введены первый и второй накопители кодов и блок управляющих сигналов.

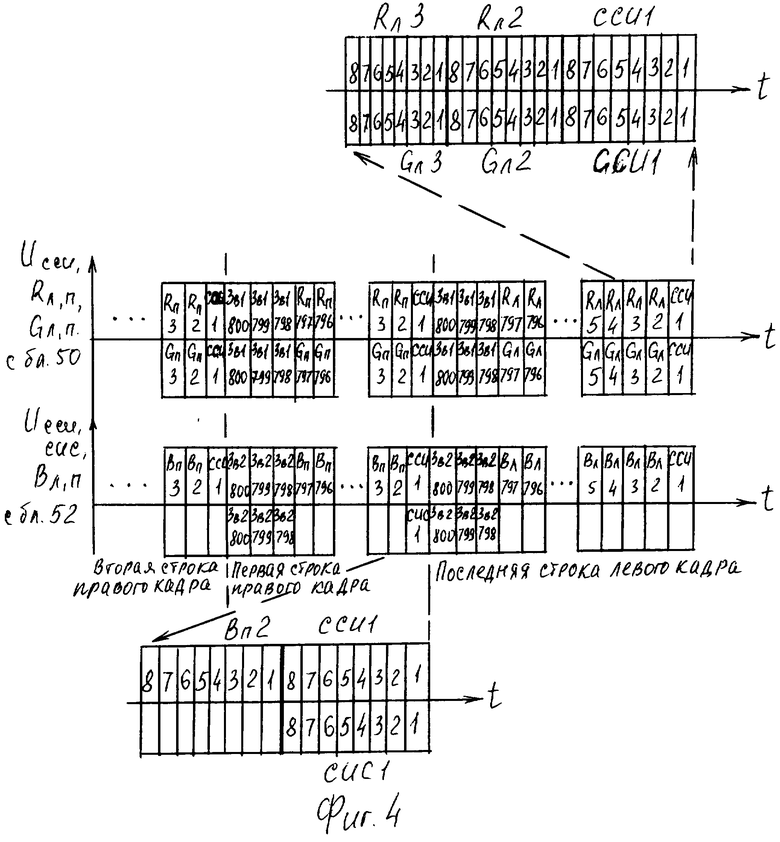

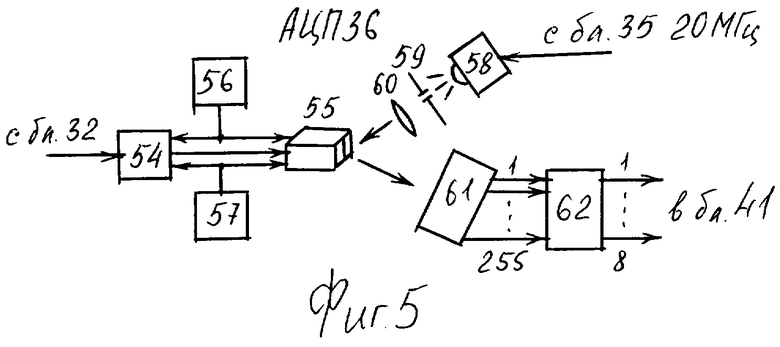

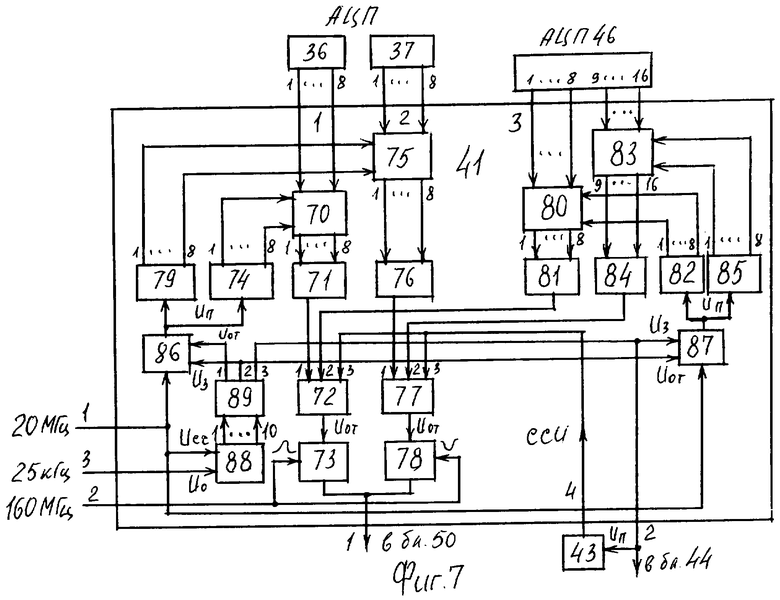

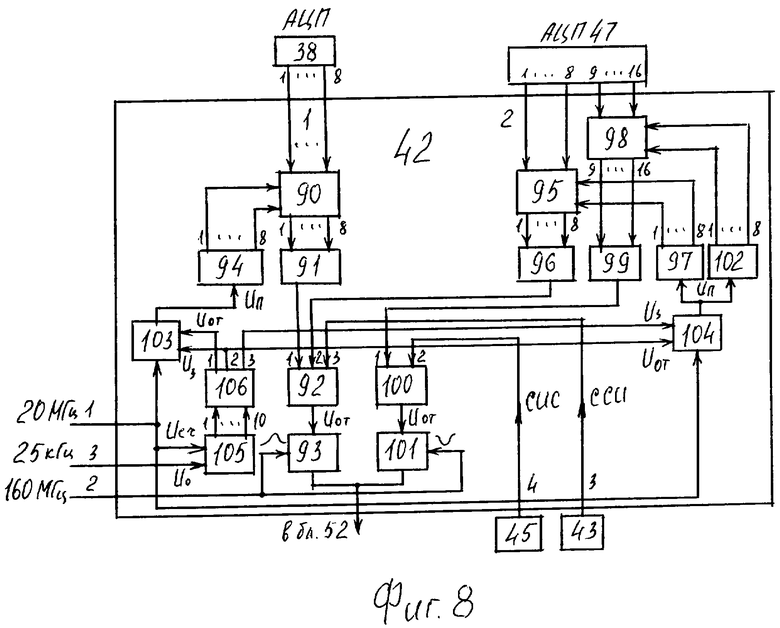

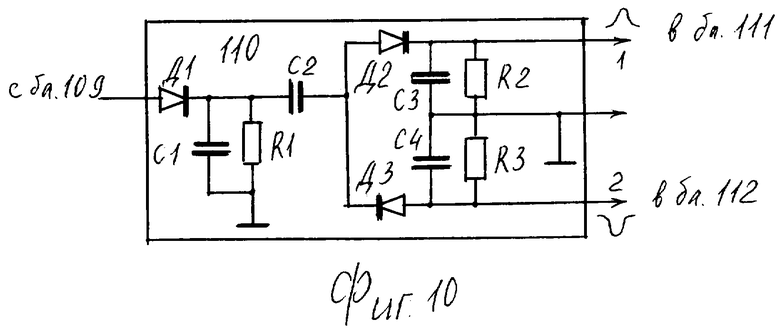

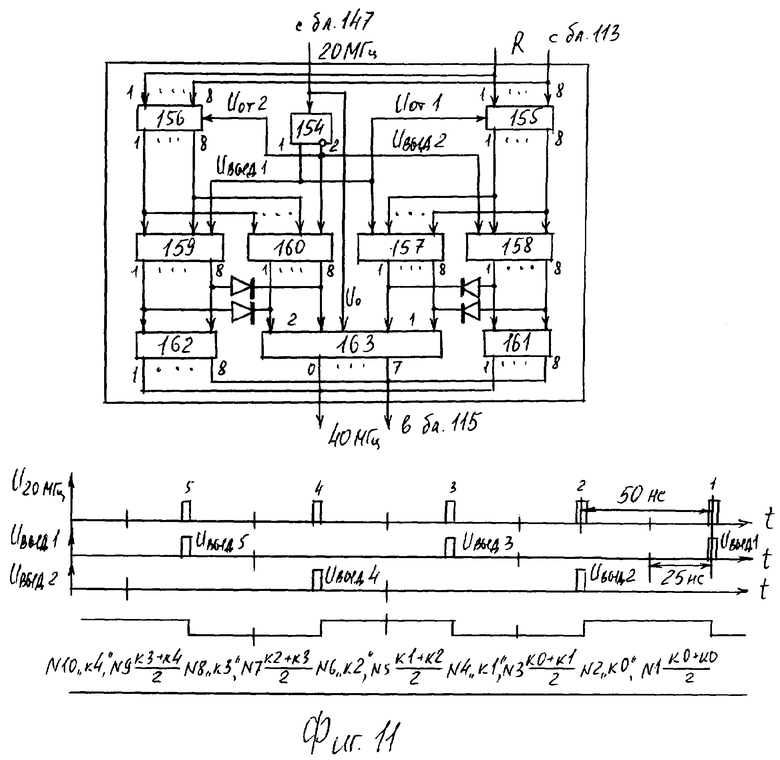

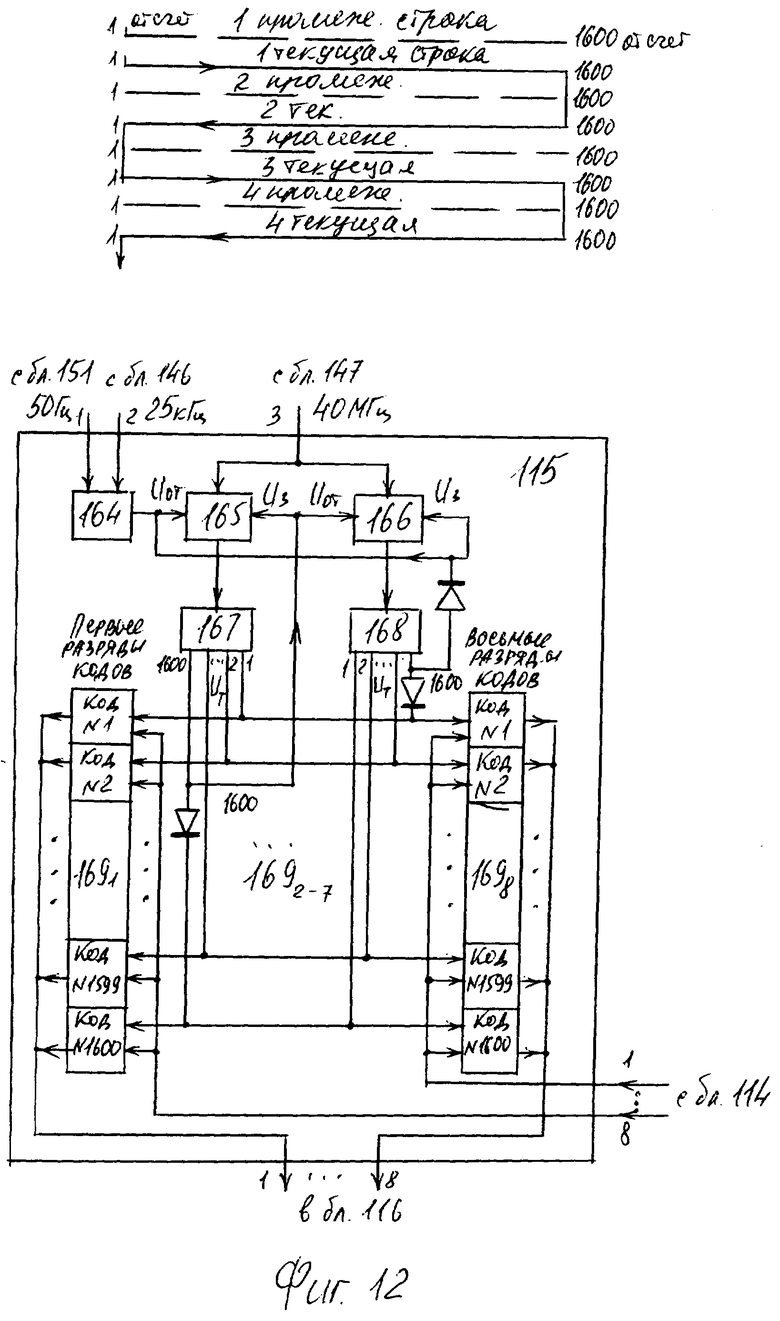

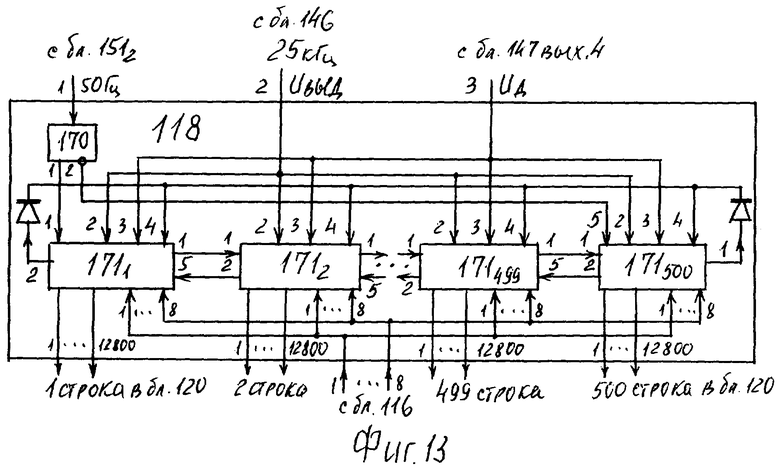

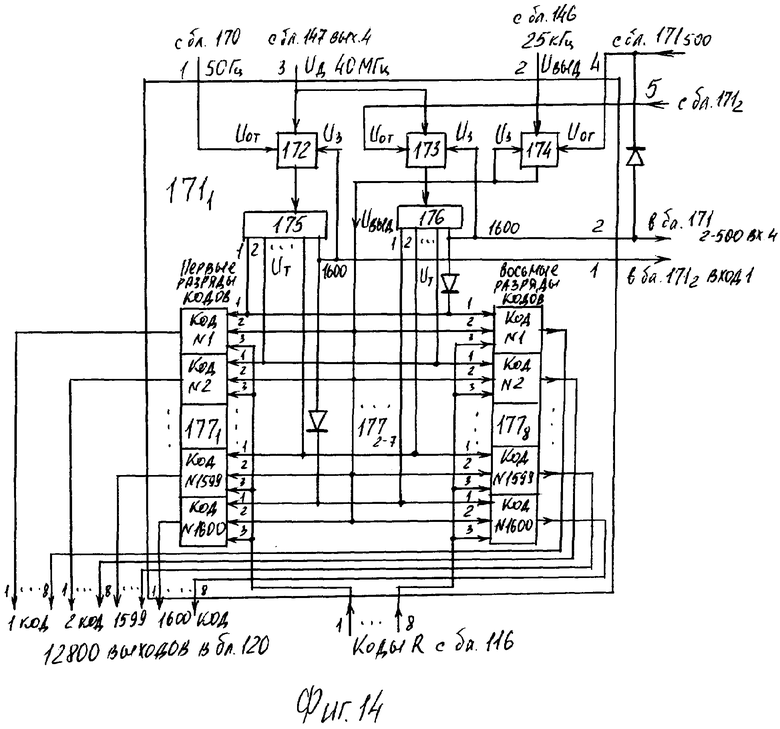

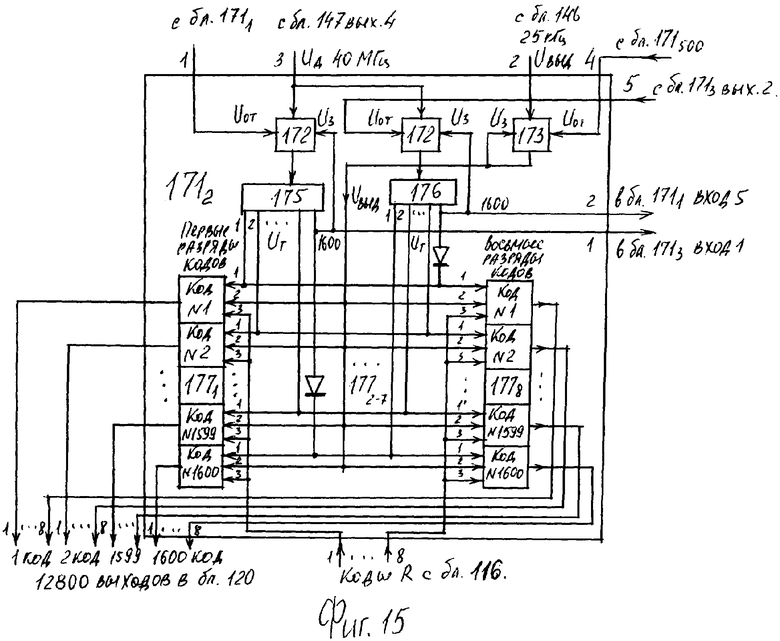

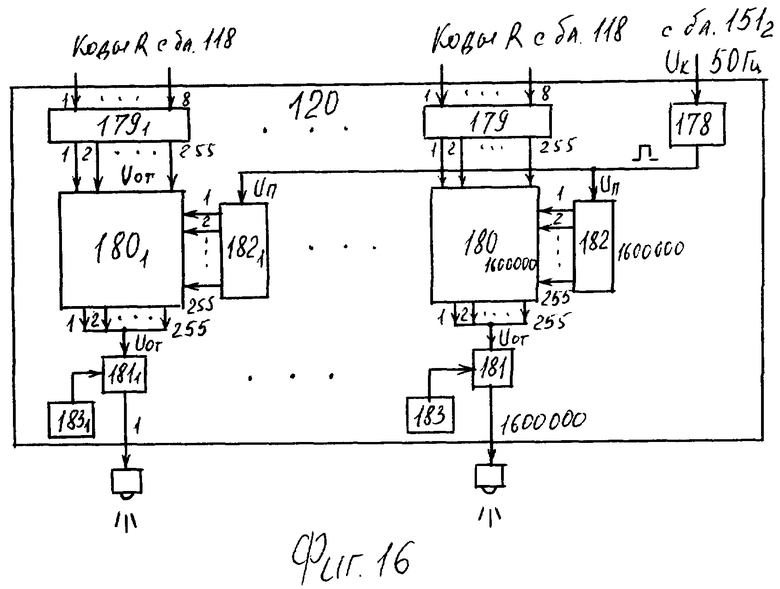

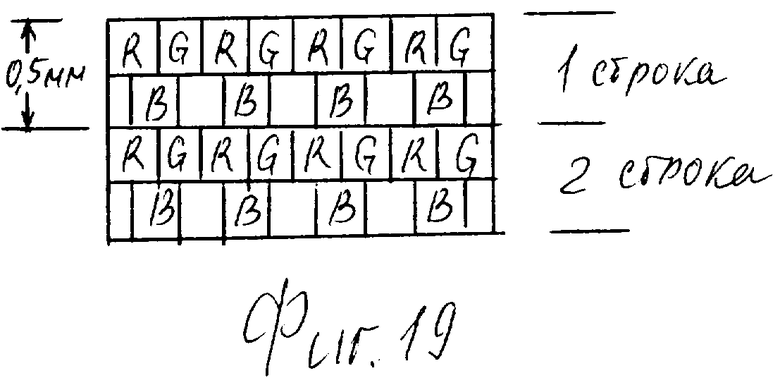

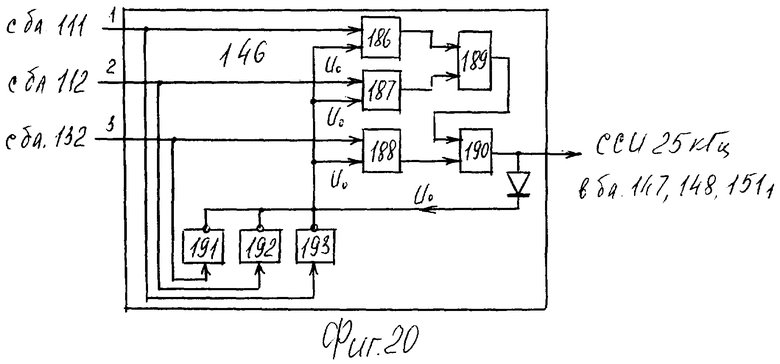

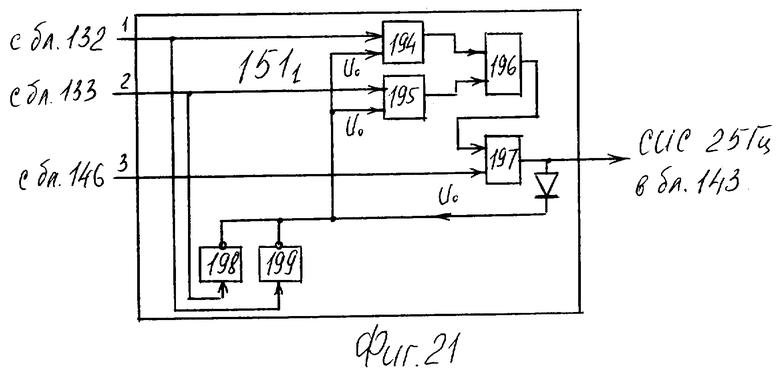

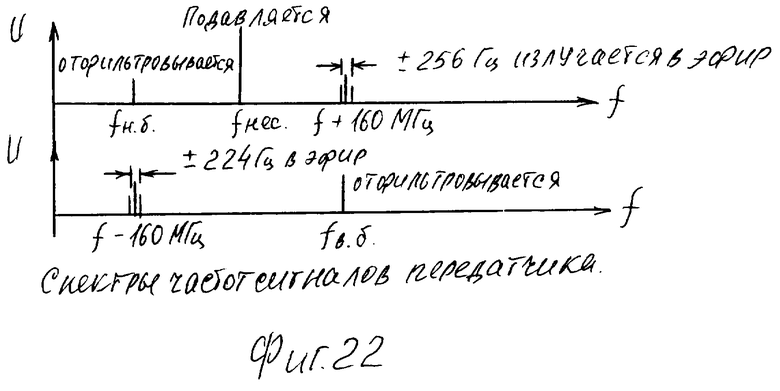

Передающая сторона на фиг.1, формирование растра на фиг.2, формы управляющих напряжений на фиг.3, структура цифровых потоков на фиг.4, АЦП видеосигнала на фиг.5, конструкция пьезодефлектора на фиг.6, первый формирователь кодов на фиг.7, второй формирователь кодов на фиг.8, приемная сторона на фиг.9, принципиальная схема двухполярного амплитудного детектора на фиг.10, блок обработки кодов на фиг.11, первый блок задержек на фиг.12, накопитель кодов кадра на фиг.13, блок регистров на фиг.14 и 15, блок управляющих сигналов на фиг.16, СД-ячейка на фиг.17, состав и форма элемента матрицы на фиг.18, расположение элементов матрицы в СД-экране на фиг.19, блок выделения строчных синхронимпульсов ССИ на фиг.20, блок выделения синхроимпульсов стереопар СИС на фиг.21, спектры частот сигналов передатчика на фиг.22, временные диаграммы работы системы на фиг.23.

Передающая сторона содержит /фиг.1/ фотоэлектрический преобразователь 1 /ФЭП/, являющийся датчиком видеосигналов двух кадров стереопары /правого и левого/, формирует последовательно три сигнала сначала правого кадра RП, GП. ВП, затем три видеосигнала левого кадра RЛ, GЛ, ВЛ, включает первую 2 и вторую 3 отражательные призмы с полным внутренним отражением, изменяющие направление лучей поля зрения на 90° [2 c.225], подвижное плоское зеркало 4 с зеркальными покрытиями на обоих внешних плоскостях, имеющего вертикальную ось поворота, повороты зеркала 4 выполняются в сторону призмы 2, затем на 90° в сторону призмы 3, частота поворотов 50 Гц, выполняются последовательно соединенными первым ключом 5, триггером 6 и исполнительным механизмом 7 по управляющим сигналам с триггера 6. Вторая отражательная призма расположена на соответствующем расстоянии слева от правой отражательной призмы 2, оптические оси их параллельны и после отражения совпадают с геометрическим центром плоского зеркала 4, расположенного в центре расстояния между отражательными призмами 2 и 3, и имеющего два фиксированных положения, первое под 45° к визирной оси первой отражательной призмы 2, второе под 45° к визирной оси второй отражательной призмы 3, при обоих положениях визирная ось плоского зеркала 4 совпадает с оптической осью объектива 8 ФЭП, который включает последовательно соединенные первый усилитель 9 и первый пьезодефлектор 10 с отражателем на торце, первый источник 11 положительного опорного напряжения, второй источник 12 отрицательного опорного напряжения, последовательно соединенные второй усилитель 13 и второй пьезодефлектор 14 с отражателем на торце, третий источник 15 положительного опорного напряжения, четвертый источник 16 отрицательного опорного напряжения, блок 17 строчной развертки из задающего генератора 18 и выходного каскада 19, блок 20 кадровой развертки из последовательно соединенных элемента И 21, задающего генератора 22 и суммирующего усилителя 23, первое дихроичное зеркало 24 и второе дихроичное зеркало 25, расположенные друг за другом и против отражателя второго пьезодефлектора 14, первый 26, второй 27, третий 28 микрообъективы, первый 29, второй 30, третий 31 фотоприемники, первый 32, второй 33, третий 34 предварительные усилители. Передающая сторона включает второй ключ 35, первый 36, второй 37, третий 38 АЦП видеосигнала соответственно цветов R, G, В, последовательно соединенные генератор 39 синусоидальных колебаний и синтезатор 40 частот, первый 41 и второй 42 формирователи кодов, первый самоходный распределитель 43 импульсов, последовательно соединенные двухразрядный счетчик 44 импульсов и второй самоходный распределитель 45 импульсов, первый 46 и второй 47 АЦП сигнала звука, на вход которых поданы сигналы звукового сопровождения, передатчик 48 радиосигналов из двух каналов. Первый канал включает последовательно соединенные усилитель 49 несущей частоты, амплитудный модулятор 50 и выходной усилитель 51, второй канал включает амплитудный модулятор 52 и выходной усилитель 53. Каждый из амплитудных модуляторов 50 и 52 состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [3 с.234], отфильтровывающего одну из боковых частот в спектре амплитудно-модулированной несущей /фиг.22/. Три АЦП 36, 37, 38 выполнены идентично /фиг.5/, каждый включает усилитель 54 и пьезодефлектор 55 с отражателем на торце, источник 56 положительного опорного напряжения, источник 57 отрицательного опорного напряжения, излучатель из импульсного светодиода 58, щелевой диафрагмы 59 и микрообъектива 60, линейку 61 многоэлементного фотоприемника и шифратор 62. Все пьезодефлекторы 10, 14, 55 являются торцевыми биморфными пъезоэлементами со световым отражателем на свободном торце, конструктивно выполнены [4 с.118] одинаково /фиг.6/ из первой 63 и второй 64 пьезопластин, внутреннего электрода 65, первого 66 и второго 67 внешних электродов. Один конец пьезопластин закреплен в держателе 68, на свободном торце пластин расположен световой отражатель 69. Первый формирователь 41 кодов включает /фиг.7/ три канала.

Первый канал включает последовательно соединенные блок 70 элементов И, первый 71 и второй 72 элементы ИЛИ, и выходной ключ 73, и самоходный распределитель 74 импульсов. Второй канал включает второй блок 75 элементов И, третий 76 и четвертый 77 элементы ИЛИ, и выходной ключ 78, и самоходный распределитель 79 импульсов. Третий канал включает два блока 80, 83 элементов И, пятый 81 и шестой 84 элементы ИЛИ, и два самоходных распределителя 82, 85 импульсов, включает первый 86 и второй 87 ключи, и последовательно соединенные счетчик 88 импульсов, и дешифратор 89, который имеет три выхода: первый подключен к первому управляющему входу ключа 86, второй подключен к второму управляющему входу ключа 86 и к первому управляющему входу ключа 87, третий подключен к второму управляющему входу второго ключа 87 и является вторым выходом блока 41, первым выходом которого являются объединенные выходы выходных ключей 73, 78. Первым-третьим информационными входами формирователя 41 кодов являются: первым - первые входы блока 70, вторым - первые входы блока 75 элементов И, третьим - первые входы блоков 80, 83 элементов И. Четвертым информационным входом блока 41 являются третьи входы второго и четвертого элементов ИЛИ 72, 77. Первым управляющим входом являются объединенные входы /20 МГц/ сигнальных входов ключей 86, 87 и счетный вход /Uсч/ счетчика 88 импульсов, вторым - объединенные сигнальные входы /160 МГц/ выходных ключей 73, 78, третьим - управляющий вход /25 кГц/ счетчика 88 импульсов. Второй формирователь 42 кодов включает /фиг.8/ два канала. Первый содержит последовательно соединенные блок 90 элементов И, первый 91 и второй 92 элементы ИЛИ, и выходной ключ 93, и самоходный распределитель 94 импульсов, второй канал включает последовательно соединенные первый блок 95 элементов И, третий элемент 96 ИЛИ, выход которого подключен к второму входу второго второго элемента 92 ИЛИ в первом канале, и первый самоходный распределитель 97 импульсов, и включает последовательно соединенные второй блок 98 элементов И, четвертый 99 и пятый 100 элементы ИЛИ, и выходной ключ 101, и второй самоходный распределитель 102 импульсов. Формирователь 42 кодов включает первый 103, второй 104 ключи, счетчик 105 импульсов и дешифратор 106, с первого по третий выходы которого подключены: первый - к первому управляющему входу ключа 103, второй - к второму управляющему входу ключа 103 и к первому управляющему входу ключа 104, третий - к второму управляющему входу ключа 104. Информационными входами являются: первым - первые входы блока 90 элементов И первого канала, вторым - первые входы блоков 96, 98 элементов И, третьим-третий вход элемента 92 ИЛИ, четвертым - второй вход элемента 100 ИЛИ. Выходом являются объединенные выходы выходных ключей 93, 101. Управляющими входами являются: первым - объединенные входы /20 МГц/ ключей 103, 104 и счетный вход счетчика 105 импульсов, вторым - сигнальные входы /160 МГц/ выходных ключей 93, 101, третьим - управляющий вход U0 счетчика 105 импульсов.

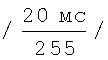

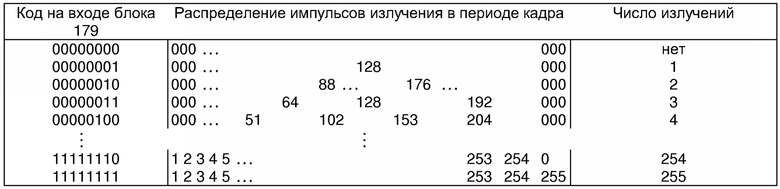

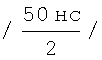

Приемная сторона включает /фиг.9/ антенну, блок 107 управления /выбор каналов/, первый и второй тракты приема и обработки кодов видеосигналов, устройство отображения видеоинформации, канал формирования управляющих сигналов и два канала воспроизведения звука. Первый тракт приема и обработки кодов видеосигналов производит прием и обработку кодов сигналов RП, GП и RЛ, GЛ и включает последовательно соединенные блок 108 приема радиосигналов, усилитель 109 радиочастоты и двухполярный амплитудный детектор 110, первый 111 и второй 112 формирователи импульсов, и включает канал сигнала R, содержащий последовательно соединенные регистр 113 сигнала R, блок 114 обработки кодов/удвоения кодов в строке/, первый блок 115 задержек и сумматор 116, второй блок 117 задержек и введенные первый накопитель 118 кодов /промежуточных строк кадра/, второй накопитель 119 кодов /текущих строк кадра/ и блок 120 управляющих сигналов, и включает канал сигнала G, содержащий последовательно соединенные регистр 121 сигнала G, блок 122 обработки кодов /удвоения кодов/, первый блок 123 задержек и сумматор 124, второй блок 125 задержек и введенные первый накопитель 126 кодов /промежуточных строк кадра/, второй накопитель 127 кодов /текущих строк/ и блок 128 управляющих сигналов. Второй тракт приема и обработки кодов видеосигналов производит прием и обработку кодов сигналов Вп, Вл, включает блок 129 приема радиосигналов, усилитель 130 радиочастоты и двухполярный амплитудный детектор 131, первый 132 и второй 133 формирователи импульсов и включает канал сигнала В, содержащий последовательно соединенные регистр 134 сигнала В, блок 135 обработки кодов, первый блок 136 задержек и сумматор 137, второй блок 138 задержек и введенные первый накопитель 139 кодов, второй накопитель 140 кодов и блок 141 управляющих сигналов. Приемная сторона включает плоскопанельный светодиодный экран 142 /СД-экран/, ИК-передатчик 143 на корпусе СД-экрана, ЗД-очки 144 с ИК-приемником 145 на оправе ЗД-очков. Порядок работы приемной стороны определяет канал формирования управляющих сигналов, включающий последовательно соединенные блок 146 выделения строчных синхроимпульсов /ССИ/, синтезатор 147 частот, первый ключ 148, счетчик 149 импульсов и дешифратор 150, включает блок 1511 выделения синхроимпульсов стереопар /СИС/ и второй ключ 1512. Приемная сторона включает идентичные первый 152, второй 153 каналы воспроизведения звука. Каждый из каналов содержит преобразователь кодов звука в аналоговые сигналы /ЦАП/, усилитель мощности и громкоговоритель. Изображение с СД-экрана зрителем воспринимается объемным через ЗД-очки. При воспроизведении на экране последовательно правого и левого кадров стереопары стекла ЗД-очков поочередно теряют прозрачность и каждый глаз видит свой кадр. Стекла очков выполнены по технологии ЖК-ячеек просветного типа, используемые как электронно-управляемые светофильтры /затворы/ [5 c.558-565]. С приходом сигнала СИС в ИК-передатчик 143 он излучает ИК-импульс, принимаемый ИК-приемником 145, который выдает управляющий сигнал в ЖК-ячейки левого стекла очков, затемняя его на 20 мс, затем уже сам ИК-приемник выдает второй управляющий сигнал ЖК-ячейки правого стекла, затемнял его на 20 мс, далее процессы повторяются. Блоки 114, 122, 135 обработки кодов идентичны /фиг.11/, каждый включает триггер 154, вход которого является управляющим входом блока, первый 155, второй 156 блоки ключей /по 8 штук в каждом/, первый 157, второй 158, третий 159, четвертый 160 регистры, первый 161 и второй 162 блоки задержек, сумматор 163 и 16 диодов. Информационными входами блока 114 являются поразрядно объединенные первый - восьмой входы блоков 155, 156 ключей, на них поступают в параллельном виде коды видеосигналов с регистра R 113 с частотой 20 МГц. Выходами являются поразрядно объединенные выходы сумматора 163 и блоков 161, 162 задержек. Частота следования кодов с блоков 114, 122, 135 40 МГц /через 25 нс/. Блоки 161, 162 выполняют задержку кодов на 50 нс, первая половина которых 25 нс приходится на время сложения кодов в сумматоре 163, выполняющем сложение за 25 нс. Первые блоки 115, 123, 136 задержек идентичны /фиг.12/, каждый включает элемент И 164, первый 165, второй 166 ключи, первый 167, второй 168 распределители импульсов и восемь регистров 1691-8 каждый из которых содержит 1600 разрядов /по числу отсчетов в строке/. Блоки 115, 123, 135 выполняют задержку кодов строки на длительность строки 40 мкс. Информационным входом блока являются объединенные поразрядно вторые входы разрядов с первого по восьмой регистров 169. Выходами являются поразрядно объединенные 1-8 выходы восьми регистров 169. Первым и вторым управляющими входами блока являются первый /50 Гц/ и второй /25 кГц/ входы элемента И 164, третьим управляющим входом являются объединенные сигнальные входы ключей 165, 166. Первые 118, 126, 139 и вторые 119, 127, 140 накопители кодов идентичны, каждый включает триггер 170 /фиг.13/ и блоки 171 регистров по числу половины строк кадра  , 1711-500. Информационным входом каждого накопителя кодов являются поразрядно объединенные 1-8 входы 500 блоков 171 регистров. Информационные входы накопителей кодов подключены: 118 к выходам сумматора 116, 119 к выходам второго блока 117 задержек, 126 к выходам сумматора 124, 127 к выходам блока 125, 139 к входам сумматора 137, 140 к выходам блока 138 задержек. Управляющими входами являются: первым - вход /50 Гц/ триггера 170, вторым - объединенные вторые управляющие входы /Uвыд 25 кГц/ блоков 1711-500, третьим - объединенные третьи управляющие входы /Uд 40 МГц/ блоков 1711-500. Первый управляющий выход каждого предыдущего блока 171 регистров подключен к первому управляющему входу каждого последующего блока 171 регистров, первый управляющий выход последнего 171500 блока через диод подключен параллельно к четвертым управляющим входам всех блоков 171 регистров. Второй управляющей выход каждого последующего блока 171 регистров подключен к пятому управляющему входу каждого предыдущего блока регистров, и второй управляющий выход первого блока 171 регистров через диод подключен параллельно к четвертым управляющим входам всех блоков 1711-500 регистров. Первый выход триггера 170 подключен к первому управляющему входу первого блока регистров 1711, второй выход триггера 170 подключен к пятому управляющему входу последнего блока 171500 регистров. Выходами каждого блока накопителя кодов являются выходы всех блоков 171 регистров, которых 6400000/1600×8×500/. Блоки 171 регистров идентичны, каждый включает /фиг.14, 15/ первый 172, второй 173, третий 174 ключи, первый 175 и второй 176 распределители импульсов и восемь регистров 1771-8. Информационными входами блока регистров являются поразрядно объединенные третьи входы разрядов восьми регистров 177. Выходами являются параллельные выходы всех разрядов восьми регистров 177, которых 12800/1600×8/. Управляющими входами блоков 171 регистров являются: первым - первый управляющий вход первого ключа 172, вторым - сигнальный вход /25 кГц/ третьего ключа 174, третьим - объединенные сигнальные входы /40 МГц/ первого 172 и второго 173 ключей, четвертым - первый управляющий вход третьего ключа 174, пятым - первый управляющий вход второго ключа 173. Первый управляющий вход первого ключа 172 в первом блоке 1711 регистров подключен к первому выходу триггера 170, первый управляющий вход второго ключа 173 в последнем блоке 171500 регистров является пятым управляющим входом и подключен к второму выходу триггера 170. Выход первого ключа 172 подключен к входу первого распределителя 175 импульсов, выходы которого последовательно с первого по 1600-й подключены к первым входам разрядов параллельно восьми регистров 177. Последний выход /1600/ распределителя 175 импульсов в блоках 1711-499 является первым управляющим выходом, подключенным к первому управляющему входу каждого последующего блока 171 регистров. Последний выход /1600/ распределителя 175 импульсов в блоке 171500 регистров является первым управляющим выходом и подключен через диод параллельно к четвертым управляющим входам всех блоков 171 регистров. Выход второго ключа 173 подключен к входу распределителя 176 импульсов, выходы которого последовательно подключены, начиная с первого, к первым входам разрядов параллельно восьми регистров 177 в обратном порядке: первый выход подключен к первым входам последних/1600/ разрядов регистров, последний 1600-й выход подключен к первым входам первых разрядов восьми регистров. Последний выход блока 176 в блоках 1712-500 регистров является вторым управляющим выходом, который от каждого последующего блока 171 регистров подключен к пятому управляющему входу каждого предыдущего блока 171499-1 регистров. Последний выход /1600/ распределителя 176 импульсов в блоке 1711 регистров является вторым управляющим выходом и подключен через диод к четвертым управляющим входам всех блоков 171 регистров. Выход третьего ключа 174 подключен параллельно к вторым входам всех разрядов восьми регистров 177 и к своему второму управляющему входу, прошедший импульс Uвыд закрывает и ключ 174. Выходы накопителей кодов 118, 119, 126, 127, 139, 140 /фиг.9/ подключены к информационным входам блоков соответственно 120, 128, 141 управляющих сигналов, назначение которых выполнять преобразование "код - число импульсов" для получения управляющих сигналов к выходному ключу 181 для подключения источника питания к светодиодам. Число управляющих сигналов к выходному ключу 181 /фиг.16/ соответствует величине кода цветового сигнала. Каждый из блоков 120, 128, 141 содержит /фиг.16/ формирователь 178 импульсов и преобразователей "код - число импульсов" соответственно разрешения в кадре 1600000 /1600×1000/. Преобразователи идентичны, каждый включает последовательно соединенные дешифратор 179, блок 180 ключей, содержащий 255 ключей, и выходной ключ 181 и включает самоходный распределитель 182 импульсов и источник 183 питания светодиода. Входы блоков 182 объединены и подключены к выходу формирователя 178 импульсов, сигнальный вход каждого выходного ключа 181 подключен к выходу своего источника 183 питания. Информационным входом преобразователя являются с первого по восьмой входы дешифратора 179, имеющего 255 выходов, подключенных к управляющим входам Uот ключей в блоке 180. Самоходный распределитель 182 импульсов имеет 255 разрядов, каждый из которых имеет свой выход, который подключен к сигнальному входу соответствующего ключа в блоке 180. Выходы всех ключей блока 180 объединены, и объединенный выход подключен к первому управляющему входу Uот ключа 181. Исходное состояние выходных ключей 181 закрытое. Формирователь 178 импульсов формирует приходящий кадровый импульс по длительности и амплитуде и выдает его на входы всех самоходных распределителей 182 импульсов. Преобразователи "код - число импульсов" работают идентично. С приходом импульса запуска Uп с выхода блока 178 самоходные распределители 182 запускаются, по мере продвижения импульса по 255 разрядам с выхода каждого разряда сигналы поступают на сигнальные входы соответствующих ключей в блоке 180. При отсутствии кода на входе дешифратора 179 ключи в блоке 180 закрыты. С приходом кода в дешифратор 179 сигналы Uот его выходов открывают соответствующие ключи в блоке 180, которые пропускают на управляющий вход выходного ключа 181 импульсы последовательно с соответствующих разрядов блока 182. Длительность каждого импульса составляет 78 мкс

, 1711-500. Информационным входом каждого накопителя кодов являются поразрядно объединенные 1-8 входы 500 блоков 171 регистров. Информационные входы накопителей кодов подключены: 118 к выходам сумматора 116, 119 к выходам второго блока 117 задержек, 126 к выходам сумматора 124, 127 к выходам блока 125, 139 к входам сумматора 137, 140 к выходам блока 138 задержек. Управляющими входами являются: первым - вход /50 Гц/ триггера 170, вторым - объединенные вторые управляющие входы /Uвыд 25 кГц/ блоков 1711-500, третьим - объединенные третьи управляющие входы /Uд 40 МГц/ блоков 1711-500. Первый управляющий выход каждого предыдущего блока 171 регистров подключен к первому управляющему входу каждого последующего блока 171 регистров, первый управляющий выход последнего 171500 блока через диод подключен параллельно к четвертым управляющим входам всех блоков 171 регистров. Второй управляющей выход каждого последующего блока 171 регистров подключен к пятому управляющему входу каждого предыдущего блока регистров, и второй управляющий выход первого блока 171 регистров через диод подключен параллельно к четвертым управляющим входам всех блоков 1711-500 регистров. Первый выход триггера 170 подключен к первому управляющему входу первого блока регистров 1711, второй выход триггера 170 подключен к пятому управляющему входу последнего блока 171500 регистров. Выходами каждого блока накопителя кодов являются выходы всех блоков 171 регистров, которых 6400000/1600×8×500/. Блоки 171 регистров идентичны, каждый включает /фиг.14, 15/ первый 172, второй 173, третий 174 ключи, первый 175 и второй 176 распределители импульсов и восемь регистров 1771-8. Информационными входами блока регистров являются поразрядно объединенные третьи входы разрядов восьми регистров 177. Выходами являются параллельные выходы всех разрядов восьми регистров 177, которых 12800/1600×8/. Управляющими входами блоков 171 регистров являются: первым - первый управляющий вход первого ключа 172, вторым - сигнальный вход /25 кГц/ третьего ключа 174, третьим - объединенные сигнальные входы /40 МГц/ первого 172 и второго 173 ключей, четвертым - первый управляющий вход третьего ключа 174, пятым - первый управляющий вход второго ключа 173. Первый управляющий вход первого ключа 172 в первом блоке 1711 регистров подключен к первому выходу триггера 170, первый управляющий вход второго ключа 173 в последнем блоке 171500 регистров является пятым управляющим входом и подключен к второму выходу триггера 170. Выход первого ключа 172 подключен к входу первого распределителя 175 импульсов, выходы которого последовательно с первого по 1600-й подключены к первым входам разрядов параллельно восьми регистров 177. Последний выход /1600/ распределителя 175 импульсов в блоках 1711-499 является первым управляющим выходом, подключенным к первому управляющему входу каждого последующего блока 171 регистров. Последний выход /1600/ распределителя 175 импульсов в блоке 171500 регистров является первым управляющим выходом и подключен через диод параллельно к четвертым управляющим входам всех блоков 171 регистров. Выход второго ключа 173 подключен к входу распределителя 176 импульсов, выходы которого последовательно подключены, начиная с первого, к первым входам разрядов параллельно восьми регистров 177 в обратном порядке: первый выход подключен к первым входам последних/1600/ разрядов регистров, последний 1600-й выход подключен к первым входам первых разрядов восьми регистров. Последний выход блока 176 в блоках 1712-500 регистров является вторым управляющим выходом, который от каждого последующего блока 171 регистров подключен к пятому управляющему входу каждого предыдущего блока 171499-1 регистров. Последний выход /1600/ распределителя 176 импульсов в блоке 1711 регистров является вторым управляющим выходом и подключен через диод к четвертым управляющим входам всех блоков 171 регистров. Выход третьего ключа 174 подключен параллельно к вторым входам всех разрядов восьми регистров 177 и к своему второму управляющему входу, прошедший импульс Uвыд закрывает и ключ 174. Выходы накопителей кодов 118, 119, 126, 127, 139, 140 /фиг.9/ подключены к информационным входам блоков соответственно 120, 128, 141 управляющих сигналов, назначение которых выполнять преобразование "код - число импульсов" для получения управляющих сигналов к выходному ключу 181 для подключения источника питания к светодиодам. Число управляющих сигналов к выходному ключу 181 /фиг.16/ соответствует величине кода цветового сигнала. Каждый из блоков 120, 128, 141 содержит /фиг.16/ формирователь 178 импульсов и преобразователей "код - число импульсов" соответственно разрешения в кадре 1600000 /1600×1000/. Преобразователи идентичны, каждый включает последовательно соединенные дешифратор 179, блок 180 ключей, содержащий 255 ключей, и выходной ключ 181 и включает самоходный распределитель 182 импульсов и источник 183 питания светодиода. Входы блоков 182 объединены и подключены к выходу формирователя 178 импульсов, сигнальный вход каждого выходного ключа 181 подключен к выходу своего источника 183 питания. Информационным входом преобразователя являются с первого по восьмой входы дешифратора 179, имеющего 255 выходов, подключенных к управляющим входам Uот ключей в блоке 180. Самоходный распределитель 182 импульсов имеет 255 разрядов, каждый из которых имеет свой выход, который подключен к сигнальному входу соответствующего ключа в блоке 180. Выходы всех ключей блока 180 объединены, и объединенный выход подключен к первому управляющему входу Uот ключа 181. Исходное состояние выходных ключей 181 закрытое. Формирователь 178 импульсов формирует приходящий кадровый импульс по длительности и амплитуде и выдает его на входы всех самоходных распределителей 182 импульсов. Преобразователи "код - число импульсов" работают идентично. С приходом импульса запуска Uп с выхода блока 178 самоходные распределители 182 запускаются, по мере продвижения импульса по 255 разрядам с выхода каждого разряда сигналы поступают на сигнальные входы соответствующих ключей в блоке 180. При отсутствии кода на входе дешифратора 179 ключи в блоке 180 закрыты. С приходом кода в дешифратор 179 сигналы Uот его выходов открывают соответствующие ключи в блоке 180, которые пропускают на управляющий вход выходного ключа 181 импульсы последовательно с соответствующих разрядов блока 182. Длительность каждого импульса составляет 78 мкс  . Выходной ключ 181 открывается каждым импульсом с блока 180 на длительность 78 мкс, и соответствующий светодиод в СД-экранн зачитывается на длительность импульса 78 мкс, т.е. дает излучение. Блоки 180 и 182 производят равномерное распределение импульсов запитывания светодиода в периоде кадра. Пример распределения импульсов излучения в периоде кадра соответственно величине кода приводится в таблице. Выходами блока управляющих сигналов 120 являются выходы 1600000 выходных ключей 181, каждый из которых подключен к своему светодиоду в СД-экране.

. Выходной ключ 181 открывается каждым импульсом с блока 180 на длительность 78 мкс, и соответствующий светодиод в СД-экранн зачитывается на длительность импульса 78 мкс, т.е. дает излучение. Блоки 180 и 182 производят равномерное распределение импульсов запитывания светодиода в периоде кадра. Пример распределения импульсов излучения в периоде кадра соответственно величине кода приводится в таблице. Выходами блока управляющих сигналов 120 являются выходы 1600000 выходных ключей 181, каждый из которых подключен к своему светодиоду в СД-экране.

0 - отсутствует излучения светодиода,

1 2 3...128...255 - номера импульсов излучения в периоде кадра. Распределение импульсов излучений в периоде кадра, через равные интервалы времени способствуют лучшей достоверности цветопередачи при воспроизведении изображения. Инерционность применяемых светодиодов не более 1 мкс. По окончании накопления блоками 118, 119, 126, 127, 139, 140 кодов кадра сигнал UК 50 Гц запускает в блоках 120, 128 и 141 все самоходные распределители 182 /фиг.16/ и коды сигналов R, G, В поступают синхронно в дешифраторы 179, преобразуются в число управляющих импульсов пропорционально величине кода. Каждый светодиод в СД-экране 142 запитывается с источника 183 на число импульсных излучений соответственно величине кода. Плоскопанельный светодиодный экран 142 представляет собой совокупность элементов матрицы соответственно разрешения кадра 1600000/1600×1000/, выполняемых в стекле СД-экрана, и включает экранное стекло и элементы матрицы по числу разрешения кадра. Каждый элемент включает три излучающих светодиодных ячейки /СД-ячейки/, каждая из которых излучает один из основных цветов R, Q, В. Светодиодная ячейка содержит /фиг.17/ светодиод 184 белого свечения и цветной светофильтр 185 из основных цветов. Три СД-ячейки составляют элемент матрицы /фиг.18/, расположение элементов матрицы и СД-ячеек в СД-экране на фиг.19. Управляющий вход каждого светодиода подключен к выходу своего преобразователя "код - число импульсов" в блоках 120 /сигнал R/, 128 /сигнал G/, 141 /сигнал В/. Уровень яркости излучения СД-ячейки воспринимается зрением пропорционально числу импульсов излучения светодиода за период кадра. Суммарное излучение трех основных цветов тремя СД-ячейкам R, G, В формирует для зрения цветовой тон и соответственно его яркость одного элемента /пиксела/. В качестве светодиодов используются сверхъяркие светодиоды белого свечения фирм "Nichia", "Ledtronics", "Kingbright" [6 c.47]. Светодиоды исполняются методом микроэлектронной технологии в стекле экрана, размеры светодиодов 0,25×0,25 мм /фиг.17/. Современные технологии позволяют выполнить каждый из блоков 118, 119, 126, 127, 139, 140 и 120, 128, 142 в одной микросхеме. Размер одного элемента матрицы 0,5×0,5 мм /фиг.18/. Размер СД-экрана 142 составляет:

по горизонтали 1600×0,5 мм = 800 мм,

по вертикали 1000×0,5 мм = 500 мм, по диагонали 1886 мм, или 74 дюйма. Блок 146 выделения строчных синхроимпульсов ССИ включает /фиг.20/ первый 186, второй 187, третий 188 счетчики импульсов, первый 189, второй 190 элементы И, с первого 191 по третий 193 элементы НЕ и диод. С приходом на счетные входы счетчиков синхронно трех кодов из 8-и единиц 11111111 на выходе блока появляется синхроимпульс ССИ строки /25 кГц/. При других кодах хотя бы в одном из них будет ноль, при котором элемент НЕ обнулит все счетчики, и ложного ССИ на выходе блока не будет. Блок 1511 выделения синхроимпульсов стереопар СИС включает /фиг.21/ первый 194, второй 195 счетчики импульсов, первый 196 и второй 197 элементы И, два элемента 198, 199 НЕ и диод. С приходом на счетные входы счетчиков синхронно двух кодов из 8-и единиц и на вход элемента И 197 импульса ССИ с блока 146 на выходе блока 1511 появляется импульс СИС 25 Гц.

ФЭП 1 формирует три аналоговых видеосигнала RП, GП, ВП правого кадра. Лучи правого поля зрения через отражающую призму 2 и плоское зеркало 4 в первом фиксированном положении поступают в объектив 8, фокусирующий изображение в плоскости отражателя пьезодефлектора 10. Отражатель имеет ширину 0,01 мм и длину 5 мм /0,01 мм × 500 строк/, размеры развертывающего элемента 0,01×0,01 мм. По управляющим напряжениям /фиг.3/ с усилителя 9 пьезодефлектор 10 выполняет колебания торца с отражателем относительно отражателя пьезодефлектора 14, выполняя сканирование правого изображения. Период управляющего напряжения равен длительности двух строк /фиг.2/. Блок 17 выдает линейно изменяющееся напряжение в воде равнобедренного треугольника /фиг.3/. Частота колебаний пьезодефлектора 10 12,5 кГц. Пьезодефлектор 14 выполняет кадровую развертку двух кадров: при развертке вниз идет правый кадр стереопары, при развертке вверх идет левый кадр. Пьезодефлектор 14 колеблется с частотой 25 Гц, что составляет 50 кадров в секунду. Кадровая развертка без обратных ходов. Ширина отражателя пьезодефлектора 14 0,01 мм, длина 8 мм /0,01 мм × 800 отсчетов/. Формирование левого кадра идет при развертке пьезодефлектора 14 вверх. По окончании периода правого кадра на вход первого ключа 5 поступает второй импульс 50 Гц, с второго выхода триггера 6 поступает сигнал в исполнительный механизм 7, который поворачивает плоское зеркало 4 за одну мс на 90° в сторону второй отражательной призмы 3 /второе положение/. Лучи второго поля зрения левого поступают через призму 3 зеркала 4 в объектив 8. Далее следует аналогичный процесс формирования видеосигналов левого кадра RЛ, GЛ, ВЛ. В качестве исполнительного механизма 7 применяется пьезоэлектрический двигатель ПЭД [7 с.40], работающий в шаговом режиме с временем поворота в 1 мс, масса 10 г /15 Вт/, управляемый сигналами с триггера 6. Суммирующий усилитель 23 блока 20 кадровой развертки выполняет суммирование линейного напряжения с задающего генератора 22 с импульсами 25 кГц частоты строк. Каждый импульс строки перемещает следующую строку в конце ее хода /фиг.2/ на шаг в одну строку, получаются 500 строк, все активные. С выхода суммирующего усилителя 23 в усилитель 13 поступает линейно изменяющееся и ступенчатое напряжение /фиг.3/, усиливаемое до необходимой величины усилителем 13 [4 c.122]. Отраженные от отражателя пьезодефлектора 14 смешанные цветовые лучи направляются в свои микрообъективы 26 /R/, 27 /В/, 28 /G/, которые собирают их в свои фотоприемники 29, 30, 31, с которых аналоговые видеосигналы поступают в предварительные усилители 32, 34, 33, с которых они поступают на информационные входы АЦП соответственно 36, 37, 38. Для синхронизации начала работы ФЭП и АЦП 36-38 с правого кадра стереопары ключи 5 и 35 открываются с каждым началом правого кадра стереопары импульсом 25 Гц с выхода элемента И 21 блока 20 кадровой развертки. Ключ 35 начинает пропускать импульсы дискретизации 20 МГц на управляющие входы АЦП с началом периода правого кадра стереопары. Ключ 5 определяет поворот зеркала 4 в первое фиксированное положение /к отражающей призме 2/ при правом кадре.

Сигнал Uот ключей 5 и 35 поступает с выхода элемента И 21 /фиг.1/ в момент прихода на его входы импульса 25 Гц импульса 25 кГц и частоты строк. Синтезатор 40 частот выдает с первого выхода импульсы дискретизации 20 МГц на управляющие входы АЦП 36-38, на первые управляющие входы формирователей 41, 42 кодов и на первые управляющие входы АЦП 46, 47, со второго выхода - импульсы тактовой частоты 160 МГц на вторые управляющие входы формирователей 41, 42 кодов, с третьего выхода - импульсы дискретизации звука 75 кГц на вторые управляющие входы АЦП 46, 47, с четвертого - импульсы 50 Гц на вход ключа 5, с пятого выхода - импульсы частоты строк 25 кГц на третьи управляющие входы блоков 41, 42, на третьи управляющие входы АЦП 46, 47 и на первый вход блока 20 кадровой развертки, с шестого выхода - импульсы частоты стереопар 25 Гц на второй вход блока 20 и на управляющий вход /U0/ блока 44, с седьмого - импульсы 12,5 кГц на вход блока 17, с восьмого выхода - синусоидальные колебания 2400 МГц несущей частоты в передатчик 48 радиосигналов. Задающий генератор 39 генерирует синусоидальные колебания со стабильностью 10-7. АЦП 46, 47 преобразуют сигналы звука в 16-разрядные коды, которые в параллельном виде поступают с АЦП 46 на третий информационный вход формирователя 41 кодов, с АЦП 47 на второй информационный вход блока 42. Самоходный распределитель 43 импульсов с приходом сигнала UП пуска со второго выхода блока 41 /в момент 800-го импульса дискретизации строки/ выдает код из 8-и единиц 11111111, являющийся кодом строчного синхроимпульса ССИ, на четвертый информационный вход блока 41 и на третий информационный вход блока 42. Самоходный распределитель 45 импульсов с приходом на его вход сигнала UП пуска с второго выхода счетчика 44 импульсов выдает код из 8-и единил, являющийся синхроимпульсом стереопары СИС, на четвертый информационный вход блока 42. Код СИС является первым кодом первой строки правого кадра /фиг.4/. Счетчик 44 импульсов двухразрядный, с приходом на счетный вход второго импульса с второго выхода блока 41 выдает сигнал UП со второго выхода в блок 45, после чего обнуляется сигналом U0 25 Гц. Второй импульс с блока 41 означает конец периода левого кадра, т.е. конец стереопары. АПЦ 36-38 идентичны /фиг.5/, имеют один принцип преобразования, заключающийся в развертке луча от светодиода 58 отражателем пьезодефлектора 55 по плоскости входных зрачков фотоприемников линейки 61. Световой импульс преобразуется в электрический сигнал, возбуждающий соответствующую шину шифратора 62, который выдает 8-разрядный код мгновенного значения входного сигнала, дискретизация 20 МГц. Источником излучения принят импульсный светодиод, например, AЛ402A с временем срабатывания 25 нс. Линейка 61 включает 255 фотоприемников для кодирования сигналов 8-разрядным кодом. Фотоприемниками являются лавинные фотодиоды ЛФД с временем срабатывания 10 нс. Шифратор из микросхем К155ИВ1 с временем срабатывания 20 нс. Шифратор 62 формирует коды с 00000000 по 11111111. Первому фотоприемнику соответствует код 00000001, второму - код 00000010, третьему - код 00000011 и т.д. 255-у - код 11111111. Время преобразования в АДП 30 не, что удовлетворяет дискретизации 20 МГц /50 нс/. Работа формирователей 41, 42 кодов /фиг.7, 8/. С выходов АЦП 36, 37 коды поступают в параллельном виде на первый и второй информационные входы блока 41, с АЦП 38 на первый информационный вход формирователя 42 кодов. Формирователь 41 кодов первым в строке формирует код ССИ /фиг.4/, из потока кодов формирует со второго по 797 коды сигналов RП, GП, /RЛ, GЛ/ и затем три кода звука 796, 799, 800 отсчеты строки. Формирователь 42 кодов первым в строке формирует коды ССИ и СИС /в первой строке правого кадра/, в потоке кодов формирует со второго по 797 коды сигналов ВП и ВЛ и затем три кода звука 798, 799, 800. Единицы в кодах RП, RЛ представляются положительными полусинусоидами моночастоты 160 МГц со стабильностью 10-7. Единицы в кодах GП, GЛ представляются отрицательными полусинусоидами той же моночастоты. Единицы в кодах ВП, ВЛ представляются положительными полусинусоидами частоты 160 МГц, единицы в коде СИС представляются отрицательными полусинусоидами той же частоты. Временные диаграммы работы блоков 41, 42 на фиг.23. Блоки 41, 42 преобразуют параллельные коды в последовательные и заменяют в них представление символов единиц с импульсов на полусинусоиды моночастоты 160 МГц. Коды с АЦП 36 поступают /фиг.7/ на первые входы блока 70 элементов И, на вторые входы которого поступают последовательно восемь импульсов с выхода блока 74, пусковой сигнал UП в который поступает с первого ключа 86. С выходов блока 70 импульсы последовательно через элементы ИЛИ 71, 72 открывают на время своей длительности 6,25 нс  выходной ключ 73, на сигнальный вход которого поступают синусоидальные колебания частоты 160 МГц. Выходной ключ 73 в открытом состоянии пропускает одну положительную полусинусоиду на выход. Аналогичный процесе проходит код, поступивший на первые входы блока 75 элементов И, импульсы с которого открывают на время своей длительности /6,25 нс/ второй выходной ключ 78, который в открытом состоянии пропускает одну отрицательную полусинусоиду. Выходы ключей 73, 78 объединены. На выходе блока 41 выходной сигнал представляется полными или неполными синусоидами частоты 160 МГц со стабильностью 10-7. Нули представляются отсутствием полусинусоид. Эти сигналы и модулируют несущую частоту 2400 МГц в модуляторе 50 передатчика 48. Очередность формирования сигналов ССИ, кодов отсчетов строки и кодов звука определяют сигналы с дешифратора 89. В исходном состоянии ключ 86 закрыт. Счетчик 88 импульсов 10-разрядный, ведет счет 800 импульсов дискретизации строки. При коде 00000001 в дешифраторе 89 с его первого выхода импульс открывает ключ 86, пропускающий сигналы 20 МГц в качестве сигналов UП в блок 74, 79, и со второго отсчета строки формируются коды видеосигналов по 797 отсчет строки. При 797 импульсе в счетчике 88 код 1100011101, дешифратор 89 при этом коде выдает сигнал со второго выхода, который закрывает ключ 86 и открывает ключ 87. Импульс UП с ключа 87 запускает блоки 82, 85, на вторые входы блоков 72, 77 элементов ИЛИ поступают соответственно 1-8 и 9-16 импульсы кодов звука. Ключ 87 открыт на время прохода трех кодов звука: 798, 799, 800 отсчетов строки. При поступлении в счетчик 800-го импульса строки с третьего выхода дешифратора 89 импульс закрывает ключ 87 и является вторым выходным сигналом с блока 41, который запускает UП самоходный распределитель 43 импульсов, который в момент первого отсчета строки подает на третьи входы элементов 72, 77 код ССИ. Этот код является первым кодом в каждой строке. Далее процессы повторяются. В кодах звука единицы в разрядах 1-8 представляются положительными полусинусоидами, в разрядах 9-16 представляются отрицательными полусинусоидами. На первый вход формирователя 42 кодов /фиг.8/ поступают коды с АЦП 38 сигналов ВП/ВЛ/ 7 на первые входы блока 90 элементов И, на вторые входы которого поступают 8 импульсов с блока 94. С выходов блока 90 импульсы последовательно через элементы ИЛИ 91, 92 открывают на время своей длительности /6,25 нс/ выходной ключ 93, на сигнальный вход которого поступают синусоидальные колебания 160 МГц. Ключ 93 в открытом состоянии пропускает одну положительную полусинусоиду. Единицы кодов В представляются положительными полусинусоидами. С приходом в дешифратор 106 кода 797-го отсчета строки сигнал со второго выхода дешифратора 106 закрывает ключ 103 и открывает ключ 104. С блоков 97, 102 на вторые входы блоков 95, 98 поступают по 8 импульсов, и с выходов этих блоков на второй элемента ИЛИ 92 и на первый вход элемента ИЛИ 100 поступают три кода сигнала звука. Единицы 1-8 разрядов в кодах звука представляются положительными полусинусоидами, единицы в разрядах 9-16 представляются отрицательными полусинусоидами. С приходом в счетчик 105 800-го импульса строки сигнал с третьего выхода дешифратора 106 закрывает ключ 104. Начинается период следующей строки, в котором с блока 43 первый код строки является кодом ССИ, поступающей на третий вход элемента ИЛИ 92, и код СИС с блока 45, поступающий на второй вход элемента ИЛИ 100. Коды ССИ и СИС являются первыми кодами первой строки только в правом кадре. Далее процессы повторяются. Спектр амплитудно-модулированного сигнала передатчика 48 /фиг.22/ состоит из несущей частоты и двух боковых частот. Сама несущая и одна из боковых частот в информационном смысле являются избыточными, поэтому в каждом амплитудном модуляторе 50, 52 подавляется несущая частота и отфильтровывается одна из боковых /ненужная/ частот. Амплитудный модулятор 50 выдает в выходной усилитель 51 верхнюю боковую частоту 2560 МГц /fН+160/, амплитудный модулятор 52 выдает в выходной усилитель 53 нижнюю боковую частоту 2240 МГц /fН-160 МГц/. Первый канал передатчика 48 излучает верхнюю боковую частоту с информацией кодов RП, GП, /RП, GЛ / и при стабильности несущей 10-7 занимает в эфире полосу ±256 Гц или 512 Гц. Второй канал излучает нижнюю боковую частоту с информацией кодов ВП/ВЛ, и занимаемая полоса в эфире ±224 Гц или 448 Гц, что составляет всего 0,00002% от несущей частоты.

выходной ключ 73, на сигнальный вход которого поступают синусоидальные колебания частоты 160 МГц. Выходной ключ 73 в открытом состоянии пропускает одну положительную полусинусоиду на выход. Аналогичный процесе проходит код, поступивший на первые входы блока 75 элементов И, импульсы с которого открывают на время своей длительности /6,25 нс/ второй выходной ключ 78, который в открытом состоянии пропускает одну отрицательную полусинусоиду. Выходы ключей 73, 78 объединены. На выходе блока 41 выходной сигнал представляется полными или неполными синусоидами частоты 160 МГц со стабильностью 10-7. Нули представляются отсутствием полусинусоид. Эти сигналы и модулируют несущую частоту 2400 МГц в модуляторе 50 передатчика 48. Очередность формирования сигналов ССИ, кодов отсчетов строки и кодов звука определяют сигналы с дешифратора 89. В исходном состоянии ключ 86 закрыт. Счетчик 88 импульсов 10-разрядный, ведет счет 800 импульсов дискретизации строки. При коде 00000001 в дешифраторе 89 с его первого выхода импульс открывает ключ 86, пропускающий сигналы 20 МГц в качестве сигналов UП в блок 74, 79, и со второго отсчета строки формируются коды видеосигналов по 797 отсчет строки. При 797 импульсе в счетчике 88 код 1100011101, дешифратор 89 при этом коде выдает сигнал со второго выхода, который закрывает ключ 86 и открывает ключ 87. Импульс UП с ключа 87 запускает блоки 82, 85, на вторые входы блоков 72, 77 элементов ИЛИ поступают соответственно 1-8 и 9-16 импульсы кодов звука. Ключ 87 открыт на время прохода трех кодов звука: 798, 799, 800 отсчетов строки. При поступлении в счетчик 800-го импульса строки с третьего выхода дешифратора 89 импульс закрывает ключ 87 и является вторым выходным сигналом с блока 41, который запускает UП самоходный распределитель 43 импульсов, который в момент первого отсчета строки подает на третьи входы элементов 72, 77 код ССИ. Этот код является первым кодом в каждой строке. Далее процессы повторяются. В кодах звука единицы в разрядах 1-8 представляются положительными полусинусоидами, в разрядах 9-16 представляются отрицательными полусинусоидами. На первый вход формирователя 42 кодов /фиг.8/ поступают коды с АЦП 38 сигналов ВП/ВЛ/ 7 на первые входы блока 90 элементов И, на вторые входы которого поступают 8 импульсов с блока 94. С выходов блока 90 импульсы последовательно через элементы ИЛИ 91, 92 открывают на время своей длительности /6,25 нс/ выходной ключ 93, на сигнальный вход которого поступают синусоидальные колебания 160 МГц. Ключ 93 в открытом состоянии пропускает одну положительную полусинусоиду. Единицы кодов В представляются положительными полусинусоидами. С приходом в дешифратор 106 кода 797-го отсчета строки сигнал со второго выхода дешифратора 106 закрывает ключ 103 и открывает ключ 104. С блоков 97, 102 на вторые входы блоков 95, 98 поступают по 8 импульсов, и с выходов этих блоков на второй элемента ИЛИ 92 и на первый вход элемента ИЛИ 100 поступают три кода сигнала звука. Единицы 1-8 разрядов в кодах звука представляются положительными полусинусоидами, единицы в разрядах 9-16 представляются отрицательными полусинусоидами. С приходом в счетчик 105 800-го импульса строки сигнал с третьего выхода дешифратора 106 закрывает ключ 104. Начинается период следующей строки, в котором с блока 43 первый код строки является кодом ССИ, поступающей на третий вход элемента ИЛИ 92, и код СИС с блока 45, поступающий на второй вход элемента ИЛИ 100. Коды ССИ и СИС являются первыми кодами первой строки только в правом кадре. Далее процессы повторяются. Спектр амплитудно-модулированного сигнала передатчика 48 /фиг.22/ состоит из несущей частоты и двух боковых частот. Сама несущая и одна из боковых частот в информационном смысле являются избыточными, поэтому в каждом амплитудном модуляторе 50, 52 подавляется несущая частота и отфильтровывается одна из боковых /ненужная/ частот. Амплитудный модулятор 50 выдает в выходной усилитель 51 верхнюю боковую частоту 2560 МГц /fН+160/, амплитудный модулятор 52 выдает в выходной усилитель 53 нижнюю боковую частоту 2240 МГц /fН-160 МГц/. Первый канал передатчика 48 излучает верхнюю боковую частоту с информацией кодов RП, GП, /RП, GЛ / и при стабильности несущей 10-7 занимает в эфире полосу ±256 Гц или 512 Гц. Второй канал излучает нижнюю боковую частоту с информацией кодов ВП/ВЛ, и занимаемая полоса в эфире ±224 Гц или 448 Гц, что составляет всего 0,00002% от несущей частоты.

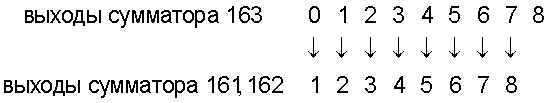

На приемной стороне принимаются два радиосигнала блоками 106, 129 /фиг.9/, являющиеся селекторами каналов соответствующих диапазонов с электронной настройкой. Каждый блок включает входную цепь, усилитель радиочастоты и смеситель [8 c.132]. Полосовой фильтр усилителя радиочастоты перестраивается в блоке 108 /129/ напряжением смещения с блока 107 управления /выбора каналов/. Радиочастотный сигнал через петлю связи поступает на смеситель, сюда же с синтезатора 147 частот /выход 5/ подается частота, равная несущей передатчика 48 /фиг.1/, которая необходима для детектирования однополосного сигнала [9 c.146]. Сигнал со смесителя, являющийся выходным сигналом блока 106 /129/, поступает на вход усилителя 109 /130/ радиочастоты, где усиливается до необходимой величины и поступает на вход двухполярного амплитудного детектора 110/131/. Вторые входы синтезатора 147 частот подключены к второй группе выходов блока 107 управления, при включении канала передачи сигнал с соответствующего выхода блока 107 поступает в блок 147 и определяет выход требуемой несущей частоты на третьи входы блоков 108, 129. Двухполярные амплитудные детекторы 110, 131 выполнены по схеме на фиг.10. Диод Д1 выделяет положительную огибающую модулирующего сигнала /фиг.23/. Диод Д2 из модулирующей выделяет огибающие положительных полусинусоид /символы единиц кодов R/, диод Д3 из модулирующей выделяет огибающие отрицательных полусинусоид /символы единиц кодов G/. Аналогично в блоке 131 для сигнала В. С первого выхода двухполярного амплитудного детектора продетектированные положительные полусинусоиды /частоты 160 МГц/ поступают на вход формирователя 111/132/ импульсов, со второго выхода продетектированные отрицательные полусинусоиды поступают на вход второго формирователя 112/133/ импульсов. Формирователи импульсов выполнены по схеме несимметричного триггера с эмиттерной связью [10 с.2091], формирующего прямоугольные импульсы из гармонически изменяющихся сигналов. Импульсы имеют одну полярность и длительность, равную длительности импульсов в кодах на передающей стороне. Единицы в кодах теперь представляются наличием импульса, нули - их отсутствием. Порядок работы приемной стороны определяются сигналами управления с канала формирования управляющих сигналов. Задающая роль принадлежит блоку 146 выделения ССИ. С приходом трех кодов ССИ блок 146 выдает строчный синхроимпульс ССИ, поступающий на первый вход синтезатора 147 частот, по ним выполняется подстройка частоты в блоке 147 под частоту и фазу задающего генератора 39 на передающей стороне. Собственная стабильность частоты синтезатора 147 частот 10-6. Синтезатор 146 частот выдает: с первого выхода импульсы дискретизации 20 МГц на первые управляющие входы регистров 113, 121, 134, на управляющие входы блоков 114, 122, 135 обработки кодов и на сигнальный вход первого ключа 148, со второго выхода - тактовые импульсы 160 МГц на вторые управляющие входы регистров 113, 121, 134 и на третьи управляющие входы каналов воспроизведения звука, с третьего выхода - импульсы 75 кГц дискретизации кодов звука на четвертые управляющие входы каналов воспроизведения звука, с четвертого - импульсы 40 МГц двойной частоты дискретизации на первые управляющие входы сумматоров 116; 124, 137 и на третьи управляющие входы первых и вторых накопителей кодов 118, 119, с пятого - синусоидальные колебания несущей частоты в блоки 106, 129, с шестого выхода - импульсы 50 Гц частоты кадров через второй ключ 1512 на первые управляющие входы первых и вторых накопителей кодов 118, 119 и на управляющие входы блоков 120, 128, 141 управляющих сигналов. Коды с блоков 111, 112, 132 в последовательном виде поступают соответственно на информационные входы регистра 113 сигнала R, регистра 121 сигнала G и регистра 134 сигнала В, с которых выдаются импульсами 20 МГц в свои блоки 114, 122, 135 обработки кодов, выполняющие удвоение отсчетов в каждой строке с 800 до 1600 получением промежуточных /средних/ отсчетов кодов между каждым прошедшим кодом и следующим за ним. Блоки выполняют сложение предыдущего кода с последующим и деление кода суммы пополам. Деление выполняются без временных затрат путем отбрасывания младшего разряда /как это делается при делении десятичного числа на 10/. Для этого выполняется соответствующее поразрядное подключение выходов сумматора 163 /фиг.11/ и выходов блоков 161, 162 задержек:

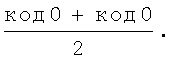

Разряд 0 означает перенос в старший разряд при сложении кодов. Удвоение отсчетов в строке сокращает период следования кодов в два раза, составляющий 25 нс  , т.е. 40 МГц. Поэтому процесс сложения должен занимать 25 нс. В сумматоре 163 применяются микросхемы К555ИМ6 с временем сложения 25 нс [11 с.258]. После включения питания в регистрах 157-160 нули. Первый импульс 20 МГц, поступающий в триггер 154, обнуляет сумматор 163. Сигнал Uвыд1 с первого выхода триггера 154 одновременно выдает: "код 0" с регистра 159 в блок 162 задержек, задерживающий код на 50 нс и через диоды в сумматор 163, из регистра 157 "код 0" в сумматор 163 открывает ключи в блоке 155 на время своей длительности, и регистры 157, 158 заполняются кодом "код 1". В сумматоре 163 идет сложение "код 0+код 0", по окончании которого /25 нс/ первый код суммы с сумматора 163 идет на выход, при котором делится на 2: код №1

, т.е. 40 МГц. Поэтому процесс сложения должен занимать 25 нс. В сумматоре 163 применяются микросхемы К555ИМ6 с временем сложения 25 нс [11 с.258]. После включения питания в регистрах 157-160 нули. Первый импульс 20 МГц, поступающий в триггер 154, обнуляет сумматор 163. Сигнал Uвыд1 с первого выхода триггера 154 одновременно выдает: "код 0" с регистра 159 в блок 162 задержек, задерживающий код на 50 нс и через диоды в сумматор 163, из регистра 157 "код 0" в сумматор 163 открывает ключи в блоке 155 на время своей длительности, и регистры 157, 158 заполняются кодом "код 1". В сумматоре 163 идет сложение "код 0+код 0", по окончании которого /25 нс/ первый код суммы с сумматора 163 идет на выход, при котором делится на 2: код №1  Блоки 161, 162 задерживают коды на 50 нс, причем первая половина задержки 25 не приходится на процесс сложения в сумматоре 163. Поэтому через 25 нс вслед за кодом №1 идет с блока 162 код №2 "код 0".

Блоки 161, 162 задерживают коды на 50 нс, причем первая половина задержки 25 не приходится на процесс сложения в сумматоре 163. Поэтому через 25 нс вслед за кодом №1 идет с блока 162 код №2 "код 0".

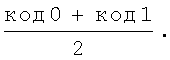

Второй импульс, поступающий в триггер 154, обнуляет сумматор 163. Сигнал Uвыд2 с второго выхода триггера одновременно выдает: "код 1" с регистра 158 в блок 161 задержек и через диоды в сумматор 163 "код 0" с регистра 160 в сумматор 163 открывает ключи в блоке 156, и регистры 159, 160 заполняются кодом "код 2", в сумматоре идет сложение "код 0 + код 1", по окончании которого код суммы идет на выход, при этом делится на 2: код №3  Через 25 нс за ним следует с блока 161 код №4 "код 1".

Через 25 нс за ним следует с блока 161 код №4 "код 1".

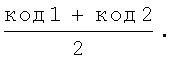

Третий импульс, поступающий в триггер 154, обнуляет сумматор 163. Сигнал Uвыд3 первого выхода триггера одновременно выдает: "код 2" с регистра 159 в блок 162 и через диоды в сумматор 163, из регистра 157 "код 1" в сумматор открывает ключи в блоке 155, регистры 157, 158 заполняются следующим кодом "код 3". В сумматоре 163 идет сложение "код 1 + код 2", по окончании которого код суммы идет на выход, при котором делится на 2: код №5  Через 25 нс за кодом №5 следует с блока 162 код №6 "код 2".

Через 25 нс за кодом №5 следует с блока 162 код №6 "код 2".

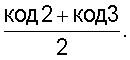

Четвертый импульс, поступающий в триггер 154, обнуляет сумматор 163, а сигнал Uвыд4 с второго выхода триггера одновременно выдает: код "код 3" с регистра 158 в блок 161 задержек и через диоды в сумматор, "код 2" с регистра 160 в сумматор открывает ключи в блоке 156, регистры 159, 160 заполняются кодом "код 4". В сумматоре 163 идет сложение "код 2 + код 3", по окончании которого код суммы идет на выход с делением на 2: код №7  Через 25 нс за ним с блока 162 следует код №8 "код 3".

Через 25 нс за ним с блока 162 следует код №8 "код 3".

Пятый импульс, поступающий в триггер 154, обнуляет сумматор 163. Сигнал Uвыд5 первого выхода триггера одновременно выдает: "код 4" с регистра 159 в блок 162 и через диоды в сумматор, из регистра 157 "код 4" в сумматор 163 открывает ключи в блоке 155, "код 5" заполняет регистры 157, 158. В сумматоре идет сложение "код 3 + код 4", по окончаний которого код суммы идет на выход, при котором делится на два: код №9  Через 25 нс за ним следует с блока 162 код №10 "код 4". С приходом шестого и следующих импульсов в триггер 154 процессы повторяются. С блока 114 коды в параллельном виде и с частотой 40 МГц поступают в первый блок задержек, во второй блок 117 задержек и на первые входы сумматора 116 /фиг.9/. Также и с блоков 123 и 136. Для удвоения строк в кадре необходимым условием является задержка кодов текущей строки относительно кодов следующей строки на ее длительность 40 мкс. В заявляемой системе направление разверток нечетных строк относительно четных встречное /фиг.2/. Первые блоки 115, 123, 136 задержек выполняют задержку кодов текущей строки на 40 мкс. С приходом импульса 50 Гц и импульса ССИ 25 кГц в элемент И 164 /фиг.12/ выходной сигнал Uот открывает ключ 165, пропускающий импульсы 40 МГц с блока 147 в распределитель 167 импульсов. Тактовые импульсы с распределителя 167 импульсов с первого по 1600 поступают на первые/тактовые/ входы с первого по 1600 разряды восьми регистров 169. На 1-8 информационные входы блока 115 /123, 136/ поступают сигналы кодов с первого по 1600 отсчеты первой строки /нечетной/ с блока 114. Сигналы первого разряда кода поступают на вторые входы разрядов первого регистра 1691, сигналы второго разряда кода поступают на вторые входы разрядов второго регистра 1692 и т.д., сигналы восьмого разряда кодов поступают на вторые входы разрядов восьмого регистра 1698. По окончании периода первой строки 1600 разрядов регистров 169 заполнены сигналами кодов строки. В период второй строки идет последовательная выдача 1600 кодов из регистров 169 в сумматор 116 /124, 137/ при одновременном заполнении освобождающихся регистров сигналами кодов второй строки.

Через 25 нс за ним следует с блока 162 код №10 "код 4". С приходом шестого и следующих импульсов в триггер 154 процессы повторяются. С блока 114 коды в параллельном виде и с частотой 40 МГц поступают в первый блок задержек, во второй блок 117 задержек и на первые входы сумматора 116 /фиг.9/. Также и с блоков 123 и 136. Для удвоения строк в кадре необходимым условием является задержка кодов текущей строки относительно кодов следующей строки на ее длительность 40 мкс. В заявляемой системе направление разверток нечетных строк относительно четных встречное /фиг.2/. Первые блоки 115, 123, 136 задержек выполняют задержку кодов текущей строки на 40 мкс. С приходом импульса 50 Гц и импульса ССИ 25 кГц в элемент И 164 /фиг.12/ выходной сигнал Uот открывает ключ 165, пропускающий импульсы 40 МГц с блока 147 в распределитель 167 импульсов. Тактовые импульсы с распределителя 167 импульсов с первого по 1600 поступают на первые/тактовые/ входы с первого по 1600 разряды восьми регистров 169. На 1-8 информационные входы блока 115 /123, 136/ поступают сигналы кодов с первого по 1600 отсчеты первой строки /нечетной/ с блока 114. Сигналы первого разряда кода поступают на вторые входы разрядов первого регистра 1691, сигналы второго разряда кода поступают на вторые входы разрядов второго регистра 1692 и т.д., сигналы восьмого разряда кодов поступают на вторые входы разрядов восьмого регистра 1698. По окончании периода первой строки 1600 разрядов регистров 169 заполнены сигналами кодов строки. В период второй строки идет последовательная выдача 1600 кодов из регистров 169 в сумматор 116 /124, 137/ при одновременном заполнении освобождающихся регистров сигналами кодов второй строки.

Выдача сигналов выполняется передним фронтом тактового импульса, занесение сигналов поступающих кодов производится этим же импульсом. В связи с тем, что развертка второй строки идет встречно к первой строке, выдача кодов с регистров 169 производится в обратном порядке, начиная с 1600-х разрядов регистров 1691-8. Заполнение освобождающихся разрядов регистров кодами второй строки также начинается с 1600-х разрядов. Выполняется вторым распределителем 168 импульсов, выходы которого подключены к первым /тактовым/ входам разрядов регистров в обратном порядке: первый выход подключен к 1600-м разрядам регистров 169, а 1600-й выход подключен к первым разрядам регистров 169. При развертке третьей строки выдача кодов с регистров выполняется импульсами с распределителя 167 импульсов, начиная с первых разрядов регистров 169. Таким образом, выполняется сложение одноименных отсчетов строк текущей и задержанной. На первые входы сумматора 116 /124, 137/ приходят коды текущей строки, на вторые входы сумматора приходят коды с блока 115, задержанные коды тех же отсчетов предыдущей строки. Сумматоры 116, 124, 137 идентичны, выполнены из микросхем К555ИМ6 с временем срабатывания 25 нс. Деление кода суммы на 2 выполняется соответствующим подключением выходов сумматора к входам своего накопителя кодов так, что отбрасывается младший разряд в коде суммы. Вторые блоки задержек 117, 125, 138 задерживают коды на 25 нс, на время срабатывания сумматоров, чтобы одноименные коды промежуточной и текущей строк приходили на входы накопителей кодов 118, 119 синхронно. Накопители кодов работают идентично. Сигналы разрядов кодов в каждом накопителе кодов поступают на информационные 1-8 входы с 1-го по 500-й блоки 171 регистров /фиг.13/, а в блоке регистров 171 /фиг.14, 15/ сигналы разрядов кодов поступают на третьи входы разрядов регистров.

Работа накопителей кодов, фиг.13.

Все накопители кодов работают синхронно. С шестого выхода блока 147 импульсы 50 Гц через открытый импульсом СИС ключ 1512 поступают на первые входы /вход триггера 170/ накопителей 118, 119, 126, 127, 139, 140 кодов. С первого выхода триггера 170 сигнал поступает на первый управляющий вход блока 1711 регистров и включает его в работу по накоплению кодов первой строки кадра. Информационные входы 500 блоков 171 поразрядно объединены, регистры блока 1711 заполняются 1600 кодами первой строки. С приходом 1600-го кода строки первый выходной управляющий сигнал с блока 1711 поступает на первый управляющий вход второго блока 1712 и запускает его в процесс накопления кодов второй строки. По заполнению регистров блока 1712 первый выходной управляющий сигнал с него запускает в работу блок 1713 регистров и т.д, процесс повторяется до заполнения кодами 500-й строки регистров в блоке 171500. Первый выходной управляющий сигнал с блока 171500 через диод поступает на четвертые управляющие входы всех блоков 1711-500 и выдает коды 500 строк синхронно в свой блок /120, 128, 141/ управляющих сигналов. С приходом второго импульса 50 Гц в триггер 170 сигнал с его второго выхода поступает на пятый управляющий вход блока 171500 и включает его в работу по накоплению кодов первой нижней строки /фиг.2/ левого кадра стереопары. Развертка левого кадра идет снизу вверх, поэтому первой строкой кадра является нижняя строка. По заполнении кодами первой строки регистров в блоке 171500 второй выходной управляющий сигнал с блока 171500 поступает на пятый управляющий вход блока 171499 и включает его в процесс заполнения кодами второй строки /снизу/ и т.д. По заполнении кодами 500-й строки в блоке 1711 его второй выходной управляющий сигнал через диод поступает на четвертые управляющие входы всех блоков 1711-500 регистров и выдает из них коды 500 строк в соответствующий блок управляющих сигналов. Затем сигнал с первого выхода триггера 170 поступает на первый управляющий вход блока 1711 регистров и процесс повторяется.

Работа блока 171 регистров, фиг.14, 15.

Сигнал с первого выхода триггера 170 поступает на первый управляющий вход первого ключа 172, открывает его. Ключ 172 пропускает импульсы Uд 40 МГц на вход распределителя 175 импульсов, с выходов которого импульсы Uт последовательно поступают на первые входы разрядов восьми регистров 177, на третьи входы разрядов которых поступают коды сигнала RП/RЛ/. По заполнении всех разрядов регистров 1771-8 импульс с 1600-го выхода блока 175 закрывает ключ 172 и является первым выходным управляющим сигналом, который открывает ключ 172 в следующем блоке 1712 регистров, и в нем идет заполнение разрядов регистров кодами второй строки. За период кадра 20 мс последовательно заполняются регистры 177 всех блоков 1711-500. Выходной управляющий сигнал с блока 171500 через диод поступает на четвертые управляющие входы всех блоков 171 и открывает в них третьи ключи 174, которые пропускают один импульс Uвыд 25 кГц, который поступает параллельно на вторые входы всех разрядов регистров 177 и выдает синхронно все коды кадра в соответствующий блок управляющих сигналов. Ключ 174 закрывает прошедшим импульсом. При левом кадре стереопары сигнал с второго выхода триггера 170 поступает на пятый управляющий вход блока 171500 и открывает второй ключ 173, который пропускает импульсы Uд на вход второго распределителя 176 импульсов, с выходов которого тактовые импульсы поступают на первые входы разрядов регистров 177. Чтобы использовать уже имеющиеся подключения выходов разрядов блоков 171 к входам блоков 120, 128, 141 управляющих сигналов последовательность подключения выходов второго распределителя 176 импульсов к первым входам разрядов регистров 177 меняется на обратную: первый выход блока 176 подключается к последним /1600-м/ разрядам регистров 177, а последний /1600-й/ выход блока 176 подключается к первым входам первых разрядов регистров 177. Для исключения прохождения на первый и второй управляющие выходы ненужных сигналов 1600-й выход с блока 175 подключается к входам последних разрядов регистров 177 через диод, и 1600 выход с блока 176 подключается к входам первых разрядов регистров через диод. Каждый накопитель кодов имеет 6400000 выходов /1600×8×500/. Накопители 118, 119 кодов подключены к блоку 120 управляющих сигналов, накопители 126, 127 подключены к блоку 128 управляющих сигналов, накопители 139, 140 подключены к блоку 141 управляющих сигналов. Каждый из блоков управляющих сигналов включает по 1600000 /1600×500×2/ преобразователей "код - число импульсов", выходы которых подключены к соответствующим входам в СД-экране 142, всего входов в СД-экран 4800000 /1600000×3/. В связи с большим числом соединений между накопителями кодов, блоками управляющих сигналов и СД-экраном лучшим вариантом для надежной и длительной работы будет исполнение этих блоков на тыльной стороне СД-экрана в единой с ним неразборной конструкции.

Работа системы.

ФЭП 1 формирует три аналоговых сигнала правого кадра, затем три аналоговых сигнала левого кадра, которые преобразуются АЦП 36, 37, 38 в 8-разрядные коды с дискретизацией 20 МГц. Первый и второй формирователи 41, 42 кодов преобразуют параллельные коды в последовательные и заменяют в кодах символы единиц с импульсов на положительные и отрицательные полусинусоиды частоты 160 МГц.

В блоке 41 к кодам в каждой строке добавляется синхроимпульс строк ССИ, в блоке 42 к первой строке каждого правого кадра добавляется первым кодом код СИС стереопары. Последними тремя отсчетами в каждой строке являются коды звука, информация кодов передается верхней и нижней боковыми частотами одной несущей частоты. На приемной стороне принимаются два радиосигнала двумя трактами приема и обработки кодов, производится детектирование, выделяются синхроимпульсы строк ССИ и стерепар СИС. Синтезатор 147 частот /фиг.9/ воспроизводит несущую частоту. Представление символов единил возвращается к импульсам. Коды цветовых сигналов R, G, В распределяются по своим каналам. Блоки 114, 122, 135 удваивают число отсчетов в каждой строке /800×2/, сумматоры 116, 124, 137 удваивают число строк /500×2/ в кадре. За период кадра накопители кодов 118, 119, 126, 127, 139, 140 производят накопление кодов кадра трех цветовых сигналов, которые в следующем периоде кадра синхронно выдаются в блоки 120, 128, 141 управляющих сигналов. Преобразователи "код-число импульсов" блоков 120, 128, 141 запитывают светодиоды в СД-экране. Каждый светодиод за период кадра излучает световые импульсы, число которых пропорционально величине кода сигнала. Видеорежим на приемной стороне 1600×1000×50 Гц. Объемным изображение зритель воспринимает через ЗД-очки 144. Звуковое сопровождение выполняется двумя каналами 152, 153 воспроизведения звука. На приемной стороне отпадает необходимость в строчной и кадровой развертках. Синхронизация работы блоков накопителей кодов с правого кадра стереопары выполняется введенным вторым ключом 1512, который открывается импульсом СИС с блока 1511.

Заявляемая система обходится одной несущей частотой и малой полосой в эфире, что определяет высокую помехозащищенность, приемная сторона имеет низковольтное питание, преобразователи "код - число импульсов" повышают яркость и достоверность цветопередачи воспроизводимого изображения на СД-экране.

Источники информации

1. Патент №2296297 С1 кл. Н04N 15/00, бюл.12 от 27.04.07, прототип.

2. Б.Н.Бегугов, Н.П.Заказнов. Теория оптических систем. М., 1973, с.225, 388.

3. Радиопередающие устройства. М.С.Шумилин и др. М., 1981, с.234, 235.

4. Фридлянд М.В, Сошников В.Г. Системы автоматического регулирования в устройствах видеозаписи. М., 1988, с.118 рис.5.5, с.122 рис.5.10.

5. Колесниченко О.В, Шишигин И.В. Аппаратные средства PC. 5-е изд., СПб, 2004, c.558, 565.

6. "Радио" №9, 2004, с.47.

7. Журнал "Приборы и системы управления" №1, 1990, с.40.

8. Бродский М.А. Телевизоры цветного изображения. Минск, 1988, с.132 рис.4.2.

9. Радиосвязь, вещание и телевидение. Под ред. А.Д.Фортушенко, М., 1981, с.146.

10. Баркан В.Ф, Жданов В.К. Усилительная и импульсная техника. М., 1984, с.209.

11. Цифровые интегральные микросхемы. Справочник. 1991, с.258.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2310996C1 |

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2004 |

|

RU2279708C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2356179C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2007 |

|

RU2339183C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2298297C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2334369C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2326508C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2316142C1 |

| ЦИФРОВАЯ СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2005 |

|

RU2292127C1 |

| ЦИФРОВАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ ВЫСОКОЙ ЧЕТКОСТИ | 2000 |

|

RU2194370C2 |

Изобретение относится к технике радиосвязи и может использоваться для цифрового телевещания. Техническими результатами являются снижение энергоемкости системы сокращением в ней третьего канала передачи - приема, повышение яркости изображения и достоверности цветопередачи, которые достигаются тем, что в систему стереотелевидения на передающей стороне в фотоэлектрический преобразователь вводятся две отражательные призмы, подвижное плоское зеркало, триггер и исполнительный механизм, передатчик радиосигналов выполняется двухканальным, а на приемной стороне вводится плоскопанельный светодиодный экран /СД-экран/ и в каждый канал сигнала R, G, В вводятся первый и второй накопители кодов и блок управляющих сигналов. 23 ил.