Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации.

Известен преобразователь кода (см. авторское свидетельство СССР №1809535 от 27.08.90, МКИ: МКИ: Н 03 М 5/12, "Устройство для преобразования дискретной информации в код", Н.И.Маркин, Г.П.Галахова и Н.Б.Фомина, опубл. 15.04.93, Бюл. №14), использующий в своем кодирующем устройстве трехуровневые коды, которые передаются по двум двухпроводным линиям связи с целью повышения помехоустойчивости и расширения функциональных возможностей схемы. Применение самосинхронизирующихся трехуровневых кодов, передаваемых по двум линиям связи с парафазными сигналами, позволяет обеспечить надежную передачу информации с обнаружением ошибок при передаче последовательностей нулей и единиц и защитой передаваемой информации от синфазной помехи.

Недостатками известного преобразователя кода являются сложность его реализации и большое количество линий связи, обусловленные тем, что необходимо формировать трехуровневые коды и передавать их по двум независимым двухпроводным линиям связи с парафазными сигналами.

Наиболее близким к заявляемому изобретению по совокупности существенных признаков является преобразователя кода (см. Б.В.Шевкопляс. Микропроцессорные структуры. Инженерные решения: Справочник. - 2-е изд. перераб. и доп. - М.: Радио и связь, 1990. - 512 с.: ил. стр.91-94, рис.3.3 и рис.3.4), содержащий центральный процессор (блок формирования кода), соединенный с контроллером (блок приема кода) через первую и вторую двухпроводные линии связи соответственно, кроме этого центральный процессор и контроллер через первую и вторую двухпроводные линии связи также соединены с первым и вторым согласующими блоками соответственно.

Недостатками известного преобразователя кода является его низкая помехоустойчивость и большое количество линий связи, обусловленные необходимостью наличия общей шины для передачи как информации, так и импульсов синхронизации тем, что мощная помеха промышленного происхождения, наводимая на выходные цепи блока формирования кода, линии связи и входные цепи блока приема кода, приводит к искажению передаваемой кодовой информации.

Задачей, решаемой предлагаемым техническим решением, является создание помехоустойчивого преобразователя кода, использующего для передачи самосинхронизирующийся код, и обладающего каналом связи с минимальным количеством линий связи.

Технический результат, заключающийся в увеличении помехоустойчивости и уменьшении количества линий связи, достигается тем, что в преобразователь кода, содержащий блоки формирования и приема кода, линию связи, дополнительно введены блоки преобразования и восстановления кода, соединенные между собой через линию связи, при этом выходы блока формирования кода соединены со входами блока преобразования кода, содержащего первый и второй логические элементы ИЛИ-НЕ и инвертор, выход которого соединен с первым входом первого логического элемента ИЛИ-НЕ, второй вход которого соединен со вторым входом второго логического элемента ИЛИ-НЕ и является входом синхронизации блока формирования кода, вход инвертора соединен с первым входом второго логического элемента ИЛИ-НЕ и является информационным входом блока формирования кода, выходы первого и второго логических элементов ИЛИ-НЕ являются соответственно первым и вторым выходами блока формирования кода, а входы блока приема кода соединены с выходами блока восстановления кода, содержащего первый и второй диоды, первый и второй резисторы и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый вход которого является одновременно первым входом и первым выходом блока восстановления кода и соединен с первым выводом первого резистора и с катодом первого диода, анод которого соединен с общей шиной нагружающего устройства, с анодом второго диода и со вторым и первым выводами первого и второго резистора соответственно, катод второго диода является вторым входом блока восстановления кода и соединен со вторым выводом второго резистора и со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого является вторым выходом блока восстановления кода.

Указанная совокупность признаков позволяет увеличить помехоустойчивость преобразователя кода при использовании минимального количества линий связи в канале связи (двухпроводная линия связи) за счет применения блока формирования самосинхронизирующегося кода, обеспечивающего передачу по информационному каналу с меньшим числом линий связи и не требующего синхронизации работы блока формирования кода и блока приема кода.

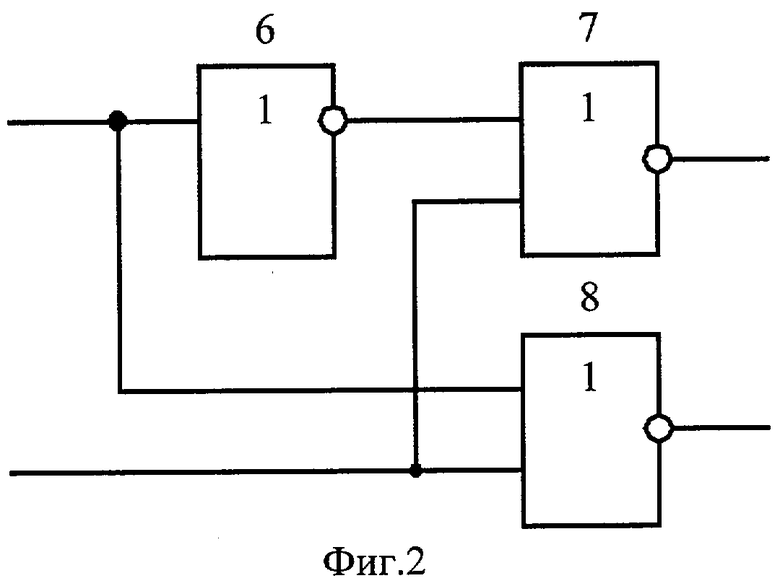

На фиг.1 представлена структурная схема преобразователя кода.

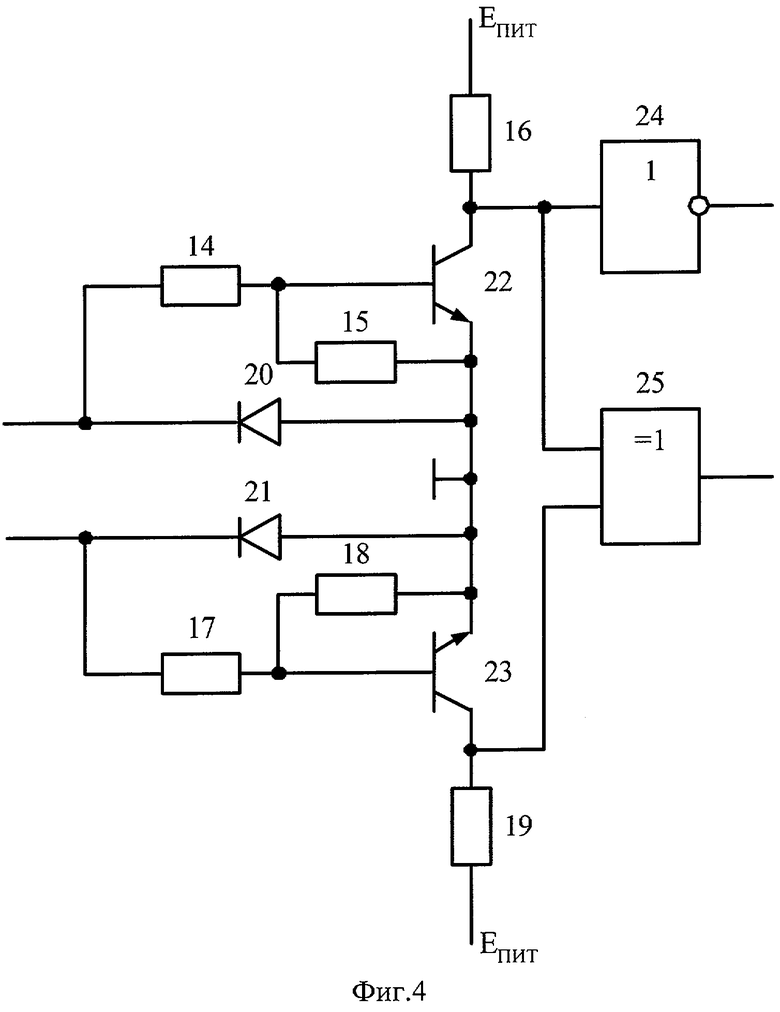

На фиг.2 представлена схема построения блока преобразования кода.

На фиг.3 представлен первый вариант построения блока восстановления кода.

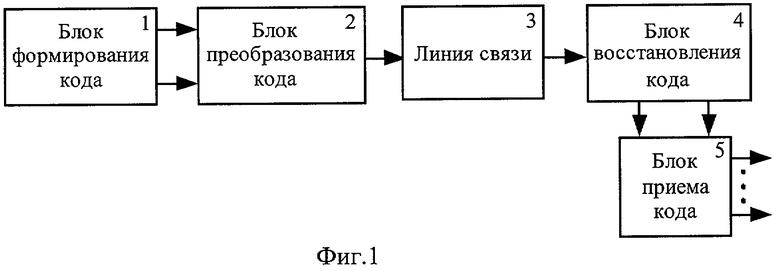

На фиг.4 представлен второй вариант построения блока восстановления кода.

Преобразователь кода содержит (см. фиг.1) блок формирования кода 1, блок преобразования кода 2, линию связи 3, блок восстановления кода 4, блок приема кода 5. Выходы блока формирования кода 1 соединены с соответствующими входами блока преобразования кода 2, выходы которого через линию связи 3 соединены с соответствующими входами блока восстановления кода 4, выходы которого соединены с соответствующими входами блока приема кода 5.

Блок преобразования кода 2 (фиг.2) содержит инвертор 6, логические элементы ИЛИ-НЕ 7 и 8. Вход инвертора 6 соединен с первым входом логического элемента ИЛИ-НЕ 8 и является информационным входом блока формирования кода, вторые входы логических элементов ИЛИ-НЕ 7 и 8 объединены и являются входом синхронизации блока формирования кода, выход инвертора 6 соединен с первым входом логического элемента ИЛИ-НЕ 7, выходы логических элементов ИЛИ-НЕ 7 и 8 являются соответственно первым и вторым выходами блока формирования кода.

Первый вариант блока восстановления кода 4 (фиг.3) содержит диоды 9, 10, резисторы 11, 12 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 13, первый вход блока восстановления кода 4 соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и катодом диода 9, анод которого соединен с анодом диода 10, катод которого через резистор 12 соединен с анодом диода 9 и общей шиной нагружающего устройства, второй вход блока восстановления кода 4 соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 и с катодом диода 10, анод которого через резистор 11 соединен с катодом диода 9, катод диода 9 является первым выходом блока восстановления кода 4, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 13 является вторым выходом блока восстановления кода 4.

Второй вариант блока восстановления кода 4 (фиг.4) содержит резисторы 14, 15, 16, 17, 18 и 19, диоды 20, 21, транзисторы 22, 23, инвертор 24 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 25, первый вход блока восстановления кода 4 соединен с катодом диода 20 и через резистор 14 - с базой транзистора 22, эммитер которого соединен с анодом диода 20, общей шиной нагружающего устройства и через резистор 15 соединен со своей базой, коллектор транзистора 22 соединен с входом инвертора 24 и через резистор 16 - с шиной питания, второй вход блока восстановления кода 4 соединен с катодом диода 21 и через резистор 17 - с базой транзистора 23, эммитер которого соединен с анодом диода 21, общей шиной нагружающего устройства и через резистор 18 соединен со своей базой, коллектор транзистора 23 соединен со вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 и через резистор 19 - с шиной питания, первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 соединен с входом инвертора 24, выход которого является первым выходом блока восстановления кода 4, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 является вторым выходом блока восстановления кода 4.

Блок формирования кода 1 может быть выполнен на микросхеме 1533ИР9, при этом входы D→, SEMO и DESYN соединены с общей шиной, входы DI0...DI7 параллельной записи являются входами данных, вход SYN - входом синхронизации и вторым выходом блока формирования 1, а выход D0 является первым выходом блока формирования 1. Линия связи 3 может быть выполнена в виде двухпроводной линии связи. Блок восстановления кода 5 может быть выполнен как показано на фиг.3 или, в случае с усилительным каскадом, как показано на фиг.4. Блок приема кода 5 может быть выполнен на микросхеме 1533ИР8, при этом вход  через резистор соединен с шиной питания, вход В - с общей шиной, вход А является первым (информационным) входом, С - вторым входом (входом синхронизации).

через резистор соединен с шиной питания, вход В - с общей шиной, вход А является первым (информационным) входом, С - вторым входом (входом синхронизации).

Преобразователь кода работает следующим образом (см. фиг.1).

Блок формирования кода 1 формирует последовательный двоичный код, в результате чего данные, поступающие на входы параллельной записи блока формирования кода 1, преобразуются из параллельного формата в последовательный. Последовательный двоичный код поступает на первый (информационный) вход, а сигналы синхронизации - на второй (тактовый) вход блока преобразования кода 2. Поступивший код и сигналы синхронизации преобразуются инвертором 7, логическими элементами ИЛИ-НЕ 8 и 9 в самосинхронизирующийся код для передачи по двухпроводной линии связи. При этом кодировании обязательно изменение уровня сигнала в середине каждого тактового интервала (информационный перепад) и необязательно - в начале интервала (тактовый перепад), причем для отображения лог. "1" принят переход с высокого уровня к низкому, а для лог. "0" - переход с низкого уровня к высокому, следует отметить, что в нашем случае высокий уровень - это положительный потенциал на первом проводе линии связи 3 относительно потенциала на втором проводе линии связи 3, а низкий уровень - положительный потенциал на втором проводе линии связи 3 относительно потенциала на первом проводе линии связи 3.

Кодовая последовательность, переданная по линии связи 3, поступает на блок восстановления кода 4 (см. фиг.3). При приходе лог. "1" диод 10 - закрыт, диод 11 - открыт, что приводит к протеканию тока по цепи "первый провод линии связи 3 - резистор 12 - диод 11 - второй провод линии связи 3" и падению напряжения на резисторе 12, т.е. на первом (информационном) выходе блока восстановления кода 4 устанавливается уровень лог. "1", который приводит к появлению уровня лог. "1" на первом входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 (в исходном состоянии на обоих входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 - уровень лог. "0") и, как следствие, к появлению уровня лог. "1" на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14, являющимся вторым (тактовым) выходом блока восстановления кода 4. При приходе лог. "0" диод 11 - закрыт, диод 10 - открыт, что приводит к протеканию тока по цепи "второй провод линии связи 3 - резистор 13 - диод 10 - первый провод линии связи 3" и падению напряжения на резисторе 13, т.е. на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 14 устанавливается уровень лог. "1", на первом входе - уровень лог. "0", а на выходе - уровень лог. "1". Таким образом, на первом (информационном) выходе блока восстановления кода 4 устанавливается уровень лог. "0", а на втором (тактовом) выходе блока восстановления кода 4 - уровень лог. "1".

При необходимости усиления сигнала можно применять блок восстановления кода 4, представленный на фиг.4. При приходе лог. "1" диод 21 - закрыт, ток протекает через делитель напряжений, выполненный на резисторах 14 и 15, и открывает транзистор 22, что приводит к протеканию тока не во внешнюю нагрузку, а по цепи "шина питания - резистор 16 - транзистор 22 - шина земли", т.е. на входе инвертора 24 устанавливается уровень лог. "0", который подается на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25, на второй вход которого подается сигнал лог. "1" (в исходном состоянии на обоих входах элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 - уровень лог. "1"), в результате на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25, а следовательно, и втором (тактовом) выходе блока восстановления кода 4 появляется уровень лог. "1", при этом на выходе инвертора 24 (первом (информационном) выходе блока восстановления кода 4) появляется уровень лог. "1". При приходе лог. "0" диод 21 - закрыт, ток протекает через делитель напряжений, выполненный на резисторах 17 и 18, и открывает транзистор 23, что приводит к протеканию тока не во внешнюю нагрузку, а по цепи "шина питания - резистор 19 - транзистор 23 - шина земли", т.е. на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25 устанавливается уровень лог. "0", на входе инвертора 24 остается уровень лог. "1", который подается на первый вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25, в результате на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 25, а следовательно, и втором (тактовом) выходе блока восстановления кода 4 появляется уровень лог. "1", при этом на выходе инвертора 24 (первом (информационном) выходе блока восстановления кода 4) появляется остается уровень лог. "0".

Таким образом, на выходе блока восстановления кода 4 получается последовательный двоичный код с сигналами синхронизации.

Последовательный двоичный код и сигналы синхронизации поступают в блок приема кода 5 и преобразуются из последовательного формата в параллельный.

При воздействии синфазной помехи происходит одновременное изменение потенциалов на двух проводах линии связи 3, однако изменения разности потенциалов между ними не происходит, что позволяет передавать кодовую последовательность без искажений, обеспечивая помехоустойчивость и уменьшение числа линий связи, необходимых для передачи кодовой информации.

Изготовлен лабораторный макет преобразователя кода, испытания которого подтвердили осуществимость и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО КОДИРОВАНИЯ, ПРИЕМА И ПЕРЕДАЧИ ЦИФРОВОЙ ИНФОРМАЦИИ ПО ДВУХПРОВОДНОЙ ЛИНИИ СВЯЗИ | 1996 |

|

RU2115240C1 |

| Устройство передачи и приема информации по двухпроводной линии связи | 1989 |

|

SU1767511A1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

| ЭЛЕКТРОСТИМУЛЯТОР | 1993 |

|

RU2121380C1 |

| Устройство для сопряжения с двухпроводной линией трактов приема и передачи | 1984 |

|

SU1193834A1 |

| Выходной каскад устройств для дистанционного управления коммутационным аппаратом | 1989 |

|

SU1737626A1 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СЕЙСМОРАЗВЕДОЧНАЯ СИСТЕМА | 1994 |

|

RU2107312C1 |

| Одновибратор | 1983 |

|

SU1129716A1 |

| Система шахтной телесигнализации с дистанционным питанием | 1984 |

|

SU1243141A1 |

Изобретение относится к вычислительной технике и может быть использовано в системах передачи цифровой информации. Технический результат - повышение помехоустойчивости. Преобразователь кода содержит блок формирования кода, блок преобразования кода, линию связи, блок восстановления кода, блок приема кода. Выходы блока формирования кода соединены с соответствующими входами блока преобразования кода, выходы которого через линию связи соединены с соответствующими входами блока восстановления кода, выходы которого соединены с соответствующими входами блока приема. 4 ил.

Преобразователь кода, содержащий блоки формирования и приема кода, линию связи, отличающийся тем, что дополнительно введены блоки преобразования и восстановления кода, соединенные между собой через линию связи, при этом выходы блока формирования кода соединены с входами блока преобразования кода, содержащего первый и второй логические элементы ИЛИ-НЕ и инвертор, выход которого соединен с первым входом первого логического элемента ИЛИ-НЕ, второй вход которого соединен со вторым входом второго логического элемента ИЛИ-НЕ и является входом синхронизации блока формирования кода, вход инвертора соединен с первым входом второго логического элемента ИЛИ-НЕ и является информационным входом блока формирования кода, выходы первого и второго логических элементов ИЛИ-НЕ являются соответственно первым и вторым выходами блока формирования кода, а входы блока приема кода соединены с выходами блока восстановления кода, содержащего первый и второй диоды, первый и второй резисторы и элемент исключающее ИЛИ, первый вход которого является одновременно первым входом и первым выходом блока восстановления кода и соединен с первым выводом первого резистора и с катодом первого диода, анод которого соединен с общей шиной нагружающего устройства, с анодом второго диода и со вторым и первым выводами первого и второго резистора соответственно, катод второго диода является вторым входом блока восстановления кода и соединен со вторым выводом второго резистора и со вторым входом элемента исключающее ИЛИ, выход которого является выходом блока восстановления кода.

| ШЕВКОПЛЯС Б.В., Микропроцессорные структуры, Инженерные решения, Справочник, 2-ое издание, переработанное, Москва, Радио и связь, 1990, стр.91-94, рис.3.3, 3.4 | |||

| RU 94032780, A1, 20.07.1996 | |||

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2206181C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| US 5160929, A, 03.11.1992 | |||

| БИБЛИОТЕКА IК. И. Умрихин и А. А. Шахназаров'~°°~~~~~~~~—• .. ~=»J | 0 |

|

SU299639A1 |

Авторы

Даты

2006-08-20—Публикация

2004-09-13—Подача