Изобретение относится к электронным схемам общего назначения, в частности к схемам кодирования, декодирования и преобразования данных при их передаче между удаленными друг от друга абонентами.

Известно устройство [1], содержащее подключенные к противоположным сторонам линии связи блоки передачи и приема данных, входы блоков передачи и выходы блоков приема данных являются входами и выходами устройства, линия связи содержит группу витых пар проводов по числу входов устройства. По одной из витых пар проводов линии передается сигнал синхронизации, по остальным витым парам - биты данных.

Недостатком устройства [1] является низкая эффективность использования линии связи. Для передачи n-разрядных слов линия должна содержать n+1 витую пару проводов, одна из которых используется для трансляции синхросигнала, а остальные - для пересылки битов данных.

Известно устройство [2] для кодирования - декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов соединен с входом шифратора и является первым выходом синхронизации первого канала устройства, группа входов данных первого канала устройства соединена с входами шифратора, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов линии связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и первый инвертор, входы группы входных усилителей соединены с витыми парами проводов линии связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных первого регистра и с входом элемента задержки, выход первого инвертора соединен с входом синхронизации первого регистра и является вторым выходом синхронизации первого канала устройства, группа выходов первого регистра является группой выходов данных первого канала устройства.

Устройство [2] преобразует параллельный двоичный код данных и синхросигнал в группу троичных сигналов, которая передается по линии связи, состоящей из группы витых пар проводов. На приемной стороне устройства группа троичных сигналов преобразуется в исходный двоичный код, сопровождаемый восстановленным синхросигналом.

Устройство [2] имеет недостаточно высокую скорость передачи данных и ограниченные функциональные возможности. Первый недостаток обусловлен двумя причинами. Во-первых, при шифрации данных для их передачи по линии связи используются не все потенциально возможные кодовые комбинации трехуровневых сигналов. Это, в свою очередь, приводит к тому, что дешифратор кодовых комбинаций оперирует не полным диапазоном кодов и поэтому не реализует потенциальные возможности восстановления кодированных данных. Во-вторых, в канале связи данные чередуются во времени с синхросигналом. Поэтому половина потенциальной пропускной способности канала связи теряется. Ограниченные функциональные возможности устройства не позволяют его использовать в многоканальном режиме с передачей признаков начала информационных кадров.

Цель изобретения - повышение скорости передачи данных и расширение функциональных возможностей устройства.

Цель достигается тем, что в устройстве для кодирования - декодирования данных, содержащем подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов соединен с входом шифратора и является первым выходом синхронизации первого канала устройства, группа входов данных первого канала устройства соединена с входами шифратора, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов линии связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и первый инвертор, входы группы входных усилителей соединены с витыми парами проводов линии связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных первого регистра и с входом элемента задержки, выход первого инвертора соединен с входом синхронизации первого регистра и является вторым выходом синхронизации первого канала устройства, группа выходов первого регистра является группой выходов данных первого канала устройства, блок передачи данных дополнительно содержит второй инвертор, вход которого соединен с выходом генератора синхросигналов, выход второго инвертора является первым выходом синхронизации второго канала устройства, входы кадровой синхронизации первого и второго каналов устройства и группа входов данных второго канала устройства соединены с входами шифратора, блок приема данных дополнительно содержит второй регистр и блок фазовой автоподстройки частоты, вход которого соединен с выходом элемента задержки, а выход - с входом первого инвертора и с входом синхронизации второго регистра и является вторым выходом синхронизации второго канала устройства, выходы кадровой синхронизации первого и второго каналов устройства соединены с выходами первого и второго регистров, группа выходов второго регистра является группой выходов данных второго канала устройства, входы данных второго регистра соединены с выходами дешифратора.

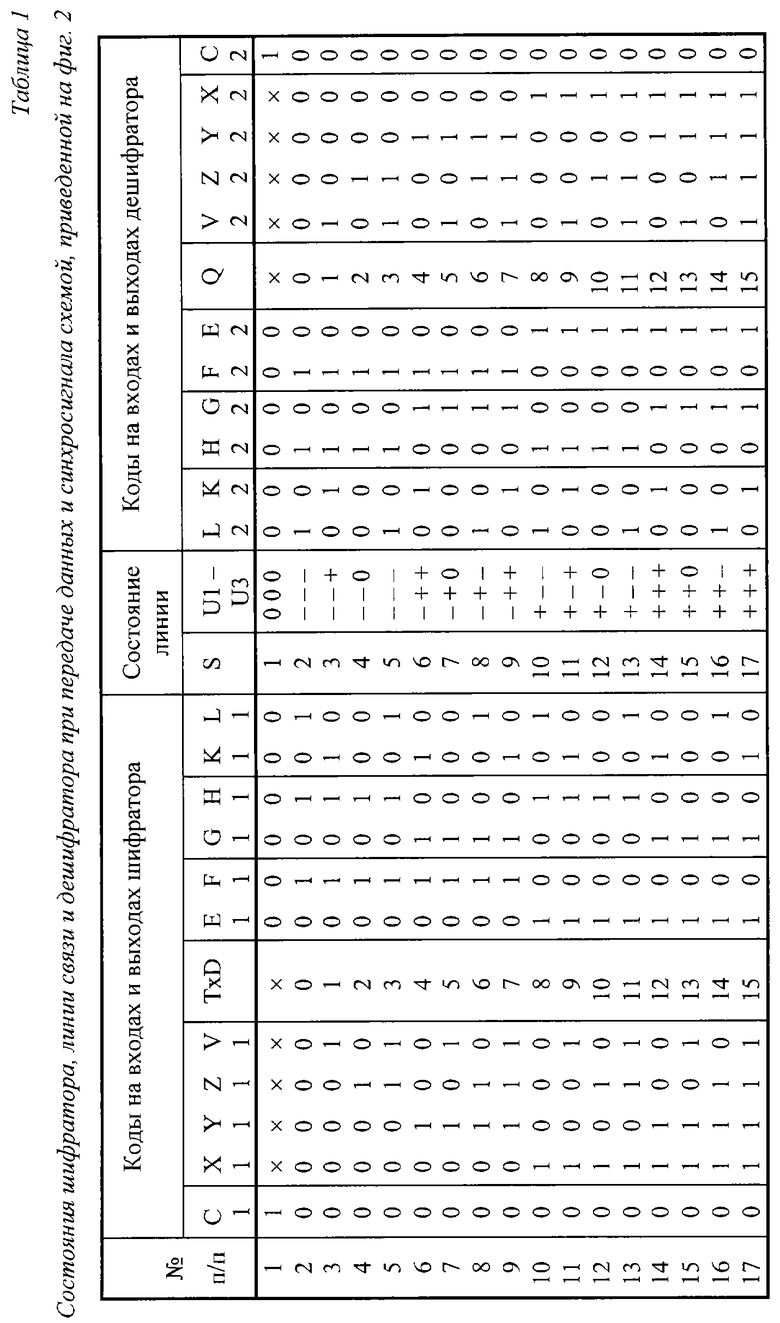

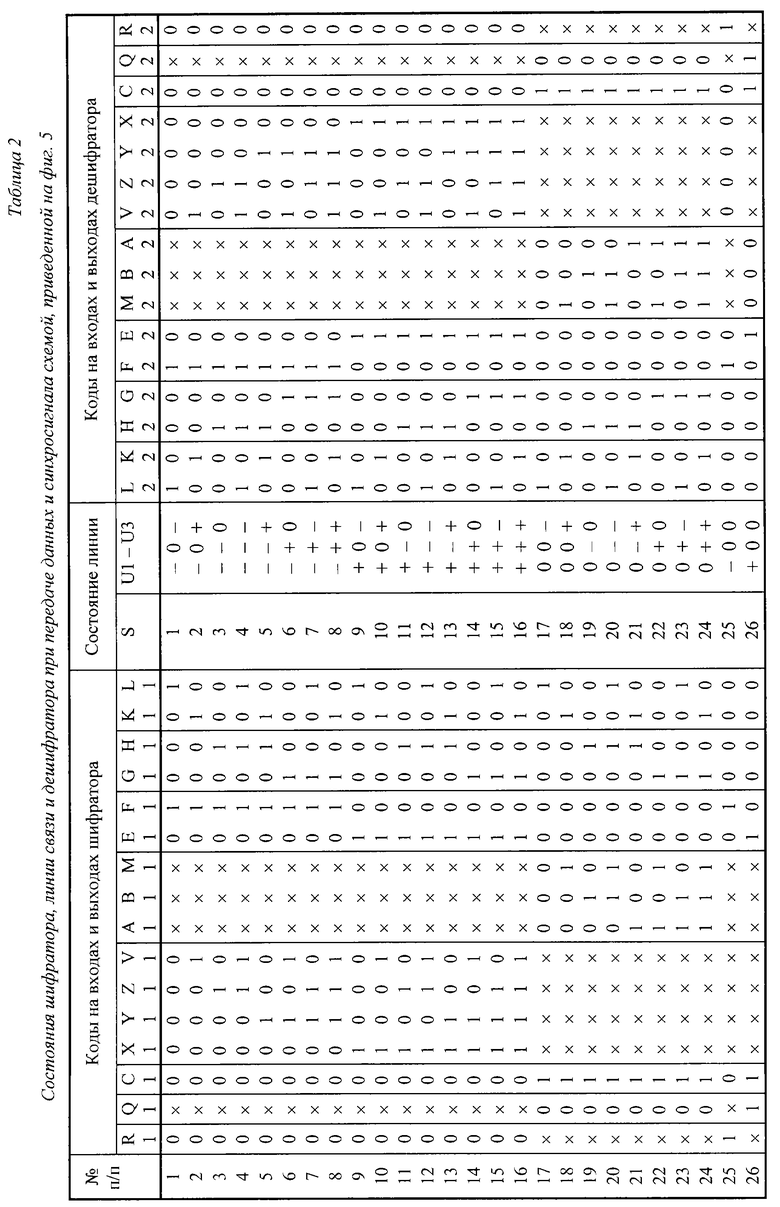

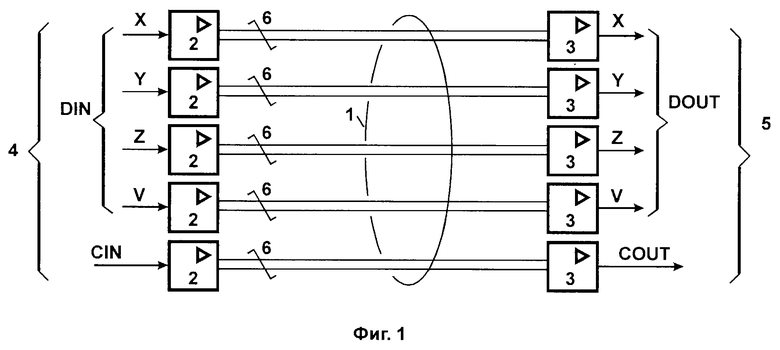

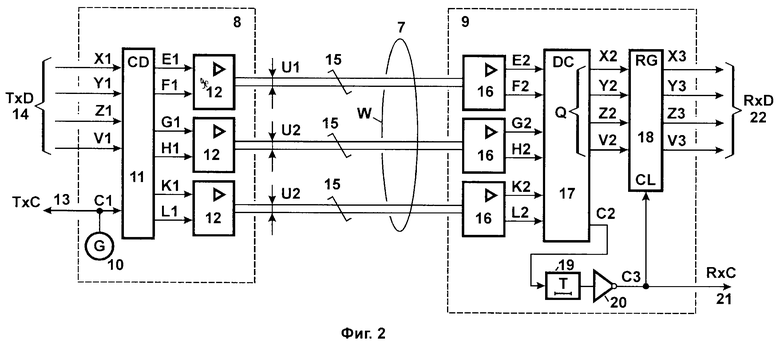

На фиг.1 и 2 представлены схемы известных устройств [1] и [2]; на фиг.3 - временные диаграммы передачи данных устройством [2]; на фиг.4 - пример схемы включения предлагаемого устройства в телекоммуникационную систему; на фиг. 5 - пример функциональной схемы предлагаемого устройства; на фиг.6 - временные диаграммы передачи данных предлагаемым устройством.

Устройство [1] (фиг.1) содержит подключенные к противоположным сторонам линии связи 1 блоки 2 передачи и 3 приема данных, входы 4 блоков передачи и выходы 5 блоков приема данных являются входами и выходами устройства, линия связи 1 содержит группу витых пар 6 проводов по числу входов устройства.

Устройство [2] (фиг.2) содержит подключенные к противоположным сторонам линии связи 7 блок 8 передачи данных и блок 9 приема данных, блок передачи данных содержит генератор 10 синхросигналов, шифратор 11, группу выходных усилителей 12, выход генератора 10 синхросигналов соединен с входом шифратора 11 и является первым выходом 13 синхронизации первого канала устройства, группа входов 14 данных первого канала устройства соединена с входами шифратора 11, группа выходов шифратора соединена с входами группы выходных усилителей 12, выходы которых соединены с витыми парами 15 проводов линии связи 7, блок 9 приема данных содержит группу входных усилителей 16, дешифратор 17, первый регистр 18, элемент задержки 19 и первый инвертор 20, входы группы входных усилителей 16 соединены с витыми парами 15 проводов линии связи 7, а их выходы - с входами дешифратора 17, выходы которого соединены с входами данных первого регистра 18 и с входом элемента задержки 19, выход первого инвертора 20 соединен с входом синхронизации первого регистра 18 и является вторым 21 выходом синхронизации первого канала устройства, группа выходов первого регистра 18 является группой выходов 22 данных первого канала устройства, выход элемента задержки 19 соединен с входом первого инвертора 20.

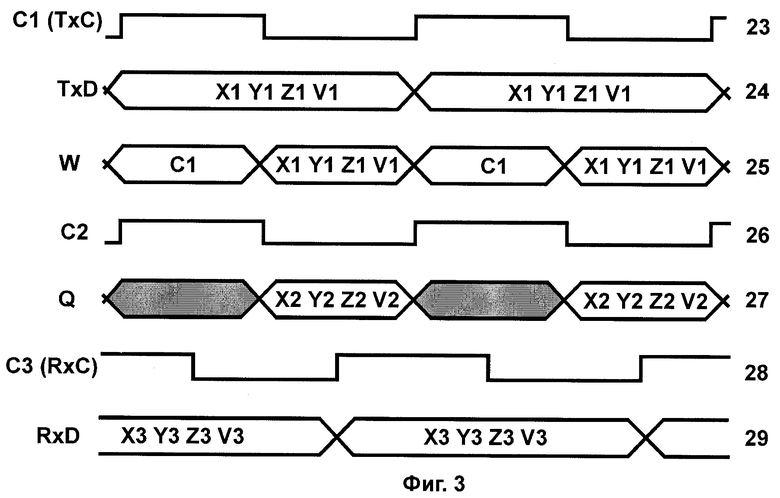

Временные диаграммы 23 и 24 (фиг.3) соответствуют сигналам на выходе 13 и входах 14 блока 8 (см. фиг.2); диаграмма 25 отображает сигналы в линии 7; диаграммы 26 и 27 соответствуют сигналам на выходах дешифратора 17; диаграммы 28 и 29 - сигналам на выходах 21 и 22 блока 9.

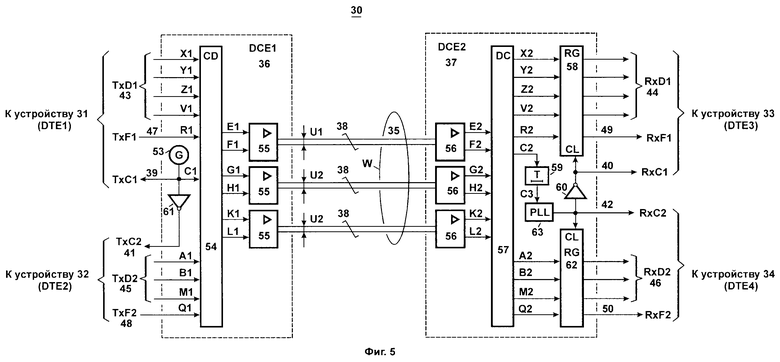

Телекоммуникационная система (фиг.4) содержит предлагаемое устройство 30 для кодирования - декодирования данных и подключенные к нему первое - четвертое 31-34 оконечные устройства DTE1-DTE4. Устройство 30 содержит подключенные к противоположным сторонам линии связи 35 блок 36 передачи данных (DCE1) и блок 37 приема данных (DCE2). Линия связи 35 содержит витые пары 38 проводов. Выходы 39 и 40 блоков 36 и 37 являются первым и вторым выходами синхронизации первого канала устройства 30. Выходы 41 и 42 блоков 36 и 37 являются первым и вторым выходами синхронизации второго канала устройства 30. Группа входов 43 блока 36 передачи данных является группой входов данных первого канала устройства 30. Группа выходов 44 блока 37 приема данных является группой выходов данных первого канала устройства 30. Группа входов 45 блока 36 передачи данных является группой входов данных второго канала устройства 30. Группа выходов 46 блока 37 приема данных является группой выходов данных второго канала устройства 30. Входы 47 и 48 блока 36 являются входами кадровой синхронизации первого и второго каналов устройства 30. Выходы 49 и 50 блока 37 являются выходами кадровой синхронизации первого и второго каналов устройства 30. Указатели 51 и 52 показывают направления передачи данных по первому и второму каналам связи.

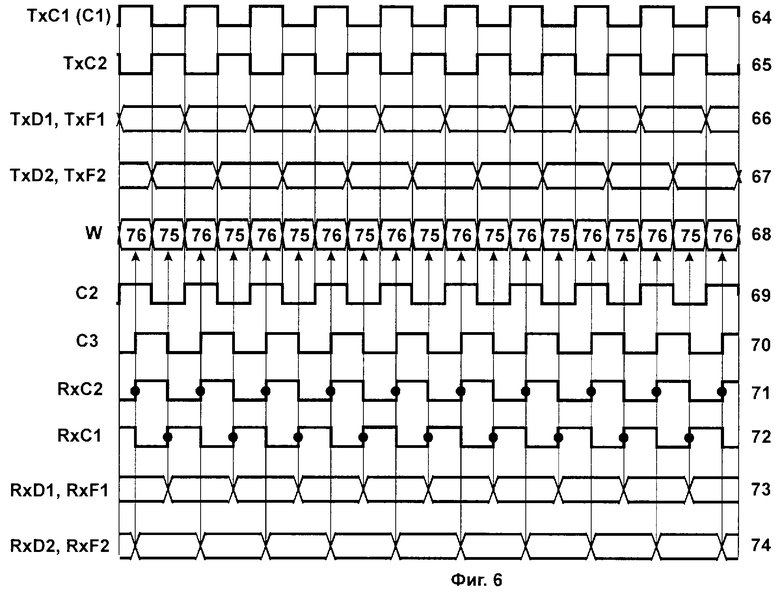

Блок 36 передачи данных (фиг.5) содержит генератор 53 синхросигналов, шифратор 54, группу выходных усилителей 55, выход генератора 53 синхросигналов соединен с входом шифратора 54 и является первым 39 выходом синхронизации первого канала устройства, группа входов 43 данных первого канала устройства соединена с входами шифратора 54, группа выходов шифратора 54 соединена с входами группы выходных усилителей 55, выходы которых соединены с витыми парами 38 проводов линии связи 35.

Блок 37 приема данных содержит группу входных усилителей 56, дешифратор 57, первый регистр 58, элемент 59 задержки и первый 60 инвертор, входы группы входных усилителей 56 соединены с витыми парами 38 проводов линии связи 35, а их выходы - с входами дешифратора 57, выходы которого соединены с входами данных первого регистра 58 и с входом элемента 59 задержки, выход первого инвертора 60 соединен с входом синхронизации первого регистра 58 и является вторым выходом 40 синхронизации первого канала устройства, группа 44 выходов первого регистра 58 является группой выходов данных первого канала устройства.

Блок 36 передачи данных дополнительно содержит второй инвертор 61, вход которого соединен с выходом генератора 53 синхросигналов, выход второго инвертора 61 является первым выходом 41 синхронизации второго канала устройства, входы 47 и 48 кадровой синхронизации первого и второго каналов устройства и группа 45 входов данных второго канала устройства соединены с входами шифратора 54.

Блок 37 приема данных дополнительно содержит второй регистр 62 и блок 63 фазовой автоподстройки частоты, вход которого соединен с выходом элемента задержки 59, а выход - с входом первого инвертора 60 и с входом синхронизации второго регистра 62 и является вторым 42 выходом синхронизации второго канала устройства, выходы 49 и 50 кадровой синхронизации первого и второго каналов устройства соединены с выходами первого 58 и второго 62 регистров, группа выходов второго регистра является группой 46 выходов данных второго канала устройства, входы данных второго регистра 62 соединены с выходами дешифратора 57.

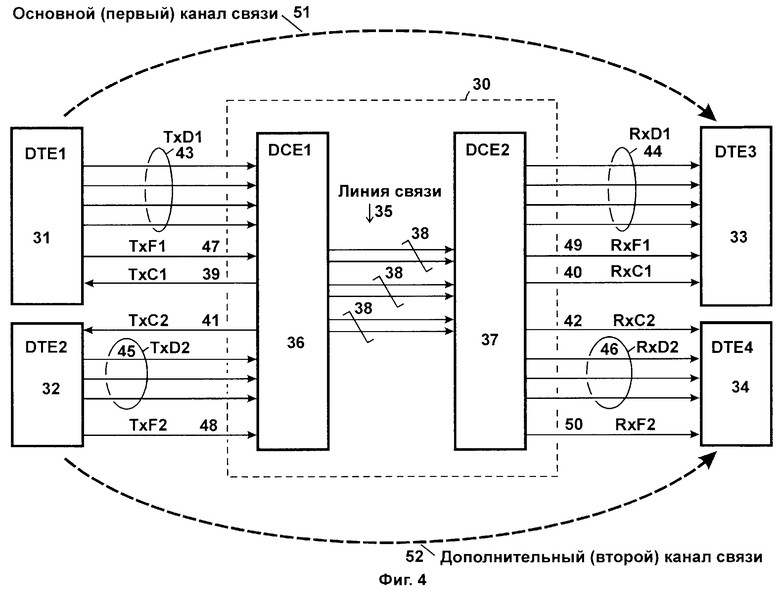

Временные диаграммы 64 и 65 (фиг.6) отображают сигналы на выходах 39 и 41 блока 36; диаграммы 66 и 67 - сигналы на входах 43, 47 и 45, 48 блока 36; диаграмма 68 - сигналы в линии связи 35; диаграммы 69-72 - сигналы на входе и выходе элемента задержки 59, на входе и выходе инвертора 60, диаграммы 73 и 74 - сигналы на выходах 44, 49 регистра 58 и на выходах 46, 50 регистра 62. Указатели 75 и 76 отображают информацию W, выдаваемую в линию 35 из блока 36.

В схеме, приведенной на фиг.1, четырехразрядный параллельный код данных DIN (X Y Z V) и сопровождающий его синхросигнал CIN передаются по витым парам 6 проводов линии связи 1 к удаленному абоненту. Напряжение между проводами витой пары 6 может быть отрицательным или положительным в зависимости от значения передаваемого бита (лог.0 или 1). Выходной код данных DOUT (X Y Z V) и принятый синхросигнал COUT совпадают с входными с точностью до задержек передачи.

Пересылка четырехразрядного параллельного кода и синхросигнала может быть выполнена по меньшему числу витых пар проводов с использованием устройства [2] (см. фиг.2).

В этом устройстве применено трехуровневое кодирование сигналов в линии связи 7. Напряжение U1 (U2, U3) между проводами витой пары 15 может быть отрицательным, нулевым или положительным (сокращенно: -, 0, +). Это напряжение формируется усилителем 12 в зависимости от сочетания битов E1 F1 (G1 H1, K1 L1) на его входах следующим образом. При E1=F1=0 (G1=H1=0, K1=L1=0) напряжение U1 (U2, U3) нулевое, при Е1=0, F1=1 (G1=0, H1=1; K1=0, L1=1) - отрицательное, при E1=1, F1=0 (G=1, H1=0; K1=1, L1=0) - положительное. Код E1 F1 G1 H1 K1 L1 формируется шифратором 11 из входного кода X1 Y1 Z1 V1 С1 (данные, синхросигнал), например, как показано в левой части табл.1.

Входные усилители 16 и дешифратор 17 осуществляют обратное преобразование сигналов, представленных напряжениями U1, U2 и U3 в витых парах проводов линии связи. В этом можно убедиться сопоставлением левой и правой частей табл. 1 - они симметричны. В центральной части таблицы показаны 17 (из 33=27 возможных) комбинаций S сигналов в линии связи. Первая (S=1) комбинация (0 0 0) выбрана для отображения единичного состояния синхросигнала С1. Символы "х" в левой части таблицы означают, что при С1=1 входные сигналы TxD не воспринимаются шифратором. Эти же символы в правой части таблицы показывают, что при выдаче восстановленного синхросигнала С2 выходные данные Х2 Y2 Z2 V2 не определены и не могут использоваться для выдачи абоненту. Остальные 16 комбинаций сигналов в линии связи распределены для отображения 16 состояний четырехразрядного кода X1 Y1 Z1 V1 при условии, что С1=0. Шифратор и дешифратор могут быть выполнены на основе ПЗУ, программируемой логики или построены из обычных логических элементов.

Из временных диаграмм, показанных на фиг.3, следует, что сигналы W, передаваемые по линии связи 7, поочередно отображают синхросигнал С1 и данные (группу битов X1, Y1, Z1, V1). Как отмечалось, группа выходных сигналов дешифратора 17 не определена при наличии синхросигнала. Этот факт отмечен затененными областями на временной диаграмме 27 группы Q сигналов Х2, Y2, Z2, V2. Для устранения неопределенности этих сигналов применен параллельный регистр 18. Данные принимаются в него по положительному фронту сигнала С3, который формируется из сигнала С2 после его задержки на четверть периода синхросигнала и последующего инвертирования. В результате сигналы RxD и RxC с некоторой задержкой повторяют сигналы TxD и ТхС.

Данный способ уменьшения числа витых пар проводов канала связи применим к схемам с различной разрядностью. При трехуровневом кодировании число состояний линии, содержащей N витых пар проводов, равно 3N. Одно из этих состояний следует выделить для кодирования единичного значения синхросигнала. С помощью оставшихся 3N-1 состояний можно отобразить М-разрядный двоичный код TxD, где М=[log2(3N-1)], прямые скобки здесь обозначают целую часть заключенного в них числа. Так, при N=2, 3, 4,..., 10 разрядность М передаваемого кода составляет 3, 4, 6, 7, 9, 11, 12, 14, 15.

Принцип действия предлагаемого устройства (см. фиг.4-6) близок рассмотренному, но по линии связи 35 передается большее число кодовых комбинаций, что повышает ее информационную нагрузку. Кроме того, синхросигнал передается по линии в "смеси" с данными (а не в явном виде), что увеличивает пропускную способность устройства. Применен дополнительный канал связи и введены средства передачи признаков начала информационных кадров.

Предлагаемое устройство 30 (фиг.4) подключено к четырем оконечным устройствам DTE1 (31) - DTE4 (34), например к четырем компьютерам. В процессе работы системы данные TxD1 и признак TxF1 начала кадра передаются из устройства 31 в устройство 33 по основному (первому) каналу. Одновременно с этим по дополнительному (второму) каналу данные TxD2 и признак TxF2 начала кадра передаются из устройства 32 в устройство 34. (Для передачи информации в обратном направлении необходимо второе устройство 30, включенное встречно. )

Сигнал TxC1 обеспечивает синхронную передачу данных TxD1 и признака TxF1 начала кадра из устройства 31 в блок 36. Сигнал ТхС2 обеспечивает синхронную передачу данных TxD2 и признака TxF2 начала кадра из устройства 32 в блок 36. Положительные фронты сигнала TxC1 задают границы битовых интервалов для каждого входного сигнала первого канала. Положительные фронты сигнала ТхС2 задают границы битовых интервалов для каждого входного сигнала второго канала. Аналогичные функции выполняет синхросигнал RxC1 (RxC2) сопровождения данных RxD1 (RxD2) и признаков RxF1 (RxF2) начала кадров.

Все процессы, протекающие при передаче данных предлагаемым устройством, синхронизируются от генератора 53 (см. фиг.5). По положительному фронту сигнала TxC1 на входы 43 и 47 устройства поступает очередной четырехразрядный двоичный код X1 Y1 Z1 V1 данных TxD1 (X1 - старший разряд) и в начале каждого информационного кадра - признак TxF1=1 (R1=1). Аналогично по положительному фронту сигнала ТхС2 на входы 45 и 48 устройства поступает очередной трехразрядный двоичный код A1 B1 M1 данных TxD2 (A1 - старший разряд) и в начале каждого информационного кадра - признак TxF2=1(Q=1).

Сигналы с входов 43, 47, 45, 48 и с выхода генератора 53 поступают на входы шифратора 54. Шифратор 54, усилители 55, 56 и дешифратор 57 выполняют преобразование кодов в соответствии с табл.2.

В предлагаемом устройстве, так же как и в прототипе, применено трехуровневое кодирование сигналов в линии связи 35. Напряжение U1 (U2, U3) между проводами витой пары 38 может быть отрицательным, нулевым или положительным (сокращенно: -, 0, +). Это напряжение формируется усилителем 55 в зависимости от сочетания битов E1 F1 (G1 H1, K1 L1) на его входах следующим образом.

При Е1=F1=0 (G1=H1=0, K1=L1=0) напряжение U1 (U2, U3) нулевое, при Е1=0, F1= 1 (G1= 0, H1=1; K1=0, L1=1) - отрицательное, при E1=1, F1=0 (G=1, H1=0; K1=1, L1=0) - положительное. Код E1 F1 G1 H1 K1 L1 формируется шифратором 54 из входного кода, как показано в левой части табл.2.

Входные усилители 56 и дешифратор 57 осуществляют обратное преобразование сигналов, представленных напряжениями U1, U2 и U3 в витых парах проводов линии связи. В графе S табл.2 перечислены 26 из 33=27 возможных состояний трехуровневых сигналов U1-U3 в линии связи (одно из состояний в данном примере не используется, хотя оно может отображать какой-либо дополнительный признак). Первое состояние (S=1) соответствует напряжениям (U1 U2 U3)=(-, 0, -); второе - напряжениям (U1 U2 U3)=(-, 0, +) и т. д.

Символы "х" в левой части таблицы означают, что соответствующие входные сигналы игнорируются шифратором. В частности, как показано в строках 1-16, при R1= С1= 0 шифратор оперирует кодом TxD1 (X1 Y1 Z1 V1) и не воспринимает сигналы с входов Q, A1, B1, M1. Аналогично при Q1=0 и С1=1 (см. строки 17 - 24) шифратор воспринимает код TxD2 (A1 B1 M1) и игнорирует остальные входные сигналы. Сочетание сигналов R1=1 и С1=0 (строка 25) однозначно трактуется как признак начала передаваемого по первому каналу информационного кадра независимо от состояний сигналов на остальных входах. Аналогично строка 26 определяется условием Q= С=1 и описывает передачу признака начала кадра по второму каналу.

Правая часть таблицы, в основном, представляет собой зеркальную копию левой части. Исключение составляют две последние строки (24 и 25), в которых некоторым символам "х" в левой части поставлены в соответствие символы "0" в правой части. Это гарантирует формирование нулевых кодов RxD1 и RxD2 в тех ситуациях, когда передаются признаки RxF1 и RxF2 начала кадров.

Из табл.2 и временных диаграмм 64 - 68 (см. фиг.6) следует, что по мере изменения логического значения тактового сигнала TxC1 (C1) в линию 35 попеременно поступает информация W из первого (указатель 75) и второго (указатель 76) каналов. При этом сигнал С2 (диаграмма 69) на выходе дешифратора 57 повторяет сигнал C1 с точностью до задержки передачи. Сигнал С3 (диаграмма 70) на выходе элемента задержки 59 сдвинут на четверть периода относительно сигнала С2 для совмещения его положительных и отрицательных фронтов с установившимися значениями информационных сигналов на входах регистров 62 и 58.

Сигнал С3 поступает на вход синхронизации блока 63 фазовой автоподстройки частоты. Блок 63 может быть выполнен по одной из известных схем (см., например, пат. США 6215835 В1). Он предназначен для формирования высокостабильного синхросигнала RxC2 на основе непрерывного слежения за входным сигналом С3. Положительный фронт сигнала RxC2 (диаграмма 71) привязан к положительному фронту сигнала С3. Благодаря достаточной инерционности блока 63 сигнал RxC2 практически нечувствителен к "дрожанию фазы" сигнала С3 и иным его кратковременным искажениям, вызванным помехами в линии связи. (Такое использование стандартного блока фазовой автоподстройки частоты в телекоммуникационных системах является общепринятым и далее не детализируется.)

По положительным фронтам сигналов RxC2 и RxC1 (диаграммы 71 и 72) информация с выходов дешифратора 57 фиксируется в регистрах 62 и 58 и поступает к оконечным устройствам 33 и 34.

Передаваемые по первому и второму каналам данные, как обычно, группируются в кадры. Длина кадра может быть постоянной или переменной. Для обозначения начала кадра, передаваемого по первому каналу, используются сигналы TxF1 (на передающей стороне) и RxF1 (на приемной стороне). Как следует из табл.2, при TxF1=1 данные TxD1 не воспринимаются на передающей стороне и доопределяются нулями на приемной стороне. То же справедливо и по отношению ко второму каналу.

Благодаря формированию дополнительного канала связи, в каждом периоде синхросигнала (ТхС1) дополнительно передаются три бита данных (код TxD2). Кроме того, исключена необходимость выполнения операции бит-стаффинга, т.е. введения служебных битов в передаваемый массив данных для создания уникальных (флаговых) кодовых комбинаций с целью обозначения признаков начала информационных кадров. Поэтому исключена необходимость передачи служебных битов по линии связи, а также последующего программного или аппаратного распознавания флаговых комбинаций и отмены бит-стаффинга, так как признаки начала кадров передаются предлагаемым устройством в явном виде. Это также повышает скорость передачи данных.

Источники информации

1. Патент США 5160929, фиг. 1.

2. Патент США 5160929, фиг. 2 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214045C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214046C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ - ДЕКОДИРОВАНИЯ ДАННЫХ | 2002 |

|

RU2214044C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2214061C2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2205445C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2271612C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2272360C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2004 |

|

RU2262205C1 |

| УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ДАННЫХ | 2004 |

|

RU2260251C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДАННЫХ | 2003 |

|

RU2242789C1 |

Изобретение относится к электронным схемам кодирования, декодирования и преобразования данных при их передаче между удаленными друг от друга абонентами. Техническим результатом является повышение скорости передачи данных и расширение функциональных возможностей устройства. Технический результат достигается тем, что устройство для кодирования - декодирования данных использует дополнительный (параллельно с основным) канал связи с возможностью передачи признаков начала информационных кадров и содержит подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и первый инвертор, причем блок передачи данных дополнительно содержит второй инвертор, второй регистр и блок фазовой автоподстройки частоты. 6 ил., 2 табл.

Устройство для кодирования - декодирования данных, содержащее подключенные к противоположным сторонам линии связи блок передачи данных и блок приема данных, блок передачи данных содержит генератор синхросигналов, шифратор, группу выходных усилителей, выход генератора синхросигналов соединен с входом шифратора и является первым выходом синхронизации первого канала устройства, группа входов данных первого канала первого устройства соединена с входами шифратора, группа выходов шифратора соединена с входами группы выходных усилителей, выходы которых соединены с витыми парами проводов линии связи, блок приема данных содержит группу входных усилителей, дешифратор, первый регистр, элемент задержки и первый инвертор, входы группы входных усилителей соединены с витыми парами проводов линии связи, а их выходы - с входами дешифратора, выходы которого соединены с входами данных первого регистра и с входом элемента задержки, выход первого инвертора соединен с входом синхронизации первого регистра и является вторым выходом синхронизации первого канала устройства, группа выходов первого регистра является группой выходов данных первого канала устройства, отличающееся тем, что блок передачи данных дополнительно содержит второй инвертор, вход которого соединен с выходом генератора синхросигналов, выход второго инвертора является первым выходом синхронизации второго канала устройства, входы кадровой синхронизации первого и второго каналов устройства и группа входов данных второго канала устройства соединены с входами шифратора, блок приема данных дополнительно содержит второй регистр и блок фазовой автоподстройки частоты, вход которого соединен с выходом элемента задержки, а выход - с входом первого инвертора и с входом синхронизации второго регистра и является вторым выходом синхронизации второго канала устройства, выходы кадровой синхронизации первого и второго каналов устройства соединены с выходами первого и второго регистров, группа выходов второго регистра является группой выходов данных второго канала устройства, входы данных второго регистра соединены с выходами дешифратора.

| Устройство для порогового выделения кода " @ " из " @ | 1981 |

|

SU955021A1 |

| US 5160929, 03.10.1992 | |||

| СПОСОБ И УСТРОЙСТВО КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ ДАННЫХ | 1995 |

|

RU2117388C1 |

| СПОСОБ КОДИРОВАНИЯ ЦИФРОВЫХ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2168270C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ЗВУКОВЫХ СИГНАЛОВ | 1996 |

|

RU2158478C2 |

| US 4910750, 20.03.1990 | |||

| УСТРОЙСТВО СИНХРОНИЗАЦИИ по РАБОЧЕМУ СИГНАЛУ | 0 |

|

SU195495A1 |

Авторы

Даты

2003-06-10—Публикация

2002-03-18—Подача