Изобретение относится к электронно-вычислительной технике и радиотехнике, а именно к средствам высокоскоростной цифровой обработки сигналов, и может быть использовано в радиоприемных устройствах, радиолокации.

Известно устройство цифровой обработки сигналов по патенту на полезную модель RU №202726, приоритет 28.10.2020, МПК: G06F 15/78, G06F 13/40, включающее связанные каналами обмена данными программируемую логическую интегральную схему (ПЛИС), аналого-цифровой преобразователь (АЦП), подключенный к ПЛИС посредством буферизированных каналов и к тактовым генераторам, буферизированные настраиваемые цифровые линии ввода/вывода стандарта LVTTL, подключенные к ПЛИС.

Недостатком данного устройства является отсутствие аналогового тракта обработки принимаемого сигнала, что ограничивает динамический диапазон. Кроме того, в схеме тактирования отсутствует блок умножения частоты, что делает невозможным обработку сигналов с доплеровским смещением. Также формат выходных данных не является дифференциальным.

Известен многофункциональный вычислительный комплекс для обработки радиолокационных сигналов по патенту на изобретение RU №2399088, приоритет 28.10.2008, МПК: G06F 15/16, содержащий устройство синхронизации, один или несколько усилителей промежуточной частоты, одно или несколько устройств аналого-цифрового преобразования.

Недостатком вычислительного комплекса является наличие только одного аналогового канала. В аналоговом тракте отсутствуют элементы фильтрации и ограничения сигнала, что уменьшает динамический диапазон. Кроме того, скорость передачи данных по выходной шине относительно небольшая.

Известен способ и устройство обработки сигналов линий связи по модели сигнала и перепрограммируемым электрическим схемам по патенту на изобретение RU №2317641, приоритет 17.05.2005, МПК: H03K 19/00, содержащее последовательно соединенные радиоприемное устройство и блок аналого-цифрового преобразования, к выходу которого подключены входы двух когерентных цифровых демодуляторов.

К недостаткам можно отнести наличие только одного аналогового канала. Данное устройство обработки сигналов линий связи рассчитано на более высокие входные рабочие частоты. Кроме того, в схеме тактирования отсутствует возможность синхронизации с внешней опорной частотой.

Наиболее близким к предлагаемому решению является модуль аналого-цифрового преобразователя по патенту на изобретение RU №2290662, приоритет 01.06.2005, МПК: G01S 13/02, который содержит два канала цифровой обработки сигнала, состоящих каждый из аналого-цифрового преобразователя.

Недостатком модуля аналого-цифрового преобразователя является наличие только двух каналов обработки сигнала. Кроме того, каналы обработки сигнала данного модуля не имеют управляемых усилителей, что ограничивает их динамический диапазон, а частота оцифровки ограничивает диапазон входных частот.

Технической проблемой, на решение которой направлено изобретение, является реализация многоканального устройства оцифровки сигналов, вносящего низкий уровень шумов и интермодуляционных искажений в обрабатываемые сигналы, а также обладающего широким динамическим диапазоном и высокой чувствительностью.

Решение указанной технической проблемы достигается тем, что процессор цифрового разделения квадратур содержит два канала обработки сигнала, два аналого-цифровых преобразователя, причем первый и второй каналы обработки сигнала являются аналоговыми, а первый и второй аналого-цифровые преобразователи входят в состав первого вычислителя, кроме того содержащего разветвитель тактового сигнала, три буфера TTL, блок управления, формирователь выходной шины, по меньшей мере один буфер LVDS, первый и второй блоки цифровой обработки сигналов, каждый состоящий из последовательно соединенных блока переноса частоты, первого цифрового фильтра нижних частот, первого дециматора, второго цифрового фильтра нижних частот, второго дециматора, третьего цифрового фильтра нижних частот, кроме этого процессор ЦРК дополнительно содержит по меньшей мере третий и четвертый аналоговые каналы обработки сигнала, по меньшей мере второй, идентичный первому, вычислитель и общий для обоих вычислителей синхронизатор, состоящий из последовательно соединенных первого усилителя, умножителя частоты, полосового фильтра, разветвителя тактового сигнала, к выходам которого подключены по меньшей мере второй и третий усилители, при этом каждый аналоговый канал обработки сигнала содержит последовательно соединенные коммутатор контрольного сигнала, в котором первый вход является входом основного сигнала, второй вход является входом контрольного сигнала, полосовой фильтр, два управляемых усилителя, усилитель-ограничитель, фильтр нижних частот, при этом третий вход каждого коммутатора контрольного сигнала и вторые входы каждого управляемого усилителя первого и второго аналогового канала обработки сигнала соединены с выходом второго буфера TTL первого вычислителя, а третий вход каждого коммутатора контрольного сигнала и вторые входы каждого управляемого усилителя третьего и четвертого аналогового канала обработки сигнала соединены с выходом второго буфера TTL второго вычислителя, выходы фильтров нижних частот первого и второго аналогового канала обработки сигнала соединены с первыми входами соответственно первого и второго аналого-цифрового преобразователя первого вычислителя, выходы фильтров нижних частот третьего и четвертого аналогового канала обработки сигнала соединены с первыми входами соответственно первого и второго аналого-цифрового преобразователя второго вычислителя, вход первого усилителя синхронизатора является входом опорного сигнала, выход второго и третьего усилителей синхронизатора соединен, с входом разветвителя тактового сигнала первого и второго вычислителей соответственно, вход первого буфера TTL первого вычислителя является входом управляющего цифрового сигнала, вход первого буфера TTL второго вычислителя соединен с выходом третьего буфера TTL первого вычислителя, вход третьего буфера TTL первого вычислителя соединен со вторым выходом блока управления первого вычислителя, при этом в каждом вычислителе выход первого буфера TTL соединен с входом блока управления, первый выход блока управления соединен с входом второго буфера TTL, третий выход блока управления соединен с третьим входом формирователя выходной шины, второй вход первого и второго аналого-цифровых преобразователей соединен соответственно с первым и вторым выходом разветвителя тактового сигнала, выход первого и второго аналого-цифровых преобразователей соединен с входом соответственно первого и второго блоков цифровой обработки сигналов, выход первого и второго блоков цифровой обработки сигналов соединен соответственно с первым и вторым входом формирователя выходной шины, выход формирователя выходной шины соединен с входом буфера LVDS, выход которого является выходом процессора ЦРК.

Технический результат, достигаемый в заявленном изобретении, заключается в преобразовании четырех аналоговых сигналов на промежуточной частоте в цифровые комплексные сигналы с низким уровнем шумов и интермодуляционных искажений, вносимых трактом обработки, обладающим высокой чувствительностью и широким динамическим диапазоном.

Сравнение заявленного технического решения с уровнем техники по научно-технической и патентной документации на дату приоритета в основной и смежных рубриках показывает, что совокупность существенных признаков заявленного решения ранее не была известна, следовательно, техническое решение соответствует условию патентоспособности "новизна".

Анализ известных технических решений в данной области техники показал, что предложенный процессор имеет признаки, которые отсутствуют в технических решениях, а использование их в заявленной совокупности дает возможность получить новый технический результат, следовательно, предложенное техническое решение имеет изобретательский уровень по сравнению с существующим уровнем техники.

Предложенное техническое решение промышленно применимо, т.к. может быть изготовлено промышленным способом, работоспособно, осуществимо и воспроизводимо, следовательно, соответствует условию патентоспособности "промышленная применимость".

Предлагаемый процессор цифрового разделения квадратур (ЦРК) поясняется чертежом: фиг. - функциональная схема процессора ЦРК.

Процессор ЦРК содержит четыре идентичных аналоговых канала 1 обработки сигнала, синхронизатор 2 и два идентичных вычислителя 3.

Каждый (первый, второй, третий и четвертый) аналоговый канал 1 обработки сигнала содержит последовательно соединенные коммутатор 4 контрольного сигнала, полосовой фильтр 5, два идентичных управляемых усилителя 6, усилитель-ограничитель 7, фильтр 8 нижних частот (ФНЧ).

Синхронизатор 2 содержит последовательно соединенные первый усилитель 9, умножитель 10 частоты, полосовой фильтр 11 поверхностных акустических волн (ПАВ), разветвитель 12 тактового сигнала, к двум выходам которого подключены идентичные второй и третий усилители 13.

Каждый (первый и второй) вычислитель 3 содержит два идентичных аналогово-цифровых преобразователя (АЦП) 14, разветвитель 15 тактового сигнала, три идентичных буфера TTL (transistor-transistor logic) 16, программируемую логическую интегральную схему (ПЛИС) 17, буфер LVDS (low-voltage differential signaling) 18.

Конфигурация ПЛИС 17 содержит два идентичных блока 19 цифровой обработки сигналов (ЦОС), блок 20 управления, формирователь 21 выходной шины.

Каждый блок 19 ЦОС состоит из последовательно соединенных: блока 22 переноса частоты (БПЧ), первого цифрового ФНЧ 23, первого дециматора 24, второго цифрового ФНЧ 25, второго дециматора 24, третьего цифрового ФНЧ 26.

Первый вход каждого коммутатора 4 контрольного сигнала является входом основного сигнала 27, 28, 29, 30 соответственно, который является аналоговым, второй вход каждого коммутатора 4 контрольного сигнала является входом контрольного сигнала 31, 32, 33, 34 соответственно, который также является аналоговым. Третий вход каждого коммутатора 4 контрольного сигнала и вторые входы каждого управляемого усилителя 6, которые являются входами управляющего сигнала, первого и второго аналогового канала 1 обработки сигнала соединены с выходом второго буфера TTL 16 первого вычислителя 3. Третий вход каждого коммутатора 4 контрольного сигнала и вторые входы каждого управляемого усилителя 6, которые являются входами управляющего сигнала, третьего и четвертого аналогового канала 1 обработки сигнала соединены с выходом второго буфера TTL 16 второго вычислителя 3.

Выходы ФНЧ 8 первого и второго аналогового канала 1 обработки сигнала соединены с первыми входами соответственно первого и второго АЦП 14 первого вычислителя 3. Выходы ФНЧ 8 третьего и четвертого аналогового канала 1 обработки сигнала соединены с первыми входами соответственно первого и второго АЦП 14 второго вычислителя 3.

Вход первого усилителя 9 синхронизатора 2 является входом опорного сигнала 35, а выходы второго и третьего усилителей 13 синхронизатора 2 соединены с входами разветвителей 15 тактового сигнала соответственно первого и второго вычислителя 3.

Вход первого буфера TTL 16 первого вычислителя 3 является входом 13-разрядного управляющего цифрового сигнала 36. Вход первого буфера TTL 16 второго вычислителя 3 соединен с выходом третьего буфера TTL 16 первого вычислителя 3. Вход третьего буфера TTL 16 первого вычислителя соединен со вторым выходом блока 20 управления первого вычислителя 3. Третий буфер TTL 16 второго вычислителя 3 в данном исполнении процессора ЦРК не задействован.

Для каждого вычислителя 3 выход первого буфера TTL 16 соединен с входом блока 20 управления, первый выход блока 20 управления соединен с входом второго буфера TTL 16, третий выход блока 20 управления соединен с третьим входом формирователя 21 выходной шины. В каждом вычислителе 3 второй вход первого и второго АЦП 14 соединен соответственно с первым и вторым выходом разветвителя 15 тактового сигнала. В каждом вычислителе 3 выход первого и второго АЦП 14 соединен с входом соответственно первого и второго блока 19 ЦОС. Выход первого и второго блока 19 ЦОС каждого вычислителя 3 соединен соответственно с первым и вторым входом формирователя 21 выходной шины. Выход формирователя 21 выходной шины каждого вычислителя 3 соединен с входом буфера LVDS 18. Выход 37, 38 буфера LVDS 18 соответственно первого и второго вычислителя 3 является выходом процессора ЦРК.

Процессор ЦРК работает следующим образом.

На первый, второй, третий и четвертый аналоговые каналы 1 обработки сигнала поступают сигналы: основные 27, 28, 29, 30 или контрольные 31, 32, 33, 34. На первый вычислитель поступает управляющий цифровой сигнал 36. При этом первый и второй аналоговый канал 1 обработки сигнала взаимодействует с первым вычислителем 3, третий и четвертый аналоговый канал 1 обработки сигнала аналогично взаимодействует со вторым вычислителем 3. Далее будет рассмотрена работа первого и второго аналогового канала 1 обработки сигнала с первым вычислителем 3.

На первый и второй аналоговый канал 1 обработки сигнала приходит соответственно основной сигнал 27 и 28 на промежуточной частоте 28 МГц с неизвестными параметрами, или соответственно контрольный сигнал 31 и 32 на частоте 28 МГц с известными параметрами, заданными заранее.

После чего основной сигнал 27, 28 или контрольный сигнал 31, 32 в первом и втором аналоговом канале 1 обработки сигнала соответственно проходит коммутатор 4 контрольного сигнала, полосовой фильтр 5, два управляемых усилителя 6, усилитель-ограничитель 7, ФНЧ 8, где преобразуется для корректной оцифровки. Управление коммутатором 4 контрольного сигнала и управляемыми усилителями 6 первого и второго аналогового канала 1 осуществляется посредством управляющего сигнала, поступающего через второй буфер TTL 16 с блока 20 управления первого вычислителя 3. Коммутатор контрольного сигнала 4 выполнен на интегральной микросхеме и осуществляет переключение между основным режимом работы процессора по оцифровке основного сигнала и режимом проверки корректности работы процессора посредством контрольного сигнала. Полосовой фильтр 5, реализованный на микросборке с полосой пропускания 7 МГц, предназначен для выделения полосы входных аналоговых сигналов: основного или контрольного. Управляемые усилители 6 имеют коэффициент усиления, изменяющийся в диапазоне от минус 11 дБ до 34 дБ, и предназначены для достижения требуемого уровня чувствительности 1 мкВ. Усилитель-ограничитель 7 имеет уровень ограничения выходного сигнала равный 1 В. ФНЧ 8 является антиалиасинговым и предназначен для фильтрации нежелательных спектральных составляющих, возникающих в процессе обработки аналогового сигнала. ФНЧ 8 выполнен, например, по схеме Т-образного пассивного ФНЧ четвертого порядка с аппроксимацией Кауэра и частотой среза 30 МГц.

Подготовленный сигнал с выхода первого и второго аналогового канала 1 обработки сигнала поступает на первый вычислитель 3 соответственно на первый и второй АЦП 14. Разрядность микросхемы АЦП составляет 14 бит.

Оцифрованный сигнал с выхода первого и второго АЦП 14 поступает по низковольтным дифференциальным линиям передачи (LVDS) на микросхему ПЛИС 17, где посредством первого и второго блока 19 ЦОС происходит выделение комплексной огибающей сигнала, которое заключается в переносе центральной частоты спектра сигнала на нулевую промежуточную частоту (ПЧ) с последующей фильтрацией и децимацией сигнала.

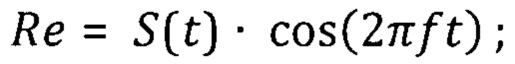

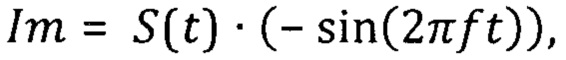

В процессе переноса центральной частоты спектра сигнала на нулевую ПЧ происходит разложение сигнала на реальную (Re) и мнимую (Im) составляющие по формулам:

где S(t) - входной сигнал,

ƒ - частота переноса сигнала.

Основным преимуществом использования комплексных сигналов является отсутствие зеркальных каналов при спектральных преобразованиях, что позволяет однозначно определять доплеровское смещение при последующей обработке сигнала. С целью подавления шумовых составляющих применены цифровые ФНЧ 23, 25, 26, соответственно первый, второй, третий. Многозвенная фильтрация обусловлена тем, что результирующий порядок трех фильтров будет меньше, чем в случае однозвенной фильтрации. Так как спектр сигнала перенесен на нулевую ПЧ, высокая частота дискретизации больше не требуется. В связи с этим посредством дециматоров 24 происходит понижение частоты дискретизации, что, в свою очередь, экономит ресурсы вычислителей 3 и снижает их энергопотребление. В результате две пары квадратурных сигналов с выхода первого и второго блока ЦОС 19 поступают в формирователь 21 выходной шины, где происходит их мультиплексирование в зависимости от режима работы процессора. После чего через буфер LVDS 18 выходные данные поступают на выходной разъем 37 процессора ЦРК. Буфер LVDS 18 используется для корректного сопряжения выходных сигналов микросхемы ПЛИС 17 с внешними устройствами.

Тактовая частота для корректного процесса оцифровки формируется в синхронизаторе 2 следующим образом. Опорный сигнал 35 с частотой 56 МГц поступает на вход первого усилителя 9, выполненного на операционном усилителе с коэффициентом усиления равным 5, затем в умножителе 10 частоты происходит формирование сигнала умножением частоты на 2. Сформированный сигнал проходит через полосовой фильтр 11 ПАВ с полосой пропускания 2 МГц, и разветвитель 12 тактового сигнала, выполненный в виде резистивного делителя. Полосовой фильтр 11 ПАВ предназначен для устранения нежелательных спектральных составляющих, содержащихся в сформированном тактовом сигнале. Разветвитель 12 тактового сигнала позволяет тактировать первый и второй вычислители 3 одним синхросигналом, что обеспечивает когерентность обработки входных сигналов. С разветвителя 12 тактового сигнала сигнал поступает на второй и третий усилители 13, выполненные также на операционных усилителях с коэффициентом усиления равным 3. Первый усилитель 9, второй и третий усилители 13 позволяют добиться уровня тактового сигнала 200 мВ для корректной работы первого и второго АЦП 14 первого и второго вычислителя 3. В результате тактовый сигнал с частотой 112 МГц со второго и третьего усилителя 13 поступает на разветвитель 15 тактового сигнала для осуществления синхронного тактирования первого и второго АЦП 14 соответственно первого и второго вычислителей 3.

Команды переключения режимов работы процессора ЦРК поступают с внешнего управляющего устройства (не показано) посредством управляющего цифрового сигнала 36 через первый буфер 16 TTL на блок 20 управления первого вычислителя 3. Передача команд переключения режимов работы процессора ЦРК на второй вычислитель 3 поступает через первый буфер 16 TTL на блок 20 управления второго вычислителя 3 с третьего буфера 16 TTL первого вычислителя 3.

Конструкция и работа процессора ЦРК не ограничивается выше приведенным описанием и может содержать 2n аналоговых каналов 1 обработки сигнала, n≥2, при этом каждая пара аналоговых каналов 1 обработки сигнала взаимодействует с соответствующим n-ым вычислителем 3, который соединен с (n+1) усилителем 13 синхронизатора 9. Третий буфер 16 TTL n-го вычислителя 3 необходим для передачи команд переключения режимов работы процессора ЦРК на первый буфер 16 TTL (n+1) вычислителя 3. Что не выходит за пределы формулы изобретения.

Такое исполнение процессора цифрового разделения квадратур позволяет осуществить преобразование четырех сигналов на промежуточной частоте в цифровые комплексные сигналы с низким уровнем шумов и интермодуляционных искажений, вносимых трактом обработки, обладающим высокой чувствительностью и широким динамическим диапазоном.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой приемник тональных сигналов | 1989 |

|

SU1635289A1 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С КАНАЛАМИ ВЫСОКОГО РАЗРЕШЕНИЯ | 2007 |

|

RU2344436C1 |

| МНОГОФУНКЦИОНАЛЬНЫЙ ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2008 |

|

RU2399088C2 |

| Устройство для цифровой фильтрации на основе дискретного преобразования Фурье | 1990 |

|

SU1795475A1 |

| ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 2013 |

|

RU2541856C2 |

| СТАНЦИЯ ТЕХНИЧЕСКОГО КОНТРОЛЯ СИГНАЛОВ СПУТНИКОВЫХ ЛИНИЙ СВЯЗИ | 2002 |

|

RU2224373C2 |

| РАДИОЛОКАЦИОННЫЙ ПРИЕМНИК С УСТРОЙСТВОМ УПРАВЛЕНИЯ | 2013 |

|

RU2535931C1 |

| Автодинное устройство | 1991 |

|

SU1811614A3 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ТЕХНИЧЕСКИХ ПАРАМЕТРОВ АВАРИЙНЫХ РАДИОМАЯКОВ/РАДИОБУЕВ | 2011 |

|

RU2453860C1 |

| СПОСОБ ФОРМИРОВАНИЯ КВАДРАТУРНЫХ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 1999 |

|

RU2168281C2 |

Изобретение относится к электронно-вычислительной технике и радиотехнике. Технический результат заключается в преобразовании четырех аналоговых сигналов на промежуточной частоте в цифровые комплексные сигналы с низким уровнем шумов и интермодуляционных искажений, вносимых трактом обработки, обладающим высокой чувствительностью и широким динамическим диапазоном, и достигается за счет того, что процессор цифрового разделения квадратур содержит четыре аналоговых канала обработки сигнала, синхронизатор и два идентичных вычислителя. Аналоговые каналы обработки содержат коммутатор контрольного сигнала, полосовой фильтр, два управляемых усилителя, усилитель-ограничитель, фильтр нижних частот (ФНЧ). Синхронизатор содержит первый усилитель, умножитель частоты, полосовой фильтр, разветвитель тактового сигнала, второй и третий усилители. Вычислители содержат два аналогово-цифровых преобразователя (АЦП), разветвитель тактовой частоты, три буфера TTL, программируемую логическую интегральную схему (ПЛИС), буфер LVDS. ПЛИС содержит два блока цифровой обработки сигналов (ЦОС), блок управления, формирователь выходной шины данных. ЦОС состоит из блока переноса частоты (БПЧ), первого цифрового ФНЧ, первого дециматора, второго цифрового ФНЧ, второго дециматора, третьего цифрового ФНЧ. 1 ил.

Процессор цифрового разделения квадратур (ЦРК), содержащий два канала обработки сигнала, два аналого-цифровых преобразователя, отличающийся тем, что первый и второй каналы обработки сигнала являются аналоговыми, а первый и второй аналого-цифровые преобразователи входят в состав первого вычислителя, кроме того содержащего разветвитель тактового сигнала, три буфера TTL, блок управления, формирователь выходной шины, по меньшей мере один буфер LVDS, первый и второй блоки цифровой обработки сигналов, каждый состоящий из последовательно соединенных блока переноса частоты, первого цифрового фильтра нижних частот, первого дециматора, второго цифрового фильтра нижних частот, второго дециматора, третьего цифрового фильтра нижних частот, кроме этого процессор ЦРК дополнительно содержит по меньшей мере третий и четвертый аналоговые каналы обработки сигнала, по меньшей мере второй, идентичный первому, вычислитель и общий для обоих вычислителей синхронизатор, состоящий из последовательно соединенных первого усилителя, умножителя частоты, полосового фильтра, разветвителя тактового сигнала, к выходам которого подключены по меньшей мере второй и третий усилители, при этом каждый аналоговый канал обработки сигнала содержит последовательно соединенные коммутатор контрольного сигнала, в котором первый вход является входом основного сигнала, второй вход является входом контрольного сигнала, полосовой фильтр, два управляемых усилителя, усилитель-ограничитель, фильтр нижних частот, при этом третий вход каждого коммутатора контрольного сигнала и вторые входы каждого управляемого усилителя первого и второго аналогового канала обработки сигнала соединены с выходом второго буфера TTL первого вычислителя, а третий вход каждого коммутатора контрольного сигнала и вторые входы каждого управляемого усилителя третьего и четвертого аналогового канала обработки сигнала соединены с выходом второго буфера TTL второго вычислителя, выходы фильтров нижних частот первого и второго аналогового канала обработки сигнала соединены с первыми входами соответственно первого и второго аналого-цифрового преобразователя первого вычислителя, выходы фильтров нижних частот третьего и четвертого аналогового канала обработки сигнала соединены с первыми входами соответственно первого и второго аналого-цифрового преобразователя второго вычислителя, вход первого усилителя синхронизатора является входом опорного сигнала, выход второго и третьего усилителей синхронизатора соединен, с входом разветвителя тактового сигнала первого и второго вычислителей соответственно, вход первого буфера TTL первого вычислителя является входом управляющего цифрового сигнала, вход первого буфера TTL второго вычислителя соединен с выходом третьего буфера TTL первого вычислителя, вход третьего буфера TTL первого вычислителя соединен со вторым выходом блока управления первого вычислителя, при этом в каждом вычислителе выход первого буфера TTL соединен с входом блока управления, первый выход блока управления соединен с входом второго буфера TTL, третий выход блока управления соединен с третьим входом формирователя выходной шины, второй вход первого и второго аналого-цифровых преобразователей соединен соответственно с первым и вторым выходом разветвителя тактового сигнала, выход первого и второго аналого-цифровых преобразователей соединен с входом соответственно первого и второго блоков цифровой обработки сигналов, выход первого и второго блоков цифровой обработки сигналов соединен соответственно с первым и вторым входом формирователя выходной шины, выход формирователя выходной шины соединен с входом буфера LVDS, выход которого является выходом процессора ЦРК.

| МОДУЛЬ АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛЯ | 2005 |

|

RU2290662C1 |

| СПОСОБ И УСТРОЙСТВО ОБРАБОТКИ СИГНАЛОВ ЛИНИЙ СВЯЗИ ПО МОДЕЛИ СИГНАЛА И ПЕРЕПРОГРАММИРУЕМЫМ ЭЛЕКТРИЧЕСКИМ СХЕМАМ | 2005 |

|

RU2317641C2 |

| US 20190140872 A1, 09.05.2019 | |||

| US 5784414 A, 21.07.1998 | |||

| JP 2008098785 A, 24.04.2008. | |||

Авторы

Даты

2022-11-23—Публикация

2022-03-09—Подача