Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно-включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage») [1-20]. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Однако в практических схемах известных ДУ коэффициент ослабления входного синфазного сигнала (Кос.сф) получается небольшим (50-60 дБ). Это связано с тем, что выходное сопротивление простейших источников опорного тока на основе токовых зеркал, обеспечивающих наиболее широкий диапазон изменения входных синфазных напряжений ДК, оказывается небольшим (30-100 кОм).

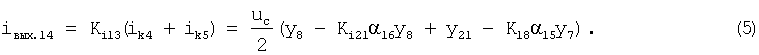

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США № 5.153.529 H 03 f 3/45, содержащий первый 1 n-p-n и второй 2 p-n-p входные транзисторы, базы которых соединены с первым 3 входом дифференциального усилителя, третий 4 n-p-n и четвертый 5 p-n-p входные транзисторы, базы которых соединены со вторым входом 6 дифференциального усилителя, первый 7 и второй 8 источники опорного тока, согласованные соответственно с шиной положительного 9 и отрицательного 10 источников питания, причем эмиттеры первого 1 и третьего 4 n-p-n входных транзисторов объединены, второго 2 и четвертого 5 p-n-p входных транзисторов - связаны друг с другом, а коллекторы третьего 4 p-n-p и четвертого 5 n-p-n входных транзисторов подключены к первым синфазным входам 11 и 12 сумматора тока 13, выход которого 14 является выходом дифференциального усилителя. Кроме этого коллекторы транзисторов 1 и 2 связаны со вторыми синфазными входами сумматора токов 13, которые обеспечивают сдвиг фазы сигнала относительно первых синфазных входов 11 и 12 на 180°.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ.

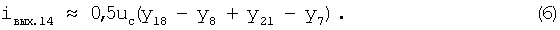

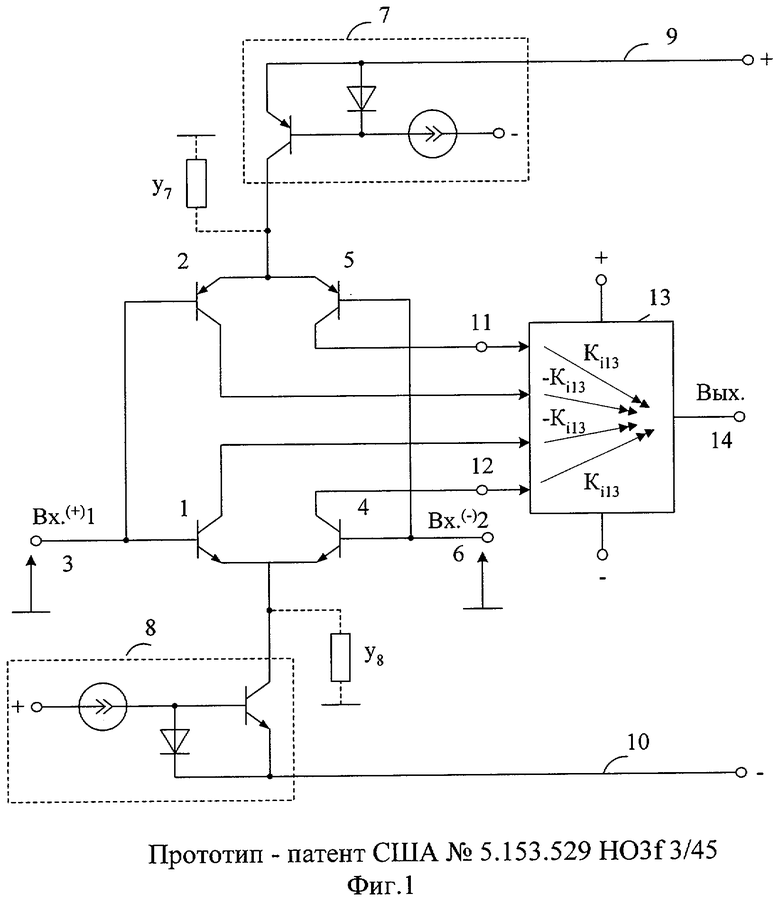

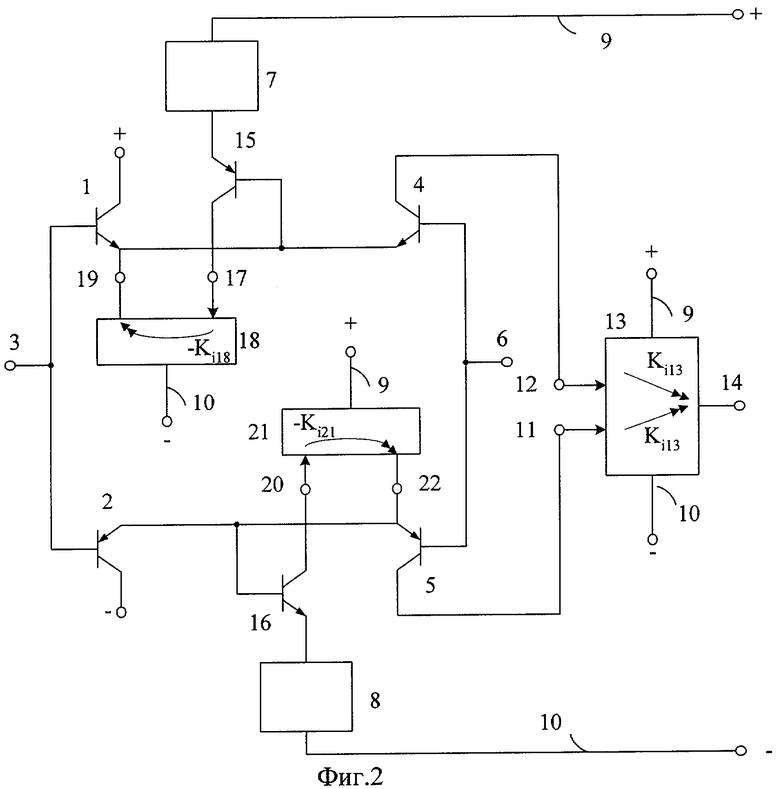

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 n-p-n и второй 2 p-n-p входные транзисторы, базы которых соединены с первым 3 входом дифференциального усилителя, третий 4 n-p-n и четвертый 5 p-n-p входные транзисторы, базы которых соединены со вторым входом 6 дифференциального усилителя, первый 7 и второй 8 источники опорного тока, согласованные соответственно с шиной положительного 9 и отрицательного 10 источников питания, причем эмиттеры первого 1 и третьего 4 n-p-n входных транзисторов объединены, второго 2 и четвертого 5 p-n-p входных транзисторов связаны друг с другом, а коллекторы третьего 4 p-n-p и четвертого 5 n-p-n входных транзисторов подключены к входам 11 и 12 сумматора тока 13, выход которого 14 является выходом дифференциального усилителя, вводятся новые элементы и связи между ними (фиг.2) - в схему введены первый p-n-p 15 и второй n-p-n 16 дополнительные транзисторы, базы которых подключены соответственно к объединенным эмиттерам первого 1 и третьего 4 входных n-p-n транзисторов и объединенным эмиттерам второго 2 и четвертого 5 p-n-p входных транзисторов, эмиттеры соединены с выходами соответствующих первого 7 и второго 8 источников опорного тока, согласованных с шиной положительного 9 и отрицательного 10 источников питания, причем коллектор первого дополнительного p-n-p транзистора 15 соединен с входом 17 первого вспомогательного токового зеркала 18, выход 19 которого связан с эмиттерами первого 1 и третьего 4 входных n-p-n транзисторов, а коллектор второго дополнительного n-p-n транзистора 16 соединен с входом 20 второго вспомогательного токового зеркала 21, выход 22 которого связан с эмиттерами второго 2 и четвертого 5 входных p-n-p транзисторов.

Схема заявляемого устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

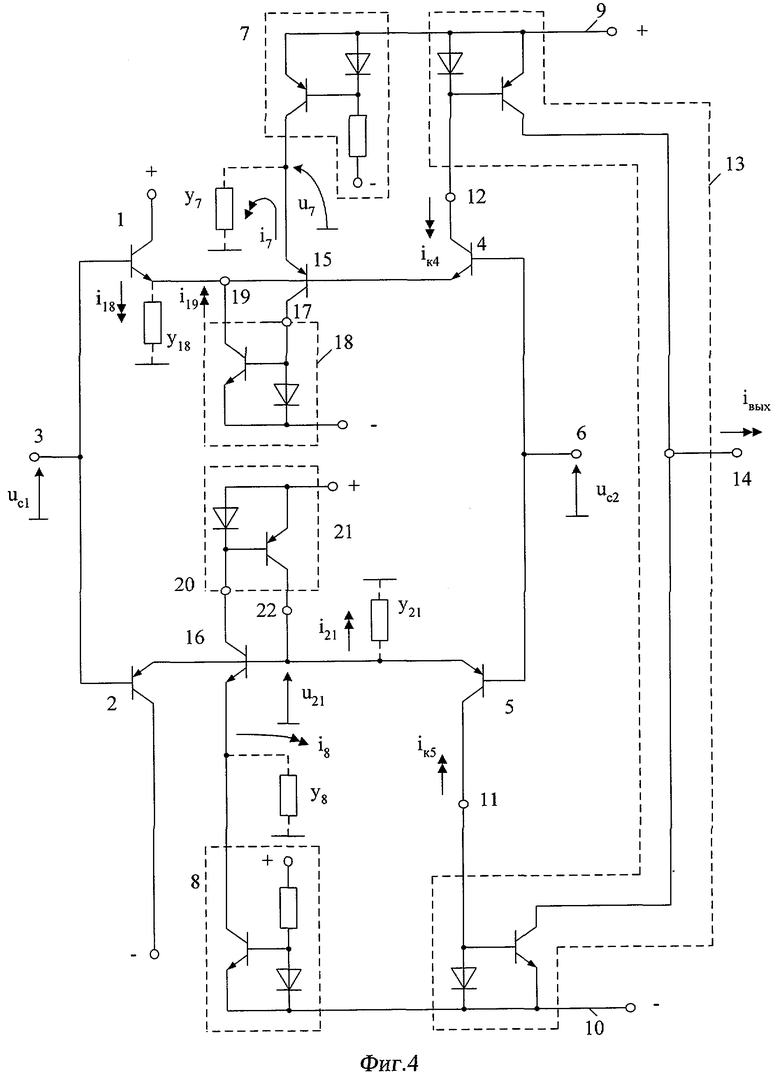

На фиг.3 показаны направления токов и напряжений схемы фиг.2 при подаче на входы 3 и 6 входного синфазного сигнала uc=uc1=uc2. На фиг.4 приведена схема ДУ фиг.2 с конкретным выполнением функциональных узлов 7, 8, 18, 21, 13.

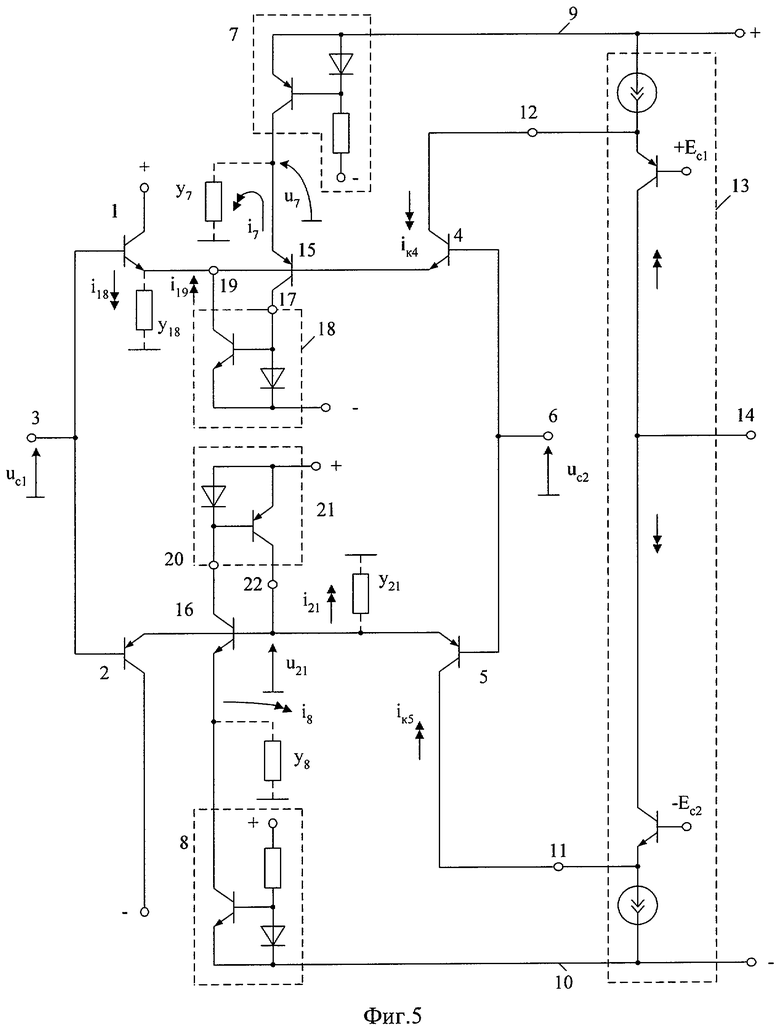

На фиг.5 сумматор тока 13 выполнен на основе так называемого «перегнутого» каскода.

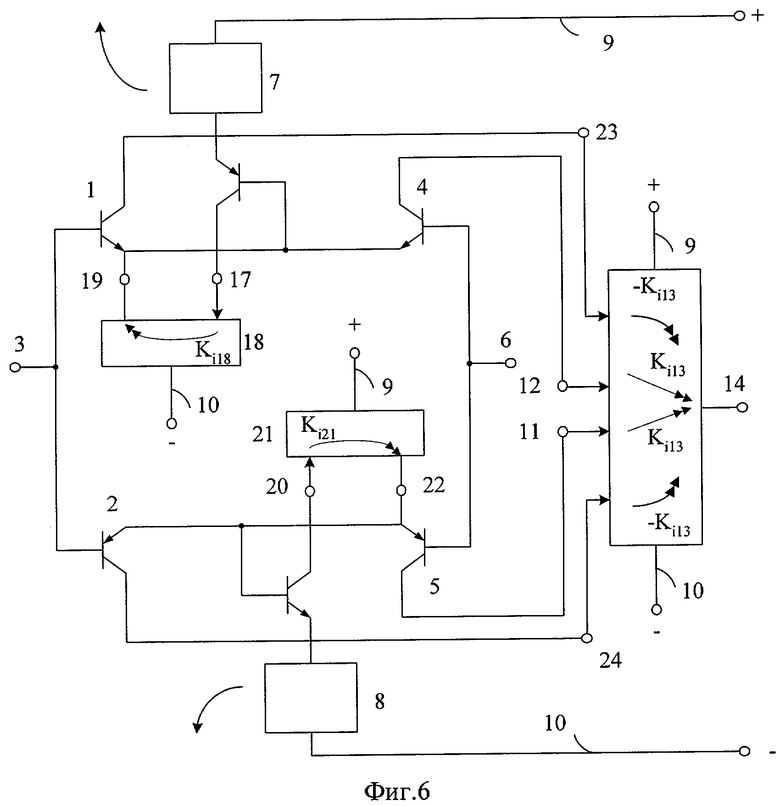

Схема заявляемого ДУ в соответствии с п.2 формулы изобретения приведена на фиг.6.

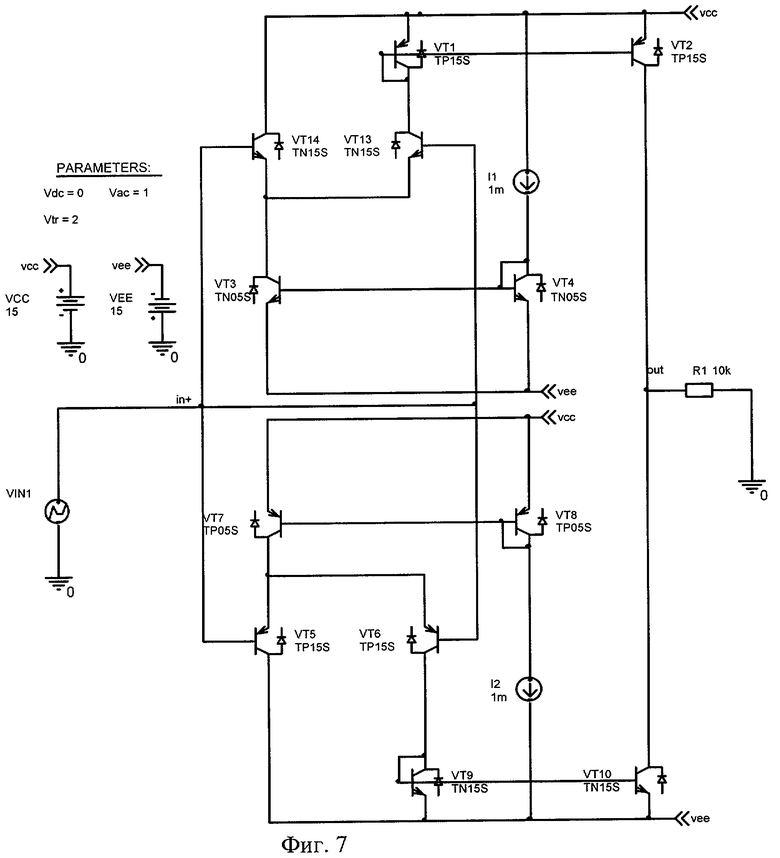

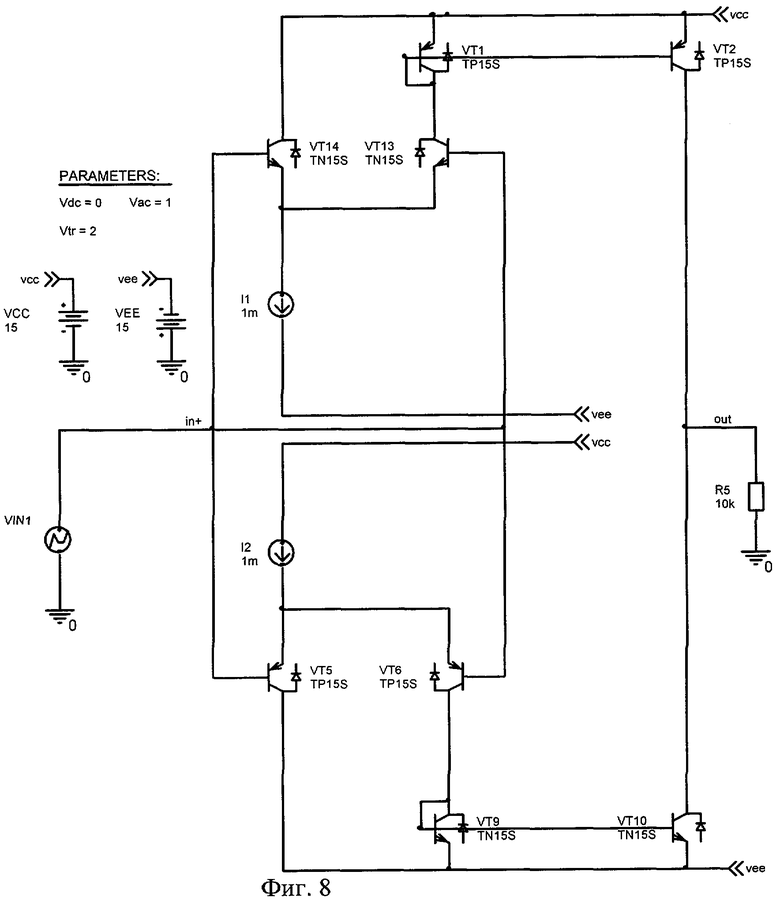

На фиг.7-8 показана схема ДУ-прототипа фиг.1 в среде компьютерного моделирования PSpice. Причем в схеме фиг.7 используются реальные, а в схеме фиг.8 - идеальные источники опорного тока 7 (I1) и 8 (I2).

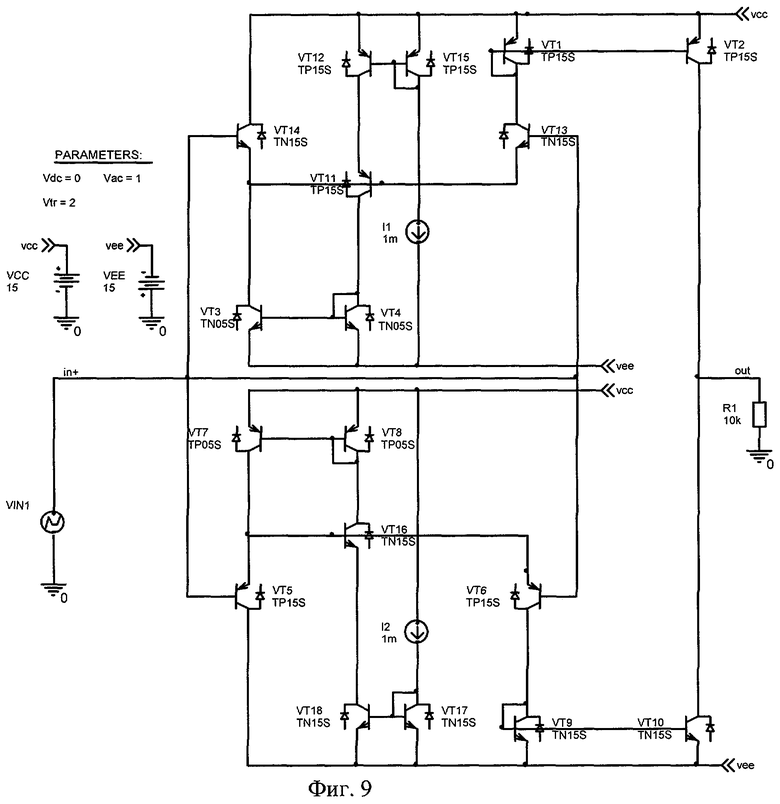

На фиг.9 приведена схема заявляемого устройства (фиг.2) в среде PSpice.

На фиг.1-10 приняты следующие обозначения:

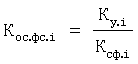

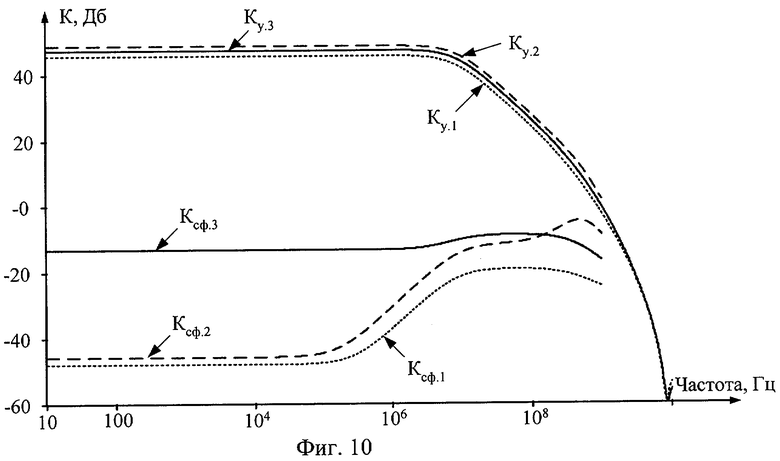

Ку.1 - коэффициент передачи по напряжению дифференциального сигнала ДУ фиг.8.

Ку.2 - коэффициент передачи по напряжению дифференциального сигнала ДУ фиг.9.

Ку.3 - коэффициент передачи по напряжению дифференциального сигнала ДУ фиг.7.

Ксф.1 - коэффициент передачи по напряжению синфазного сигнала ДУ фиг.8.

Ксф.2 - коэффициент передачи по напряжению синфазного сигнала ДУ фиг.9.

Ксф.3 - коэффициент передачи по напряжению синфазного сигнала ДУ фиг.7.

- коэффициент ослабления входного синфазного сигнала.

- коэффициент ослабления входного синфазного сигнала.

Графики фиг.10 характеризуют частотную зависимость дифференциальных коэффициентов усиления по напряжению ДУ фиг.7 (прототип) (Ку3), ДУ фиг.8 (Kу1) и ДУ фиг.9 заявляемого устройства (Ку2), а также их коэффициентов передачи синфазного сигнала Ксф.1 (фиг.8), Ксф.2 (фиг.9), Ксф.3 (фиг.7).

Дифференциальный усилитель фиг.2 содержит первый 1 n-p-n и второй 2 p-n-p входные транзисторы, базы которых соединены с первым 3 входом дифференциального усилителя, третий 4 n-p-n и четвертый 5 p-n-p входные транзисторы, базы которых соединены со вторым входом 6 дифференциального усилителя, первый 7 и второй 8 источники опорного тока, согласованные соответственно с шиной положительного 9 и отрицательного 10 источников питания, причем эмиттеры первого 1 и третьего 4 n-p-n входных транзисторов объединены, второго 2 и четвертого 5 p-n-p входных транзисторов связаны друг с другом, а коллекторы третьего 4 p-n-p и четвертого 5 n-p-n входных транзисторов подключены к первым синфазным входам 11 и 12 сумматора тока 13, выход которого 14 является выходом дифференциального усилителя. В схему введены первый p-n-p 15 и второй n-p-n 16 дополнительные транзисторы, базы которых подключены соответственно к объединенным эмиттерам первого 1 и третьего 4 входных n-p-n транзисторов и объединенным эмиттерам второго 2 и четвертого 5 p-n-p входных транзисторов, эмиттеры соединены с выходами соответствующих первого 7 и второго 8 источников опорного тока, согласованных с шиной положительного 9 и отрицательного 10 источников питания, причем коллектор первого дополнительного p-n-p транзистора 15 соединен со входом 17 первого вспомогательного токового зеркала 18, выход 19 которого связан с эмиттерами первого 1 и третьего 4 входных n-p-n транзисторов, а коллектор второго дополнительного n-p-n транзистора 16 соединен со входом 20 второго вспомогательного токового зеркала 21, выход 22 которого связан с эмиттерами второго 2 и четвертого 5 входных p-n-p транзисторов.

В дифференциальном усилителе фиг.6 сумматор тока 13 кроме первых синфазных входов 11 и 12 имеет вторые синфазные входы 23, 24. Причем относительно первых синфазных входов 11 и 12 вторые синфазные входы 23, 24 обеспечивают сдвиг фазы входных сигналов на 180°.

Рассмотрим работу заявляемого ДУ фиг.3 (фиг.2).

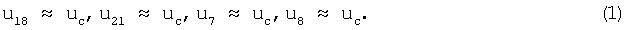

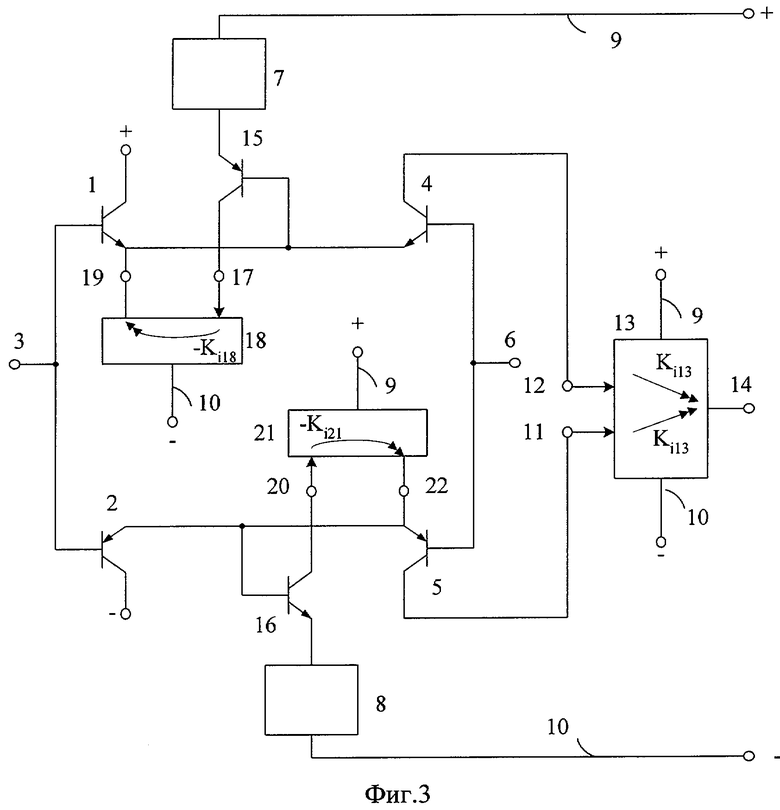

Входной синфазный сигнал uc=uc1=uc2 практически с единичным коэффициентом передачи поступает в эмиттерные цепи дифференциальных каскадов на транзисторах 1, 4 и 2, 5, а также источники опорного тока 7 и 8:

Это приводит к изменению выходного тока токовых зеркал 18 и 21 и токов эмиттеров транзисторов 15 и 16:

где y18, y21, y7, y8 - выходные проводимости токовых зеркал 18, 21 и источников опорного тока 7 и 8.

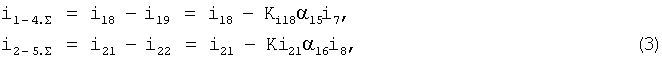

Приращения токов i7 и i8 передаются в цепи коллекторов транзисторов 15 и 16, а затем через токовые зеркала 18 и 21 - в общие эмиттерные цепи дифференциальных каскадов. Как следствие суммарные токи общих эмиттерных цепей ДК на транзисторах 1, 4 и 2, 5:

где Ki18, Ki21 - коэффициенты передачи по току токовых зеркал 18 и 21;

α15, α16 - коэффициенты передачи по току эмиттера транзисторов 15 и 16.

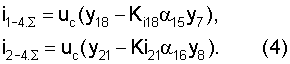

Или после преобразований (3)

Поэтому выходной ток сумматора 13, усиленный в Кi13-раз, равен

Учитывая, что Кi21≈α16≈1, из (5) находим, что выходной ток ДУ, обусловленный наличием на его входах 3 и 6 синфазного сигнала

В практических схемах источник опорного тока 7 и токовое зеркало 21, а также источник опорного тока 8 и токовое зеркало 18 выполняются по одним и тем же схемам и имеют одинаковые выходные транзисторы и их статический режим. Как следствие, их выходные проводимости равны y18=y8, y21=y7. Причем для интегральных n-p-n и p-n-p транзисторов ФГУП НПП «Пульсар» выполняются неравенства y8≪y7, y21≫y18. Поэтому в заявляемом ДУ выходной сигнал, обусловленный напряжением на выходах 3 и 6 синфазной составляющей входного напряжения равен нулю, что свидетельствует о высоких значениях коэффициента ослабления входных синфазных сигналов Кос.сф. Практически Кос.сф в заявляемом ДУ определяется неидентичностью сопротивлений коллекторных переходов транзисторов 1, 4 и 2, 5, которые оказывают на 1-2 порядка меньшее влияние на Кос.сф, чем выходные проводимости источника опорного тока. Таким образом в ДУ фиг.2 за счет введения новых связей существенно ослабляется прохождение синфазного сигнала на выход 14. Полученные выше теоретические выводы подтверждаются результатами компьютерного моделирования (фиг.10) ДУ фиг.7-9. Из графиков фиг.10 следует, что:

1. Коэффициент передачи входного синфазного сигнала Ксф.2 в заявляемом ДУ (фиг.9) в 40-50 раз меньше Ксф.3 ДУ-прототипа (фиг.7) и близок по величине Ксф.1 ДУ (фиг.8) с идеальными источниками опорного тока 7 и 8.

2. Коэффициенты передачи дифференциального сигнала заявляемого ДУ и ДУ-прототипа приблизительно одинаковы.

3. Коэффициент ослабления входного синфазного сигнала Кос.сф заявляемого ДУ в 50-80 раз лучше, чем Кос.сф ДУ-прототипа.

Библиографический список

1. Патент РФ № 2193273, H 03 F 3/45.

2. Патент Японии № 53-25232, H 03 F 3/26, 98(5) А332.

3. Патент US 2001/0052818 A1, H 03 F, 3/45.

4. Патент Японии № JP 8222972.

5. Авт. Свид. СССР № 611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - стр.103. Рис.6.11.

7. Патент США № 6.366.170 В1, H 03 F/45.

8. Патент США № 6.268.769, H 03 F/45.

9. Патент США № 3.974.455, H 03 F/45.

10. Патент США № 3.968.451, H 03 F/45.

11. Патент США № 4.837.523, H 03 F/45.

12. Патент США № 5.291.149, H 03 F/45.

13. Патент США № 4.636.743, H 03 F/45.

14. Патент США № 4.783.637, H 03 F/45.

15. Патент США № 5.515.005, H 03 F/45.

16. Патент США № 5.291.149, H 03 F/45.

17. Патент США № 5.140.280, H 03 F/45.

18. Патент США № 5.455.535, H 03 F/45.

19. Патент США № 5.523.718, H 03 F/45.

20. Патент США № 4.600.893, H 03 F/45.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292638C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2283533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292636C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292637C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2293433C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2278466C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в различных микроэлектронных устройствах усиления и преобразования аналоговых сигналов с малым напряжением питания. Технический результат заключается в повышении коэффициента ослабления входного синфазного сигнала. Дифференциальный усилитель (ДУ) содержит соединенные параллельно по входам (3, 6) ДУ дифференциальные каскады на транзисторах (Т) (1, 4) и (2, 5) и источники опорного тока (ИОТ) (7, 8), коллекторы Т (4, 5) подключены к первым синфазным входам (11 и 12) сумматора тока (13), выход которого является выходом (14) ДУ. В ДУ введены дополнительные Т (15, 16), базы которых подключены соответственно к объединенным эмиттерам Т (1, 4) и Т (2, 5), эмиттеры соединены с выходами соответствующих ИОТ (7 и 8), согласованных с шиной положительного (9) и отрицательного (10) источников питания. Причем коллектор Т (15) соединен с входом (17) первого токового зеркала (Т3) (18), выход (19) которого связан с эмиттерами Т (1 и 4), а коллектор Т (16) соединен с входом (20) второго Т3 (21), выход (22) которого связан с эмиттерами Т (2 и 5). 1 з.п. ф-лы, 10 ил.

| US 5153529 А, 06.10.1992 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| Дифференциальный усилитель | 1976 |

|

SU611288A1 |

| US 5455535 А, 03.10.1995 | |||

| US 4837523, 06.06.1989. | |||

Авторы

Даты

2007-01-27—Публикация

2005-06-21—Подача