Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с токостабилизирующими двухполюсниками в эмиттерных цепях входных транзисторов (так называемые "dual input stage") [1-20]. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Причем в качестве токостабилизирующих двухполюсников каждого из параллельно включенных ДК таких ДУ применяются резисторы [21-24], если усилитель не работает с синфазным сигналом, или источники опорного тока на транзисторах [25-29], если входные сигналы имеют синфазную составляющую. Первый вариант построения ДУ практически не используется в структуре операционных усилителей, т.к. он не дает приемлемых значений коэффициента ослабления входного синфазного сигнала (Кос.сф). Это связано с тем, что для получения больших значений Кос.сф необходимо выбирать сопротивление токостабилизирующих резисторов на уровне сотен килом, что создает проблемы со статическим режимом при низковольтном питании. В технической литературе по аналоговой схемотехнике хорошо известно следующее правило построения ДУ - "в качестве токостабилизирующих двухполюсников ДУ не следует применять резисторы" (Ежков Ю.С. Справочник по схемотехнике усилителей, М., Радиософт, 2002. - С.81, 3 абзац сверху). С другой стороны, второй вариант построения ДУ также имеет ряд недостатков, связанных с уменьшением надежности схемы при радиационных и тепловых воздействиях, а также с наличием паразитной емкости на подложку у транзисторов ДУ, что ухудшает частотный диапазон. Кроме того, в практических схемах известных ДУ коэффициент Кос.сф оказывается также небольшим в связи с тем, что выходное сопротивление простейших токостабилизирующих двухполюсников на основе токовых зеркал оказывается также небольшим (30-100 кОм).

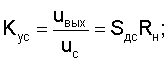

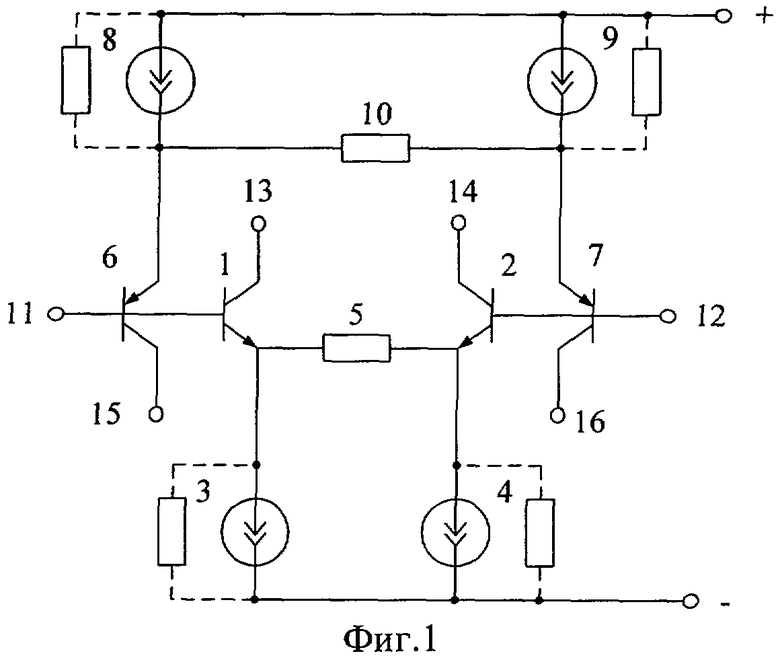

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4636743, H 03 F 3/45 (прототип), содержащий первый 1 и второй 2 входные n-p-n транзисторы, эмиттеры которых соединены с первыми выводами первого 3 и второго 4 токостабилизирующих двухполюсников и связаны друг с другом через первый 5 резистор местной обратной связи, первый 6 и второй 7 входные транзисторы p-n-p типа, эмиттеры которых соединены с первыми выводами третьего 8 и четвертого 9 токостабилизирующих двухполюсников и связаны друг с другом через второй 10 резистор местной обратной связи, причем база первого n-p-n транзистора 1 соединена с базой первого p-n-p транзистора 6 и первым входом 11 дифференциального усилителя, база второго n-p-n транзистора 2 соединена с базой второго p-n-p транзистора 7 и вторым 12 входом дифференциального усилителя, коллекторы первого 1 и второго 2 входных n-p-n транзисторов соединены с соответствующими первым 13 и вторым 14 токовыми выходами, согласованными с шиной положительного источника питания, а коллекторы первого 6 и второго 7 p-n-p входных транзисторов соединены с соответствующими третьим 15 и четвертым 16 токовыми выходами, согласованными с шиной отрицательного источника питания.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов при изменении входного синфазного напряжения в диапазоне, близком к напряжению питания. В значительной степени этот недостаток проявляется при использовании в качестве токостабилизирующих двухполюсников-резисторов.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ и расширении допустимого диапазона изменения входных синфазных напряжений до уровня напряжений питания. При этом в качестве токостабилизирующих двухполюсников авторы рекомендуют применять резисторы, что недостижимо при других вариантах построения ДУ.

Поставленная цель достигается тем, что в дифференциальный усилитель фиг.1, содержащий первый 1 и второй 2 входные n-p-n транзисторы, эмиттеры которых соединены с первыми выводами первого 3 и второго 4 токостабилизирующих двухполюсников и связаны друг с другом через первый 5 резистор местной обратной связи, первый 6 и второй 7 входные транзисторы p-n-p типа, эмиттеры которых соединены с первыми выводами третьего 8 и четвертого 9 токостабилизирующих двухполюсников и связаны друг с другом через второй 10 резистор местной обратной связи, причем база первого n-p-n транзистора 1 соединена с базой первого p-n-p транзистора 6 и первым входом 11 дифференциального усилителя, база второго n-p-n транзистора 2 соединена с базой второго p-n-p транзистора 7 и вторым 12 входом дифференциального усилителя, коллекторы первого 1 и второго 2 входных n-p-n транзисторов соединены с соответствующими первым 13 и вторым 14 токовыми выходами, согласованными с шиной положительного источника питания, а коллекторы первого 6 и второго 7 p-n-p входных транзисторов соединены с соответствующими третьим 15 и четвертым 16 токовыми выходами, согласованными с шиной отрицательного источника питания, вводятся новые связи - второй вывод третьего токостабилизирующего двухполюсника 8 соединен с первым токовым выходом 13, второй вывод четвертого токостабилизирующего двухполюсника 9 соединен со вторым токовым выходом 14, второй вывод первого токостабилизирующего двухполюсника 3 связан с третьим токовым выходом 15, а второй вывод второго токостабилизирующего двухполюсника 4 соединен с четвертым токовым выходом 16.

Схема заявляемого устройства в соответствии с п.1, п.2 формулы изобретения показана на чертеже фиг.2.

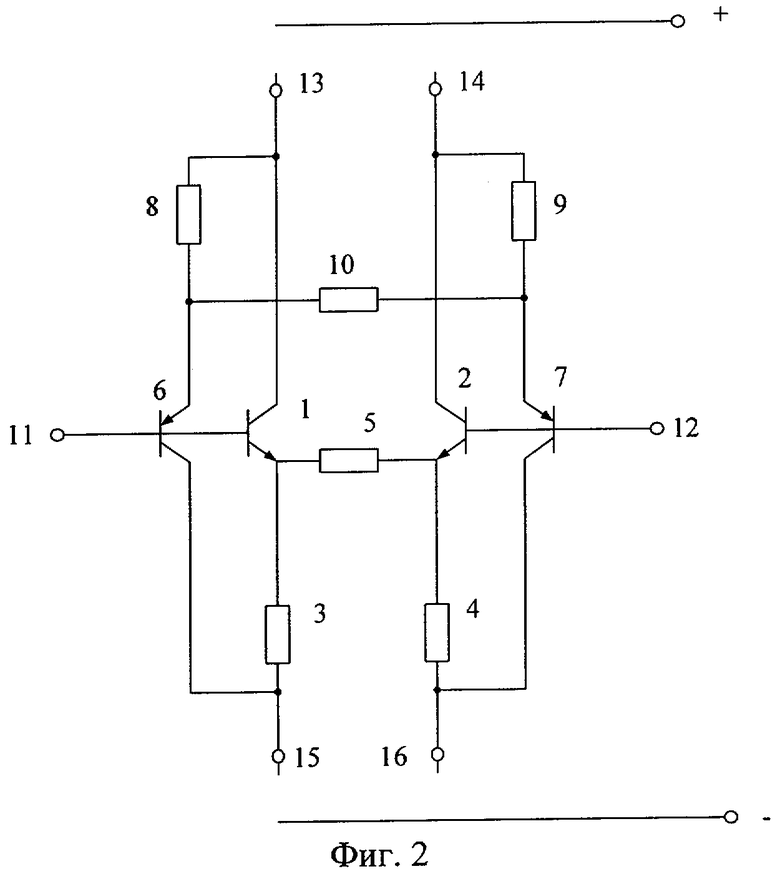

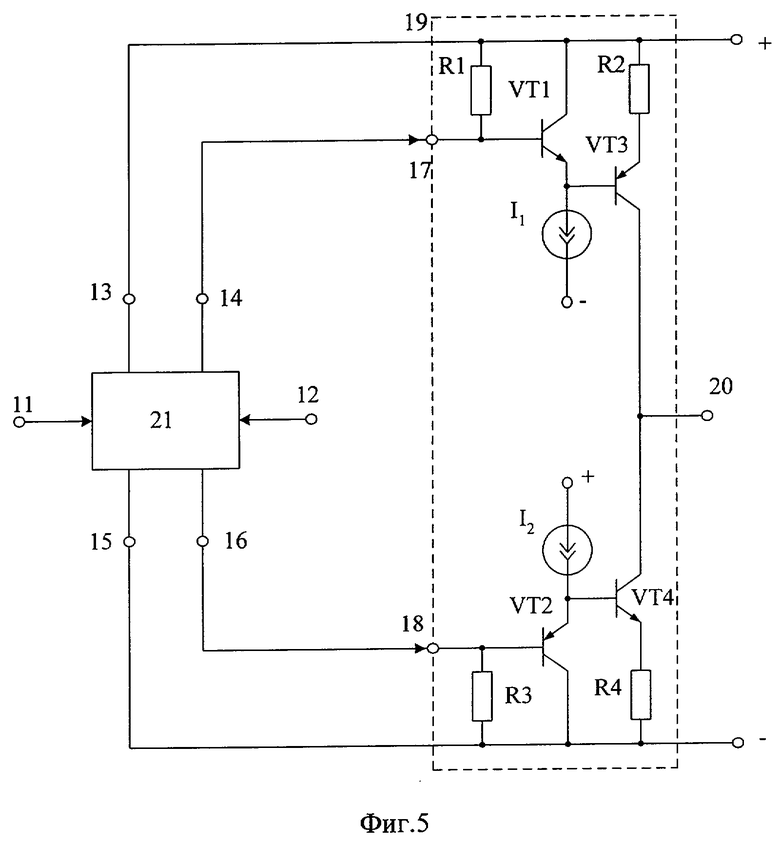

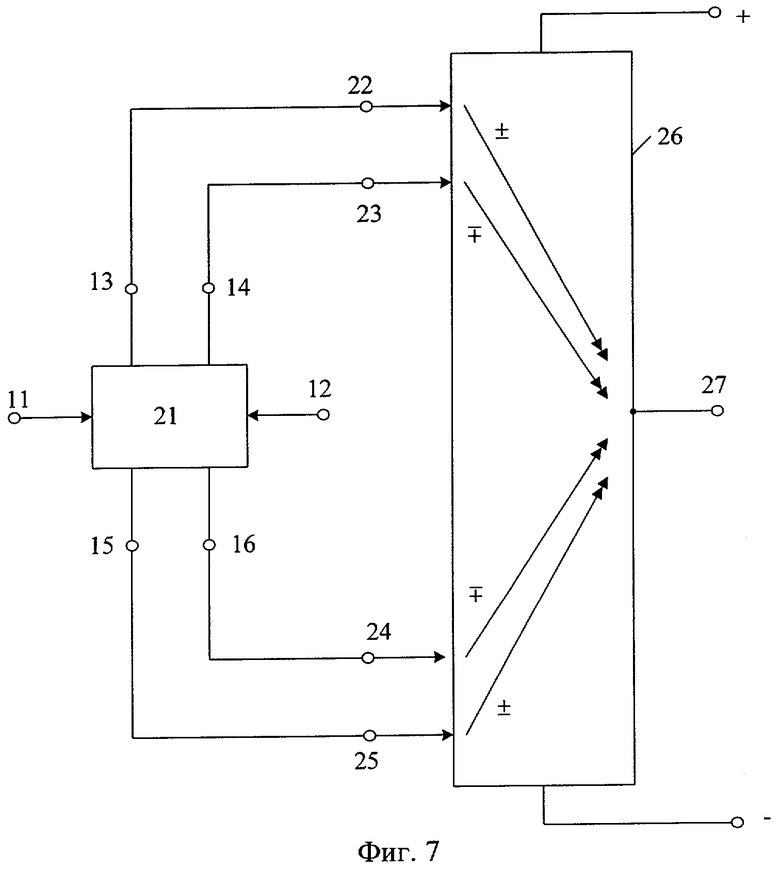

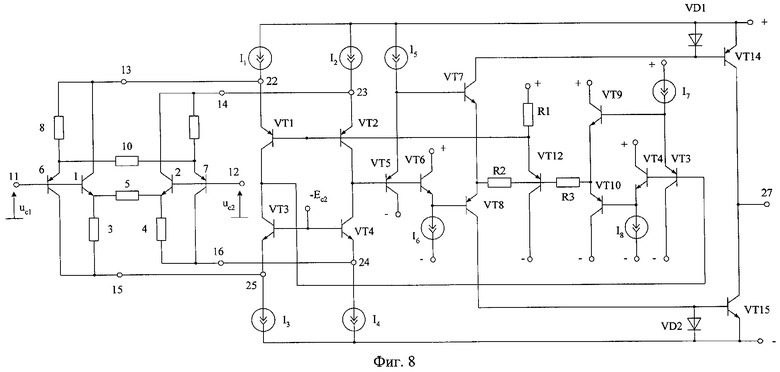

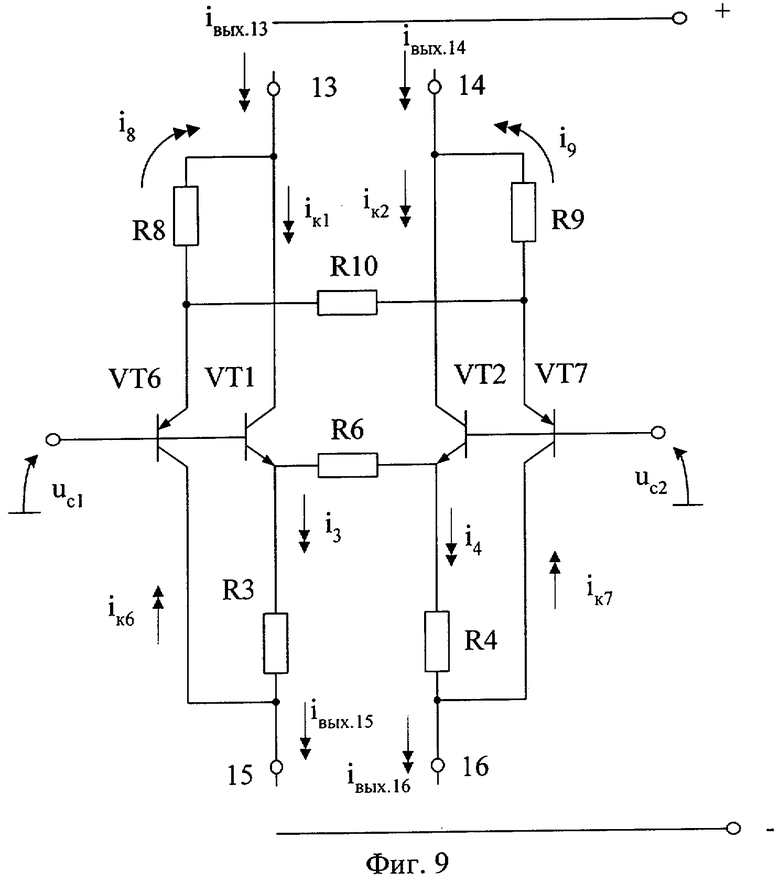

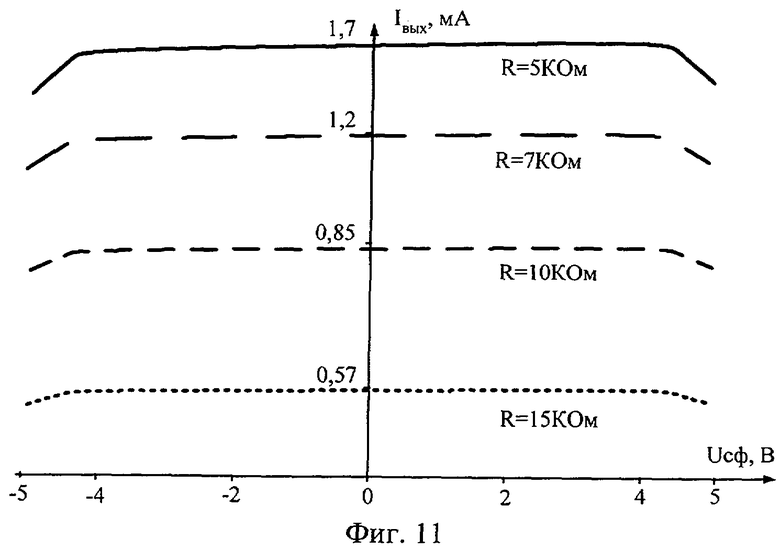

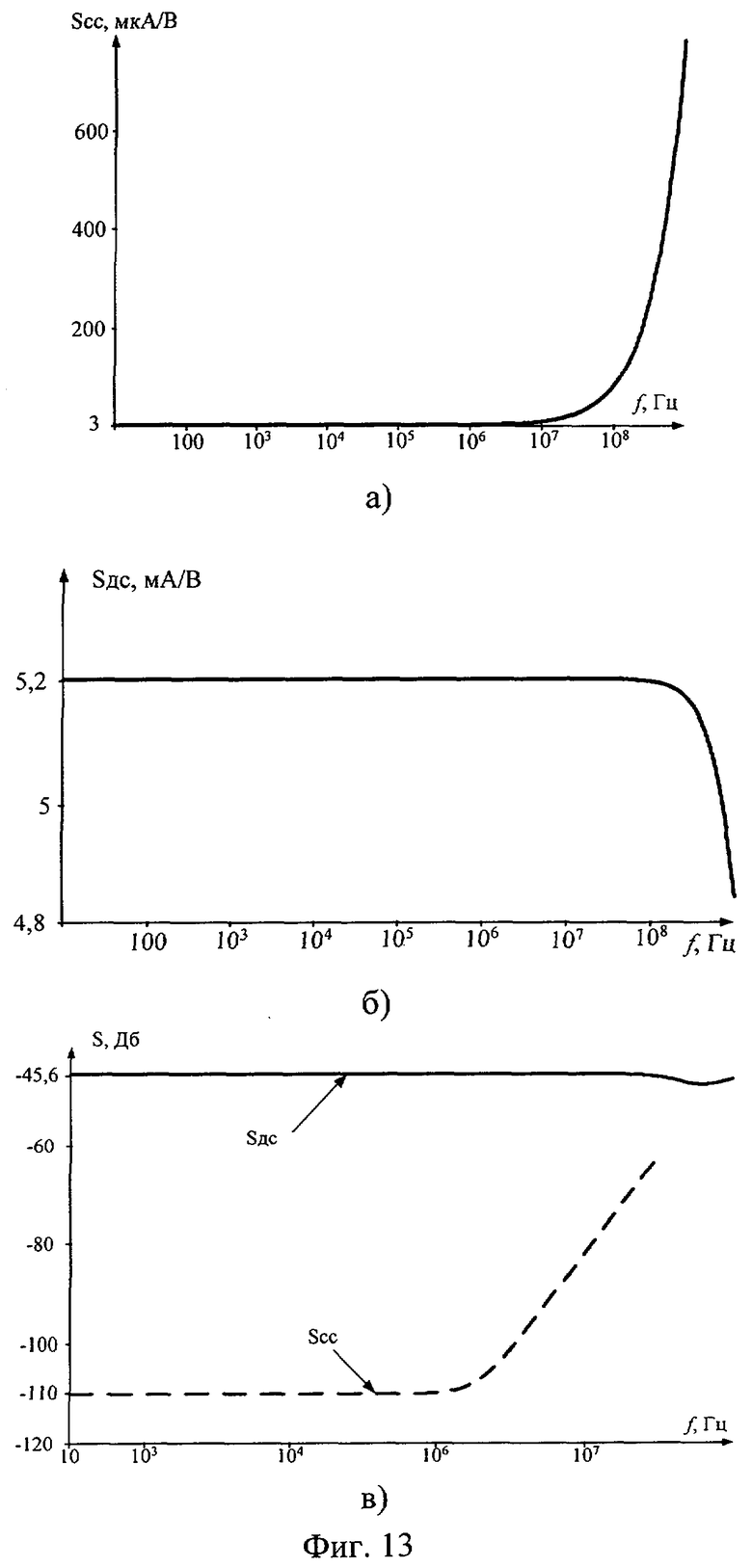

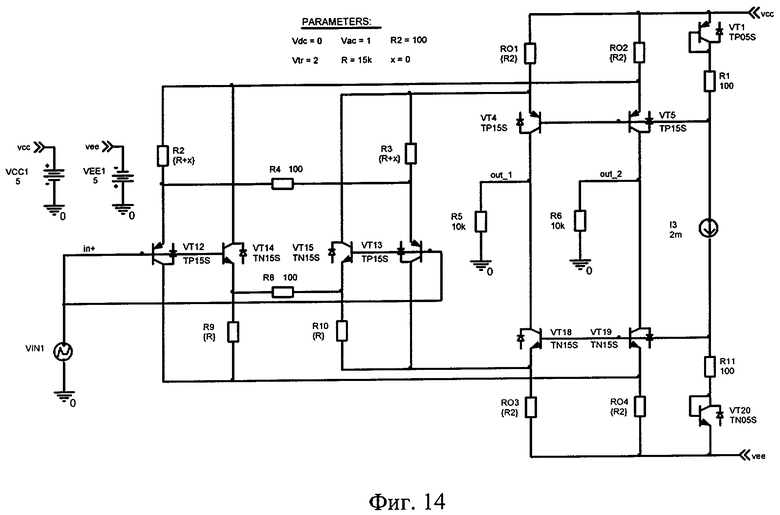

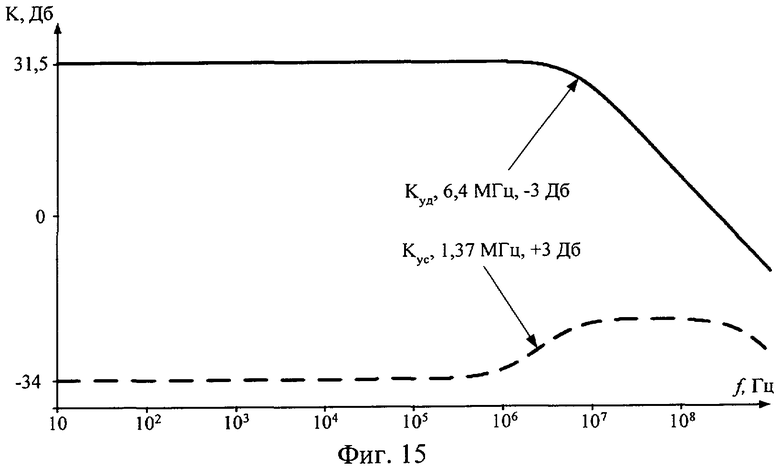

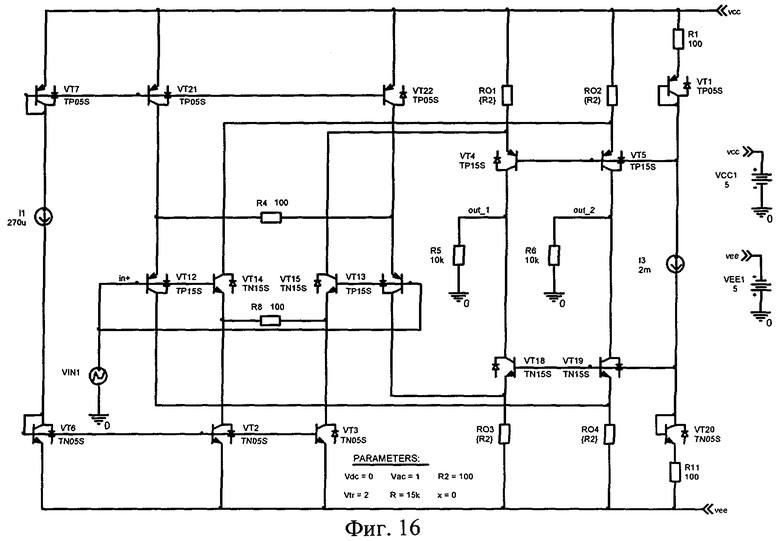

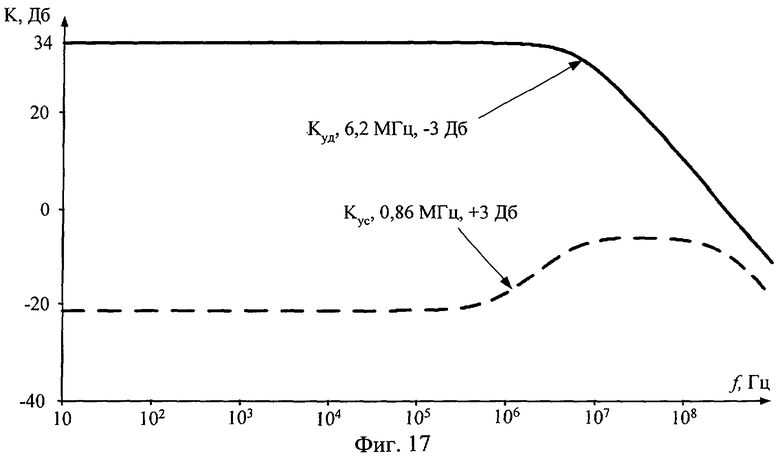

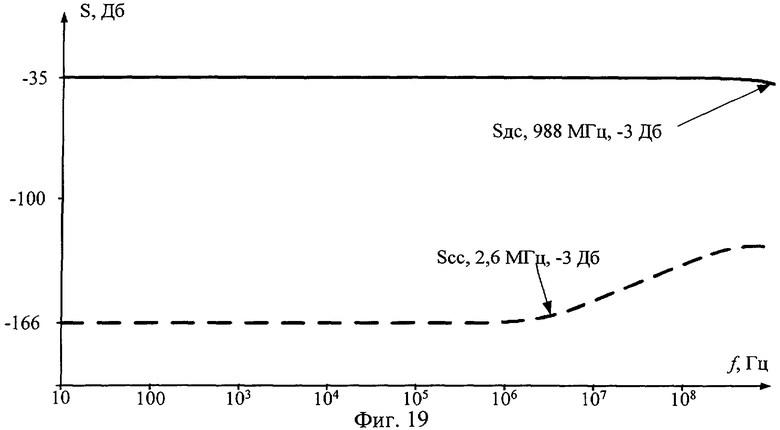

На чертежах фиг.3 и фиг.7 показан заявляемый ДУ в соответствии с п.3 и п.4 формулы изобретения. Частные варианты построения ДУ фиг.3 показаны на чертежах фиг.4, фиг.5, фиг.6. Пример построения ДУ фиг.7 показан на чертеже фиг.8. На чертеже фиг.9 приведены токи и напряжения ДУ фиг.2, поясняющие его работу на синфазном сигнале uc=uc1=uc2. Результаты компьютерного моделирования ДУ фиг.2 при параметрах элементов и режимах, указанных на чертеже фиг.10, показаны на чертеже фиг.11. На чертеже фиг.12 приведена схема заявляемого ДУ, которая исследовалась авторами в среде PSpice на моделях интегральных транзисторов ФГУП НПП "Пульсар". Результаты этого моделирования показаны на чертеже фиг.13. На чертеже фиг.14 изображена частная схема ДУ фиг.3, которая исследовалась авторами в среде PSpice (фиг.15). На чертеже фиг.16 приведена схема ДУ-прототипа с реальными токостабилизирующими двухполюсниками на основе транзисторов VT21, VT22 и VT2, VT3. На чертеже фиг.17 показаны результаты компьютерного моделирования схемы фиг.16. На чертеже фиг.18 приведена исследованная авторами схема ДУ, соответствующая фиг.7. На чертеже фиг.20 показана схема исследованного авторами Rail-to-rail по входу и Rail-to-rail по выходу операционного усилителя. На чертеже фиг.21 показана амплитудная характеристика усилителя фиг.20 в режиме повторителя напряжения (при 100% обратной связи).

На чертежах фиг.13, фиг.15. фиг.17, фиг.19 приняты следующие обозначения параметров ДУ:

Scc - крутизна передачи ДУ по дифференциальному входному сигналу uвх;

Sдс - крутизна передачи ДУ по синфазному входному сигналу uc;

Куд - коэффициент передачи дифференциального входного напряжения ДУ uвх;

Кус - коэффициент передачи синфазного входного напряжения uc.

Причем между этими параметрами и коэффициентом ослабления входных синфазных сигналов Кос.сф существует следующая взаимосвязь

где uвх - напряжение между входами ДУ 11 и 12;

uc - синфазное входное напряжение на входах 11 и 12;

uвых - выходное напряжение ДУ;

Rн - сопротивление нагрузки, подключаемое к выходу ДУ.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные n-p-n транзисторы, эмиттеры которых соединены с первыми выводами первого 3 и второго 4 токостабилизирующих двухполюсников и связаны друг с другом через первый 5 резистор местной обратной связи, первый 6 и второй 7 входные транзисторы p-n-p типа, эмиттеры которых соединены с первыми выводами третьего 8 и четвертого 9 токостабилизирующих двухполюсников и связаны друг с другом через второй 10 резистор местной обратной связи, причем база первого n-p-n транзистора 1 соединена с базой первого p-n-p транзистора 6 и первым входом 11 дифференциального усилителя, база второго n-p-n транзистора 2 соединена с базой второго p-n-p транзистора 7 и вторым 12 входом дифференциального усилителя, коллекторы первого 1 и второго 2 входных n-p-n транзисторов соединены с соответствующими первым 13 и вторым 14 токовыми выходами, согласованными с шиной положительного источника питания, а коллекторы первого 6 и второго 7 p-n-p входных транзисторов соединены с соответствующими третьим 15 и четвертым 16 токовыми выходами, согласованными с шиной отрицательного источника питания. Второй вывод третьего токостабилизирующего двухполюсника 8 соединен с первым токовым выходом 13, второй вывод четвертого токостабилизирующего двухполюсника 9 соединен со вторым токовым выходом 14, второй вывод первого токостабилизирующего двухполюсника 3 связан с третьим токовым выходом 15, а второй вывод второго токостабилизирующего двухполюсника 4 соединен с четвертым токовым выходом 16.

В соответствии с п.3 формулы изобретения на чертеже фиг.3 выходы 14 и 16 ДУ соединены с синфазными входами 17 и 18 синфазного сумматора двух сигналов 19, имеющего выход 20. Частные варианты построения синфазного сумматора двух сигналов 19 и его соединение с заявляемым ДУ приведены на чертежах фиг.4, фиг.5, фиг.6.

На чертеже фиг.7 приведен частный вариант включения заявляемого ДУ 21 в соответствии с п.4 формулы изобретения. В этой схеме первый 13 и третий 15 токовые выходы, а также второй 14 и четвертый 16 токовые выходы связаны с попарно противофазными входами 22 и 23, 24 и 25 сумматора четырех сигналов 26, имеющего выход 27. В этой схеме обеспечивается более глубокое ослабление синфазного сигнала.

Рассмотрим работу заявляемого ДУ фиг.2. Приращение токов в схеме фиг.2 при изменении входного синфазного сигнала uc=uc1=uc2 показано на чертеже фиг.9.

Если на входы 11 и 12 подать синфазное напряжение uc=uc1=uc2, то в элементах схемы появятся переменные составляющие токов

I3≈ucy3, i4≈ucy4, i8≈ucy8, i9≈ucy9,

где y3=R3 -1, y4=R4 -1, y8=R8 -1, y9=R9 -1.

Эти приращения токов эмиттеров транзисторов VT1, VT2 и VT6, VT7 передаются в коллекторные цепи

iк1=α1i3, iк2=α2i4, iк6=α6i8, iк7=α7i9,

где αi≈1, - коэффициент передачи по току эмиттера i-го транзистора.

Следует обратить внимание, что в выходных узлах 13, 14 и 15, 16 происходит вычитание близких по величине токов

iвых.13=iк1-i8, iвых.14=iк2-i9, iвых.15=i3-iк6, iвых.16=i4-iк7

или

iвых.13=uc(α1y3-y8), iвых.14=uc(α2y4-y9), iвых.15=uc(y3-α6y8),

iвых.16=uc(y4-α7y9).

Если обеспечить равенство y3=y4=y8=y9, то при αi=1 в выходных узлах 13-16 будут отсутствовать составляющие, обусловленные входным синфазным сигналом, то есть крутизна преобразования входного синфазного напряжения в выходной ток Scc=iвых/uc будет близка к нулю. В реальных схемах минимальные значения Scc.min будут определяться проводимостями коллекторных переходов применяемых транзисторов, а также отличием их коэффициентов передачи по току эмиттера (αi) от единицы:

где rк1=1÷2 МОм - сопротивление закрытого коллекторного перехода транзистора VT1.

При R8=y8 -1=y3 -1=10 КОм, α=0,99 - эффективное значение минимальной крутизны преобразования синфазного сигнала

Scc.min≈10-6Ом-1.

Заметим, что при использовании классических источников опорного тока, выходное сопротивление которых не превышает 60-100 кОм, численные значения Sсс оказываются значительно хуже.

Важнейшее свойство заявляемой схемы ДУ, которое наиболее ярко проявляется при его использовании в структурах фиг.3, фиг.7 - широкий допустимый диапазон изменения синфазного сигнала (uc.max) - практически равный или даже превышающий на 50-100 мВ напряжения питания (Еп). Следует обратить внимание, что построение высокоэффективных входных дифференциальных каскадов с uc.max=±Eп относится к числу нерешенных проблем современной аналоговой микросхемотехники. Для построения так называемых Rail-to-rail по входу дифференциальных усилителей с низковольтным питанием предложено большое число каскадов с переключаемыми (синфазным сигналом) источниками опорного тока, например [31]. Однако они характеризуются повышенным уровнем нелинейных искажений и другими недостатками.

В заявляемой схеме имеется два канала усиления, причем при uc (+)=Еп (+) происходит самовыключение одного канала на p-n-p транзисторах, а при uc (-)=Еп (-) самовыключается канал на n-p-n транзисторах. При этом суммарное усиление дифференциального сигнала в ДУ (фиг.3, фиг.7) уменьшается только в два раза, что несущественно для многих применений ДУ в системах с глубокой обратной связью. Таким образом, заявляемый ДУ имеет более высокий, чем известные устройства, диапазон изменения входного синфазного сигнала.

Полученные выше выводы подтверждаются результатами моделирования предлагаемых схем в среде PSpice с использованием моделей интегральных транзисторов ФГУП НПП "Пульсар" (г. Москва).

На чертеже фиг.11 показана зависимость выходного тока ДУ фиг.10 (фиг.2) от уровня входного синфазного сигнала при разных сопротивлениях резисторов R1=R2=R3=R4. Данные графики показывают, что выходной ток узла 13 ДУ фиг.10 практически не изменяется, что свидетельствует о высоком подавлении синфазного сигнала.

Графики частотной зависимости крутизны усиления дифференциального сигнала (Sдс=iвых/uвх) (ДУ фиг.12), зависящей от сопротивления резисторов 5 и 10, и крутизны усиления синфазного (Sсс=iвых/uс) сигнала (ДУ фиг.10), приведенные на чертеже фиг.13, показывают, что коэффициент ослабления синфазного сигнала для каждого отдельного выхода схемы заявляемого ДУ имеет значение порядка 60 дБ. Это значительно лучше, чем Кос.сф ДУ-прототипа фиг.16 на основе транзисторных источников опорного тока. Действительно, сравнение результатов моделирования схем фиг.14 и фиг.16 показывает, что предлагаемые ДУ имеют более высокий Кос.сф и более широкий частотный диапазон по ослаблению синфазных сигналов. Еще большие значения Кос.сф реализуются в схеме фиг.18, которая отличается от схемы фиг.14 введением дополнительного повторителя тока F1, вычитающего синфазные ошибки, присутствующие на выходах 13-14 ДУ. Это обеспечивает существенное повышение Кос.сф (до величины 3,1·106 или до 130 дБ), т.к. схема фиг.18 становится полностью симметричной. Об этом свидетельствуют результаты эксперимента, представленные на чертеже фиг.19.

Исследования максимально возможного диапазона изменения входного синфазного напряжения Uс.max в заявляемом ДУ проводились при его включении в схему ОУ фиг.20. Эти исследования показывают (фиг.21), что Uc.max только на 20-30 мВ меньше напряжения питания, что недостижимо при других известных вариантах построения входного каскада. Для дальнейшего повышения Uc.max в схеме фиг.20 необходимо уменьшать статическое падение напряжения на резисторах R01-R04 с 0,3 В до 0,1 В. При этом Uc.max может достигать 5,1 В.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент РФ №2193273, H 03 F 3/45.

2. Патент Японии №53-25232, H 03 F 3/26, 98(5) А332.

3. Патент US 2001/0052818 A1, H 03 F, 3/45.

4. Патент Японии №JP8222972.

5. Авт. Свид. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989. - Стр.103, рис.6.11.

7. Патент США №6366170 В 1 H 03 F/45.

8. Патент США №6268769 H 03 F/45.

9. Патент США №3974455 H 03 F/45.

10. Патент США №3968451 H 03 F/45.

11. Патент США №4837523 H 03 F/45.

12. Патент США №5291149 H 03 F/45.

13. Патент США №4636743 H 03 F/45.

14. Патент США №4783637 H 03 F/45.

15. Патент США №5515005 H 03 F/45.

16. Патент США №5291149 H 03 F/45

17. Патент США №5140280 H 03 F/45.

18. Патент США №5455535 H 03 F/45.

19. Патент США №5523718 H 03 F/45.

20. Патент США №4600893 H 03 F/45.

21. Полонников Д.Е. Операционные усилители: Принципы построения, теория, схемотехника. - М., 1983.- 216 с. - Стр.156 рис.4.25.

22. Патент США №4131809, H 03 FK.

23. Патент США №3323070 H 03 F 3/45.

24. Патент ЕР №1351381 A1, H 03 F 3/30.

25. Патент США №5365191 H 03 F 3/45.

26. Патент США №4390848 H 03 F 3/45.

27. Патент США №5774020 H 03 F 3/45.

28. Патент США №4146844 H 03 F 1/26.

29. Патент США №4890067 H 03 F 3/45.

30. Патент США №4636743, H 03 F 3/45.

31. Патент США №5610557 H 03 F 3/45.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292637C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2005 |

|

RU2292636C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2320078C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444116C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441316C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ СИНФАЗНОГО СИГНАЛА | 2006 |

|

RU2319286C1 |

Изобретение относится к радиотехнике и связи для использования в различных микроэлектронных устройствах усиления и преобразования аналоговых сигналов с малым напряжением питания. Технический результат заключается в повышении коэффициента ослабления входного синфазного сигнала в более широком диапазоне изменения входных синфазных напряжений. Дифференциальный усилитель (ДУ) содержит (на фиг.2) входные n-p-n транзисторы (Т) (1, 2), эмиттеры которых соединены с токостабилизирующими двухполюсниками (ТД) (3, 4) и связаны друг с другом через резистор (Р) (5) местной обратной связи, входные Т (6, 7) p-n-p типа, эмиттеры которых соединены с ТД (8, 9) и связаны друг с другом через Р (10) местной обратной связи, причем базы Т (1, 6) соединены с первым входом ДУ, базы Т (2, 7) - со вторым входом ДУ, а являющиеся токовыми выходами ДУ коллекторы Т (1, 2, 6, 7) соединены соответственно со вторыми выводами ТД (8, 9, 3, 4). 3 з.п. ф-лы, 21 ил.

| US 4636743, 13.01.1987 | |||

| Дифференциальный усилитель | 1985 |

|

SU1246340A1 |

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| US 3551832, 29.12.1970. | |||

Авторы

Даты

2006-09-10—Публикация

2005-04-04—Подача