Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ), компараторах и т.п.) с малым напряжением питания.

Известны схемы дифференциальных усилителей (ДУ) с токостабилизирующим двухполюсником в эмиттерной цепи входных транзисторов и с выходным каскадом, выполненном на повторителе тока (токовом зеркале). ДУ с такой архитектурой стали основой построения многих современных операционных усилителей [1-12], в т.ч. ОУ с опцией rail-to-rail, имеющих максимальную амплитуду выходного напряжения, близкую к напряжению питания. Однако такие ДУ имеют недостаточно высокое ослабление входных синфазных сигналов (коэффициент Кос.сф) при использовании в общей эмиттерной цепи в качестве токостабилизирующего двухполюсника пассивных элементов (резисторов), что отрицательно сказывается на точности аналоговых интерфейсов с их использованием. Это связано с тем, что для получения больших значений Кос.сф необходимо выбирать сопротивление токостабилизирующего резистора на уровне сотен килоом, что создает проблемы со статическим режимом при низковольтном питании (Еп=1,5÷5 В). С другой стороны, при малых напряжениях питания (Еп=±1 В применение токостабилизирующих резисторов является

единственным вариантом построения дифференциального каскада, так как другие схемы его построения по биполярным технологиям требуют напряжения питания не менее 1,5 В).

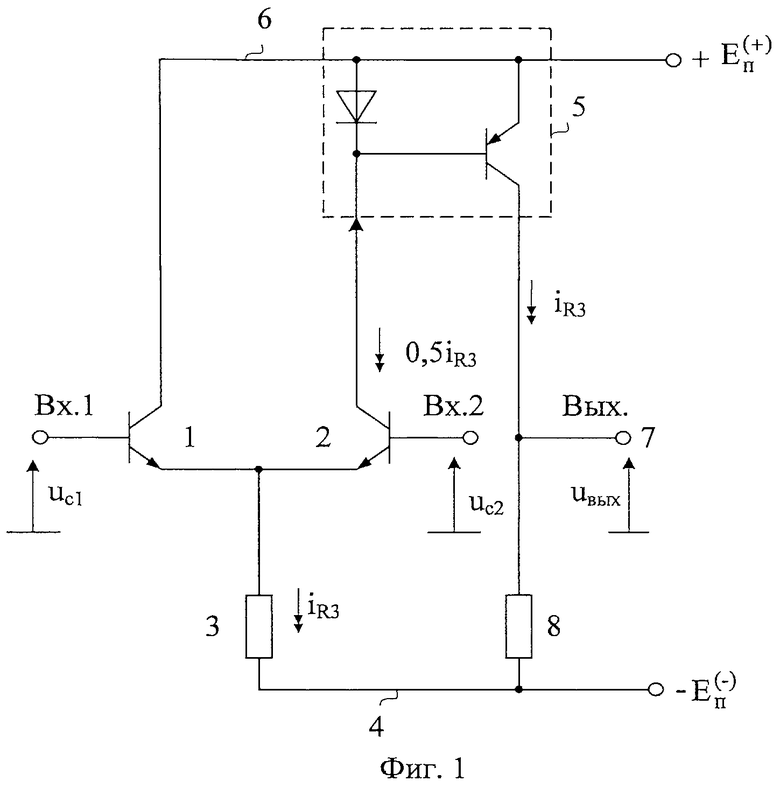

Ближайшим прототипом (фиг.1) заявляемого устройства является дифференциальный усилитель, описанный в патенте США №4264873, fig. 3, содержащий первый 1 и второй 2 входные транзисторы, эмиттеры которых объединены и через первый 3 токостабилизирующий двухполюсник связаны с первой 4 шиной источника питания, коллектор второго 2 входного транзистора соединен со входом первого 5 токового зеркала, согласованного со второй 6 шиной источника питания, выход первого 5 токового зеркала подключен к выходу 7 устройства и через двухполюсник нагрузки 8 связан с первой 4 шиной источника питания, причем коллектор первого 1 входного транзистора связан со второй 6 шиной источника питания.

Существенный недостаток известного ДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов. Прежде всего, данный недостаток проявляется при использовании в качестве токостабилизирующего двухполюсника 3 резисторов или простейших источников тока на транзисторах с малым напряжением Эрли, которые при милиамперных токах имеют небольшое выходное сопротивление (порядка 30-60 кОм).

Основная задача предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ДУ (Кос.сф) при относительно небольших внутренних сопротивлениях токостабилизирующего двухполюсника 3. При этом в заявляемом ДУ в качестве токостабилизирующего двухполюсника при низковольтном питании могут применяться сравнительно низкоомные резисторы (единицы килоом). Тем не менее это несущественно сказывается на численных значениях Кос.сф.

Поставленная задача решается тем, что в дифференциальном усилителе фиг.1, содержащем первый 1 и второй 2 входные транзисторы, эмиттеры которых объединены и через первый 3 токостабилизирующий двухполюсник связаны с первой 4 шиной источника питания, коллектор второго 2 входного транзистора соединен со входом первого 5 токового зеркала, согласованного со второй 6 шиной источника питания, выход первого 5 токового зеркала подключен к выходу 7 устройства и через двухполюсник нагрузки 8 связан с первой 4 шиной источника питания, причем коллектор первого 1 входного транзистора связан со второй 6 шиной источника питания, предусмотрены новые элементы и связи - объединенные эмиттеры первого 1 и второго 2 входных транзисторов соединены с базой дополнительного транзистора 9, коллектор дополнительного транзистора 9 соединен с первой 4 шиной источника питания, эмиттер дополнительного транзистора 9 связан со входом дополнительного токового зеркала 10 через второй 11 токостабилизирующий двухполюсник, а выход дополнительного токового зеркала 10 соединен с выходом 7 устройства.

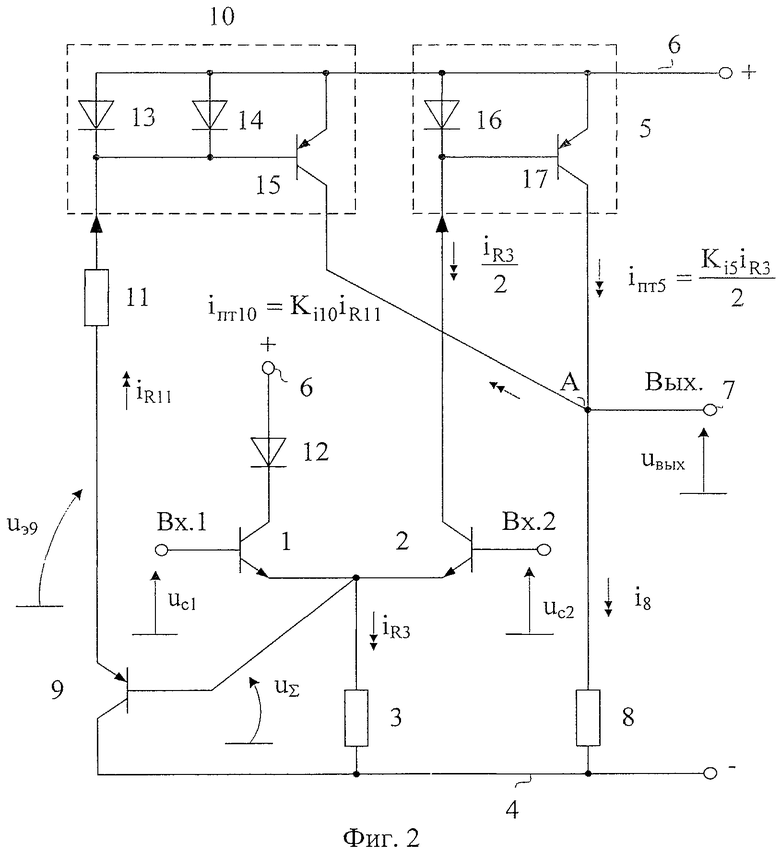

На фиг.1 показана схема ДУ-прототипа. Схема заявляемого устройства показана на фиг.2.

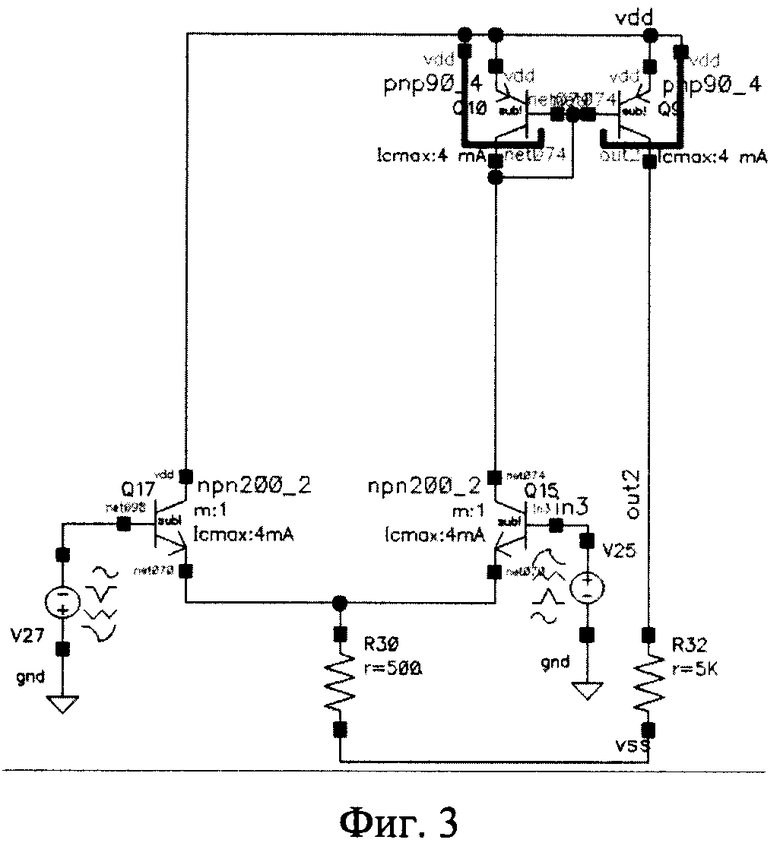

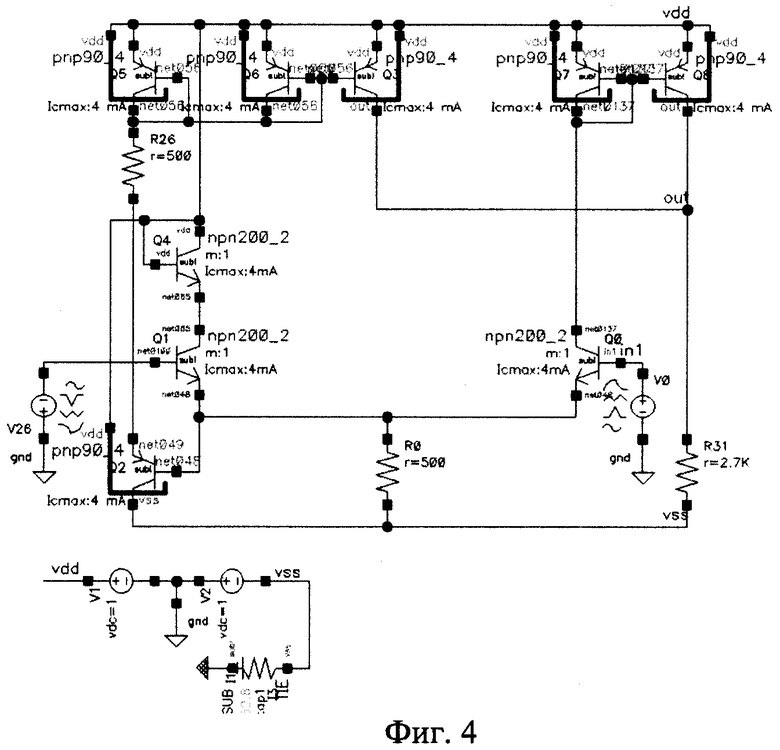

На фиг.3 представлена схема фиг.1 в среде компьютерного моделирования Cadance на моделях SiGe интегральных транзисторов, а на фиг.4 - заявляемого ДУ.

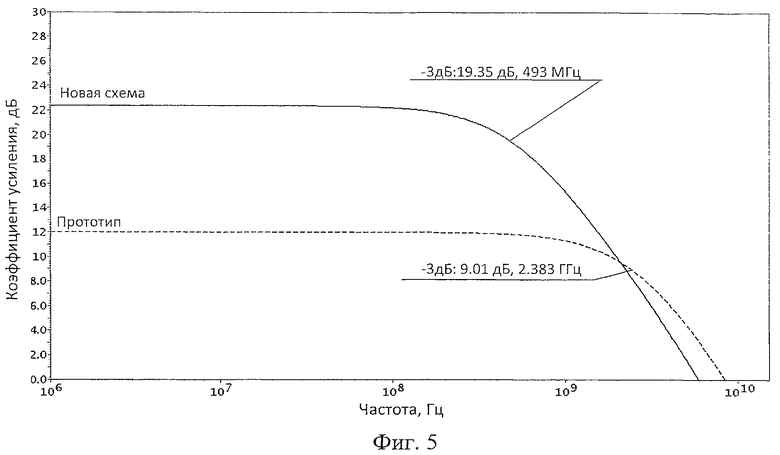

На фиг.5 показаны частотные зависимости ее коэффициента усиления по напряжению сравниваемых схем ДУ фиг.3 и фиг.4.

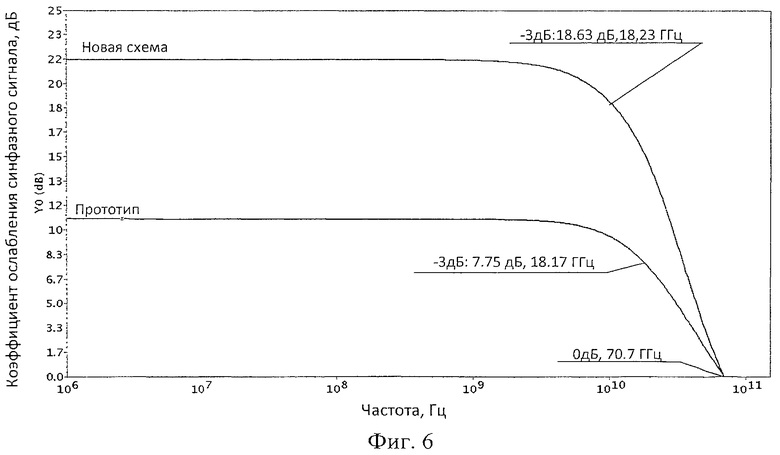

На фиг.6 приведены результаты компьютерного моделирования частотной зависимости Кос.сф сравниваемых схем фиг.3 и фиг.4.

Дифференциальный усилитель фиг.2 содержит первый 1 и второй 2 входные транзисторы, эмиттеры которых объединены и через первый 3 токостабилизирующий двухполюсник связаны с первой 4 шиной источника питания, коллектор второго 2 входного транзистора соединен со входом первого 5 токового зеркала, согласованного со второй 6 шиной источника питания, выход первого 5 токового зеркала подключен к выходу 7 устройства и через двухполюсник нагрузки 8 связан с первой 4 шиной источника питания, причем коллектор первого 1 входного транзистора связан со второй 6 шиной источника питания. Объединенные эмиттеры первого 1 и второго 2 входных транзисторов соединены с базой дополнительного транзистора 9, коллектор дополнительного транзистора 9 соединен с первой 4 шиной источника питания, эмиттер дополнительного транзистора 9 связан со входом дополнительного токового зеркала 10 через второй 11 токостабилизирующий двухполюсник, а выход дополнительного токового зеркала 10 соединен с выходом 7 устройства.

На фиг.2, в соответствии с п.2 формулы изобретения, первый 3 и второй 11 токостабилизирующие двухполюсники выполнены в виде резисторов с приблизительно одинаковыми сопротивлениями, причем коэффициент передачи по току первого 5 токового зеркала близок к единице, а дополнительного токового зеркала 10 - в два раза меньше.

Кроме этого на фиг.2, в соответствии с п.3 формулы изобретения, первый 3 и второй 11 токостабилизирующие двухполюсники выполнены в виде резисторов, причем сопротивление первого 3 токостабилизирующего резистора может быть в два раза меньше сопротивления второго 11 токостабилизирующего двухполюсника, а коэффициент передачи по току первого 5 и дополнительного 11 токовых зеркал одинаковы. Токовые зеркала 5 и 10 выполнены на p-n переходах 13, 14, 16 и транзисторах 15 и 17. При этом коэффициент передачи по току токового зеркала 10 получается в 2 раза меньше, чем токового зеркала 5.

В соответствии с п.4 формулы изобретения, коллектор первого 1 входного транзистора ДУ фиг.2 связан со второй 6 шиной источника питания через дополнительный p-n переход 12. При этом обеспечивается симметрия статического режима транзисторов 1 и 2 по напряжению коллектор-база, что снижает его погрешности.

В качестве двухполюсника 8 могут применяться источники опорного тока на биполярных транзисторах или резисторах.

Рассмотрим работу заявляемого ДУ фиг.2.

Статический режим ДУ фиг.2 при uc1=uc2=0 обеспечивается двухполюсниками 3 и 11. Учитывая, что напряжение между входом токового зеркала 16 и второй 6 шиной источников питания близко к напряжению эмиттер-база транзисторов 1, 2, 9 (Uэб=0,7 В) можно найти, что статическое падение напряжения на двухполюсниках (резисторах) 11 и 3 одинаково и при одинаковых сопротивлениях R11=R3 через них текут одинаковые статические токи.

Если на выходы ДУ фиг.2 подается синфазное напряжение uс1=uс2=uс, то это вызывает изменение токов iR3 и iR11 через двухполюсники 3 и 11

где R3, R11 - сопротивления двухполюсников 3 и 11;

uΣ- приращение напряжения на эмиттерах входных транзисторов 1 и 2, вызванное изменением uc;

u9≈uэ9≈uc - приращение напряжения на эмиттере транзистора 9.

Ток iR3 делится по каналам между эмиттерами транзисторов 1 и 2, далее, передается на выход токового зеркала 5 (iпт5) и создает в двухполюснике нагрузки 8 первую составляющую выходного тока, обусловленную влиянием синфазного сигнала uc

где α2 - коэффициент передачи по току эмиттера второго 2 входного транзистора;

Кi5 - коэффициент передачи по току первого токового зеркала 5 (iпт10).

Вторая составляющая выходного тока (iпт10), обусловленная влиянием uc и направленная в двухполюснике нагрузки 8 противофазно первой составляющей iпт5, создается токовым зеркалом 10

где Кi10 - коэффициент передачи по току токового зеркала 10.

Поэтому результирующий ток нагрузки 8 (i8) и напряжение на двухполюснике нагрузки 8 (i8R8), а также коэффициент передачи синфазного сигнала Ксф

где R3, R11, R8 - сопротивления двухполюсников 3, 11, 8.

Ксф - коэффициент передачи синфазного сигнала ДУ фиг.2,

- коэффициент передачи синфазного сигнала ДУ uс=uс1=uc2 фиг.2 при Кi10=0 (т.е. ДУ-прототипа фиг.1),

- коэффициент передачи синфазного сигнала ДУ uс=uс1=uc2 фиг.2 при Кi10=0 (т.е. ДУ-прототипа фиг.1),

Nc - коэффициент, характеризующий эффективность компенсации

синфазной ошибки в ДУ фиг.2.

Причем

Таким образом, при выборе R3=R11, Кi10=0,5α2Кi5=0,5 в схеме фиг.2 передача синфазного сигнала uc на выход ДУ уменьшается в Nс>>1 раз. Однако для этого необходимо, чтобы коэффициенты передачи по току токовых зеркал 5 и 6 удовлетворяли следующим условиям: Кi10=0,5 и Ki5=1. Данные теоретические выводы подтверждаются результатами моделирования коэффициента ослабления входных синфазных сигналов ДУ фиг.7:

где Ку - коэффициент усиления дифференциального сигнала uвх=uc1-uc2.

Температурная стабилизация статического режима заявляемого ДУ может быть выполнена в соответствии с патентом RU 2386205.

Особенность схемы фиг.2 - это двухканальная передача дифференциального сигнала uвх=uc1-uc2 через транзисторы 1, 2 и токовое зеркало 5, а также через транзисторы 1, 9 и токовое зеркало 10. Причем второй канал передачи uвx характеризуется широким диапазоном активной работы, близким к падению напряжения на резисторе 11, а диапазон активной работы параллельного канала на транзисторе 1, 2 - близок к ±50 мВ. Наличие в архитектуре операционных усилителей таких ДУ с широким диапазоном активной работы существенно повышает его быстродействие в режиме большого сигнала. Кроме этого параллельный канал повышает коэффициент усиления по напряжению ДУ (фиг.5).

Полученные выше выводы подтверждаются результатами моделирования предлагаемого ДУ в среде Cadance с использованием моделей SiGe интегральных транзисторов (фиг.5, фиг.6). Заявляемый ДУ имеет более высокие значения коэффициента ослабления входных синфазных сигналов (Кос.сф) при сравнительно низкоомном двухполюснике 3. Однако данная схема эффективна и при других вариантах построения цепей стабилизации статического режима.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 4264873, fig.3.

2. Патент RU 1748611.

3. Патент WO/2002/047257.

4. Патент США 7782139, fig.5.

5. Патент JP 154-10221, H03F 3/45.

6. Патентная заявка US 2006/0012432, fig.6.

7. Патент США 43664426, fig.2.

8. Патент США 4262261.

9. Патент ФРГ 2928841, fig.3.

10. Патeнт US 4433302.

11. Патент JP 54-102949/98(5)А21.

12. Патент US 7605658, fig.4.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2444117C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2011 |

|

RU2458455C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441316C1 |

| ПРЕЦИЗИОННЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2010 |

|

RU2433523C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2011 |

|

RU2449464C1 |

| ДВУХТАКТНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319289C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2283533C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2005 |

|

RU2292633C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2319288C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2446554C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, в операционных усилителях (ОУ), компараторах и т.п.) с малым напряжением питания. Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов ДУ (Кос.сф) при относительно небольшом (единицы килоом) внутреннем сопротивлении токостабилизирующего двухполюсника. Дифференциальный усилитель с малым напряжением питания содержит первый и второй входные транзисторы, дополнительный транзистор, первый и второй токостабилизирующие двухполюсники, двухполюсник нагрузки, первое и дополнительное токовые зеркала. 3 з.п. ф-лы, 6 ил.

1. Дифференциальный усилитель с малым напряжением питания, содержащий первый (1) и второй (2) входные транзисторы, эмиттеры которых объединены и через первый (3) токостабилизирующий двухполюсник связаны с первой (4) шиной источника питания, коллектор второго (2) входного транзистора соединен со входом первого (5) токового зеркала, согласованного со второй (6) шиной источника питания, выход первого (5) токового зеркала подключен к выходу (7) устройства и через двухполюсник нагрузки (8) связан с первой (4) шиной источника питания, причем коллектор первого (1) входного транзистора связан со второй (6) шиной источника питания, отличающийся тем, что объединенные эмиттеры первого (1) и второго (2) входных транзисторов соединены с базой дополнительного транзистора (9), коллектор дополнительного транзистора (9) соединен с первой (4) шиной источника питания, эмиттер дополнительного транзистора (9) связан со входом дополнительного токового зеркала (10) через второй (11) токостабилизирующий двухполюсник, а выход дополнительного токового зеркала (10) соединен с выходом (7) устройства.

2. Дифференциальный усилитель с малым напряжением питания по п.1, отличающийся тем, что первый (3) и второй (11) токостабилизирующие двухполюсники выполнены в виде резисторов с приблизительно одинаковыми сопротивлениями, причем коэффициент передачи по току первого (5) токового зеркала близок к единице, а дополнительного токового зеркала (10) - в два раза меньше.

3. Дифференциальный усилитель с малым напряжением питания по п.1, отличающийся тем, что первый (3) и второй (11) токостабилизирующие двухполюсники выполнены в виде резисторов, причем сопротивление первого (3) токостабилизирующего резистора в два раза меньше сопротивления второго (11) токостабилизирующего двухполюсника, а коэффициенты передачи по току первого (5) и дополнительного (11) токовых зеркал одинаковы.

4. Дифференциальный усилитель с малым напряжением питания по п.1, отличающийся тем, что коллектор первого (1) входного транзистора связан со второй (6) шиной источника питания через дополнительный p-n переход (12).

| US 4264873 A, 28.04.1981 | |||

| US 4284958 A, 18.08.1981 | |||

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НИЗКОВОЛЬТНЫМ ПИТАНИЕМ | 2006 |

|

RU2310268C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

Авторы

Даты

2012-02-27—Публикация

2011-02-09—Подача