Изобретение относится к вычислительной технике. Оно может быть использовано в электрически перепрограммируемом постоянном запоминающем устройстве, сохраняющем информацию при отключении источника питания и широко применяемом в вычислительной технике, автоматике, микропроцессорах.

Целью изобретения является упрощение матричного накопителя.

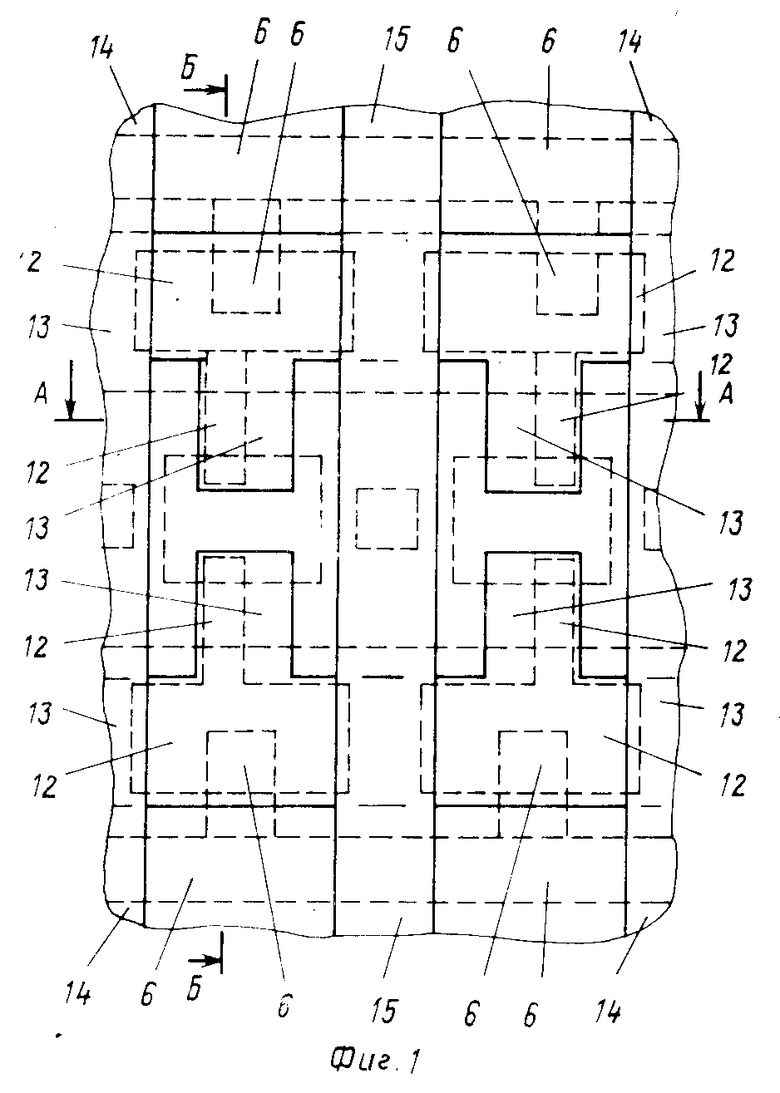

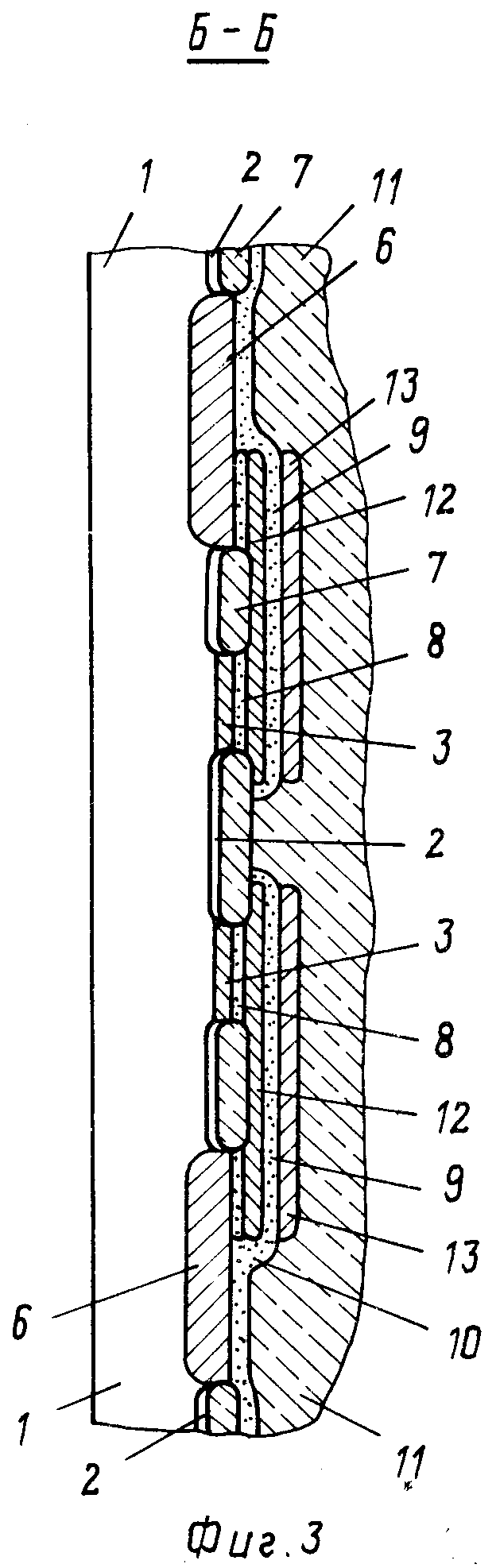

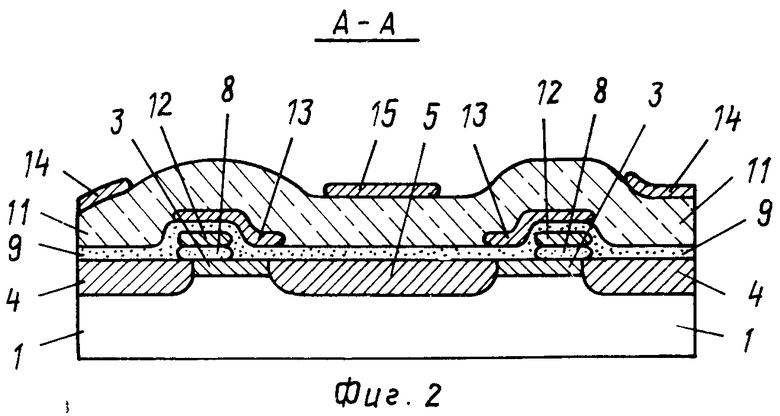

На фиг. 1 представлен матричный накопитель, вид сверху; на фиг. 2 и 3 - сечения А-А и Б-Б на фиг. 1.

Накопитель содержит полупроводниковую подложку 1 первого типа проводимости, диффузионные слои 2 и 3 первого типа проводимости, диффузионные области 4 и 5 второго типа проводимости, диффузионные шины 6 с выступами второго типа проводимости, диэлектрические слои 7-11 разной толщины, поликремниевые электроды 12, адресные поликремниевые шины 13, разрядные металлические шины 14 и 15.

В местах пересечения адресных и разрядных шин образованы ячейки памяти в виде адресного запоминающего лавинно-инжекционного транзистора с плавающим и управляющим затворами, включенные последовательно, и электрически перепрограммируемого конденсатора.

Адресная поликремниевая шина 13 является затвором адресного МДП-транзистора, управляющим затвором лавинно-инжекционного запоминающего транзистора. Поликремниевый электрод 12 является плавающим затвором запоминающего транзистора и одной из обкладок электрически перепрограммируемого конденсатора, другой обкладкой которого являются выступы диффузионной шины 6 второго типа проводимости.

Работает матричный накопитель следующим образом. В режиме считывания информации на выбранные адресную поликремниевую 13 и диффузионную 6 и разрядную металлическую 15 шины подают низкое положительное напряжение (+5 В), на остальные шины 6, 13 и 15, на одни из разрядных металлических шин 14 - нулевое напряжение. На остальные невыбранные разрядные металлические шины 14 и 15 - низкое положительное напряжение (+5 В) или их отключают.

Если пороговое напряжение выбранного запоминающего транзистора отрицательное (положительное), то через этот запоминающий транзистор и адресный МДП-транзистор, выбранную другую разрядную металлическую шину 15 протекает (не протекает) ток, что эквивалентно единичному (нулевому) состоянию запоминающего транзистора.

Через остальные запоминающие транзисторы ток не протекает из-за нулевого напряжения на адресной шине 13 (закрыт адресный МДП-транзистор) или из-за нулевой разности напряжений между разрядными металлическими шинами 14 и 15.

При строчном (общем) стирании информации на выбранную диффузионную шину 6 (или все шины 6) подают высокое импульсное положительное напряжение (например, +21 В, 10 мс), на все остальные шины 6, 13, 14 и 15 - нулевое напряжение.

Под действием этого напряжения заряд электронов инжектируется с плавающих затворов запоминающих транзисторов выбранной строки (всего матричного накопителя) и удаляется через диэлектрический слой 10 наименьшей толщины, диффузионную шину 6, в результате чего пороговые напряжения выбранных запоминающих транзисторов строки (матрицы) становятся отрицательными (-7-10 В).

Для программирования нулевого состояния выбранных запоминающих транзисторов на выбранные разрядные шины 14 подают высокое положительное импульсное напряжение ( ≈10 В, 10 мс), на выбранные адресную и диффузионную шины 13 и 6 - высокое положительное импульсное напряжение (+12-15 В, 10 мс), на выбранную другую разрядную шину 15 - нулевое напряжение, на остальные разрядные шины 14 и 15 - низкое положительное напряжение (+ 5 В), на остальные поликремниевые адресные и диффузионные шины 13 и 6 - нулевое напряжение.

Под действием этих напряжений через выбранные запоминающие транзисторы и адресные МДП-транзисторы протекает ток, за счет инжекции горячих электронов из канала выбранных запоминающих транзисторов увеличивается заряд электронов на плавающих затворах. Это приводит к увеличению пороговых напряжений (до +10 В), что эквивалентно нулевому состоянию.

Состояния остальных запоминающих транзисторов сохраняются неизменными из-за отсутствия канальной инжекции и нулевой разности потенциалов между обкладками электрически перепрограммируемых конденсаторов, отсутствия изменения заряда электронов на плавающих затворах.

Следует отметить, что при необходимости одновременного перевода всех запоминающих транзисторов в нулевое состояние на все адресные шины 13 подают высокое положительное импульсное напряжение (+25-30 В; 10 мс), на все остальные шины 6, 14 и 15 - нулевое напряжение. Под действием этих напряжений электроны инжектируются из диффузионной шины 6, туннелируют через диэлектрический слой 10 электрически перепрограммируемых конденсаторов, захватываются плавающими затворами.

Изобретение относится к вычислительной технике. Оно может быть использовано в электрически перепрограммируемом постоянном запоминающем устройстве, сохраняющем информацию при отключении источника питания. Целью изобретения является упрощение матричного накопителя. Поставленная цель достигается за счет выполнения разрядных шин 15 металлическими и размещения их на поверхности пятого диэлектрического слоя 11 и поверхности других диффузионных областей 5 второго типа проводимости с зазором относительно диффузионных шин 6 с выступами второго типа проводимости. Это позволяет исключить третий поликремниевый слой, из которого выполнены другие разрядные поликремниевые шины известного накопителя и дополнительный шестой диэлектрический слой, изолирующий поликремниевые электроды 12 от других разрядных поликремниевых шин 15. 3 ил.

| IEEE Transactions on Elektron Devices | |||

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

Авторы

Даты

1994-12-30—Публикация

1986-05-18—Подача