Изобретение относится к вычислительной технике и может быть использовано для построения средств автоматики, функциональных узлов систем управления и др.

Известны компараторы двоичных чисел (см., например, третий снизу рис. в табл.3.5 на стр.103 в кн.: Справочник по цифровой вычислительной технике. Малиновский Б.Н., Александров В.Я., Боюн В.П. и др. / Под ред. Б.Н.Малиновского. Киев: Техника, 1974 г.), содержащие элемент «Запрет» и выполняющие идентификацию признака х2>х1, где x1, х2∈{0,1} - одноразрядные двоичные числа, задаваемые двоичными сигналами.

К причине, препятствующей достижению указанного ниже технического результата при использовании известных компараторов двоичных чисел, относится ограниченные функциональные возможности, обусловленные тем, что не допускается сравнение четырехразрядных двоичных чисел, задаваемых двоичными сигналами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятый за прототип, компаратор двоичных чисел (рис.2.67 в на стр.271 в кн.: Шило В.Л. Популярные цифровые микросхемы. М.: Радио и связь, 1988 г.), который содержит два элемента «2ИЛИ», выполняет идентификацию признаков А>В, А=В, А<В, где A=a3a2a1a0 и В=b3b2b1b0 - четырехразрядные двоичные числа, задаваемые двоичными сигналами a0, ..., a3, b0, ..., b3∈{0,1}, и допускает каскадирование, при котором получается устройство сравнения двух 4n-разрядных двоичных чисел (n - количество каскадируемых компараторов).

К причине, препятствующей достижению указанного ниже технического результата при использовании прототипа, относится сложная структура, поскольку прототип имеет три входа каскадирования.

Техническим результатом изобретения является упрощение структуры за счет уменьшения количества входов каскадирования при сохранении функциональных возможностей прототипа.

Указанный технический результат при осуществлении изобретения достигается тем, что в компараторе двоичных чисел, содержащем два элемента «2ИЛИ», особенность заключается в том, что в него дополнительно введены шесть элементов «2ИЛИ», шестнадцать элементов «Запрет» и элемент «2ИЛИ-НЕ», причем все элементы сгруппированы в четыре группы так, что j-я  группа содержит два элемента «2ИЛИ» и четыре элемента «Запрет», а четвертая группа дополнительно содержит элемент «2ИЛИ-НЕ», в j-й группе выход i-го

группа содержит два элемента «2ИЛИ» и четыре элемента «Запрет», а четвертая группа дополнительно содержит элемент «2ИЛИ-НЕ», в j-й группе выход i-го  элемента «Запрет», подключенного инвертирующим входом к неинвертирующему входу (3-i)-го элемента «Запрет», и выход i-го элемента «2ИЛИ», подключенного вторым входом к инвертирующему входу (5-i)-го элемента «Запрет», соединены соответственно с первым входом i-го элемента «2ИЛИ» и неинвертирующим входом (2+i)-го элемента «Запрет», в четвертой группе первый и второй входы элемента «2ИЛИ-НЕ» подключены соответственно к выходам третьего и четвертого элементов «Запрет», выход (2+i)-го элемента «Запрет» предыдущей группы соединен с вторым входом i-го элемента «2ИЛИ» последующей группы, а второй вход i-го элемента «2ИЛИ» первой группы и выход (2+i)-го элемента «Запрет» четвертой группы являются соответственно i-ым входом каскадирования и i-ым выходом компаратора двоичных чисел, j-й, (4+j)-й информационные входы и третий выход которого образованы соответственно неинвертирующими входами первого, второго элементов «Запрет» j-й группы и выходом элемента «2ИЛИ-НЕ».

элемента «Запрет», подключенного инвертирующим входом к неинвертирующему входу (3-i)-го элемента «Запрет», и выход i-го элемента «2ИЛИ», подключенного вторым входом к инвертирующему входу (5-i)-го элемента «Запрет», соединены соответственно с первым входом i-го элемента «2ИЛИ» и неинвертирующим входом (2+i)-го элемента «Запрет», в четвертой группе первый и второй входы элемента «2ИЛИ-НЕ» подключены соответственно к выходам третьего и четвертого элементов «Запрет», выход (2+i)-го элемента «Запрет» предыдущей группы соединен с вторым входом i-го элемента «2ИЛИ» последующей группы, а второй вход i-го элемента «2ИЛИ» первой группы и выход (2+i)-го элемента «Запрет» четвертой группы являются соответственно i-ым входом каскадирования и i-ым выходом компаратора двоичных чисел, j-й, (4+j)-й информационные входы и третий выход которого образованы соответственно неинвертирующими входами первого, второго элементов «Запрет» j-й группы и выходом элемента «2ИЛИ-НЕ».

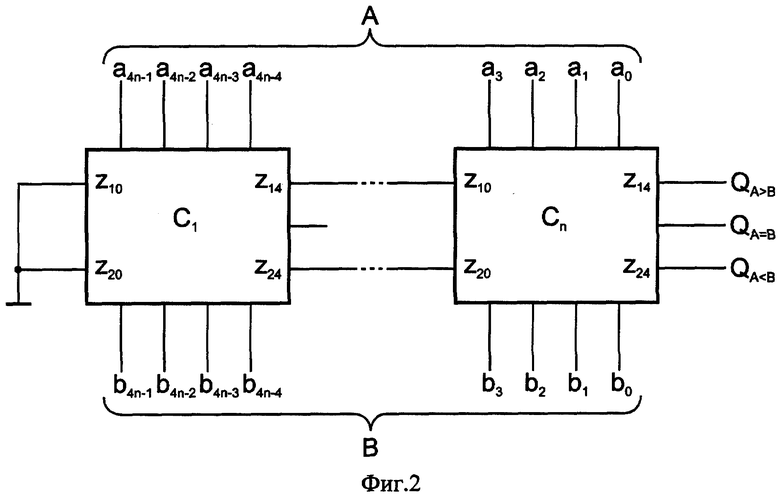

На фиг.1 и фиг.2 представлены соответственно схема предлагаемого компаратора двоичных чисел и схема его каскадирования.

Компаратор двоичных чисел содержит шестнадцать элементов «Запрет» 111, ..., 144, восемь элементов «2ИЛИ» 211, ..., 224, элемент «2ИЛИ-НЕ» 3, причем все элементы сгруппированы в четыре группы так, что j-я  группа содержит элементы 11j, 12j, 13j, 14j, 21j, 22j, а четвертая группа дополнительно содержит элемент 3, выход элемента 1ij

группа содержит элементы 11j, 12j, 13j, 14j, 21j, 22j, а четвертая группа дополнительно содержит элемент 3, выход элемента 1ij , подключенного инвертирующим входом к неинвертирующему входу элемента 1(3-i)j, и выход элемента 2ij, подключенного вторым входом к инвертирующему входу элемента 1(5-i)j, соединены соответственно с первым входом элемента 2ij и неинвертирующим входом элемента 1(2+i)j, первый и второй входы элемента 3 подключены соответственно к выходам элементов 134 и 144, выход элемента 1(2+i)k

, подключенного инвертирующим входом к неинвертирующему входу элемента 1(3-i)j, и выход элемента 2ij, подключенного вторым входом к инвертирующему входу элемента 1(5-i)j, соединены соответственно с первым входом элемента 2ij и неинвертирующим входом элемента 1(2+i)j, первый и второй входы элемента 3 подключены соответственно к выходам элементов 134 и 144, выход элемента 1(2+i)k соединен с вторым входом элемента 2i(k+1), а второй вход элемента 2i1 и выход элемента 1(2+i)4 являются соответственно i-ым входом каскадирования и i-ым выходом компаратора двоичных чисел, j-й, (4+j)-й информационные входы и третий выход которого образованы соответственно неинвертирующими входами элементов 11j, 12j и выходом элемента 3.

соединен с вторым входом элемента 2i(k+1), а второй вход элемента 2i1 и выход элемента 1(2+i)4 являются соответственно i-ым входом каскадирования и i-ым выходом компаратора двоичных чисел, j-й, (4+j)-й информационные входы и третий выход которого образованы соответственно неинвертирующими входами элементов 11j, 12j и выходом элемента 3.

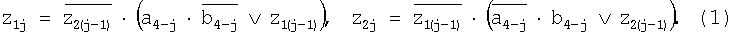

Работа предлагаемого компаратора двоичных чисел осуществляется следующим образом. На его первый, ..., четвертый и пятый, ..., восьмой информационные входы подаются соответственно произвольные двоичные сигналы a3, ..., a0∈{0,1} и b3, ..., b0∈{0,l}, которые задают подлежащие сравнению четырехразрядные двоичные числа А=а3а2а1а0 и В=b3b2b1b0 (а3, b3 и a0, b0 определяют значения старших и младших разрядов соответственно). Тогда сигналы на выходах элементов 13j, 14j будут определяться выражениями

будут определяться выражениями

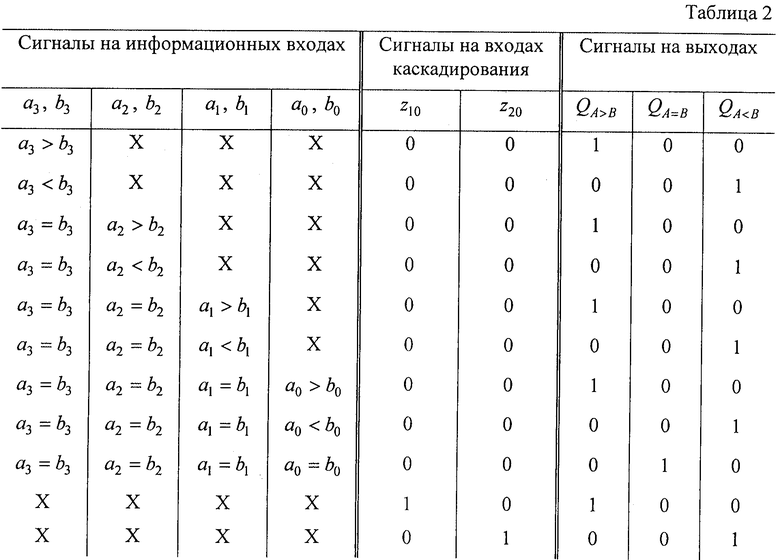

В табл.1 приведены значения реализуемых выражениями (1) функций на всех возможных наборах значений их аргументов. Анализ данных, приведенных в табл.1, позволяет заключить, что: 1) если z1(j-1)=z2(j-1)=0 и a4-j=b4-j, то z1j=z2j=0; 2) если z1(j-1)=z2(j-1)=0 и a4-j>b4-j (z1(j-1)=z2(j-1)=0 и а4-j<b4-j), то z1j=1 и z2j=0 (z1j=0 и z2j=1); 3) если z1(j-1)=1 и z2(j-1)=0 (z1(j-1)=0 и z2(j-1)=1), то z1j=1 и z2j=0 (z1j=0 и z2j=1). Таким образом, состояния предлагаемого компаратора будут характеризоваться табл.2, в которой символом Х обозначено произвольное отношение порядка.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемый компаратор двоичных чисел выполняет идентификацию признаков А>В, А=В, А<В, где А=а3а2а1а0 и B=b3b2b1b0 - четырехразрядные двоичные числа, задаваемые двоичными сигналами a0, ..., a3, b0, ..., b3∈{0,1}, допускает каскадирование (фиг.2), при котором получается устройство сравнения двух 4n-разрядных двоичных чисел (n - количество каскадируемых компараторов С), и обладает более простой по сравнению с прототипом структурой, так как имеет только два входа каскадирования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СЕЛЕКТОР ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2365975C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2007 |

|

RU2353966C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363038C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2005 |

|

RU2298220C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2017 |

|

RU2675301C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363036C1 |

| УСТРОЙСТВО СЕЛЕКЦИИ ДВОИЧНЫХ ЧИСЕЛ | 2018 |

|

RU2703352C1 |

| СЕЛЕКТОР ДВОИЧНЫХ ЧИСЕЛ | 2015 |

|

RU2606311C2 |

| УСТРОЙСТВО СЕЛЕКЦИИ БОЛЬШЕГО ИЗ ДВУХ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363034C1 |

| УСТРОЙСТВО СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ | 2008 |

|

RU2363035C1 |

Изобретение относится к вычислительной технике для построения средств автоматики, функциональных узлов систем управления и др. Технический результат заключается в упрощении структуры за счет уменьшения количества входов каскадирования при сохранении функциональных возможностей прототипа. В компаратор двоичных чисел (фиг.1), содержащий два элемента «2ИЛИ» (2), введены шесть элементов «2ИЛИ» (2ij), шестнадцать элементов «Запрет» (1ij), где  ,

,  и элемент «2ИЛИ-НЕ» (3), причем все элементы сгруппированы в четыре группы так, что j-я

и элемент «2ИЛИ-НЕ» (3), причем все элементы сгруппированы в четыре группы так, что j-я  группа содержит два элемента «2ИЛИ» (2ij) и четыре элемента «Запрет» (1ij), а четвертая группа дополнительно содержит элемент «2ИЛИ-НЕ» (3). 2 ил., 2 табл.

группа содержит два элемента «2ИЛИ» (2ij) и четыре элемента «Запрет» (1ij), а четвертая группа дополнительно содержит элемент «2ИЛИ-НЕ» (3). 2 ил., 2 табл.

Компаратор двоичных чисел, содержащий два элемента «2ИЛИ», отличающийся тем, что в него дополнительно введены шесть элементов «2ИЛИ», шестнадцать элементов «Запрет» и элемент «2ИЛИ-НЕ», причем все элементы сгруппированы в четыре группы так, что j-я  группа содержит два элемента «2ИЛИ» и четыре элемента «Запрет», а четвертая группа дополнительно содержит элемент «2ИЛИ-НЕ», в j-й группе выход i-го

группа содержит два элемента «2ИЛИ» и четыре элемента «Запрет», а четвертая группа дополнительно содержит элемент «2ИЛИ-НЕ», в j-й группе выход i-го  элемента «Запрет», подключенного инвертирующим входом к неинвертирующему входу (3-i)-го элемента «Запрет», и выход i-го элемента «2ИЛИ», подключенного вторым входом к инвертирующему входу (5-i)-го элемента «Запрет», соединены соответственно с первым входом i-го элемента «2ИЛИ» и неинвертирующим входом (2+i)-го элемента «Запрет», в четвертой группе первый и второй входы элемента «2ИЛИ-НЕ» подключены соответственно к выходам третьего и четвертого элементов «Запрет», выход (2+i)-го элемента «Запрет» предыдущей группы соединен с вторым входом i-го элемента «2ИЛИ» последующей группы, а второй вход i-го элемента «2ИЛИ» первой группы и выход (2+i)-го элемента «Запрет» четвертой группы являются соответственно i-м входом каскадирования и i-м выходом компаратора двоичных чисел, j-й, (4+j)-й информационные входы и третий выход которого образованы соответственно неинвертирующими входами первого, второго элементов «Запрет» j-й группы и выходом элемента «2ИЛИ-НЕ».

элемента «Запрет», подключенного инвертирующим входом к неинвертирующему входу (3-i)-го элемента «Запрет», и выход i-го элемента «2ИЛИ», подключенного вторым входом к инвертирующему входу (5-i)-го элемента «Запрет», соединены соответственно с первым входом i-го элемента «2ИЛИ» и неинвертирующим входом (2+i)-го элемента «Запрет», в четвертой группе первый и второй входы элемента «2ИЛИ-НЕ» подключены соответственно к выходам третьего и четвертого элементов «Запрет», выход (2+i)-го элемента «Запрет» предыдущей группы соединен с вторым входом i-го элемента «2ИЛИ» последующей группы, а второй вход i-го элемента «2ИЛИ» первой группы и выход (2+i)-го элемента «Запрет» четвертой группы являются соответственно i-м входом каскадирования и i-м выходом компаратора двоичных чисел, j-й, (4+j)-й информационные входы и третий выход которого образованы соответственно неинвертирующими входами первого, второго элементов «Запрет» j-й группы и выходом элемента «2ИЛИ-НЕ».

| ШИЛО В.Л | |||

| Популярные цифровые микросхемы, Москва, Радио и связь, 1988, с.271, рис.2.67 | |||

| СУММАТОР-ВЫЧИТАТЕЛЬ СТАРШИМИ РАЗРЯДАМИ ВПЕРЕД НА НЕЙРОНАХ | 2002 |

|

RU2205444C1 |

| DE 4403401 A1, 11.08.1994 | |||

| US 5742224 A, 21.04.1998 | |||

| Способ лечения гемангиом | 1982 |

|

SU1079241A1 |

Авторы

Даты

2007-05-27—Публикация

2005-12-23—Подача