Выход

О

to

СО СО СО Ю

Изобретение относится к вычислительной технике и технике связи и может использоваться при проектировании и создании цифровых систем связи.

Цель изобретения - повышение помехоустойчивости при одновременном повышении скорости передачи.

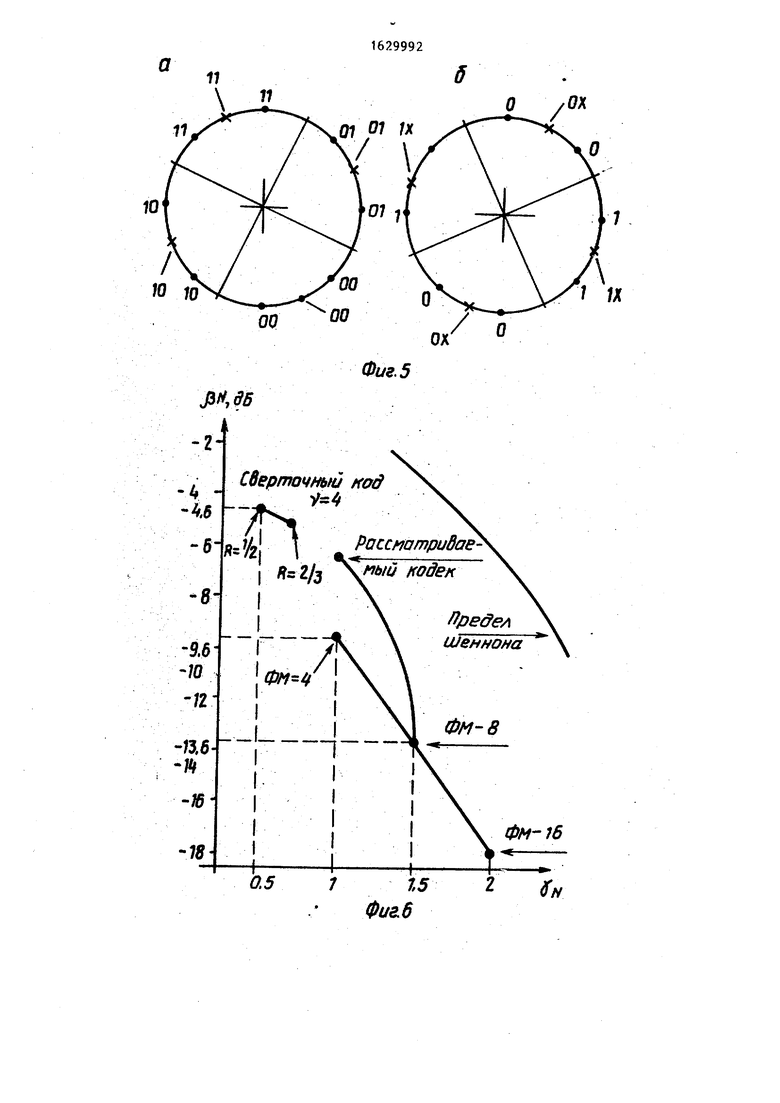

На фиг. 1 приведена блок-схема кодека; на фиг. 2 - схема выполнения передающей стороны в случае трехкратной фазовой модуляции (ФМ); на фиг.3 - решетчатая диаграмма сверточного кода на фиг. 4 - векторы сигналов трехкратной фазовой модуляции; на фиг. 5 - схема объединения принятых сигналов в группы; на фиг. 6 - сравнительные результаты различных систем связи; на фиг. 7 - векторы сигналов четырехкратной фазовой модуляции; на фиг.8 схема.объединения принимаемых сигналов в группы.

кодек включает в себя передающую сторону 1, приемную сторону 2 и канал 3 связи. Передающая сторона 1 содер- жит кодер 4 сверточного кода, первый и второй регистры 5,6 сдвига, буферный регистр 7, модулятор 8 сигналов ФМ и блок 9 тактовой синхронизации. Приемная сторона 2 содержит демоду- лятор 10 сигналов ФМ, блоки 11 вычисления среднеарифметических сигналов, декодер 12 сверточного кода, блок 13 тактовой синхронизации и блок 14 ветпевой синхронизации.

Блоки 11 вычисления среднеарифметических проекций сигналов могут быть реализованы на источнике 15 опорных сигналов, первом и втором вычитате- лях 16,17, первом и втором квадрато- pax 18,19, сумматоре 20 и вычислителе 21 корня.

Кодер 4 сверточного кода состоит (фиг. 2) из регистра 22 сдвига и сумматоров 23,24 по модулю два, соединенных в соответствии с генераторными полиномами сверточного кода. На фиг. 2 , представлено также подключение выходов регистров 5,6 сдвига к буферному регистру 7 для случая, когда число генераторных полиномов , а число дополнительных сдвигов . При этом кратность фазовой модуляции равна ., т.е. модулятор 3 сигналов ФМ реализует различных фаз в передаваемом сигнале (обозначается ФМ-8).

Работа кодера 4 описывается решетчатой диаграммой (фиг. 3), которая представляет собой набор всех состоя

5

5

0

ний кодера 4, соединенных переходами (ветвями)„ Каждый переход помечен кодируемыми символами (кодовыми ветвями), генерируемыми на данном переходе. На фиг. 3 обозначены также состояния выходов регистров 5,6 сдвига (фиг. 2).

На фиг. 4 показаны векторы сигналов трехкратной ФМ (ФМ-8), расположенных согласно манипуляционному коду Грея. Демодулятор 10 производит когерентное детектирование принимаемых фазомодулированных сигналов и определение проекций суммы принимаемого сигнала и помехи на взаимноортогональные опорные колебания. Формируемые на выходах демодулятора 10 синфазный и квадратурный (сдвинутый на 90°) сигналы подаются в блоки 13 и 14, где выделяются сигналы соответственно тактовой, и ветвевой синхронизации. Блок 14 обеспечивает указание неоднозначности фазы опорного колебания демодулятора 10 и разделения потока принимаемых символов на кодовые ветви. I

Кроме того, сигналы с демодулятора 10 подаются в блоки 11, принцип построения и функционирования которых основан на следующем вновь разработанном алгоритме.

Для декодирования в соответствии с алгоритмом Витерби на каждом шаге декодирования необходимо вычислять метрики ветвей, т.е. расстояния принимаемой суммы сигнала и помехи до групп символов, соответствующих ветвям решетчатой диаграммы. На первом шаге решетчатой диаграммы необходимо вычислить метрики ветви , на втором шаге - метрики ветви (фиг. 3). Поскольку ветви сверточного кода а объединяются на передаче и передаются одним сигналом трехкратной фазовой модуляции, при декодировании все сигнальные векторы объединяются в группы с одинаковыми символами а,аЈ (фиг. 5а) и группы с одинаковым символом а. (фиг. 56) , находящиеся в соответствующих секторах. Поскольку символы в группах передаются равновероятно, в целях упрощения декодирования вычисляют расстояние не до каждого конкретного сигнала в группе, а до опорного сигнала, находящегося на оси симметрии каждого из секторов. Ортогональные проекции опорных сигналов определяются как среднее арифметическое соответствую5 . 162 щих проекций сигналов, входящих в данную группу.

Таким образом, на первом шаге решетчатой диаграммы, содержащем символы , метрики вычисляют, как расстояния от принятого сигнала, заданного проекциями (у,х), до четырех опорных сигналов MOO, M01, М10 и М11, также заданных своими проекциями (Уоо х00), (уд, , х0)), (yw , х10) и (у ц , х)( ). На Лиг. 5а опорные сигналы отмечены крестиками. На втором шаге решетчатой диаграммы, содержащем символ а , метрики вычисляют, как расстояния до опорных сигналов, отмеченных крестиком на Лиг. 56.

Блок 11, обеспечивающий вычисление метрик ветвей сверточного кода, работающий по рассмотренного способу вы- числений, может быть реализован различными аппаратурными средствами.

Например, на фиг. 1 приведена подробная структурная схема блока 11, использующего принцип вычисления по формуле. Согласно этому способу вычисления необходимо рассчитать метрики ветвей 00, 01, 10 и 11 для шага решетчатой диаграммы, содержащего кодированные символы a,at, и метрики ветвей 0 и 1 для шага решетчатой диаграммы, содержащего символ а . Для расчета расстояний между принятым из канала сигнальным вектором, заданным своими проекциями (у, х) на ортогональные оси, и опорными сигналами, также заданными своими проекциями (уоп , хОГ| ) используется выражение

(у-Уоп)г-|- х-х0п)2.

Для рассматриваемого примера коди- роцания и канале с ЬМ-3 необходимо рассчитать шесть метрик ветвей (расстояний) - г00 , г0(, г10, г ,, для первого шага решетчатой диаграммы и г0 , г для второго шага. Поэтому приемная сторона 2 содержит шесть блоков 11. На первые входы вычита- телей 16,17 с выходов демодулятора 10 поступают ортогональные проекции (у,х) принятого сигнала. На вторые входы вычитателей 16,17 с выходов источника 15 опорных сигналов поступают ортогональные проекции Cy0h,xon) COOT- ветствующего опорного сигнала, за- данные в виде чисел. На выход блока 11 поступает расстояние г от принятого сигнала до соответствующего опорно

- .« -

0

5 Q

5

0

5 0 5 |

го, которое используется в декодере 12 в качестве метрик ветвей.

Поскольку вычисление метрик ветвей по формуле достаточно сложно, для упрощения реализации блока 11 можно использовать табличный способ вычислений метрик. При этом используется то же выражение для расчета расстояний г между принятым сигналом и опорными сигналами. Однако метрики ветвей 00, 01, 10, 11 и 01, предварительно рассчитанные, записаны в постоянное запоминающее устройство (ПЗУ).

Устройство вычитания метрик ветвей состоит из шести постоянных запоминающих устройств; на адресные входы которых с выходов демодулятора 10 поступают проекции (у,х) принятого сигнального вектора, причем по адресу, определенному значениями (у,х) проекций, записаны расстояния от принятого сигнального вектора до опорных сигналов, определенных в первых 2П блоках 17 как среднее арифметическое соответствующих проекций 2mсигналов, кодовые комбинации которых определяют как значения первых кодированных символов, а также все возможные значения остальных символов, а в последующих 2 блоках 11 - как среднее арифметическое соответствующих проекций 2№, 2ти,..., 2 сигналов, кодовые комбинации которых определяют как значения га-го кодированного символа, так и все возмож- ные значения остальных кодированных символов. Декодер 12 сверточного кода реализует алгоритм Витерби.

Кодер работает следующим образом.

Непрерывная последовательность информационных символов поступает на вход сверточного кодера 4. При выбранных параметрах и кодирование производят, сдвигая информацию в кодере 4 на один такт и определяя символы а, и а. на первом и втором выходах, затем вновь сдвигая информацию на один такт и определяя один кодированный символ а у на выходе первого кодового генератора. Ла передающей стороне 1 такое преобразование символов реализовано путем использования двухразрядных регистров 5,6 сдвига и трехразрядного буферного регистра 7. Сигналы с кодера 4 поступают на входы регистров 5,6 тактируемых синхронно с регистром 22 кодера 4 сверточного кода. Через два такта в первом регистре 5 содержатся

кодированные символы первого кодовоҐ +-+1

го генератора а и а , во втором регистре 6 кодированные символы второго кодового генератора а и а . Один раз за два такта происходит перезапись трех кодированных символов a, и а Ј в буферный регистр 7. Четвертый символ в канал 3 не

передают. Таким образом, на два информационных символа на входе кодера 4 получают три кодированных символа на его выходе, скорость кода повышает12

ся от. до величины . Из решетчатой диаграммы такого кодера (фиг.З) видно, что на каждом шаге декодирования в каждый узел диаграммы входят только две ветви, что значительно упрощает декодирование по сравнению со стандартной диаграммой кода со скоростью 2/3, где в каждый узел входят по четыре ветйи.,

Три кодированных символа а( с выходов регистра 7 поступают на входы модулятора 8 сигналов трехкратной фазовой модуляции. После передачи сигналов по каналу 3 и демодуляции в демодуляторе 10 с помощью блоков 11 осуществляют вычисление мет- рик ветвей, которые используются затем в декодере 12 свер очного кода.

Эффективность различных систем передачи информации (в том числе и с использованием помехоустойчивого кодирования) принято сравнивать при помощи диаграммы частотной и энергетической эффективности (фиг. 6).

Под эффективностью системы связи в общем случае понимают степень ис- пользования основных ресурсов, отводимых для передачи сообщений. Такими ресурсами являются отношение энергии сигнала к односторонней спектральной плотности белого шума (Ес/М0) и полоса частот канала (F). Поэтому эффективность систем передачи информации принято оценивать коэффициентами энергетической (R) и частотной эффективности (У)

,R

ЕС/N0

R F где R - скорость передачи сообщений

I

по каналу.

Поскольку полоса частот, занимаемых сигналом, не всегда определяется

Р

О F

0

5

5 Q

„ с

5

Р

р,

.однозначно, то целесообразно перейти к нормированным значениям

N E JV

у. R

dN TN

где N - число независимых отсчетов сигнала в единицу времени. Различные системы связи отображаются в виде точек на -диаграмме- Например , наиболее широко используемой в настоящее время двукратной четырех- фазной фазовой модуляции (ФМ-4) соответствует точка с координатами щ -9,6 дБ;

ЦЧ-1 -10 ).

V id

Зм -1Относительно этой точки проводят сравнение систем связи с многопозиционными сигналами и помехоустойчивым сверточным кодированием.

Применение многократной фазовой модуляции позволяет получить более высокую удельную скорость передачи за счет снижения энергетической эффективности системы. Например, системе связи с трехкратной (восьмифазной) фазовой модуляцией (ФМ-8) соответствует точка с координатами ,6 дБ; (Рл 1 -10-).

J-H-1.5.

Таким образом, перевод от двукратной к трехкратной фазовой модуляции увеличивает скорость передачи информации в 1,5 раза без расширения полосы частот. Энергетическая эффективность снижается на 4 дБ, поскольку увеличение кратности модуляции или числа фаз сигнала уменьшает различимость соседних позиций сигнала.

Применение помехоустойчивого кодирования позволяет повысить энергетическую эффективность системы связи за счет снижения удельной скорости передачи (расширения полосы занимаемых частот). Например, системе связи с помехоустойчивым сверточным кодированием и декодированием по алгоритму Витерби соответствуют точки с координатами :

для сверточного кода со скоростью и длиной кодового ограничения ,6 дБ;

1().

,

для сверточного кода со скоростью и длиной кодового ограничения

дБ;

1(Рл 1 -1(Г).

,666, 6

Испытания рассматриваемого кодека показали, что его энергетический выигрыш по сравнению с некодированной двукратной ФМ составляет 3 дБ. Обе системы связи имеют одинаковую удельную скорость передачи t ц 1. Таким

образом, разработанная система отобрашении скорости передачи, на передающей стороне введены первый и второй регистры сдвига и буферный регистр, тактовые входы регистров сдвига объединены и подключены к первому выходу блока тактовой синхронизации, второй выход которого соединен с тактовыми входами буАерного регистра, и модулятор сигналов фазовой модуляции, первый и второй выходы кодера сверточного кода подключены к информационным входам соответственно первого и второго регистров сдвига, выходы пер10

жается на Ау -диаграмме точкой с коор-,. вого - n-го разрядов первого регистра

20

динатами

,6 дБ;

().

Г 1Использование рассматриваемого алгоритма кодирования со скоростью (, ) и сигналов четырехкратной фазовой модуляции позвопяет повысить удельную скорость передачи в 1,5 раз по сравнению с некодирован-25 ной двукратной фазовой модуляцией в той же полосе частот канала. Сигналы четырехкратной ФМ показаны на фиг.7, а объединение сигналов в группы и опорные сигналы в группах приведены -jo на фиг. 8. Формула изобретения

1. Кодек для системы связи с многократной фазовой модуляцией, содержаний на передающей стороне кодер сверточного кода, информационный вход ко- торого объединен с входом блока тактовой синхронизации и является входом кодека, первый выход блока тактовой синхронизации соединен с тактовым входом кодера сверточного кода, модулятор сигналов фазовой модуляции, выход которого подключен к входу канала связи, на приемной стороне - демодулятор сигналов фазовой модуля40

45

сдвига (п - число генераторных полиномов сверточного кода) и выходы (п-тп+ - t )-го-п-го разрядов второго регистра сдвига (тч - чиспо дополнительных символов в кодовом слове сверточного кода, ) соединены с соответствующими информационными входами буферного регистра, выходы которого подключены соответственно к первому - (п+т)-му информационным входам модулятора сигналов фазовой модуляции, на приемной стороне введены первый - (2П+2т)-й блоки вычисления срепнеквадратических проекций сигналов, синЛазный и квадратурный выходы демодулятора сигналов фазовой модуляции подключены соответственно к первым и вторым входам блока тактовой синхронизации, блока ветвевой синхронизации и всех блоков вычисления среднеарифметических проекций сигналов, выходы которых соединены с соответствующими информационными входами детектора сверточного кода.

2. Кодек по п. 1, отличающий с я тем, что блок вычисления среднеарифметических проекций сигналов содержит первый и второй квадраторы, сумматор, вычислитель корня, источник опорных сигналов и первый и второй вычитатели, первые входы которых являются соответственно первым и вторым входами блока, первый и второй выходы источника опорных сигналов соединены с вторыми входами соответственно первого и второго вычитате- лей, выходы которых через одноименные квадраторы подключены к входам сумматора, выход которого соединен с входом вычислителя корня, выход которого является выходом блока.

ции, вход которого подключен к выходу канала связи, - блок тактовой синхронизации и блок ветвевой синхронизации, выходы которых соединены соответственно с тактовым входом и входом синхронизации декодера сверточного кода, выход которого является выходом кодека, отличающийся тем, что, с целью повышения помехоустойчивости при одновременном повы5

9942Ю

шении скорости передачи, на передающей стороне введены первый и второй регистры сдвига и буферный регистр, тактовые входы регистров сдвига объединены и подключены к первому выходу блока тактовой синхронизации, второй выход которого соединен с тактовыми входами буАерного регистра, и модулятор сигналов фазовой модуляции, первый и второй выходы кодера сверточного кода подключены к информационным входам соответственно первого и второго регистров сдвига, выходы пер10

вого - n-го разрядов первого регистра

сдвига (п - число генераторных полиномов сверточного кода) и выходы (п-тп+ - t )-го-п-го разрядов второго регистра сдвига (тч - чиспо дополнительных символов в кодовом слове сверточного кода, ) соединены с соответствующими информационными входами буферного регистра, выходы которого подключены соответственно к первому - (п+т)-му информационным входам модулятора сигналов фазовой модуляции, на приемной стороне введены первый - (2П+2т)-й блоки вычисления срепнеквадратических проекций сигналов, синЛазный и квадратурный выходы демодулятора сигналов фазовой модуляции подключены соответственно к первым и вторым входам блока тактовой синхронизации, блока ветвевой синхронизации и всех блоков вычисления среднеарифметических проекций сигналов, выходы которых соединены с соответствующими информационными входами детектора сверточного кода.

2. Кодек по п. 1, отличающий с я тем, что блок вычисления среднеарифметических проекций сигналов содержит первый и второй квадраторы, сумматор, вычислитель корня, источник опорных сигналов и первый и второй вычитатели, первые входы которых являются соответственно первым и вторым входами блока, первый и второй выходы источника опорных сигналов соединены с вторыми входами соответственно первого и второго вычитате- лей, выходы которых через одноименные квадраторы подключены к входам сумматора, выход которого соединен с входом вычислителя корня, выход которого является выходом блока.

ЖЯЭ

-С ;

4-Fr

о

of

I

tt

Ч

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ ПРИЕМНО-ДЕМОДУЛИРУЮЩЕЕ УСТРОЙСТВО ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ СИСТЕМ СВЯЗИ | 2005 |

|

RU2305375C2 |

| Система передачи информации перфорированным сверточным кодом с восьмифазной модуляцией | 1990 |

|

SU1795499A1 |

| Устройство для декодирования сверточного кода | 1989 |

|

SU1612378A1 |

| Устройство для декодирования сверточного кода | 1991 |

|

SU1839281A1 |

| Кодек двоичных блочных кодов | 1986 |

|

SU1408532A1 |

| Кодек блочной сигнально-кодовой конструкции | 1989 |

|

SU1711337A1 |

| Выходное устройство декодера Витерби | 1990 |

|

SU1775858A1 |

| УСТРОЙСТВО ДЛЯ РАСПОЗНАВАНИЯ ВИДОВ ПЕРЕДАЧ | 1995 |

|

RU2099786C1 |

| УСТРОЙСТВО ВЫЧИСЛЕНИЯ МЕТРИК ПУТЕЙ ДЕКОДЕРА ВИТЕРБИ | 1990 |

|

RU2022473C1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

Изобретение относится к вычислительной технике и технике связи. Его использование в цифровых системах связи позволяет повысить помехоустойчивость и одновременно скорость передачи . Кодек состоит из передающей стороны 1, содержащей кодер 4 сверточно- го кода, модулятор 8 сигналов фазовой модуляции и блок 9 тактовой синхронизации, из канала 3 связи и приемной стороны 2, содержащей демодулятор 10 сигналов фазовой модуляции, декодер 12 сверточного кода, блок 13 тактовой синхронизации и блок 14 ветвевой синхронизации. Цель изобретения достигается благодаря введению на передающей стороне 1 регистров 5, 6 сдвига и буферного регистра 7, а на приемной стороне 2 - блоков 11 вычисления среднеарифметических проекций сигналов. 1 з.п. Ъ-лы. 8 ил. S IE

в,Ч

00

777

700

Фие.1

00

Фиг. З

ш

ю ю

00

МЫ

-zOX

Фиг. 5

Фигб

looowoo0001

Фиг. 7

to

to QO °°

1ЮО

0100

о о о

Фиг. 8

| Способ кодирования и декодированияСВЕРТОчНОгО КОдА | 1978 |

|

SU809634A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Устройство для передачи и приема дискретной информации | 1987 |

|

SU1443178A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Зарубежная радиоэлектроника, 1981, № 3, с | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кларк Дж., Кейн Дж | |||

| Кодирование с исправлением ошибок в системах цифровой связи | |||

| - М.: Радио и связь, 1987, с | |||

| Машина для удаления камней из почвы | 1922 |

|

SU231A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-02-23—Публикация

1987-12-14—Подача