Изобретение относится к радиотехнике и может использоваться в радиолокации, в частности в системах автоматического измерения угловых координат цели (угла места, азимута) [1, 2], где необходимо выделение пачки импульсных сигналов из аддитивной смеси сигналов и шума в условиях возможного «замирания» сигналов, вызванных попаданием в минимумы диаграммы обратного рассеяния цели.

Известен обнаружитель пачки двоично-квантованных сигналов по авт. св. №640219 [3], содержащий определенным способом соединенные регистр сдвига на N1 разрядов, дешифратор, реверсивный счетчик, регистр сдвига на N0 разрядов, первый и второй элемент ИЛИ, контрольный счетчик, блок переключении, блок управления, дополнительный элемент НЕ, а также идентичные первый и второй формирователи сигналов сложения и вычитания, каждый из который состоит из двух элементов НЕ и двух элементов И.

На вход обнаружителя пачки двоично-квантованных сигналов поступает детерминированный поток прямоугольных импульсов S(K), где К - номер интервала длительностью Т. Обнаружитель работает в скользящем режиме и на каждом шаге, задаваемом первыми тактовыми импульсами, вычисляет сумму числа единиц в интервале N1T и числа нулей в предшествующем ему интервале N0T, сравнивает ее с пороговым числом, при превышении которого формируется решение об обнаружении пачки.

Однако данный обнаружитель характеризуется рядом недостатков: обнаруживая сам факт наличия сигналов, устройство не способно точно измерить время начала и конца пачки сигналов и, соответственно, точно измерить угловые координаты цели, устройство работоспособно только с пачками бинарно-квантованных сигналов, тогда как в радиолокационных измерениях угловых координат цели, как правило, отраженные от цели эхо-сигналы необходимо обнаружить на фоне шумов. При этом их амплитуда значительно флюктуирует в связи с попаданием в максимум или минимум диаграммы обратного рассеяния цели, что также значительно снижает точность измерения угловых координат цели.

Известно устройство обнаружения сигнала по авт. св. №640220 [4], содержащее определенным способом соединенные бинарный преобразователь, пороговое устройство, схему запуска, формирователь поисковых стробов, формирователь опережающих стробов, формирователь запаздывающих стробов, первый и второй временные селекторы, счетчик периодов, первый и второй счетчики превышений, решающую схему, формирователь сброса, первую и вторую схему И.

Однако данное устройство характеризуется некоторыми недостатками: при флюктуациях амплитуды отраженного от цели сигнала в связи с попаданием в максимум или минимум диаграммы обратного рассеяния может наблюдаться явление «замирания» сигналов. В результате пачка сигналов, поступающих на устройство, может характеризоваться пропаданием сигналов. В этом случае описываемое устройство не способно определить начало и конец пачки и, соответственно, измерить угловые координаты цели с необходимой точностью.

Наиболее близким по технической сущности к заявляемому является последовательный обнаружитель по авт. св. №540230 [5], являющийся прототипом.

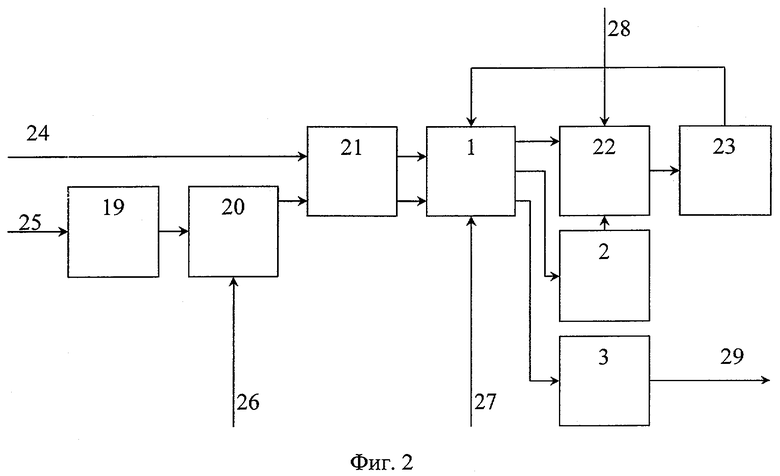

Последовательный обнаружитель включает:

1 - Реверсивный счетчик;

2 - Блок сравнения с верхним порогом;

3 - Первый блок сравнения с нижним порогом (при поиске);

4 - Делитель частоты;

5 - Первый элемент ИЛИ;

6 - Вентиль;

7 - Второй блок сравнения с нижним порогом (при контроле);

8 - Первый элемент И;

9 - Второй элемент ИЛИ;

10 - Третий элемент ИЛИ;

11 - Триггер;

12 - Второй элемент И;

13 - Вход анализируемой последовательности импульсов;

14 - Вход контрольной шумовой последовательности импульсов;

15 - Вход вспомогательной последовательности импульсов;

16 - Вход запуска;

17 - Выход индикации состояния «поиск» и «контроль»;

18 - Выход последовательного обнаружителя.

Последовательный обнаружитель содержит делитель частоты 4 и реверсивный счетчик 1, первый выход которого соединен с блоком сравнения 2 с верхним порогом, а второй выход соединен с первым блоком сравнения 3 с нижним порогом (при поиске), между выходом блока сравнения с верхним порогом 2 и первым входом, являющимся входом сложения реверсивного счетчика 1, включен вентиль 6, между выходом делителя частоты 4 и вторым входом, являющимся входом вычитания реверсивного счетчика 1, включен первый элемент ИЛИ 5. Третий выход реверсивного счетчика 1 соединен с последовательно включенными вторым блоком сравнения 7 с нижним порогом (при контроле), первым элементом И 8, вторым и третьим элементами ИЛИ 9, 10 и триггером 11, второй вход которого соединен с выходом блока сравнения 2. Между выходом блока сравнения с нижним порогом 3 и вторым входом второго элемента ИЛИ 9 включен второй элемент И 12, причем третий вход реверсивного счетчика 1 соединен с вторым входом третьего элемента ИЛИ 10, первый выход триггера 11 соединен с вторым входом элемента И 8, второй выход триггера 11 соединен с вторым входом элемента И 12. Третий вход реверсивного счетчика 1 является входом его установки в начальное состояние, первый вход вентиля 6 является входом запрета, второй вход вентиля 6 является входом 13 - входом анализируемой последовательности импульсов, второй вход первого элемента ИЛИ 5 является входом 14 - входом контрольной шумовой последовательности импульсов, вход делителя частоты 4 является входом 15 - входом вспомогательной последовательности импульсов, второй вход третьего элемента ИЛИ 10 является входом 16 - входом запуска, второй выход триггера 11 является выходом 17 - выходом индикации состояния «поиск» и «контроль», выход второго элемента ИЛИ 9 является выходом 18 - выходом последовательного обнаружителя.

Последовательный обнаружитель работает следующим образом. Подачей импульса пуска на вход 16 обнаружитель ставится в состояние обнаружения при поиске сигнала. Импульс пуска устанавливает реверсивный счетчик 1 в начальное состояние S (0<S<N-1) где N - емкость реверсивного счетчика 1, а также, пройдя через элемент ИЛИ 10, устанавливает триггер 11 в состояние «поиск». При этом выходным напряжение блока сравнения 2 вентиль 6 устанавливается в открытое состояние, с выходов триггера 11 на элемент И 12 подается разрешающее напряжение, а на элемент И 8 - запрещающее. На вход сложения реверсивного счетчика 1 через вентиль 6 поступают бинарно-квантованные по амплитуде импульсы анализируемой (сигнальной или шумовой) последовательности, а на вход вычитания через элемент ИЛИ 5 поступает сумма бинарно-квантованных по амплитуде импульсов контрольной шумовой последовательности, подаваемой на вход 14 и поделенной в n раз по частоте в делителе частоты 4 вспомогательной последовательности бинарно-квантованных по амплитуде импульсов, подаваемых на вход 15, имеющих частоту повторения обнаруживаемого сигнала и не совпадающих по времени с импульсами анализируемой и контрольной последовательностей. Состояние обнаружения при поиске длится до тех пор, пока реверсивный счетчик 1 не достигнет либо своего верхнего состояния N-1, либо состояния Mn≥0.

Если реверсивный счетчик 1 попадает в состояние Mn, то на выходе блока сравнения 3 с нижним порогом при поиске появляется напряжение, которое через элементы И 12 и ИЛИ 9 поступает на выход 18 обнаружителя, что означает принятие обнаружителем решения об отсутствии сигнала в анализируемой последовательности. Если реверсивный счетчик 1 достигает своего верхнего состояния N-1, то на выходе блока сравнения 2 с верхним порогом появляется напряжение, которое, попав на вход триггера 11, переводит его в состояние «контроль». Изменение напряжения на выходе 17 триггера 11 свидетельствует о принятии обнаружителем решения о наличии сигнала в анализируемой последовательности и о переходе обнаружителя из состояния обнаружения при поиске сигнала в состояние контроля за наличием сигнала в анализируемой последовательности. При контроле с выходов триггера 11 на элемент И 12 подается запрещающее напряжение, а на элемент И 8 - разрешающее напряжение, в результате чего выход 18 обнаружителя отключается от блока сравнения 3 и подключается к блоку сравнения 7 с нижним порогом при контроле. В состоянии N-1 реверсивного счетчика 1 напряжение с выхода блока сравнения 2 закрывает вентиль 6, чем отключает вход сложения реверсивного счетчика 1 от входа 13 обнаружителя и предохраняет его от переполнения. При контроле реверсивный счетчик 1 может принимать любые состояния от N-1 до Мк+1>0. Если состояние реверсивного счетчика 1 падает до величины Мк≥0, то на выходе блока сравнения 7 появляется напряжение, которое через элемент И 8 и элемент ИЛИ 9 поступает на выход 18 обнаружителя и через элемент ИЛИ 10 на вход триггера 11, который при этом переходит из состояния «контроль» в состояние «поиск», что свидетельствует о принятии обнаружителем решения о потере сигнала в режиме «контроль» и о необходимости вести его поиск в другой импульсной последовательности.

Однако прототип также имеет некоторые недостатками: обнаруживая факт наличия сигналов, устройство не предназначено для точного измерения времени начала и конца пачки сигналов. Соответственно, точно измерить угловые координаты цели невозможно. При флюктуациях амплитуды сигнала в связи с попаданием в максимум или минимум диаграммы обратного рассеяния цели может наблюдаться явление пропадания («замирания») сигналов в пачке. В результате также возникают трудности с измерением угловых координат цели.

Задачей изобретения является повышение точности измерения времени начала и конца пачки в аддитивной смеси с шумом, характеризующейся пропусками сигналов, вызванных «замираниями» отраженных эхо-сигналов в минимумах диаграммы обратного рассеяния цели и, соответственно, точности измерения угловых координат цели и режекции шумовых выбросов, превышавших пороговый уровень обнаружителя и воспринятых устройством как полезный сигнал.

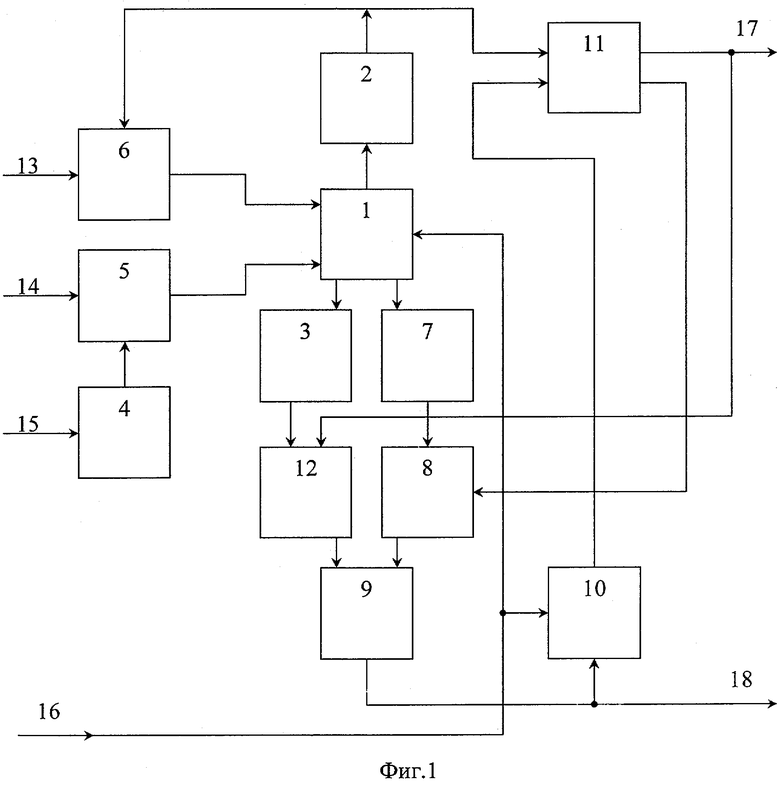

Для достижения указанного технического результата в обнаружитель пачки сигналов, содержащий реверсивный счетчик 1, первый выход которого соединен с входом блока сравнения с верхним порогом 2, а второй выход соединен с входом блока сравнения с нижним порогом 3, дополнительно введены интегратор 19, пороговое устройство 20, первая схема коммутации 21, вторая схема коммутации 22 и линия задержки на период повторения 23, при этом вход интегратора 19 является входом 25 обнаружителя, выход интегратора подключен к первому входу порогового устройства 20, выход которого подключен к первому входу первой схемы коммутации 21. Первый выход первой схемы коммутации 21 подключен к первому входу реверсивного счетчика 1, второй выход первой схемы коммутации 21 подключен к второму входу реверсивного счетчика 1. Третий выход реверсивного счетчика 1 подключен к первому входу второй схемы коммутации 22, выход которой подключен к входу линии задержки на период повторения 23. Выход линии задержки на период повторения соединен с третьим входом реверсивного счетчика 1. При этом на второй вход порогового устройства поступает «пороговый уровень» 26, на второй вход первой схемы коммутации 21 «опорная последовательность импульсов» 24, на четвертый вход реверсивного счетчика 1 поступает «импульс обнуления» 27, на второй вход второй схемы коммутации 22 поступает сигнал «ограничение кода по максимуму» 28. Выход блока сравнения с верхним порогом 2 соединен с третьим входом второй схемы коммутации 22. Выход блока сравнения с нижним порогом 3 является выходом обнаружителя пачки сигналов 29.

Изобретение иллюстрируется чертежами, представленными на фиг.1 -3, где: на фиг.1 представлена электрическая функциональная схема прототипа; на фиг.2 - электрическая функциональная схема заявляемого обнаружителя пачки сигналов, на фиг.3 - эпюры, поясняющие работу обнаружителя пачки сигналов.

Таким образом, обнаружитель пачки сигналов содержит:

1 - Реверсивный счетчик;

2 - Блок сравнения с верхним порогом;

3 - Блок сравнения с нижним порогом;

19 - Интегратор;

20 - Пороговое устройство;

21 - Первая схема коммутации;

22 - Вторая схема коммутации;

23 - Линия задержки на период повторения;

24 - Вход опорной последовательности импульсов;

25 - Вход обнаружителя пачки сигналов;

26 - Вход порогового уровня;

27 - Вход импульса обнуления;

28 - Вход ограничения кода по максимуму;

29 - Выход обнаружителя пачки сигналов.

При этом первый выход реверсивного счетчика 1 подключен к входу блока сравнения с верхним порогом 2, второй выход реверсивного счетчика 1 подключен к входу блока сравнения с нижним порогом 3, вход интегратора 19 является входом 25 обнаружителя пачки сигналов. Выход интегратора 19 подключен к первому входу порогового устройства 20, выход порогового устройства 20 подключен к первому входу первой схемы коммутации 21, первый выход первой схемы коммутации 21 подключен к первому входу реверсивного счетчика 1, второй выход первой схемы коммутации 21 подключен к второму входу реверсивного счетчика 1, третий выход реверсивного счетчика 1 подключен к первому входу второй схемы коммутации 22, выход второй схемы коммутации 22 подключен к входу линии задержки на период повторения 23, выход которой соединен с третьим входом реверсивного счетчика 1. При этом второй вход порогового устройства 20 является входом 26 порогового уровня, второй вход первой схемы коммутации 21 является входом 24 опорной последовательность импульсов, четвертый вход реверсивного счетчика 1 является входом 27 импульса обнуления, третий вход второй схемы коммутации 22 является входом 28 сигнала ограничения кода по максимуму, выход блока сравнения с верхним порогом 2 соединен с вторым входом второй схемы коммутации 22, выход блока сравнения с нижним порогом 3 является выходом обнаружителя пачки сигналов 29.

Обнаружитель пачки сигналов работает следующим образом. Аддитивная смесь шума и пачки полезных сигналов, являющаяся входным сигналом 25 обнаружителя пачки сигналов (фиг.3а), поступает на вход интегратора 19, имеющего постоянную времени, согласованную с длительностью пачки сигналов, где происходит накопление полезного сигнала (фиг.3б). Накопленный сигнал сравнивается в пороговом устройстве 20 с пороговым уровнем 26, поступающим на его второй вход. Выходной сигнал порогового устройства 20 поступает на первый (управляющий) вход первой схемы коммутации 21. При наличии на управляющем входе сигнала разрешения с выхода порогового устройства 20 (фиг.3в) опорная последовательность импульсов 24, проходит через первую схему коммутации 21 на первый вход (вход сложения) реверсивного счетчика 1 (фиг.3г), при отсутствии сигнала разрешения - на второй вход (вход вычитания) реверсивного счетчика 1 (фиг.3д). В начальный момент реверсивный счетчик 1 обнуляется «импульсом обнуления» 27, поступающим на его четвертый вход. При отсутствии пачки импульсов на вход вычитания поступает последовательность логических «1» и выходной код реверсивного счетчика 1 будет равен «0» (т.к. он был обнулен в начальный момент времени). По приходу пачки сигналов последовательность логических «1» опорной последовательности импульсов поступает на вход сложения реверсивного счетчика 1, который начинает их счет. Код счета с выходов реверсивного счетчика 1 поступает на входы блока сравнения с нижним порогом 3, блока сравнения с верхним порогом 2 и второй схемы коммутации 22. При этом значения кода счета на первом, втором и третьем выходах реверсивного счетчика равны. Блок сравнения с нижним порогом 3 сравнивает код счета с некоторым числом «А», например «3». Если текущий код превышает значение «А», то делается вывод о наличии пачки сигналов и формируется импульс выхода, являющийся выходным сигналом обнаружителя пачки сигналов 29. Если код счета меньше «А», то делается вывод о действии шумового выброса и импульс выхода не формируется. Блок сравнения с верхним порогом 2 и вторая схема коммутации 22 образуют схему ограничения кода по максимуму. Блок сравнения с верхним порогом 2 сравнивает полученный код счета с некоторым числом «2А+1» (например, «7»). Если код счета больше этого числа, то вырабатывается управляющий сигнал, переключающий вторую схему коммутации 22 на передачу установленного на ее третьим входе кода ограничения по максимуму 28 «2А+1» на выход. Если меньше - то на вход линии задержки на период повторения 23 через вторую схему коммутации 22 поступает текущий код счета с третьего выхода реверсивного счетчика 1. Тем самым происходит ограничение максимального кода счета числом «2А+1» и обеспечивается неизменность размеров пачки. Код счета задерживается в линии задержки на период повторения 23 и поступает на установочный вход реверсивного счетчика 1, тем самым устанавливая в каждом цикле либо текущий, либо ограниченный по максимуму код счета. Ограничение кода счета некоторым значением необходимо для сохранения размеров пачки сигналов. Если начало пачки сигналов сдвинуто во временной области на три периода повторения, то конец пачки необходимо формировать с запаздыванием на три периода повторения. Тем самым размеры пачки сигналов остаются неизменными, а пропадания сигналов, вызванные замираниями в минимумах диаграммы обратного рассеяния цели, исключаются (фиг.3е). Одновременно подобная обработка обеспечивает защиту от мешающих шумовых выбросов, прошедших бинарное квантование и воспринятых как полезные сигналы.

Предлагаемый обнаружитель пачки сигналов реализован на дискретных электрорадиоэлементах (интегратор) и типовых интегральных микросхемах. (реверсивный счетчик, пороговые устройства и линия задержки) [6]. Таким образом, предлагаемое изобретение соответствует критерию «промышленная применимость».

Список литературы

1. Самсоненко С.В. Цифровые методы оптимальной обработки радиолокационных сигналов. - М.: Военное издательство, 1968. - 320 с.: ил. (стр.180-210).

2. Дымова А.И., Альбац М.Е., Бонч-Бруевич А.М. Радиотехнические системы. Под ред. А.И. Дымовой. Учеб. для вузов. - М.: Советское радио, 1975. - 440 с.: ил. (стр.230-236).

3. Авт. свидетельство №640219. Опубл. 30.12.78. Бюл. №48.

4. Авт. свидетельство №640220. Опубл. 30.12.78. Бюл. №48.

5. Авт. свидетельство №540230. Опубл. 25.12.76. Бюл. №47.

6. Шило В.Л. Популярные цифровые микросхемы. Справочник. - М.: Радио и связь, 1987. - 352 с.: ил. (стр.91-93).

| название | год | авторы | номер документа |

|---|---|---|---|

| ОБНАРУЖИТЕЛЬ ПЕРЕОТРАЖЕННЫХ СИГНАЛОВ | 1999 |

|

RU2191400C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| ЧАСТОТНО-АДАПТИВНАЯ РАДИОЛИНИЯ ДЛЯ ПЕРЕДАЧИ СРЕДНЕСКОРОСТНЫХ ПОТОКОВ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1998 |

|

RU2142200C1 |

| Амплитудный временной квантователь с регулируемым порогом | 1982 |

|

SU1345150A1 |

| Устройство для цифровой записи воспроизведения речевой информации | 1988 |

|

SU1573470A1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1994 |

|

RU2083995C1 |

| Устройство для измерения амплитуды радиоимпульсов | 1977 |

|

SU717675A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ И ОБРАБОТКИ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2004 |

|

RU2260192C1 |

Изобретение относится к радиотехнике и может использоваться в радиолокации, в частности в системах автоматического измерения угловых координат цели (угла места, азимута). Задачей изобретения является повышение точности измерения времени начала и конца пачки сигналов в аддитивной смеси с шумом, характеризующейся «замираниями» отраженных эхо-сигналов в минимумах диаграммы обратного рассеяния цели и, соответственно, точности измерения угловых координат цели и режекции шумовых выбросов, превышающих пороговый уровень обнаружителя. Обнаружитель пачки сигналов состоит из реверсивного счетчика (1), блока сравнения с верхним порогом (2), блока сравнения с нижним порогом (3), интегратора (19), первой (21) и второй (22) схем коммутации, линии задержки на период повторения (23). Вход (25) является входом обнаружителя, вход (26) - входом порогового уровня, вход (27) - входом импульса обнуления, вход (28) - входом ограничения кода по максимуму, выход (29) - выходом обнаружителя пачки сигналов. 3 ил.

Обнаружитель пачки сигналов, состоящий из реверсивного счетчика, первый выход которого подключен к входу блока сравнения с верхним порогом, второй выход подключен к входу блока сравнения с нижним порогом, отличающийся тем, что в него введены интегратор, пороговое устройство, первая и вторая схема коммутации, линия задержки на период повторения, при этом вход интегратора является входом обнаружителя пачки сигналов, выход интегратора подключен к первому входу порогового устройства, выход порогового устройства подключен к первому входу первой схемы коммутации, первый выход первой схемы коммутации подключен к первому входу реверсивного счетчика, второй выход первой схемы коммутации подключен к второму входу реверсивного счетчика, третий выход реверсивного счетчика подключен к первому входу второй схемы коммутации, выход второй схемы коммутации подключен к входу линии задержки на период повторения, выход которой соединен с третьим входом реверсивного счетчика, при этом второй вход порогового устройства является входом порогового уровня, второй вход первой схемы коммутации является входом опорной последовательности импульсов, четвертый вход реверсивного счетчика является входом импульса обнуления, третий вход второй схемы коммутации является входом сигнала ограничения кода по максимуму, выход блока сравнения с верхним порогом соединен с вторым входом второй схемы коммутации, выход блока сравнения с нижним порогом является выходом обнаружителя пачки сигналов.

| Последовательный обнаружитель | 1974 |

|

SU540230A1 |

| Устройство обнаружения сигналов | 1976 |

|

SU640220A2 |

| Обнаружитель пачки двоично квантованных сигналов | 1976 |

|

SU640219A1 |

| GB 980440, 13.01.1965 | |||

| JP 61020875, 29.01.1986 | |||

| JP 55065168, 16.05.1980. | |||

Авторы

Даты

2007-10-10—Публикация

2006-04-17—Подача