11

Изобретение относится к радиотехнике и может использоваться в обнаружителях сигналов на фоне нестационарных по азимуту -помех.

Цель изобретения -- увеличение быстродействия регулирования порога при наличии азимутально нестационарных помех без подавления сигналов точечных целей,

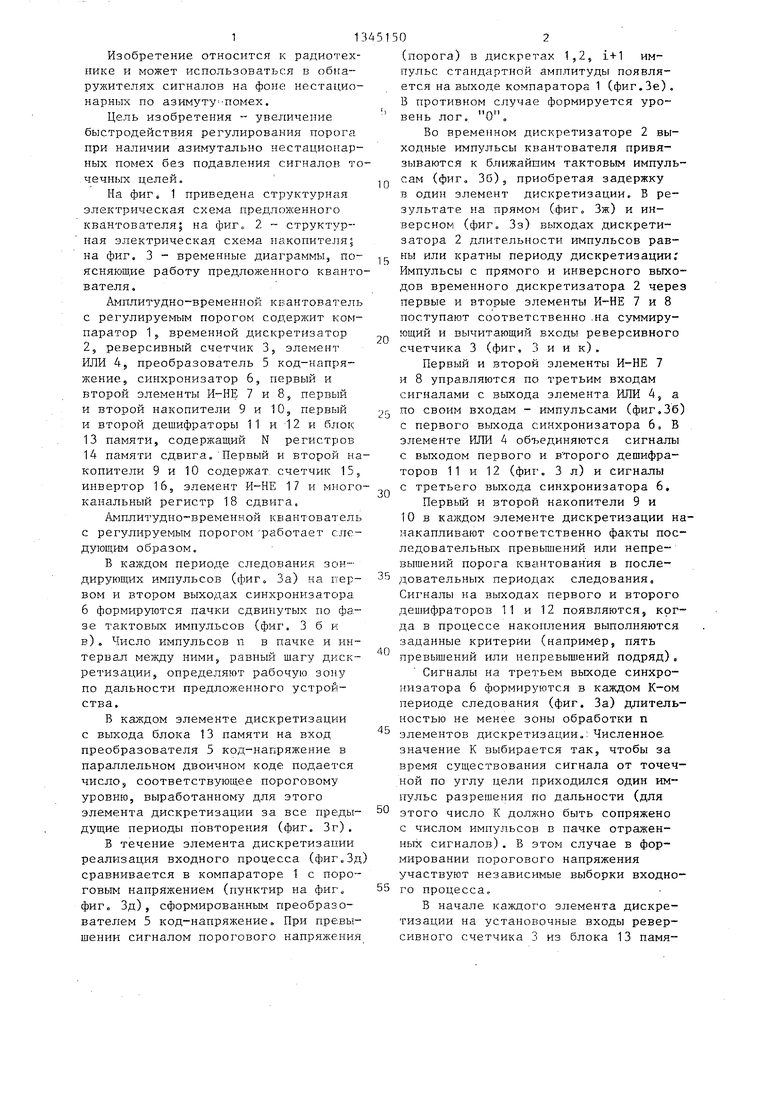

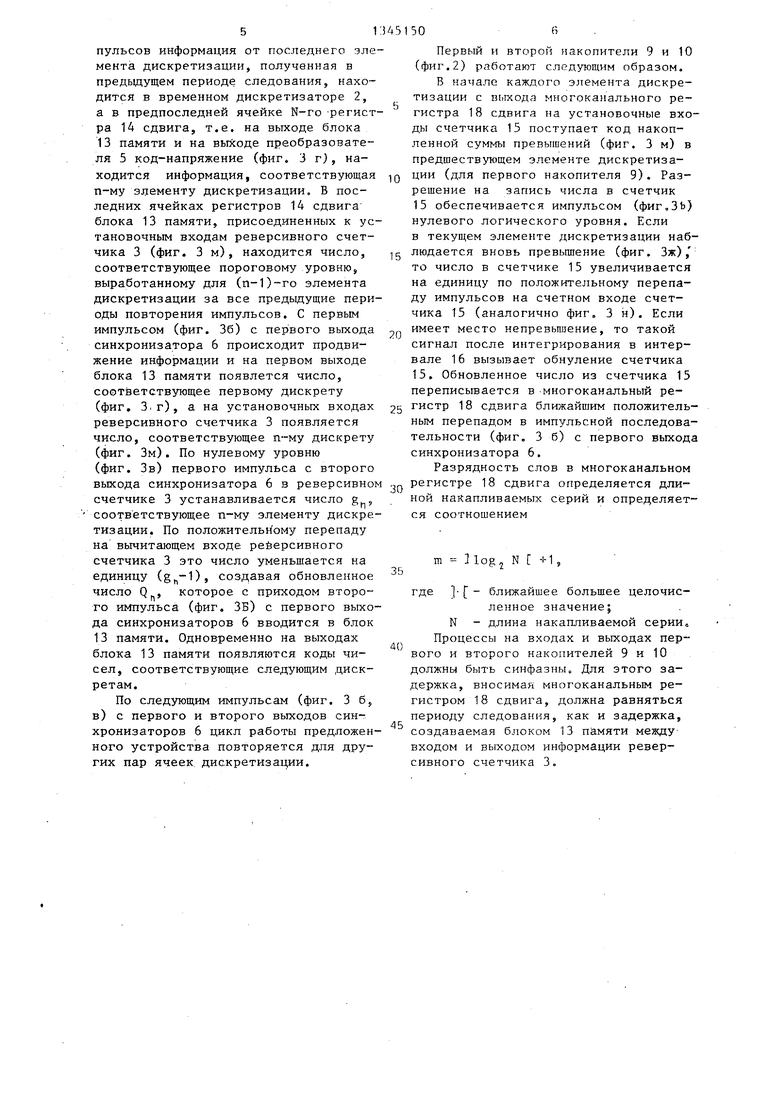

Иа фиг. 1 приведена структурная электрическая схема предложенного квантователя; на фиг,, 2 структурная электрическая схема накопителя; на фиг, 3 - временные диаграммы, по- ясняющие работу предложенного квантователя.

Амплитудно-временной квантователь с регулируемым порогом содержит компаратор 15 временной дискретизатор 2, реверсивный счетчик 3, элемент ИЛИ 4, преобразователь 5 код-напряжение, синхронизатор 6, первый и второй элементы И-НЕ 7 и 8, первый и второй накопители 9 и 10, первый и второй дешифраторы 11 и 12 и блок

13памяти, содержащий N регистров

14памяти сдвига. Первый и второй накопители 9 и 10 содержат, счетчик 15, инвертор 16, элемент И-НЕ 17 и многоканальный регистр 18 сдвига.

Амплитудно-временной квантователь с регулируемым порогом работает следующим образом.

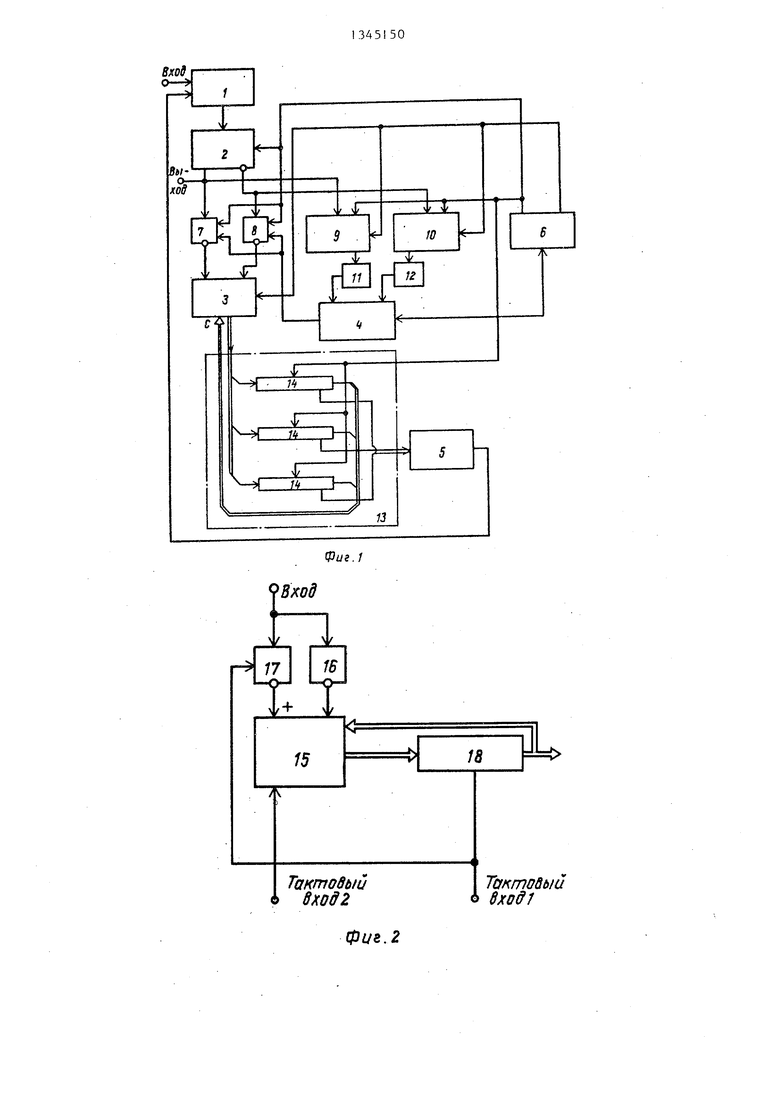

В каждом периоде следования зондирующих импульсов (фиг За) на пер- вом и втором выходах синхронизатора 6 формируются пачки сдвинутых по фазе тактовых импульсов (фиг. 3 б и

в). Число импульсов п. в пачке и ин

тервал между ними, равный шагу дискретизации, определяют рабочую зону по дальности предложенного устройства.

В каждом элементе дискретизации с выхода блока 13 памяти на вход преобразователя 5 код-напряжение в параллельном двоичном коде подается число, соответствующее пороговому уровню, выработанному для этого элемента дискретизации за все преды- дущие периоды повторения (фиг. Зг).

В течение элемента дискретизации реализация входного процесса (фиг.Зд сравнивается в компараторе 1 с пороговым напряжением (пунктир на фиг. фиг. Зд), сформированным преобразователем 5 код-напряжение. При превышении сигналом порогового напряжения

д

,

5

5

0

0

5

0

502

(порога) в дискретах 1,2, i+1 импульс стандартной амплитуды появляется на выходе компаратора 1 (фиг.Зе). В противном случае формируется уровень лог. 0

Во временном дискретизаторе 2 выходные импульсы квантователя привязываются к ближайшим тактовым импульсам (фиг, Зб)5 приобретая задержку в оди}1 элемент дискретизации. В результате на прямом (фиг, Зж) и инверсном (фиг. Зз) выходах дискрети- затора 2 длительности импульсов равны или кратны периоду дискретизации; Импульсы с прямого и инверсного выходов временного дискретизатора 2 через первые и вторые элементы И-НЕ 7 и 8 поступают соответственно .на суммирующий и вычитающий входы реверсивного счетчика 3 (фиг, 3 и и к).

Первый и второй элементы И-НЕ 7 и 8 управляются по третьим входам сигналами с выхода элемента ИЛИ 4, а по своим входам - импульсами (фиг.Зб) с первого выхода синхронизатора 6. В элементе ИЛИ 4 объединяются сигналы с выходом первого и в торого дешифраторов 11 и 12 (фиг. 3 л) и сигналы с третьего выхода синхронизатора 6,

Первый второй накопители 9 и 10 в каждом элементе дискретизации на- накапливают соответственно факты последовательных превьшений или непре- вьгагений порога квантования в последовательных периодах следования. Сигналы на выходах первого и второго дешифраторов 11 и 12 появляются, когда в процессе накопления выполняются заданные критерии (например, пять превьшений или непревышений подряд).

Сигналы на третьем выходе синхронизатора 6 формируются в каждом К-ом периоде следования (фиг. За) длительностью не менее зоны обработки п элементов дискретизации.: Численное значение К выбирается так, чтобы за время существования сигнала от точечной по углу цели приходился один импульс разрешения по дальности (для этого число К должно быть сопряжено с числом импульсов в пачке отраженных сигналов). В этом случае в формировании порогового напряжения участвуют независимые выборки входного процесса.

В начале каждого элемента дискретизации на установочные входы реверсивного счетчика 3 из блока 13 памяти в параллельном двоичном коде подается число g (фиг. 3м), выработанное за все предыдущие периоды следования в этом элементе дискретизации.

Нулевым уровнем импульса тактовой последовательности (фиг. Зв) с второго выхода синхронизатора 6 это число в параллельном коде вводится в реверсивный счетчик 3 (число 3 и),

По положительным перепадам на счетных входах счетчика (фиг. 3 и и к) число в реверсивном счетчике 3 увеличивается или уменьшается на единицу в зависимости от того, превысил (дискреты 1,2, i+1) или не превысил сигнал пороговое напряжение. По. положительному перепаду импульсов (фиг. Зб) с первого выхода синхронизатора 6 обновленное в реверсивном счетчике 3 число Q заносится в блок 13 памяти.

В тех элементах дискретизации, где нет импульса разрешения, постуКогда в одном из элементов дискретизации появляется протяженная по азимуту помеха, в первом накопителе 9 в элементах дискретизации 1 и 2 (фиг. Зд) начинает накапливаться серия единиц, соответствующих превышению помехой порогового напряжения. При выполнении в первом дешифраторе

1Q 11 заданной логики обнаружения (например, последовательность из 5 единиц) на его выходе и соответственно на входах первого и второго элементов И-НЕ 7 и 8 вырабатывается сигнал раз15 рушения (фиг. 3л), который разрешает обновление чисел в реверсивном счетчике 3 в каждом периоде следования. При этом максимально увеличивается скорость повышения порогового напря2Q жения (в данном примере 6 раз) до достижения стационарного состояния.

когда Р 0,5 и оба накопителя 9 и 10 не вьщают сигналов разрешения. По окончании протяженной по азимуту

35

пающего с выхода элемента ИЛИ 4 (нап- 25 помехи пороговое напряжение оказывается избыточным для шумов (элементы дискретизации L; i+2;n на фиг.Зд) ,поэтому во втором накопителе 10 накапливается серия, соответствующая последовател(ь- 2Q ным непревышениям порога, и на его выходе по истечении пяти периодов следования меньше, чем за ширину диаграммы направленности антенны, вырабатывается сигнал, разрешающий ускоренное уменьшение кода чисел в реверсивном счетчике 3 в каждом периоде следования (фиг. 3 л). Время переходного процесса установления nor- рогового напряжения при этом минимально, при этом обеспечиваются условия для обнаружения слабых целей, расположенных непосредственно за азимутальной границей помех.

Если порог срабатывания первого накопителя 9 выбрать так, что он не достигается при приеме сигнала от точечной цели в элементе дискретизации (i+1) , то первый и второй накопители 9 и 10 не оказывают действия при приеме сигналов от таких целей.

Правильное функционирование предложенного устройства обеспечивается временным совмещением всех процессов. Число ячеек N в регистрах 14 сдвига, должно быть сопряжено с числом импульсов на первом и втором

ример, в элементе i+2), обновление числа в реверсивном счетчике 3 не происходит и в блоки памяти записывается то же число g(i+1), которое ранее было считано из него.

В тот период следования, когда на третьем выходе синхронизатора 6 формируется сигнал разрешения (например, в каждом шестом периоде следования), обновление чисел в реверсивном счетчике 3 происходит во всех элементах дискретизации независимо от сигналов на выходе первого и второго дешифраторов 11 и 12. Если на сигнальном входе компаратора 1 действует стационарный во времени шумовой процесс, а амплитуды всплесков в соседних периодах следования некоррелированы, то на выходе устройства осуществляется стабилизация с вероятностью превышения порога Pjjj 0,5, т.е. вероятности превьшения и непрерывшения видеошумом порогового напряжения равны.

В этом случае появление на выходе компаратора 1 серии из последовательных превышений или непревьшзений является маловероятным событием, поэтому первый и второй накопители 9 и 10 в этих условиях не оказывают влияния на работу устройства, и обновление порогового напряжения (как ,и чисел в реверсивном счетчике 3) происходит в одном из шести периодов следования.

40

45

50

55

выходах (фиг. 3,6,в) синхронизатора 6 так, что перед началом очередного периода следования зондирующих им45150Когда в одном из элементов дискретизации появляется протяженная по азимуту помеха, в первом накопителе 9 в элементах дискретизации 1 и 2 (фиг. Зд) начинает накапливаться серия единиц, соответствующих превышению помехой порогового напряжения. При выполнении в первом дешифраторе

1Q 11 заданной логики обнаружения (например, последовательность из 5 единиц) на его выходе и соответственно на входах первого и второго элементов И-НЕ 7 и 8 вырабатывается сигнал раз15 рушения (фиг. 3л), который разрешает обновление чисел в реверсивном счетчике 3 в каждом периоде следования. При этом максимально увеличивается скорость повышения порогового напря2Q жения (в данном примере 6 раз) до достижения стационарного состояния.

когда Р 0,5 и оба накопителя 9 и 10 не вьщают сигналов разрешения. По окончании протяженной по азимуту

35

25 2Q

25 2Q

40

45

50

55

выходах (фиг. 3,6,в) синхронизатора 6 так, что перед началом очередного периода следования зондирующих им5i

пульсов информация от последнего элемента дискретизации, полученная в предыдущем периоде следования, находится в временном дискретизаторе 2, а в предпоследней ячейке N-ro -регистра 14 сдвига, т.е. на выходе блока 13 памяти и на выходе преобразователя 5 код-напряжение (фиг. 3 г), находится информация, соответствующая п-му элементу дискретизации. Б последних ячейках регистров 14 сдвига блока 13 памяти, присоединенных к установочным входам реверсивного счетчика 3 (фиг. 3м), находится число, соответствующее пороговому уровню, выработанному для (n-l)-ro элемента дискретизации за все предыдущие периоды повторения импульсов. С первым импульсом (фиг. 36) с первого выхода синхронизатора 6 происходит продвижение информации и на первом выходе блока 13 памяти появлется число, соответствующее первому дискрету (фиг. З.г), а на установочных входах реверсивного счетчика 3 появляется число, соответствующее п-му дискрету (фиг. 3м). По нулевому уровню (фиг. Зв) первого импульса с второго выхода синхронизатора 6 в реверсивно счетчике 3 устанавливается число g , соответствующее п-му элементу дискретизации. По положительному перепаду на вычитающем входе рейерсивного счетчика 3 это число уменьшается на единицу (), создавая обновленное число Q , которое с приходом второго импульса (фиг, ЗБ) с первого выхода синхронизаторов 6 вводится в блок 13 памяти. Одновременно на выходах блока 13 памяти появляются коды чисел, соответствующие следующим дискретам.

По следующим импульсам (фиг. 3 б, в) с первого и второго выходов синхронизаторов 6 цикл работы предложенного устройства повторяется для других пар ячеек дискретизации.

50В .

Первый и второй накопители 9 и 10 (фиг.2) работают следующим образом.

В начале каждого элемента дискретизации с выхода многоканального регистра 18 сдвига на установочные входы счетчикс 15 поступает код накопленной суммы превышений (фиг. 3 м) в предшествующем элементе дискретизации (для первого накопителя 9). Разрешение на запись числа в счетчик 15 обеспечивается импульсом (фиг,ЗЬ) нулевого логического уровня. Если в текущем элементе дискретизации наблюдается вновь превышение (фиг. Зж) , то число в счетчике 15 увеличивается на единицу по положительному перепаду импульсов на счетном входе счетчика 15 (аналогично фиг, 3 н). Если имеет место непревьшение, то такой сигнал после интегрирования в интервале 16 вызывает обнуление счетчика 15. Обновленное число из счетчика 15 переписывается в -многоканальный регистр 18 сдвига ближайшим положительным перепадом в импульсной последовательности (фиг, 3 б) с первого выхода синхронизатора 6.

Разрядность слов в многоканальном регистре 18 сдвига определяется длиной накапливаемых серий и определяется соотношением

Q g п 25 .

40

m -- logj N -М ,,

где - ближайшее большее целочисленное значение; N - длина накапливаемой серии Процессы на входах и выходах первого и второго накопителей 9 и 10 должны быть синфазнЫо Для этого задержка, вносимая многоканальным регистром 18 сдвига, должна равняться периоду следования, как и задержка, создаваемая блоком 13 памяти междувходом и выходом информации реверсивного счетчика 3.

9Вход

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1981 |

|

SU999112A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| СПОСОБ ОБНАРУЖЕНИЯ ХАОТИЧЕСКОЙ ПОСЛЕДОВАТЕЛЬНОСТИ ИМПУЛЬСОВ | 2013 |

|

RU2536638C1 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 2002 |

|

RU2244384C2 |

| СПОСОБ ОБНАРУЖЕНИЯ ЦЕЛЕЙ ИМПУЛЬСНОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИЕЙ И РАДИОЛОКАЦИОННАЯ СТАНЦИЯ ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2004 |

|

RU2270461C2 |

| Устройство для кодирования звуковых сигналов с инерционным компандированием | 1983 |

|

SU1109848A1 |

| СПОСОБ И УСТРОЙСТВО СИНХРОНИЗАЦИИ М-ПОСЛЕДОВАТЕЛЬНОСТИ | 1997 |

|

RU2127954C1 |

| Устройство обработки сигналов | 1981 |

|

SU1167556A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

1. Амплитудно-временной квантователь с регулируемым порогом, содержащий реверсивный счетчик, синхронизатор, блок памяти и последовательно соединенные преобразователь код-напряжения, компаратор и временной дискретнаатор, при этом блок памяти содержит N регистров сдвига, входы которых соединены с вьгходами одноименных разрядов реверсивного счетчика, а выходы - с установочными входами одноименных разрядов реверсивного счетчика, отвод каждого из N регистров сдвига соединен с входом одноименного из N разрядов преобразователя код-напряжение, а первый и второй выходы синхронизатора соединены соответственно с соединенными между собой тактовыми входами временного дискретизатора и N регистров сдвига блока памяти и .с тактовым входом реверсивного счетчика, отличающийся тем, что, с целью увеличения быстродействия регулирования порога при наличии азимутально нестационарных помех без подавления сигналов точечных целей, введены первый и второй элементы И-НЕ, первый и второй накопители, первый и второй дешифраторы и элементы ИЛИ, при этом прямой выход временного дискретизатора соединен через первый элемент И-НЕ с суммирующим входом реверсивного счетчика, а через последовательно соединенные первый накопитель и первый дешифратор - с первым входом элемента ИЛИ, инверсный выход временного дискретизатора соединен через второй элемент И-НЕ с вычитающим входом реверсивного счетчика, а через последовательно соединенные второй накопитель и второй дешифратор - с вторым входом элемента ИЛИ, вторые входы первого и второго элементов И-НЕ соединены с первым выходом синхронизатора, третий выход которого соединен с третьим входом элемента ИЛИ, соединенного своим выходом с третьими входами первого и второго элементов И-НЕ, а первый и второй выходы синхронизатора соединены соответственно с первым и вторым тактовыми входами обоих накопителей. 2. Квантователь по п. 1, отличающийся тем, что.накопитель содержит инвертор и последовательно соединенные элемент И-НЕ, счетчик и многоканальный регистр сдвига, выход которого соединен с разрешающим входом счетчика и является выходом накопителя, входом и первым и вторым тактовыми входами которого соответственно являются соединенные между собой вход инвертора и первый вход элемента И-НЕ, соединенные между собой второй вход элемента И-НЕ, и так-, товый вход многоканального регистра сдвига и тактовый вход счетчика, а выход инвертора соединен с вторым входом счетчика. Ш (Л . со 4 СЛ СЛ О

Тактовый А SKOdZ

Фиг.2

Таг тобыи 6xoff1

Фиг

| Устройство для контроля перекоса утка в движущейся ткани | 1948 |

|

SU84648A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Штамп для надрезки и отгибки язычков в стенке полого изделия | 1974 |

|

SU537740A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-10-15—Публикация

1982-12-07—Подача