Предлагаемое устройство относится к области радиотехники и может найти применение в адаптивных системах специальной радиосвязи для передачи данных по радиоканалу в условиях воздействия комплекса преднамеренных помех.

Известен программный модем для использования характеристик искажения, обусловленного групповой задержкой, для определения оптимальной скорости передачи символов и частоты несущей для передачи и приема данных, описанный в [1], в котором в различных вариантах определяется дисперсия искажения, обусловленного групповой задержкой, либо непосредственно, либо косвенным путем как корреляция амплитудного искажения или как корреляция выбранного фильтра предыскажения передачи, определенного в протоколе V.34 ITU.

Известен цифровой модем для систем передачи данных с фазоманипулированными и амплитудно-манипулированными сигналами, передаваемыми с одной боковой полосой (ФМ ОБП и АФМ ОБП) и с частично подавленной боковой полосой (ФМ ЧБП и АФМ ЧБП), описанный в [2], в котором устраняются быстрые флуктуации фазы несущего колебания на основе метода адаптивной компенсации.

Недостатком вышеупомянутых устройств является то, что они предназначены для функционирования только в условиях естественных помех и не работоспособны при активных и пассивных атаках противника [3, 12].

Наиболее близким по технической сущности к заявляемому является устройство, описанное в [4], принятое за прототип.

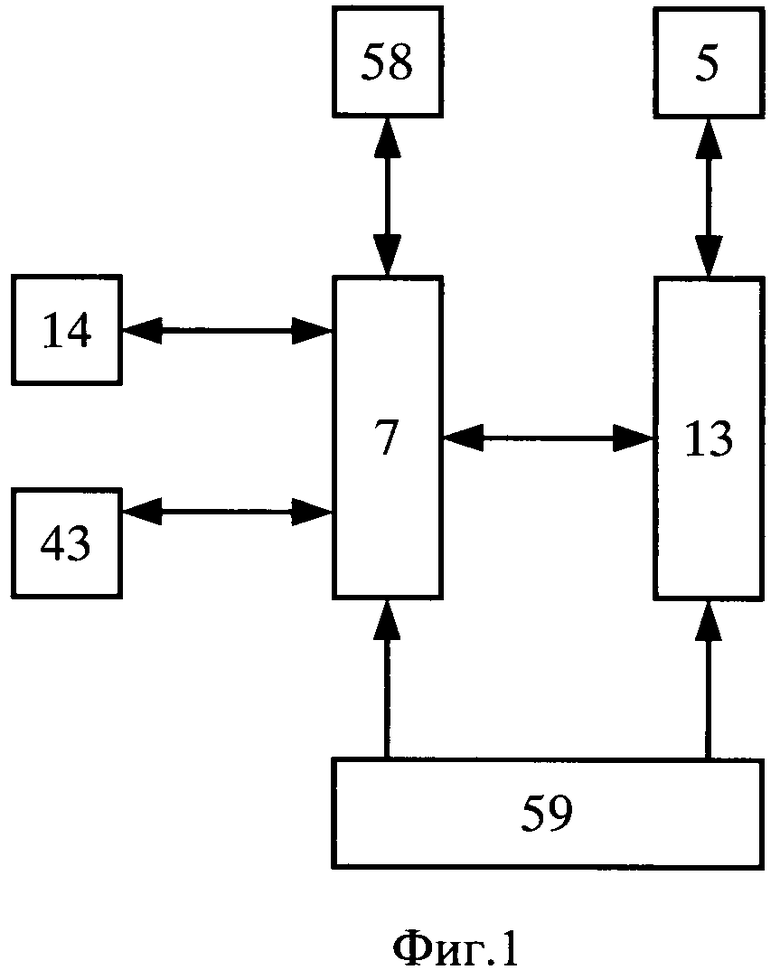

Функциональная схема устройства-прототипа приведена на фиг.1, где приняты следующие обозначения:

5 - антенно-фидерный блок (АФБ);

7 - кодек (блок управления);

13 - передающий блок (ПБ);

14 - первый интерфейс;

43 - второй интерфейс;

58 - светодиодный индикатор работы (СИР);

59 - гальваническая изоляция цепей питания (ГИЦП).

Устройство-прототип содержит кодек, первый вход-выход которого соединен с входом-выходом первого интерфейса 14, второй вход-выход - с входом-выходом второго интерфейса 43, третий вход-выход - с входом-выходом СИР 58, а четвертый вход-выход - с входом-выходом ПБ 13, второй вход-выход которого соединен с входом-выходом АФБ 5. Первый выход ГИЦП 59 соединен с одиночным входом кодека 7, а второй выход - с одиночным входом ПБ 13.

Блок 14 выполнен как интерфейс RS-232.

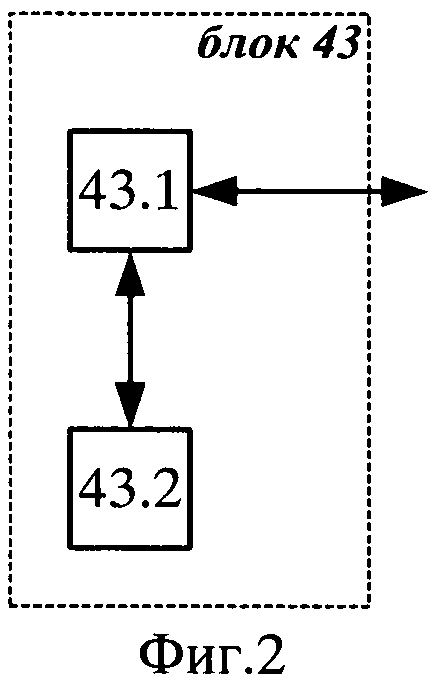

Функциональная схема блока 43 выполнена так, как показано на фиг.2, где приняты следующие обозначения:

43.1 - оптическая изоляция RS-485 (ОИ);

43.2 - интерфейс RS-485.

Блок 43 содержит интерфейс RS-485 43.2, вход-выход которого соединен с первым входом-выходом ОИ 43.1, второй вход-выход которого является входом-выходом блока 43.

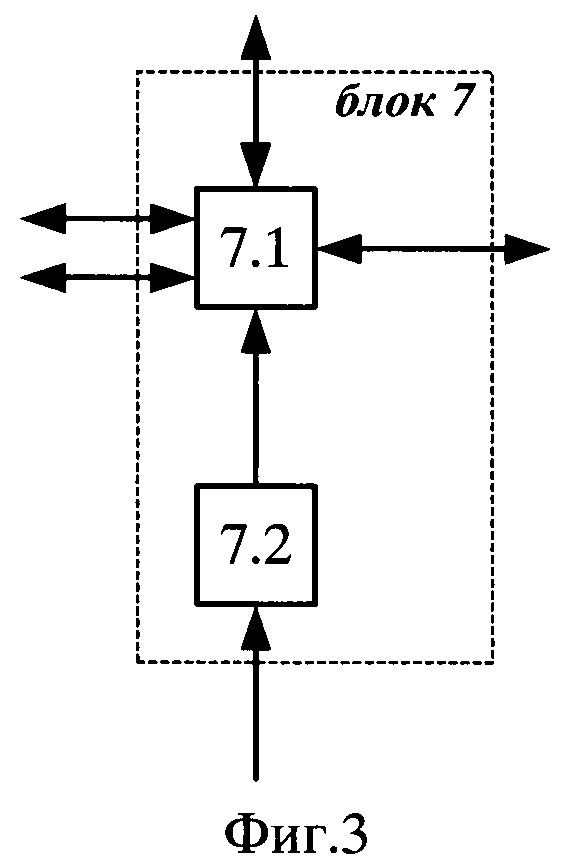

Функциональная схема кодека представлена на фиг.3, где приняты следующие обозначения:

7.1 - управляющий микроконтроллер (УМ);

7.2 - стабилизатор питания микроконтроллера (СПМ).

Блок 7 содержит последовательно соединенные СПМ 7.2, вход которого является входом кодека 7, и УМ 7.1, четыре входа-выхода которого являются соответствующими входами-выходами кодека 7.

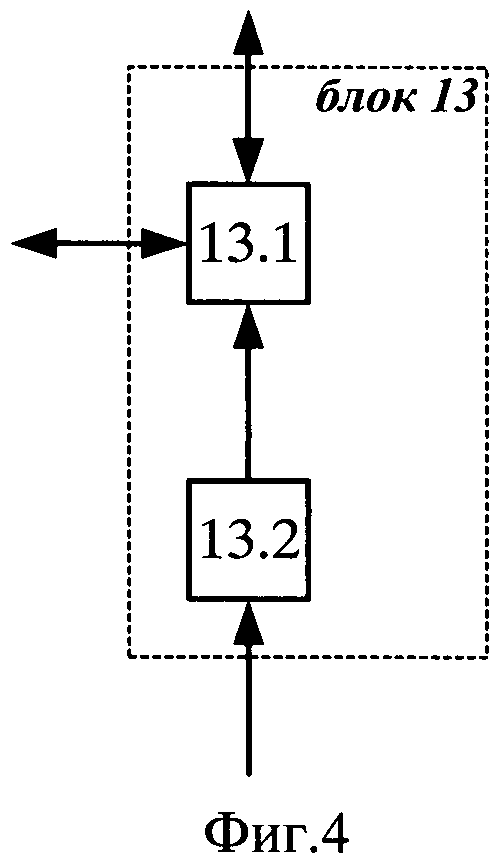

ПБ 13 выполнен так, как показано на фиг.4, где приняты следующие обозначения:

13.1 - радио-приемопередатчик (РПП);

13.2 - стабилизатор питания радио-приемопередатчика (СПР).

ПБ 13 содержит последовательно соединенные СПР 13.2, вход которого является входом блока 13, и РПП 13.1, два входа-выхода которого являются соответствующими входами-выходами ПБ 13.

Работа устройства-прототипа заключается в следующем.

Радиомодем содержит печатную плату, на которой расположен кодек 7, АФБ 5, СИР 58 и ПБ 13. Поток данных поступает через блок 14 в кодек 7, который кодирует данный поток. Кодированные данные поступают в ПБ 13, где они преобразуются в модулированный радиочастотный сигнал, который передается получателю с помощью АФБ 5. Режимы работы индицируются в СИР 58. Кроме того, обработанные данные передаются через блок 43 на внешние устройства. Цепи питания радиомодема гальванически изолированы от внешнего блока питания блоком ГИУП 59.

Исходя из описания работы устройства-прототипа можно сделать вывод о том, что он не приспособлен к работе в условиях специальной связи. Данные условия подразумевают функционирование радиомодема в условиях "информационной войны", то есть способность устройства противостоять несанкционированному доступу к данным, проходящим через него. Эта способность обеспечивается применением средств криптографической защиты информации (СКЗИ) и псевдослучайной перестройки рабочей частоты (ППРЧ), причем СКЗИ и ППРЧ должны применяться в условиях сетевой работы. Поэтому в устройстве-прототипе кодирование данных может пониматься только как эффективное или помехоустойчивое кодирование (а не как применение СКЗИ) по следующим соображениям.

Современные сети связи представляют собой совокупность большого числа мобильных абонентов (мобильных модемов), работающих синхронно. Слово "мобильный" подразумевает, что какой-либо из абонентов может временно выйти из сетевого синхронизма (отключиться; отъехать дальше зоны действия сети; и т.д.). Для того чтобы вернуться в сеть и продолжить обмен данными с другими абонентами сети, ему нужно восстановить с ними синхронный режим работы. Восстановление синхронизма понимается в первую очередь как восстановление синхронизма в СКЗИ (выработка одинаковых псевдослучайных чисел) и ППРЧ (обмен данными на одинаковых частотах). Это можно обеспечить только введением в радиомодем специальных алгоритмов остановки общей синхронной работы сети и обмена некой информацией со всеми абонентами сети (в том числе и с абонентом, желающим войти в сеть), чтобы на основе данной информации заново запустить сеть.

Таким образом, недостатком устройства-прототипа является невозможность обеспечения защиты данных от несанкционированного доступа.

В заявляемом изобретении решается задача введения способности радиомодема обеспечить защищенный режим работы для сетей связи, состоящей из мобильных абонентов.

Достигаемый при использовании изобретения технический результат - обеспечение защищенного режима работы с самовосстановлением радиосети с пакетной передачей данных (РППД), состоящей из мобильных абонентов, при пассивных атаках противника.

Для решения поставленной задачи в радиомодем, содержащий первый кодек, третий и шестой интерфейсы, передающий блок, соединенный с первым антенно-фидерным блоком, выход которого является выходом устройства, согласно изобретению введены последовательно соединенные первый интерфейс, аналого-цифровой преобразователь (АЦП) и первый коммутатор, выход которого соединен с первым входом первого кодека; последовательно соединенные первый сумматор, первый вход которого соединен с выходом первого кодека, второй коммутатор, второй сумматор, третий коммутатор и пакетатор, выход которого соединен с первым входом передающего блока; последовательно соединенные второй АФБ, вход которого является входом устройства, усилительно-преобразовательный блок (УПБ), блок фазовой автоподстройки (БФА), приемный блок, четвертый коммутатор, четвертый сумматор, третий сумматор, шестой кодек, пятый коммутатор, цифроаналоговый преобразователь (ЦАП) и седьмой интерфейс; последовательно соединенные четвертый интерфейс, пятый регистр, второй регистр, первый регистр и первый блок криптозащиты (БКЗ), выход которого соединен со вторым входом первого регистра, второй выход которого соединен со вторым входом второго регистра; последовательно соединенные пятый интерфейс, первый регистр сдвига, второй БКЗ, третий регистр и четвертый регистр, первый выход которого соединен со вторым входом третьего регистра, второй выход которого соединен со вторым входом второго блока криптозащиты; последовательно соединенные второй регистр сдвига, первый вход которого соединен со вторым выходом пятого интерфейса, третий БКЗ и шестой регистр; кроме того, введены управляющий блок, генератор тактовых импульсов, генератор кодовых последовательностей, четвертый БКЗ, блок отождествления элемента сигнала (БОЭС), мультиплексор, компаратор, k схем сравнения, а также первый, второй, третий и четвертый синтезаторы частот; второй интерфейс; второй, третий, четвертый и пятый кодеки; седьмой, восьмой и девятый регистры; при этом третий выход первого регистра соединен со вторым входом первого сумматора; третий выход третьего регистра соединен со вторым входом второго сумматора; второй выход второго регистра соединен с первым входом второго кодека, выход которого соединен со вторым входом второго коммутатора; второй выход четвертого регистра соединен с первыми входами первого и второго синтезаторов частот и третьего кодека, выход которого соединен со вторым входом третьего коммутатора; второй выход четвертого коммутатора соединен с первым входом пятого кодека, выход которого соединен с первым входом девятого регистра, выход которого соединен со вторым входом седьмого регистра, первый выход которого соединен со вторым входом четвертого БКЗ; второй выход седьмого регистра соединен со вторым входом третьего сумматора; третий выход четвертого коммутатора соединен с первым входом четвертого кодека, выход которого соединен с первым входом восьмого регистра, выход которого соединен с первыми входами третьего и четвертого синтезаторов частот и вторым входом шестого регистра, первый выход которого соединен со вторым входом третьего БКЗ; второй выход шестого регистра соединен со вторым входом четвертого сумматора; второй выход второго АФБ соединен с первым, сигнальным входом БОЭС, выход которого соединен с сигнальными входами k схем сравнения, выходы которых соединены с соответствующими k сигнальными входами компаратора и мультиплексора; выход компаратора соединен с адресным входом мультиплексора, выход которого соединен со вторым входом БФА; кроме того, выход первого регистра сдвига соединен со вторым входом первого БКЗ, а выход второго регистра сдвига - с первым входом четвертого БКЗ, выход которого соединен с первым входом седьмого регистра; группа выходов второго интерфейса шиной соединена с группой информационных входов управляющего блока, первая группа выходов которого шиной соединена с группами управляющих входов первого коммутатора, первого, второго и третьего кодеков, второго и третьего коммутаторов, а вторая группа выходов управляющего блока шиной соединена с группами управляющих входов четвертого и пятого коммутаторов, а также четвертого, пятого и шестого кодеков; выход третьего синтезатора частот соединен со вторым входом УПБ, а выход четвертого синтезатора частот - со вторым входом БОЭС; выход третьего интерфейса соединен с третьим входом первого коммутатора; выход генератора кодовых последовательностей соединен со вторым входом пакетатора, второй выход пятого коммутатора соединен с шестым интерфейсом; второй выход второго коммутатора соединен с четвертым входом третьего коммутатора; второй выход четвертого интерфейса соединен со вторым входом четвертого регистра; выход первого синтезатора частот соединен со вторым входом передающего блока, а выход второго синтезатора частот - с третьим входом передающего блока; выход генератора тактовых импульсов соединен с тактовыми входами управляющего блока, компаратора, передающего и приемного блоков, БФА, АЦП, ЦАП, БОЭС, пакетатора, мультиплексора, генератора кодовых последовательностей, каждого из шести кодеков, каждого из шести коммутаторов, каждого из четырех сумматоров, каждого из девяти регистров, каждого из двух регистров сдвига, каждого из четырех синтезаторов частот, каждого из четырех блоков криптозащиты, каждой из k схем сравнения.

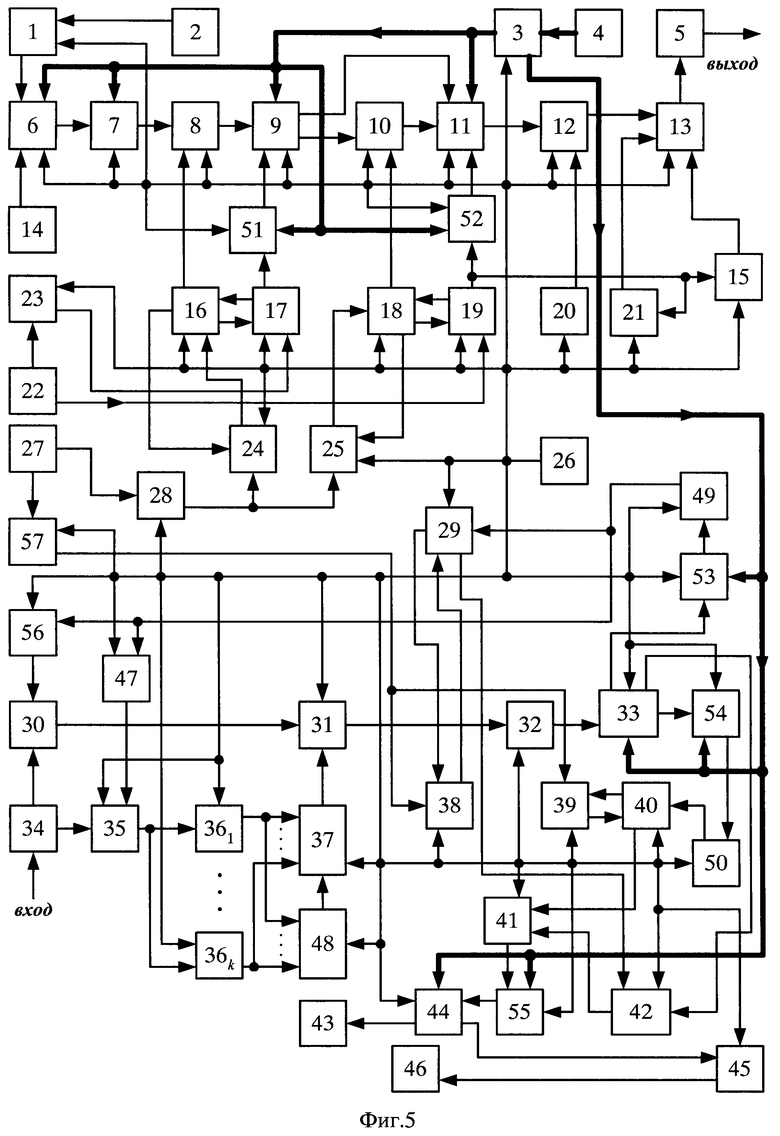

Функциональная схема заявляемого устройства приведена на фиг.5, где приняты следующие обозначения:

1 - аналого-цифровой преобразователь (АЦП);

2 - первый интерфейс (И1);

3 - управляющий блок (УБ);

4 - второй интерфейс (И2);

5 - первый антенно-фидерный блок (АФБ1);

6 - первый коммутатор (К1);

7 - первый кодек;

8 - первый сумматор (С1);

9 - второй коммутатор (К2);

10 - второй сумматор (С2);

11 - третий коммутатор (К3);

12 - пакетатор;

13 - передающий блок (ПБ);

14 - третий интерфейс (И3);

15 - первый синтезатор частот (СЧ1);

16 - первый регистр (Р1);

17 - второй регистр (Р2);

18 - третий регистр (Р3);

19 - четвертый регистр (Р4);

20 - генератор кодовых последовательностей (ГКП);

21 - второй синтезатор частот (СЧ2);

22 - четвертый интерфейс (И4);

23 - пятый регистр (Р5);

24 - первый блок криптозащиты (БКЗ1);

25 - второй блок криптозащиты (БКЗ2);

26 - генератор тактовых импульсов (ГТИ);

27 - пятый интерфейс (И5);

28 - первый регистр сдвига (РС1);

29 - шестой регистр (Р6);

30 - усилительно-преобразовательный блок (УПБ);

31 - блок фазовой автоподстройки (БФА);

32 - приемный блок (ПРБ);

33 - четвертый коммутатор (К4);

34 - второй антенно-фидерный блок (АФБ2);

35 - блок отождествления элемента сигнала (БОЭС);

361…36k - k схем сравнения (СС);

37 - мультиплексор;

38 - третий блок криптозащиты (БКЗ3);

39 - четвертый блок криптозащиты (БКЗ4);

40 - седьмой регистр (Р7);

41 - третий сумматор (С3);

42 - четвертый сумматор (С4);

43 - шестой интерфейс (И6);

44 - пятый коммутатор (К5);

45 - цифроаналоговый преобразователь (ЦАП);

46 - седьмой интерфейс (И7);

47 - четвертый синтезатор частот (СЧ4);

48 - компаратор;

49 - восьмой регистр (Р8);

50 - девятый регистр (Р9);

51 - второй кодек;

52 - третий кодек;

53 - четвертый кодек;

54 - пятый кодек;

55 - шестой кодек;

56 - третий синтезатор частот (СЧ3);

57 - второй регистр сдвига (РС2).

Заявляемое устройство содержит последовательно соединенные И1 2, АЦП 1, К1 6, первый кодек 7, С1 8, К2 9, С2 10, К3 11, пакетатор 12, ПБ 13 и АФБ1 5, выход которого является выходом устройства; последовательно соединенные АФБ2 34, вход которого является входом устройства, УПБ 30, БФА 31, ПРБ 32, К4 33, С4 42, С3 41, шестой кодек 55, К5 44, ЦАП 45 и И7 46; последовательно соединенные И4 22, Р5 23, Р2 17, P1 16 и БКЗ1 24, выход которого соединен со вторым входом Р1 16, второй выход которого соединен со вторым входом Р2 17; последовательно соединенные И5 27, РС1 28, БКЗ2 25, Р3 18 и Р4 19, первый выход которого соединен со вторым входом Р3 18, второй выход которого соединен со вторым входом БКЗ2 25. Второй выход И5 27 соединен с последовательно соединенными РС2 57, БКЗ3 38 и Р6 29.

Кроме того, выход РС1 28 соединен со вторым входом БКЗ1 24, а выход РС2 57 - с первым входом БКЗ4 39, выход которого соединен с первым входом Р7 40.

Третий выход Р1 16 соединен со вторым входом С1 8; третий выход Р3 18 соединен со вторым входом С2 10; второй выход Р2 17 соединен с первым входом второго кодека 51, выход которого соединен со вторым входом К2 9; второй выход Р4 19 соединен с первыми входами СЧ1 15, СЧ2 21 и третьего кодека 52, выход которого соединен со вторым входом К3 11.

Второй выход К4 33 соединен с первым входом пятого кодека 54, выход которого соединен с первым входом Р9 50, выход которого соединен со вторым входом Р7 40, первый выход которого соединен со вторым входом БКЗ4 39.

Второй выход Р7 40 соединен со вторым входом С3 41. Третий выход К4 33 соединен с первым входом четвертого кодека 53, выход которого соединен с первым входом Р8 49, выход которого соединен с первыми входами СЧ3 56, СЧ4 47 и вторым входом Р6 29, первый выход которого соединен со вторым входом БКЗ3 38. Второй выход Р6 29 соединен со вторым входом С4 42.

Второй выход АФБ2 34 соединен с первым, сигнальным входом БОЭС 35, выход которого соединен с сигнальными входами k схем сравнения (СС) 361-36k, выходы которых соединены с соответствующими k сигнальными входами компаратора 48 и мультиплексора 37. Выход компаратора 48 соединен с адресным входом мультиплексора 37, выход которого соединен со вторым входом БФА 31.

Группа выходов И2 4 шиной соединена с группой информационных входов УБ 3, первая группа выходов которого шиной соединена с группами управляющих входов К1 6, первого кодека 7, второго кодека 51, третьего кодека 52, К2 9, К3 11, а вторая группа выходов УБ 3 шиной соединена с группами управляющих входов К4 33, К5 44, четвертого кодека 53, пятого кодека 54 и шестого кодека 55.

Выход СЧ3 56 соединен со вторым входом УПБ 30, а выход СЧ4 47 - со вторым входом БОЭС 35. Выход И3 14 соединен с третьим входом К1 6. Выход ГКП 20 соединен со вторым входом пакетатора 12. Второй выход К5 44 соединен с И6 43.

Второй выход К2 9 соединен с четвертым входом К3 11. Второй выход И4 22 соединен со вторым входом Р4 19. Выход СЧ1 15 соединен со вторым входом ПБ 13, а выход СЧ2 21 - с третьим входом ПБ 13.

Выход ГТИ 26 соединен с тактовыми входами блоков 1, 3, 6-13, 15-21, 23-25, 28, 29, 31-33, 35, 37-42, 44, 45, 47-57, а также тактовыми входами k схем сравнения 361-36k.

Устройство работает следующим образом. На передающей стороне поток аналоговой информации поступает через И1 2 в АЦП 1, где он оцифровывается. Полученный цифровой поток данных так же, как и цифровой поток данных, поступающий через И3 14, через К1 6 поступает в первый кодек 7, который кодирует данный поток на основании сигнала управления с УБ 3. При этом К1 6 пропускает или поток данных от И3 14, или поток данных от АЦП 1, на основании сигнала управления с УБ 3.

Кодированные данные поступают блоками по y1 бит в С1 8, где происходит их суммирование с содержимым Р1 16 (размером y1 бит), являющимся псевдослучайной величиной. Зашифрованные в С1 8 данные поступают блоками по y2 бит через К2 9, на основании сигнала управления с УБ 3, в С2 10, где происходит их суммирование с содержимым Р3 18 (размером y2 бит), являющимся псевдослучайной величиной. Зашифрованные вторично в С2 10 данные поступают через К3 11, на основании сигнала управления с УБ 3, в пакетатор 12, где происходит их объединение с синхропоследовательностью, поступающей из ГКП 20.

Пакет, образованный в пакетаторе 12 и состоящий из двух частей - зашифрованной информации и синхропоследовательности, поступает в ПБ 13, где он преобразуется в модулированный радиочастотный сигнал, который передается получателю с помощью АФБ1 5. Каждая из двух частей пакета модулируется разными частотами, поступающими в пакетатор 13 из СЧ1 15 и СЧ2 21. Номера этих частот (размером до x2 бит каждая) поступают в СЧ1 15 и СЧ2 21 из Р4 19.

Две цифровые константы размером x1 и x2 бит соответственно поступают через И4 22 в Р5 23 и Р4 19. Данные константы должны быть индивидуальны для каждого сетевого радиомодема и могут представлять собой, например, некоторые функции от сетевого адреса того ПС, в состав которого входит данный радиомодем. Константа из Р5 23 переписывается в Р2 17. Таким образом осуществляется первоначальная загрузка блоков 17 и 19, имеющих размеры соответственно x1 и x2 бит.

Блоки 16 и 18 должны иметь размеры соответственно y1≥x1 и y2≥x2 бит. Поэтому значения блоков 17 и 19 должны "размножиться" в значения блоков 16 и 18 согласно функциям f1 и f2. "Размножение" может состоять, например, в простом дублировании определенных битов. Таким образом, y1=f1(x1), а y2=f2(x2).

При первоначальной загрузке значения Р1 16 и Р3 18 еще не являются псевдослучайным числом, а являются только лишь исходным (нулевым) состоянием блоков 24 и 25 соответственно. Поэтому для выработки псевдослучайных чисел, используемых для суммирования с поступающими данными в С1 8 и С2 10, значение Р1 16 поступает в БКЗ1 24, а значение Р3 8 - в БКЗ2 25. В блоках 24 и 25 происходит выработка псевдослучайных чисел по криптографическим алгоритмам g1 и g2 соответственно. Выработка происходит на основании значения РС1 28, загружаемого в БКЗ1 24 и БКЗ2 25 и поступающего в РС1 28 через И5 27. Данное значение представляет собой константу размером z бит, которая является ключом криптографических алгоритмов g1 и g2. Если криптографический алгоритм состоит из нескольких циклов, после каждого цикла в блоке 28 происходит сдвиг на d бит.

Полученные псевдослучайные числа загружаются из БКЗ1 24 в Р1 16 и из БКЗ2 25 в Р3 18 соответственно, и полученные в результате значения Р1 16 и Р2 18 используются для суммирования с поступающими данными в С1 8 и С2 10. Таким образом, быстродействие блока 24 должно быть таким, чтобы выработать псевдослучайное число до поступления в блок 8 очередного блока данных, а быстродействие блока 25 - чтобы выработать псевдослучайное число до поступления в блок 10 очередного блока данных.

Наличие шифраторов в модеме обеспечивает конфиденциальность циркулирующей в сети информации. Однако, для сохранения синхронности работы модема на передающей и приемной сторонах, вместо передачи зашифрованных данных по основному алгоритму (описанному выше) через каждые Т секунд предусмотрена следующая процедура:

1) определенные биты (в количестве x1) из текущего значения блока 16 загружаются в блок 17;

1) определенные биты (в количестве x2) из текущего значения блока 18 загружаются в блок 19;

3) значение блока 17, называемое первой текущей временной меткой (ТВМ1), поступает во второй кодек 51, который кодирует ТВМ1 на основании сигнала управления с УБ 3;

4) на основании сигнала управления с УБ 3 кодированная ТВМ1 через К2 9 поступает в К3 11;

5) на основании сигнала управления с УБ 3 через К3 11 кодированная ТВМ1 поступает в пакетатор 12;

6) значение блока 19, называемое второй текущей временной меткой (ТВМ2), поступает в третий кодек 52, который кодирует ТВМ2 на основании сигнала управления с УБ 3;

7) на основании сигнала управления с УБ 3 через К3 11 кодированная ТВМ2 поступает в пакетатор 12;

8) в пакетаторе 12 происходит объединение ТВМ1 и ТВМ2 с синхропоследовательностью, поступающей из ГКП 20;

9) пакет, образованный в пакетаторе 12 и состоящий из трех частей: синхропоследовательности, ТВМ1 и ТВМ2, поступает в ПБ 13, где он преобразуется в модулированный радиочастотный сигнал, который передается получателю с помощью АФБ1 5;

10) каждая из трех частей пакета модулируется разными частотами, поступающими в пакетатор 13 из СЧ1 15 и СЧ2 21, причем номера этих частот (размером до x2 бит каждая) поступают в СЧ1 15 и СЧ2 21 из Р4 19;

11) пункты 9, 10 повторяются m раз.

После завершения процедуры, состоящей из пунктов 1-11, значения блоков 17 и 19 должны "размножиться" в значения блоков 16 и 18 согласно функциям f1 и f2. После этого работа передающей части устройства соответствует работе по передаче зашифрованных данных по основному алгоритму.

На приемном конце входной сигнал, представляющий собой смесь полезного сигнала и помех, принимается АФБ2 34, где происходит его разделение на служебную и информационную составляющие.

Часть входного сигнала, содержащая служебную составляющую, со второго выхода АФБ2 34 поступает на первый сигнальный вход БОЭС 35. Последовательность случайных элементов смеси преобразуется в БОЭС 35 в случайную последовательность решений о символах, соответствующих принятым элементам сигнала, с помощью частоты приема, полученной на выходе СЧ4 47 на основе значения, подаваемого с выхода Р8 49. Эта последовательность решений о символах в общем случае за счет действия помех не совпадает ни с одной из последовательностей символов элементов, которые использовались на передающей стороне при формировании синхропоследовательностей в ГКП 20. В БОЭС 35 происходит оптимальная обработка смеси элемента сигнала и помехи, и на его выходе выдается последовательность решений о том, какой элемент синхропоследовательности (логический "0" или логическая "1") действовал. Полученная последовательность решений о символах поэлементно сравнивается с кодами ожидаемых синхропоследовательностей в соответствующих СС 361-36k.

Результаты сравнения с выходов СС 361-36k подаются на компаратор 48, который устанавливает максимум из k входных значений. Данный максимум определяет сигнал управления для мультиплексора 37.

Результаты сравнения с выходов СС 361-36k подаются, кроме того, на соответствующие сигнальные входы мультиплексора 37, в котором на основании сигнала управления, приходящего с компаратора 48, происходит выбор одного из k входов, сигнал с которого через мультиплексор 37 подается на второй сигнальный вход БФА 31.

Другая часть входного сигнала, содержащая информационную составляющую, поступает на первый вход УПБ 30, в котором спектр входного сигнала смещается на промежуточную частоту, на которой производится основная обработка сигнала, с последующим усилением сигнала промежуточной частоты.

Преобразование на частоту приема происходит в УПБ 30 на основе частоты, поступающей с выхода СЧ3 56 на основе значения, подаваемого с выхода Р8 49.

Сигнал с выхода УПБ 30 поступает на первый сигнальный вход БФА 31, в котором происходит точная фазовая подстройка информационной составляющей и тактовой последовательности на основе служебной составляющей. Сигнал с выхода БФА 31 поступает на сигнальный вход ПРБ 32, где он демодулируется.

С выхода блока 32 зашифрованные данные поступают блоками по y2 бит через К4 33, на основании сигнала управления с УБ 3, в С4 42, где происходит их суммирование с содержимым Р6 29 (размером y2 бит), являющимся псевдослучайной величиной. После блока 42 зашифрованные данные поступают блоками по y1 бит в С3 41, где происходит их суммирование с содержимым Р7 40 (размером y1 бит), также являющимся псевдослучайной величиной.

Для выработки псевдослучайных чисел, используемых для суммирования с зашифрованными данными в С4 42 и С3 41, значение Р6 29 поступает в БКЗ3 38, а значение Р7 40 - в БКЗ4 39. В блоках 38 и 39 происходит выработка псевдослучайных чисел по криптографическим алгоритмам g2 и g1 соответственно. Выработка происходит на основании значения РС2 57, загружаемого в БКЗ3 38 и БКЗ4 39 и поступающего в РС2 57 через И5 27. Данное значение представляет собой константу размером z бит, которая является ключом криптографических алгоритмов g1 и g2. Если криптографический алгоритм состоит из нескольких циклов, после каждого цикла в блоке 57 происходит сдвиг на d бит.

Расшифрованный поток данных с выхода С3 41 поступают в шестой кодек 55, который декодирует данный поток на основании сигнала управления с УБ 3. С выхода шестого кодека 55 через К5 44, на основании сигнала управления с УБ 3, поток поступает на внешние устройства либо через блок 43, либо, после преобразования в аналоговый сигнал в ЦАП 45, через блок 46.

Исходя из описанного алгоритма работы следует, что безошибочное декодирование данных на приемной стороне зависит от состояния Р6 29 и Р7 40. Для сохранения синхронности работы модема на передающей и приемной сторонах, вместо приема зашифрованных данных по основному алгоритму (описанному выше) через каждые Т секунд принимается две цифровые константы размером x1 и x2 бит соответственно. Константы, на основании сигнала управления с УБ 3, поступают через К4 33 в пятый кодек 54 и четвертый кодек 53 соответственно. Константы, декодированные в пятом 54 и четвертом 53 кодеках, на основании сигнала управления с УБ 3, записываются соответственно в Р9 50 и Р8 49.

Таким образом осуществляется первоначальная загрузка блоков 50 и 49, имеющих размеры соответственно x1 и x2 бит.

Блоки 40 и 29 имеют размеры соответственно y1≥x1 и y2≥x2 бит. Поэтому значения блоков 50 и 49 должны преобразоваться в значения блоков 40 и 29 согласно функциям f1 и f2, одинаковым на приемной и передающей сторонах. То есть y1=f1(x1), a y2=f2(x2).

УБ 3 управляет работой блоков 6, 7, 9, 11, 33, 44, 51-55 на основании управляющей программы, поступающей через И2 4.

С выхода ГТИ 26 на блоки 1, 3, 35, 44, 45, 6-13, 15-21, 23-25, 28, 29, 31-33, 37-42, 47-57, а также на СС 361-36k подаются тактовые импульсы, определяющие начало каждой микрооперации, в результате чего обеспечивается синхронизация работы устройства в целом.

БФА 31 может быть реализован в виде схем привязки синхросигнала к битовым интервалам принимаемых данных [5, глава 9]. БОЭС 35 может быть реализован как решающее устройство [6, глава 7.4]. СС 361-36k могут быть реализованы в виде дискретных согласованных фильтров [6, глава 7.4-7.5].

ПБ 13 и ПРБ 32 могут быть реализованы как процессоры семейства DSP56800 фирмы Motorola [7, стр.1-11, глава 5]. Блоки 24, 25, 38, 39 могут быть реализованы как любой из блочных или поточных шифров, описанных в [3].

СЧ может быть реализован как [9, глава 3.2], УПБ - как [9, глава 2]. Интерфейс может быть реализован как любой из стандартных стыков: С1-ФЛ, RS-232, USB, Ethernet IEEE 802.3, Ethernet IEEE 802.11 a/g, Ethernet IEEE 802.16, оптический канал.

ГКП может быть реализован как генератор М-последовательностей [6, глава 4]. Блоки 6, 9, 11 могут быть реализованы как мультиплексоры, а 33, 44 - как демультиплексоры, где в качестве адресного кода выступает сигнал, поступающий с УБ 3 [11].

Пакетатор и кодеки могут быть реализованы, например, как цифровые сигнальные процессоры, описанные в [10, глава 9], в том числе как комплект AD20msp430, содержащий два процессора, отвечающих за формирование пакетов протокола передачи данных, и выполняющий функции речевого и канального кодирования.

УБ 3 может быть реализован, например, как процессор на базе ядра SC140 Star*Core фирмы Motorola [7], который содержит устройство управления программами (УУП), включающее конвейер с пятью ступенями. Ядро SC140 имеет шестнадцать 40-разрядных универсальных регистров данных и двадцать семь 32-разрядных регистров адреса, в которых могут содержаться значения и адреса сигналов управления для блоков 6, 7, 9, 11, 33, 44, 51-55. Значение регистра данных, в которых содержится номер используемого кодека, поступает в блоки 7, 51-55, где на основании данного номера происходит кодирование и декодирование. Значение регистра данных, в которых содержится номер используемого вида информации (цифровой или аналоговый), поступает на блок 6, который открывает или закрывает соответствующий вход. Значения регистров данных, определяющие текущее состояние процесса передачи и приема (передача или прием временной метки или передача или прием данных), поступают (согласно программному контроллеру SC140, который выбирает команды и выполняет циклы) на блоки 9, 11, 33, 44, которые открывают или закрывают соответствующие входы.

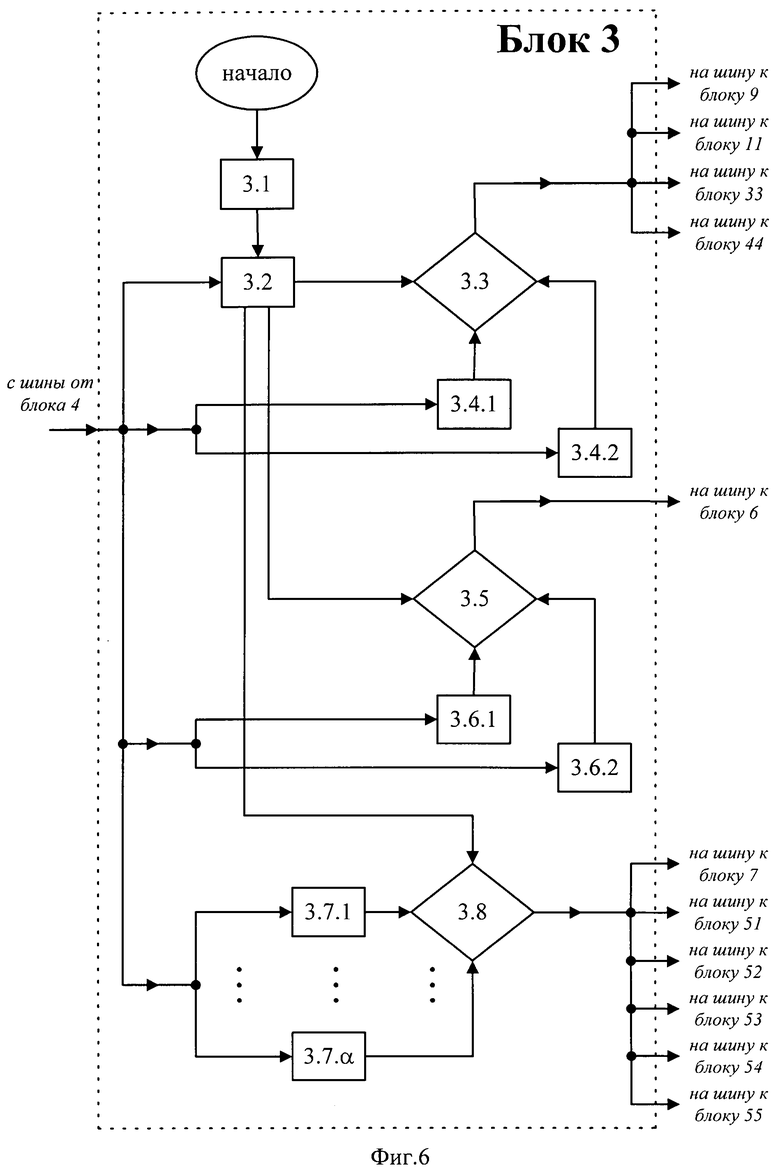

Алгоритм функционирования УБ 3 приведен на фиг.6.

Значения, содержащиеся в блоках 3.4.1, 3.4.2, 3.6.1, 3.6.2, 3.7.1-3.7.α, a также программа управления блока УУП 3.2 загружаются в УБ 3 с помощью интерфейса 4.

Работа УБ 3 начинается с запуска счетчика 3.1, на основании сигналов которого УУП 3.2 выдает сигналы управления на блоки мультиплексирования:

- 3.3, в результате чего определяется, какое из значений, содержащееся в блоках 3.4.1 или 3.4.2, выдается на выход УБ 3 на блоки 9, 11, 33, 44;

- 3.5, в результате чего определяется, какое из значений, содержащееся в блоках 3.6.1 или 3.6.2, выдается на выход УБ 3 на блок 6;

- 3.8, в результате чего определяется, какое из значений, содержащееся в блоках 3.7.1-3.7.α, выдается на выход УБ 3 на блоки 7, 51-55.

Таким образом, введение в предлагаемом устройстве новых блоков и связей позволяет обеспечить вхождение абонентов, вышедших из общего синхронного режима работы сети, обратно в сеть, что позволяет применять радиомодем в специальной связи в условиях несанкционированного доступа со стороны противника. Кроме того, наличие нескольких АФБ и БКЗ позволяет радиомодему вести не один, а более сеансы связи (например, обеспечивать связь в качестве мобильной точки доступа [8] между разными подсетями или выступать в качестве ретранслятора).

Источники информации

1. Патент РФ на изобретение №2155454 "Устройство, способ и программный модем для использования характеристик искажения, обусловленного групповой задержкой, для определения скорости передачи символов и частоты несущей для пересылки данных", Дж.Л.Моран III, С.Верма, В.Л.Браун, 1997 год.

2. Патент РФ на изобретение №2218666 "Цифровой модем", Агапова В.Н., Александров С.В., Бочков В.К., Захаренков В.Е., Кашлов В.В., Кирюхин М.С., Кольчугин А.И., Котлов В.Ф., Лавров Г.И., Лысиков А.В., Миронов Н.П., Прохоров А.Д., Султанов Б.В., Фунтиков В.А., Шутов С.Л., 2001 год.

3. Шнайер Б. Прикладная криптография. Протоколы, алгоритмы, исходные тексты на языке Си. - М.: Изд. ТРИУМФ, 2002.

4. Патент РФ на полезную модель №59918 "Радиомодем", 2006, Липский Р.Н., Шкуро Ю.В.

5. С.Н.Сухман, А.В.Бернов, Б.В.Шевкопляс. Синхронизация в телекоммуникационных системах. Анализ инженерных решений. - М.: Эко-Трендз, 2003.

6. Пестряков В.Б. Шумоподобные сигналы в системах передачи информации. М., Советское радио, 1973 г.

7. Техническое обеспечение цифровой обработки сигналов. Справочник. Куприянов М.С., Матюшкин Б.Д., Иванова В.Е., Матвиенко Н.И., Усов Д.Ю. - СПб. "Форт", 2000.

8. П.Рошан, Дж.Лиери. Основы построения беспроводных локальных сетей стандарта 802.11. Пер. с англ. - М.: Издательский дом "Вильямс", 2004.

9. Радиоприемные устройства, под ред. Л.Г.Барулина. - М., Радио и связь, 1984 г.

10. У.Кестер. Цифровая обработка сигналов. Analog Devices, 1999 г.

11. А.Г.Алексеенко, И.И.Шагурин. Микросхемотехника, 1990 г.

12. Борисов В.И. и др. Помехозащищенность систем радиосвязи с расширением спектра сигналов методом псевдослучайной перестройки рабочей частоты. - М.: Радио и связь, 2000.

| название | год | авторы | номер документа |

|---|---|---|---|

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| СПОСОБ ЗАЩИТЫ ИНФОРМАЦИИ В РАДИОСЕТИ С ПАКЕТНОЙ ПЕРЕДАЧЕЙ ДАННЫХ | 2009 |

|

RU2425455C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПЕРЕДАЧИ ДАННЫХ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2356171C1 |

| СПОСОБ АДАПТИВНОЙ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2007 |

|

RU2356167C1 |

| УСТРОЙСТВО РАДИОСВЯЗИ СО СКАЧКООБРАЗНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2005 |

|

RU2313178C2 |

| СПОСОБ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ С ПСЕВДОСЛУЧАЙНЫМИ СИГНАЛАМИ | 2005 |

|

RU2284666C1 |

| Устройство для приема дискретной информации | 1985 |

|

SU1285615A1 |

| ЦИФРОВОЙ МОДЕМ КОМАНДНОЙ РАДИОЛИНИИ ЦМ КРЛ | 2013 |

|

RU2548173C2 |

| СПОСОБ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ДИНАМИЧЕСКИ ИЗМЕНЯЕМОЙ ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2396713C1 |

| УСТРОЙСТВО ЗАСЕКРЕЧИВАНИЯ И МУЛЬТИПЛЕКСИРОВАНИЯ ТРАФИКА РЕЧИ И ДАННЫХ | 1998 |

|

RU2152134C1 |

Изобретение относится к области радиотехники и может быть использовано в адаптивных системах специальной радиосвязи для передачи данных по радиоканалу в условиях воздействия комплекса преднамеренных помех. Технический результат - обеспечение защищенного режима работы с самовосстановлением радиосети с пакетной передачей данных (РППД), состоящей из мобильных абонентов, при пассивных атаках противника. Устройство содержит аналого-цифровой преобразователь (1), интерфейсы (2, 4, 14, 22, 27, 43, 46), управляющий блок (3), кодеки (7, 51, 52, 53, 54, 55), антенно-фидерные блоки (5, 34), коммутаторы (6, 9, 11, 33, 44), сумматоры (8, 10, 41, 42), пакетатор (12), передающий блок (13), синтезаторы частот (15, 21, 56, 47), регистры (16, 17, 18, 19, 23, 29, 40, 49, 50), генератор кодовых последовательностей (20), блоки криптозащиты (24, 25, 38, 39), генератор тактовых импульсов (26), регистры сдвига (28, 57), усилительно-преобразовательный блок (30), блок фазовой автоподстройки (31), приемный блок (32), блок отождествления элемента сигнала (35), k схем сравнения (361…36k), мультиплексор (37), цифроаналоговый преобразователь (45), компаратор (48). В устройстве формируют, передают и принимают пакет, состоящий из криптографически защищенной информации с использованием комбинационного шифра, определяемого первым и вторым псевдослучайными числами (ПСЧ1 и ПСПЧ2), и синхропоследовательности, причем каждую из двух частей пакета модулируют разными частотами, определяемыми ПСПЧ2. 6 ил.

Радиомодем, содержащий первый кодек, третий и шестой интерфейсы и передающий блок, соединенный с первым антенно-фидерным блоком (АФБ), выход которого является выходом устройства, отличающийся тем, что введены последовательно соединенные первый интерфейс, аналого-цифровой преобразователь (АЦП) и первый коммутатор, выход которого соединен с первым входом первого кодека; последовательно соединенные первый сумматор, первый вход которого соединен с выходом первого кодека, второй коммутатор, второй сумматор, третий коммутатор и пакетатор, выход которого соединен с первым входом передающего блока; последовательно соединенные второй АФБ, вход которого является входом устройства, усилительно-преобразовательный блок (УПБ), блок фазовой автоподстройки (БФА), приемный блок, четвертый коммутатор, четвертый сумматор, третий сумматор, шестой кодек, пятый коммутатор, цифроаналоговый преобразователь (ЦАП) и седьмой интерфейс; последовательно соединенные четвертый интерфейс, пятый регистр, второй регистр, первый регистр и первый блок криптозащиты (БКЗ), выход которого соединен со вторым входом первого регистра, второй выход которого соединен со вторым входом второго регистра; последовательно соединенные пятый интерфейс, первый регистр сдвига, второй БКЗ, третий регистр и четвертый регистр, первый выход которого соединен со вторым входом третьего регистра, второй выход которого соединен со вторым входом второго блока криптозащиты; последовательно соединенные второй регистр сдвига, первый вход которого соединен со вторым выходом пятого интерфейса, третий БКЗ и шестой регистр; кроме того, введены управляющий блок, генератор тактовых импульсов, генератор кодовых последовательностей, четвертый БКЗ, блок отождествления элемента сигнала (БОЭС), мультиплексор, компаратор, k схем сравнения, а также первый, второй, третий и четвертый синтезаторы частот; второй интерфейс; второй, третий, четвертый и пятый кодеки; седьмой, восьмой и девятый регистры; при этом третий выход первого регистра соединен со вторым входом первого сумматора; третий выход третьего регистра соединен со вторым входом второго сумматора; второй выход второго регистра соединен с первым входом второго кодека, выход которого соединен со вторым входом второго коммутатора; второй выход четвертого регистра соединен с первыми входами первого и второго синтезаторов частот и третьего кодека, выход которого соединен со вторым входом третьего коммутатора; второй выход четвертого коммутатора соединен с первым входом пятого кодека, выход которого соединен с первым входом девятого регистра, выход которого соединен со вторым входом седьмого регистра, первый выход которого соединен со вторым входом четвертого БКЗ; второй выход седьмого регистра соединен со вторым входом третьего сумматора; третий выход четвертого коммутатора соединен с первым входом четвертого кодека, выход которого соединен с первым входом восьмого регистра, выход которого соединен с первыми входами третьего и четвертого синтезаторов частот и вторым входом шестого регистра, первый выход которого соединен со вторым входом третьего БКЗ; второй выход шестого регистра соединен со вторым входом четвертого сумматора; второй выход второго АФБ соединен с первым сигнальным входом БОЭС, выход которого соединен с сигнальными входами k схем сравнения, выходы которых соединены с соответствующими k сигнальными входами компаратора и мультиплексора; выход компаратора соединен с адресным входом мультиплексора, выход которого соединен со вторым входом БФА; кроме того, выход первого регистра сдвига соединен со вторым входом первого БКЗ, а выход второго регистра сдвига - с первым входом четвертого БКЗ, выход которого соединен с первым входом седьмого регистра; группа выходов второго интерфейса шиной соединена с группой информационных входов управляющего блока, первая группа выходов которого шиной соединена с группами управляющих входов первого коммутатора, первого, второго и третьего кодеков, второго и третьего коммутаторов, а вторая группа выходов управляющего блока шиной соединена с группами управляющих входов четвертого и пятого коммутаторов, а также четвертого, пятого и шестого кодеков; выход третьего синтезатора частот соединен со вторым входом УПБ, а выход четвертого синтезатора частот - со вторым входом БОЭС; выход третьего интерфейса соединен с третьим входом первого коммутатора; выход генератора кодовых последовательностей соединен со вторым входом пакетатора, второй выход пятого коммутатора соединен с шестым интерфейсом; второй выход второго коммутатора соединен с четвертым входом третьего коммутатора; второй выход четвертого интерфейса соединен со вторым входом четвертого регистра; выход первого синтезатора частот соединен со вторым входом передающего блока, а выход второго синтезатора частот - с третьим входом передающего блока; выход генератора тактовых импульсов соединен с тактовыми входами управляющего блока, компаратора, передающего и приемного блоков, БФА, АЦП, ЦАП, БОЭС, пакетатора, мультиплексора, генератора кодовых последовательностей, каждого из шести кодеков, каждого из шести коммутаторов, каждого из четырех сумматоров, каждого из девяти регистров, каждого из двух регистров сдвига, каждого из четырех синтезаторов частот, каждого из четырех блоков криптозащиты, каждой из k схем сравнения.

| RU 2007113104 A, 27.10.2008 | |||

| СПОСОБ ФОРМИРОВАНИЯ КЛЮЧА ШИФРОВАНИЯ-ДЕШИФРОВАНИЯ | 1994 |

|

RU2090006C1 |

| СПОСОБ ЗАЩИТЫ ИНФОРМАЦИИ И СИСТЕМА РАДИОСВЯЗИ С ПОВЫШЕННОЙ РАЗВЕДЗАЩИЩЕННОСТЬЮ | 2003 |

|

RU2253184C2 |

| СПОСОБ ПОТОЧНОГО ШИФРОВАНИЯ ДАННЫХ | 2001 |

|

RU2239290C2 |

| Фронтально-перекидной погрузчик | 1975 |

|

SU534419A1 |

Авторы

Даты

2012-01-10—Публикация

2010-06-01—Подача