Настоящее изобретение относится к электронным схемам. В частности, настоящее изобретение относится к новым и усовершенствованным способу и схеме для обеспечения сигналов сопряжения между интегральными схемами.

Многие электронные схемы реализуются с использованием нескольких интегральных схем (ИС), которые сопрягаются между собой для обеспечения необходимых функций системы. Во многих случаях сопряжение схем обеспечивается за счет цифровых сигналов, имеющих два логических уровня (например, высокий и низкий) для выражения цифровых значений. Цифровые сигналы широко используются для сопряжения по причине простоты их реализации и жесткой устойчивости к шуму.

Особые проблемы возникают при сопряжении цифровых ИС с аналоговыми ИС. Цифровые ИС более эффективны и требуют меньших затрат при реализации цифровых функций, например обработки цифровых сигналов и т.п. Аналоговые схемы используются для обеспечения линейных функций, например усиления сигнала, буферизации, фильтрации, модуляции, смешения и т.д. Многие схемные решения предусматривают реализацию сопряжения между цифровыми и аналоговыми ИС с использованием цифровых сигналов. В аналоговой ИС цифровые сигналы буферизуются, преобразуются, в случае необходимости, в аналоговый(е) сигнал(ы) и поступают на аналоговую(ые) цепь(и).

Во многих приложениях использование цифровых сигналов для сопряжения цифровых и аналоговых ИС по некоторым причинам нежелательно. Во-первых, цифровые сигналы имеют большой размах и резкие переходные фронты и потому генерируют большой коммутационный шум. Этот шум может ухудшать характеристики аналоговых схем, которые обычно работают при меньшем размахе сигнала. Величину шума можно несколько уменьшить, используя раздельные источники питания и средства заземления для аналоговых и цифровых цепей в аналоговой ИС. Однако для некоторых приложений такое снижение может оказаться недостаточным. Во-вторых, поскольку каждый цифровой сигнал обычно обеспечивает один бит данных, то для обеспечения нескольких, например восьми, битов данных требуется несколько, например, восемь, цифровых сигналов. Кроме того, для защелкивания битов данных на принимающей ИС обычно предусматривают один или несколько тактовых сигналов. Таким образом, для согласования ИС может потребоваться большое количество линий сигнала и соответствующее количество ножек схемы. Кроме того, с увеличением количества линий цифровых сигналов обычно возрастает коммутационный шум.

Вышеупомянутые причины обуславливают необходимость в способе обеспечения усовершенствованного сопряжения между ИС с использованием меньшего количества линий сигнала, генерирующих пониженный шум. Желательно также, чтобы для реализации сопряжения не требовалось сложных схем.

Настоящее изобретение предусматривает способ сопряжения цифровой ИС и аналоговой ИС. Согласно одному аспекту изобретения, одна или несколько схем сопряжения, реализованные на цифровой ИС, принимают входные сигналы данных и выдают соответствующие сигналы сопряжения, поступающие на аналоговую ИС. В некоторых вариантах сопряжения (например, по модулирующим сигналам) используются дифференциальные токовые сигналы, имеющие разрешение в несколько битов. Для реализации этих сигналов требуется меньшее количество линий сигнала, и они создают меньший шум по сравнению с цифровыми сигналами. Для генерации сигналов сопряжения может быть предусмотрен опорный сигнал.

Вариант осуществления изобретения предусматривает схему для генерации сигнала сопряжения между первой и второй интегральными схемами. Схема содержит схему опорного сигнала, схему сопряжения и схемный элемент. Схема опорного сигнала выдает опорный сигнал. Схема сопряжения реализована на первой интегральной схеме, в ходе эксплуатации подключается к схеме опорного сигнала, принимает опорный сигнал, и входной сигнал данных и генерирует сигнал сопряжения. Схемный элемент реализован на второй интегральной схеме, в ходе эксплуатации подключается к схеме управления, принимает сигнал сопряжения и выдает выходной сигнал.

Согласно варианту осуществления, схема сопряжения содержит токовое зеркало, подключенное к массиву переключателей. Токовое зеркало принимает опорный сигнал и содержит два или более зеркальных трактов. Массив переключателей принимает и декодирует входной сигнал данных и направляет ток из выбранного набора зеркальных трактов на выход массива переключателей.

Опорный сигнал может представлять собой сигнал напряжения или сигнал тока (т.е. генерируемый на основании опорного напряжения) и может генерироваться схемой опорного сигнала, реализованной на первой или (что предпочтительно в ряде приложений) на второй интегральной схеме. Согласно варианту осуществления, сигнал сопряжения является дифференциальным токовым сигналом, имеющим разрешение в несколько (например, четыре, восемь или более) битов и фильтрованным RC-цепью. Схема сопряжения может работать в режиме передискретизации для упрощения требований к фильтрации. В иллюстративном варианте осуществления сигнал сопряжения представляет синфазный (I) или квадратурный (Q) модулирующий сигнал в квадратурном передатчике или сигнал управления. Схемный элемент может представлять собой, например, УРУ, модулятор или иную схему.

Другой вариант осуществления изобретения предусматривает схемы передатчика, в том числе первую схему сопряжения (и в некоторых приложениях вторую схему сопряжения), в ходе эксплуатации подключаемые к модулятору. Первая (и вторая) схема сопряжения реализована на первой интегральной схеме, принимает первый (или второй) входной сигнал данных и выдает первый (или второй) дифференциальный токовый сигнал. Модулятор реализован на второй интегральной схеме, принимает первый (и второй) дифференциальный токовый сигнал и несущий сигнал и генерирует соответствующий выходной сигнал. Каждый входной сигнал данных представляет цифровой модулирующий сигнал и может иметь разрешение в четыре, восемь или более битов. Схема опорного сигнала может быть реализована на второй (возможно, первой) интегральной схеме для выдачи опорного сигнала. Схемы сопряжения генерируют дифференциальный токовый сигнал на основании, отчасти, опорного сигнала.

Еще один вариант осуществления изобретения предусматривает передатчик сотового телефона (например, системы МДКР), который содержит цифровой процессор, первую и вторую интегральные схемы и модулятор. Цифровой процессор реализован на первой интегральной схеме и выдает цифровые синфазный (I) и квадратурный (Q) модулирующие сигналы. Первая и вторая схемы сопряжения реализованы на первой интегральной схеме и подключены к цифровому процессору. Каждая схема сопряжения принимает соответствующий цифровой модулирующий сигнал и выдает аналоговый модулирующий сигнал. Каждый аналоговый модулирующий сигнал имеет разрешение, по меньшей мере, четыре бита и реализован в виде дифференциального токового сигнала. Модулятор реализован на второй интегральной схеме, оперативно подключается к первой и второй схемам сопряжения и принимает и модулирует аналоговыми модулирующими сигналами сигнал несущей, выдавая модулированный выходной сигнал. Передатчик также может содержать схему опорного сигнала, выдающую опорный сигнал. В этом случае схемы сопряжения принимают опорный сигнал и генерируют аналоговые модулирующие сигналы на основании, отчасти, опорного сигнала.

Еще один вариант осуществления изобретения предусматривает способ обеспечения сигнала сопряжения с первой интегральной схемы на вторую. Согласно способу, опорный сигнал генерируют либо на первой, либо на второй интегральной схеме и подают на первую интегральную схему. Входной сигнал данных также принимают на первой интегральной схеме и используют совместно с опорным сигналом для генерации сигнала сопряжения. Сигнал сопряжения подают с первой интегральной схемы на вторую интегральную схему. Схемный элемент, входящий в состав второй интегральной схемы, принимает сигнал сопряжения и генерирует соответствующий выходной сигнал. Схемный элемент может также принимать сигнал, связанный с опорным сигналом, и может генерировать выходной сигнал на основании, отчасти, этого принятого сигнала.

Существенные признаки, характер и преимущества настоящего изобретения явствуют из нижеследующего подробного описания, приведенного в сочетании с чертежами, в которых используется сквозная нумерация, и где:

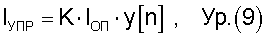

фиг.1 - упрощенная блок-схема варианта осуществления квадратурного передатчика;

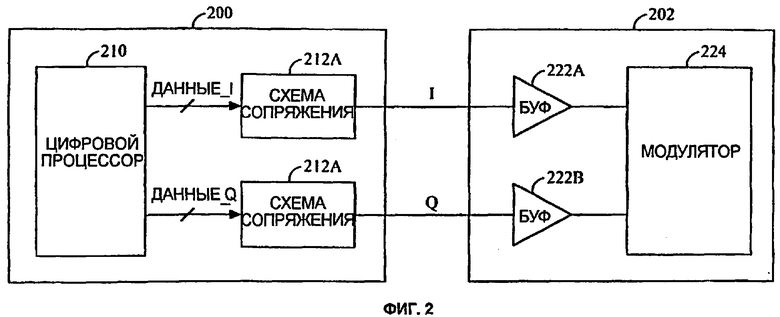

фиг.2 - блок-схема варианта осуществления сопряжения между цифровой ИС и аналоговой ИС для модулирующих сигналов I и Q;

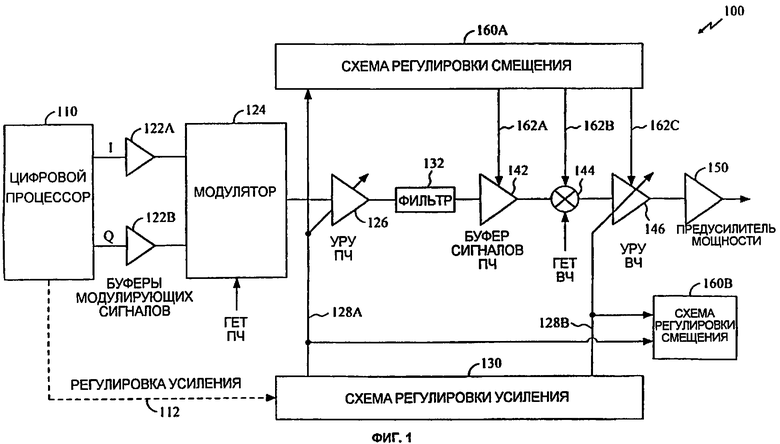

фиг.3 - схема варианта осуществления схемы сопряжения;

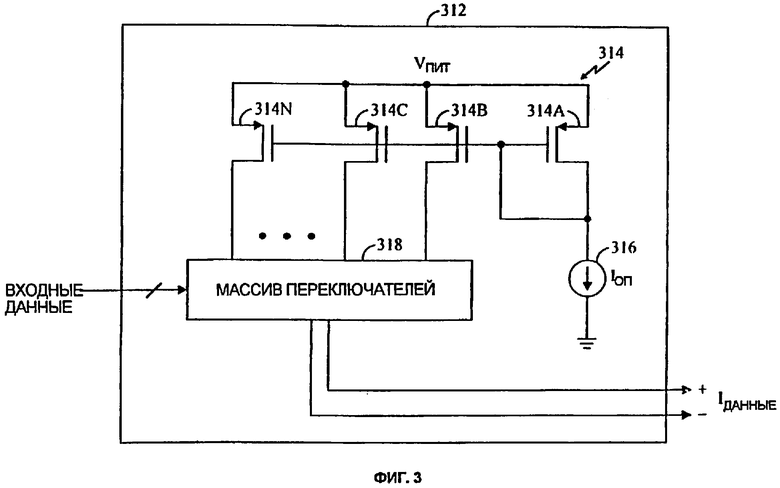

фиг.4 - блок-схема другого варианта осуществления сопряжения между цифровой ИС и аналоговой ИС по модулирующим сигналам I и Q;

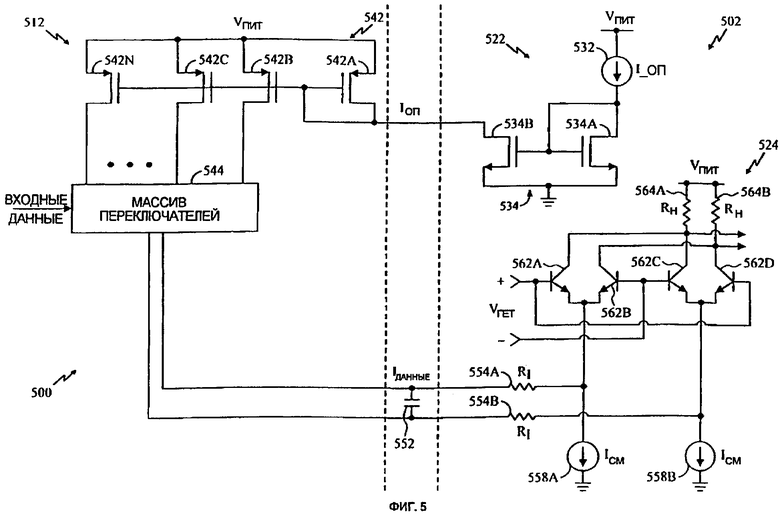

фиг.5 - схема конкретного варианта осуществления сопряжения и схем, показанных на фиг.4;

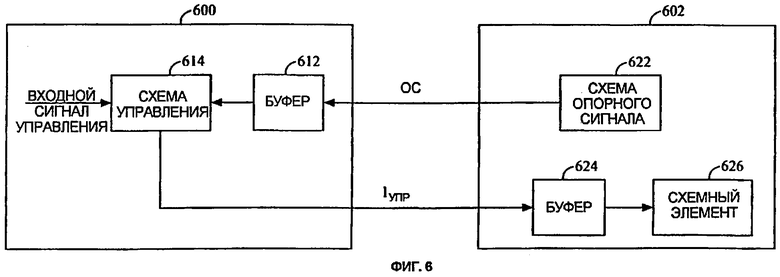

фиг.6 - блок-схема варианта осуществления схем, используемых для генерации сигнала управления согласно изобретению.

Изобретение можно реализовать в различных электронных схемах и системах. Для ясности, опишем изобретение применительно к конкретной реализации в передатчике системы сотовой связи.

На фиг.1 изображена упрощенная блок-схема варианта осуществления квадратурного передатчика 100. Цифровой процессор 110 генерирует данные, кодирует данные и преобразует данные, подвергнутые цифровой обработке, в синфазный (I) и квадратурный (Q) модулирующие сигналы. Модулирующие сигналы поступают на буферы 122а и 122b модулирующего сигнала, которые буферизуют сигналы и выдают буферизованные сигналы на модулятор 124. Модулятор 124 также принимает сигнал (например, несущий синусоидальный сигнал) промежуточной частоты (ГЕТ ПЧ) и модулирует сигнал ГЕТ ПЧ буферизованными модулирующими сигналами, генерируя модулированный сигнал ПЧ. Модулятор 124 может представлять собой модулятор с одной боковой полосой или с двумя боковыми полосами. В случае модулятора с одной боковой полосой, для генерации сигналов ГЕТ ПЧ с нужными фазами можно использовать один или несколько фазовращателей. Сигнал ПЧ поступает на усилитель 126 ПЧ с регулируемым усилением (УРУ ПЧ), который усиливает сигнал с коэффициентом усиления, регулируемым сигналом 128а регулировки усиления, поступающим от схемы 130 регулировки усиления. Усиленный сигнал ПЧ поступает на фильтр 132, который фильтрует сигнал ПЧ для удаления внеполосного шума и паразитных сигналов.

Фильтрованный сигнал ПЧ поступает на буфер 142 ПЧ, который буферизует сигнал и выдает буферизованный сигнал ПЧ на смеситель 144. Смеситель 144 также принимает сигнал (например, несущий синусоидальный сигнал) высокой частоты (ГЕТ ВЧ) и преобразует с повышением частоты буферизованный сигнал ПЧ с помощью сигнала ГЕТ ВЧ, генерируя сигнал ВЧ. Смеситель 144 также может представлять собой смеситель с одной боковой полосой и с двумя боковыми полосами. Вариант осуществления смесителя с одной боковой полосой может предусматривать наличие фазовращателей на трактах ГЕТ ПЧ и ВЧ. Сигнал ВЧ поступает на УРУ ВЧ 146, который усиливает сигнал с коэффициентом усиления, регулируемым сигналом 128b регулировки усиления, поступающим от схемы 130 регулировки усиления. Усиленный сигнал ВЧ поступает на предусилитель 150 мощности (ПУМ), который, в свою очередь, сопрягается с другими цепями, например внешним фильтром (например, для отфильтровки зеркальных боковых полос и паразитных сигналов) и усилителем мощности (оба эти элемента на фиг.1 не показаны). ПУМ обеспечивает необходимое предварительное усиление мощности, и его выходной сигнал поступает на антенну через вентиль и дуплексер (эти элементы на фиг.1 не показаны).

Вариант осуществления, показанный на фиг.1, допускает различные модификации. Например, на тракте передачи сигнала можно устанавливать меньше или больше каскадов фильтрации, буферизации и усиления. Некоторые компоненты, указанные на фиг.1, в некоторых вариантах осуществления могут не использоваться. Кроме того, можно изменять порядок расположения элементов на тракте передачи сигнала. Кроме того, регулировку усиления на тракте передачи сигнала можно осуществлять не только посредством УРУ (как показано на фиг.1), но и регулируемых аттенюаторов, умножителей, других элементов регулировки усиления или их комбинации. Кроме того, можно использовать прямое преобразование с повышением частоты, при котором модулирующие сигналы напрямую преобразуются с повышением частоты в сигнал ВЧ.

Передатчик 100 можно использовать во многих приложениях связи, например в системах сотовой связи. Примерами систем сотовой связи могут служить системы связи множественного доступа с кодовым разделением (МДКР), системы связи множественного доступа с временным разделением (МДВР) и системы связи с аналоговой ЧМ. Использование методов МДКР в системе связи множественного доступа раскрыто в патенте США 4301307, озаглавленном «Система связи множественного доступа с расширением по спектру, содержащая спутниковые или наземные ретрансляторы», и в патенте США 5103459, озаглавленном «Система и способ создания форм волны в системе сотовой телефонии МДКР», которые оба принадлежат правообладателю настоящего изобретения и включены в данное описание посредством ссылки. В основе большинства систем МДКР лежит стандарт «TIA/EIA/IS-95-A Стандарт совместимости мобильной станции и базовой станции для двухрежимной широкополосной системы сотовой связи с расширением по спектру», именуемый здесь стандартом IS-95-A, который также включен в настоящее описание посредством ссылки.

Согласно фиг.1, токи смещения для некоторых элементов на тракте передачи сигнала можно регулировать на основании сигналов регулировки усиления, генерируемых схемой 130 регулировки усиления. Например, схема 160а регулировки смещения может регулировать каждый из токов смещения буфера 142 ПЧ, смесителя 144 и УРУ ВЧ 146 посредством соответствующих сигналов 162а, 162b и 162с регулировки смещения, генерируемых на основании значения сигнала 128а регулировки усиления. Аналогично, схема 160b регулировки смещения может регулировать ток смещения предусилителя мощности 150 посредством сигнала 162b регулировки смещения, генерируемого на основании сигнала 128а или 128b регулировки усиления или обоих. Сигналы 128а и 128b регулировки усиления можно генерировать на основании сигнала 112 регулировки усиления, который может поступать от цифрового процессора 110 (что показано на фиг.1 пунктирной линией) или иного источника сигнала управления.

Согласно варианту осуществления, тракт передачи сигнала от буферов 122 МС на ПУМ 150 (возможно, без использования фильтра 132) реализуется в одной или нескольких (например, аналоговых) интегральных схемах. Согласно варианту осуществления, цифровой процессор реализован на другой (например, цифровой) интегральной схеме. Схемы регулировки усиления и смещения могут быть реализованы на той же интегральной схеме, что и цифровой процессор, на интегральной(ых) схеме(ах), используемой(ых) для реализации тракта передачи сигнала, или на отдельной интегральной схеме. Таким образом, можно обеспечивать сигналы сопряжения по модулирующим сигналам, выдаваемым цифровым процессором, и сигналам управления (например, усилением и смещением), поступающим от схем управления.

Согласно фиг.1, каждый из модулирующих сигналов I и Q может иметь разрешение в несколько бит. Этого можно добиться, например, фильтрацией двухуровневого цифрового сигнала с помощью цифрового фильтра. Таким образом, для сопряжения цифрового процессора с аналоговыми схемами может потребоваться несколько линий сигнала.

Согласно одной традиционной конструкции, каждый из модулирующих сигналов I и Q имеет разрешение восемь бит, и сопряжение содержит восемь линий сигнала данных и две линии тактового сигнала. Линии сигнала данных совместно используются сигналами I и Q с разделением по времени. Линии тактового сигнала обеспечивают два тактовых сигнала, сдвинутых по фазе относительно друг друга (например, на 180 градусов). Линии сигнала данных используются для обеспечения сигнала I на одной фазе тактового сигнала и сигнала Q на другой фазе тактового сигнала. При такой конструкции линии сигнала данных и тактового сигнала генерируют шум, который может ухудшать характеристики аналоговых схем на тракте передачи сигнала. Кроме того, линии (десять) сигнала данных и тактового сигнала требуют соответствующего количества ножек на цифровой и аналоговой ИС.

На фиг.2 показана блок-схема варианта осуществления сопряжения между цифровой ИС 200 и аналоговой ИС 202 по модулирующим сигналам I и Q. Согласно фиг.2, цифровой процессор 210, входящий в состав ИС 200, выдает сигналы данных I и Q на соответствующие схемы 212а и 212b сопряжения. Согласно одному варианту осуществления, каждый из сигналов данных I и Q содержит множественные биты данных. Каждая схема 212 сопряжения принимает соответствующий входной сигнал данных, преобразует сигнал данных в аналоговый модулирующий сигнал и выдает аналоговый модулирующий сигнал на ИС 202. На ИС 202 модулирующие сигналы I и Q поступают на буферы 222а и 222b соответственно, и буферизованные сигналы поступают на модулятор 224.

На фиг.3 показана схема варианта осуществления схемы 312 сопряжения. Одну схему сопряжения 312 можно использовать для реализации каждой из схем 212а и 212b сопряжения, показанных на фиг.2. Согласно этому варианту осуществления, схема 312 сопряжения содержит набор р-канальных транзисторов 314а-314n, образующих токовое зеркало 314. Затворы транзисторов 314а-314n соединены между собой, а истоки также соединены между собой и с линией питания VПИТ. Сток транзистора 314а подключен к затвору транзистора 314а и источнику 316 тока, который выдает опорный ток IОП. Каждый из транзисторов 314b-314n способен выдавать тот или иной «зеркальный» ток, пропорциональный опорному току IОП. Коэффициент пропорциональности (масштабный коэффициент) для конкретного зеркального тракта зависит от отношения размера транзистора на этом тракте к размеру транзистора 314а. Например, если размер транзистора 314b вдвое больше размера транзистора 314а, то ток через транзистор 314b будет примерно вдвое больше опорного тока IОП.

Массив 318 переключателей подключен к транзисторам 314b-314n. Массив 318 переключателей также принимает и декодирует входной сигнал данных и активирует набор переключателей в массиве, которые избирательно направляют ток транзисторов 314b-314n на выход массива. Входной сигнал данных может представлять собой сигнал I данных или сигнал Q данных, показанные на фиг.2. Согласно варианту осуществления, массив 318 переключателей содержит схему, генерирующую дифференциальный токовый сигнал IДАННЫЕ в качестве выходного сигнала схемы 312 сопряжения.

Использование схем 312 сопряжения, выдающих модулирующие сигналы I и Q на аналоговую ИС, обеспечивает многочисленные преимущества. Ниже описаны некоторые из этих преимуществ.

Во-первых, для обеспечения дифференциальных токовых сигналов, соответствующих модулирующим сигналам I и Q, требуется только два набора линий дифференциального сигнала (т.е. всего четыре линии). Для сравнения, традиционная конструкция предусматривает восемь линий цифровых данных и две линии тактового сигнала. Ввиду меньшего количества линий сигнала, уменьшается количество ножек, необходимых для сопряжения ИС.

Во-вторых, дифференциальный токовый сигнал IДАННЫЕ обычно имеет низкий импеданс и ограниченный (или сниженный) размах. Для сравнения, цифровые сигналы, предусмотренные вышеупомянутой традиционной конструкцией, имеют большой размах сигнала и резкие переходные фронты. Таким образом, дифференциальные токовые сигналы порождают значительно меньший шум, чем цифровые сигналы.

В-третьих, использование дифференциальных токовых сигналов позволяет упростить схему на исходной и конечной ИС.

Для повышения характеристик (например, достижения широкой полосы пропускания, линейности и т.д.) многие высокоскоростные аналоговые схемы рассчитаны на работу с разными токовыми сигналами. Благодаря подаче дифференциального токового сигнала на аналоговую ИС (вместо сигналов напряжения или цифровых сигналов), в аналоговой ИС можно исключить схемы буферизации и преобразования напряжения в ток, что упрощает ее конструкцию.

Для системы МДКР, отвечающей техническим условиям IS-95-A, каждый из сигналов данных, I и Q, имеет битовую скорость 1,2288 Мбит/с. Согласно варианту осуществления, сигналы I и Q данных подвергают передискретизации и фильтрации (например, на цифровом процессоре) для обеспечения фильтрованных сигналов данных I и Q соответственно. Известно, что генерация аналогового сигнала из дискретизированного сигнала данных порождает зеркальные боковые полосы на частоте дискретизации. Благодаря передискретизации сигналов I и Q данных (например, с коэффициентом 16), зеркальные боковые полосы смещаются в сторону более высоких частот с коэффициентом, равным коэффициенту передискретизации (в данном случае, 16), что упрощает фильтрацию зеркальных боковых полос. Передискретизация позволяет отфильтровывать зеркальные боковые полосы с помощью простой RC-цепи, что описано ниже.

Для многих интегральных схем вариации в процессе изготовления затрудняют генерацию точных значений компонентов (например, точных значений резисторов и конденсаторов). Однако согласование компонентов обычно бывает весьма высоким, поскольку вся ИС обычно находится в аналогичных условиях процесса. Таким образом, хотя часто бывает трудно изготовить резистор, значение которого в точности попадает в пределы допуска ±30 процентов от номинала, вполне возможно согласовать два резистора в пределах допуска в несколько процентов.

Даже при изменениях процесса изготовления, схемы, входящие в состав аналоговой ИС, должны удовлетворять техническим условиям. Для обеспечения согласования характеристик при переходе от одной ИС к другой можно предусмотреть, чтобы схемы могли, в ходе эксплуатации, использовать опорный сигнал (или опорное значение), который(ое) можно точно генерировать на ИС. Для электронных схем можно предусмотреть схему опорного межпорогового напряжения для выдачи (относительно) точного опорного напряжения (даже при изменениях процесса). Кроме того, опорное межпороговое напряжение обычно бывает стабильным при изменениях времени, напряжения питания и температуры. Опорное межпороговое напряжение можно использовать для генерации других опорных напряжений - и токов, используемых схемами, входящими в состав ИС.

На фиг.4 показана блок-схема другого варианта осуществления сопряжения между цифровой ИС 400 и аналоговой ИС 402 по модулирующим сигналам I и Q. Согласно фиг.4, цифровой процессор 410, входящий в состав ИС 400, выдает сигналы I и Q данных на схемы 412а и 412b сопряжения соответственно. Каждая схема 412 сопряжения принимает соответствующий входной сигнал данных и опорный сигнал ОС от схемы 422 опорного сигнала, входящей в состав ИС 402, преобразует сигнал данных в аналоговый сигнал (например, используя, отчасти, опорный сигнал ОС) и выдает аналоговый сигнал на буфер и модулятор 424, входящие в состав ИС 402. Копия опорного сигнала ОС или сигнал, связанный с ним, может также поступать со схемы 422 опорного сигнала на буфер и модулятор 424, что указано пунктирной линией.

Опорный сигнал ОС может, в общем случае, представлять собой опорное напряжение (например, опорное межпороговое напряжение) или опорный ток. Обеспечив работу схемы сопряжения и модулятора на основании общего опорного сигнала, можно сделать так, чтобы эти схемы согласовывались друг с другом по параметрам, компенсируя их разброс, обусловленный изменениями процесса на соответствующих ИС, в состав которых они входят, что описано ниже.

На фиг.5 показана схема конкретного варианта осуществления сопряжения и схем, показанных на фиг.4. Согласно фиг.5, цифровая ИС 500 содержит схему 512 сопряжения, подключенную к схеме 522 опорного сигнала и модулятору 524, входящим в состав аналоговой ИС 502. Схема 522 опорного сигнала, схема 512 сопряжения и модулятор 524 соответствуют схеме опорного сигнала 422, схеме 412 сопряжения и модулятору 424, соответственно изображенным на фиг. 4.

Согласно варианту осуществления, схема 522 опорного сигнала содержит источник 532 тока, подключенный к токовому зеркалу 534. Согласно варианту осуществления, источник 532 тока выдает опорный ток I_ОП, генерируемый путем подачи опорного межпорогового напряжения через резистор. Резистор может быть внешним (т.е. дискретным) резистором или внутренним резистором, изготовленным на ИС 502, причем выбор зависит от нужных характеристик схемы и ее функций, что описано ниже. Опорный ток I_ОП поступает на опорный тракт (т.е. через n-канальный транзистор 534а) токового зеркала 534. Ток через зеркальный тракт (т.е. через n-канальный транзистор 534b) содержит опорный ток IОП, поступающий на ИС 500. В общем случае IОП пропорционален I_ОП с коэффициентом пропорциональности, определяемым отношением размера транзистора 534b к размеру транзистора 534а.

В ИС 500 опорный ток IОП поступает на схему 512 сопряжения. Согласно варианту, схема 512 сопряжения содержит токовое зеркало 542, подключенное к массиву 544 переключателей. В частности, опорный ток IОП поступает на опорный тракт (т.е. через р-канальный транзистор 542а) токового зеркала 542. Поскольку напряжение исток-затвор транзисторов 542a-542n примерно одинаково, ток через каждый зеркальный тракт (т.е. через транзисторы 542b-542n) связан с током IОП через опорный тракт (т.е. через транзистор 542а). Коэффициент пропорциональности определяется отношением размера транзистора того или иного зеркального тракта к размеру транзистора 542а. Транзисторы 542b-542n могут иметь такие размеры, чтобы обеспечивать примерно одинаковый ток на всех зеркальных трактах (например, 1, 1, 1 и т.д.), экспоненциально возрастающие токи (например, 1, 2, 4 и т.д.) или другие наборы значений тока.

Массив 544 переключателей подключен к транзисторам 542b-542n и также принимает входной сигнал данных. Массив 544 переключателей декодирует входной сигнал данных и на основании декодированного сигнала данных избирательно направляет токи с зеркальных трактов на выход массива переключателей. Токовый сигнал IДАННЫЕ поступает от массива 544 переключателей на ИС 502. Согласно одному варианту осуществления и фиг.5, для повышения устойчивости к шумам выходной ток обеспечивают в виде дифференциального токового сигнала.

Схема 512 сопряжения действует наподобие цифроаналогового преобразователя (ЦАП). В результате, восстановленный выходной сигнал схемы 512 сопряжения содержит зеркальные боковые полосы на частотах n·fд, где fд - частота дискретизации (т.е. битовая скорость входного сигнала данных), и n=1, 2, 3, .... Схема 512 сопряжения может работать в режиме передискретизации (например, с коэффициентом 2, 4, 8, 16 или в иных отношениях передискретизации), чтобы отраженные боковые полосы восстановленного сигнала смещались в область более высоких частот для облегчения фильтрации.

Согласно фиг.5, токовый сигнал IДАННЫЕ фильтруется КС-цепью для удаления нежелательного шума и зеркальных боковых полос, обычно присутствующих в выходном сигнале цифроаналогового преобразователя. В частности, конденсатор 522 подключен между линиями дифференциального токового сигнала IДАННЫЕ, которые, в свою очередь, подключены к резисторам 554а и 554b. Конденсатор 552 и резисторы 554 могут быть внешними (т.е. дискретными) компонентами или внутренними компонентами, реализованными в ИС (т.е. ИС 500 или 502 или обеих). Согласно варианту осуществления, конденсатор 552 является внешним компонентом (т.е. имеющим значение, превышающее значение, которое можно практически реализовать в ИС), а резисторы 554 являются внутренними компонентами, реализованными в ИС 502.

Другие концы резисторов 544а и 544b подключены к источникам 558а и 558b тока, соответственно входящим в состав модулятора 524. Согласно варианту осуществления, каждый источник тока 558 выдает ток смещения 1 см, связанный с опорным током I_ОП, что описано ниже. Модулятор 524 также содержит пару дифференциальных усилителей. Первый дифференциальный усилитель содержит транзисторы 562а и 562b, эмиттеры которых соединены друг с другом и с источником 558а тока. Второй дифференциальный усилитель содержит транзисторы 562с и 562d, эмиттеры которых соединены между собой и с источником 558b тока. Базы транзисторов 562а и 562d соединены друг с другом и принимают положительную полуволну несущего сигнала VГЕТ+, и базы транзисторов 562b и 562с соединены друг с другом и принимают отрицательную полуволну несущего сигнала VГЕТ-. Коллекторы транзисторов 562а и 562с соединены между собой и с резистором 564а, который, в свою очередь, подключен к линии питания VПИТ. Коллекторы транзисторов 562b и 562d соединены между собой и резистором 564b, который, в свою очередь, подключен к линии питания VПИТ. Дифференциальные напряжения на резисторах 564а и 564b образуют выходной сигнал напряжения VВЫХ модулятора 524.

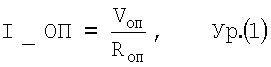

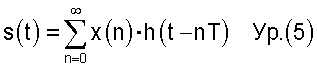

Согласно варианту осуществления, опорный ток I_ОП зависит от опорного межпорогового напряжения, поступающего от схемы опорного межпорогового напряжения (не показана на фиг.5). Согласно варианту осуществления, опорное межпороговое напряжение поступает через внешний резистор (т.е. дискретный резистор, внешний по отношению к ИС 502) для генерации опорного тока I_ОП, который можно выразить следующим образом:

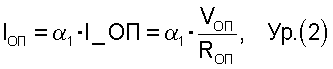

где VОП - опорное межпороговое напряжение, и RОП - значение внешнего опорного резистора. Использование внешнего резистора позволяет генерировать точный опорный ток I_ОП, поскольку дискретные резисторы с допуском 1,0 (или 0,1) процент легко доступны. Опорный ток IОП пропорционален опорному току I_ОП в соответствии с конкретной конструкцией токового зеркала 534, что можно выразить следующим образом:

где α1 - масштабный коэффициент, связанный с токовым зеркалом 534.

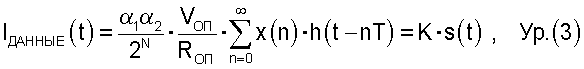

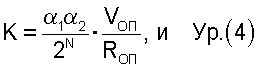

Схема 512 сопряжения генерирует дифференциальный токовый сигнал IДАННЫЕ, который является масштабированной версией опорного тока IОП. Масштабный коэффициент определяется входным сигналом данных и конкретной конструкцией токового зеркала 542 (т.е. размерами транзисторов 542a-542n). В частности, отношение размеров каждого из транзисторов 542b-542n к размеру транзистора 542а определяет величину тока, переключаемого каждым трактом тока. Входной сигнал данных определяет, какие из переключателей массива 544 переключателей должны активироваться, и, таким образом, тракт(ы) тока, подлежащие подаче на выход массива переключателей. Токовый сигнал IДАННЫЕ можно теоретически выразить следующим образом:

где x[n] - значение входного сигнала данных, h(t) - отклик нулевого порядка ЦАП, N - разрядность входного сигнала данных, α2 - масштабный коэффициент, связанный с токовым зеркалом 542,

Для восьмиразрядного входного сигнала данных х[n] принимает значения от 0 до 255, и 2N равно 256.

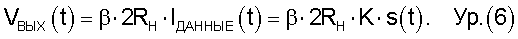

Модулятор 524 генерирует сигнал напряжения VВЫХ на основании токового сигнала IДАННЫЕ несущего сигнала VГЕТ нагрузочного резистора RH и коэффициента β усиления или преобразования модулятора. Сигнал напряжения можно выразить следующим образом:

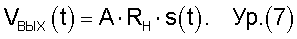

Сгруппировав константы, уравнение (6) можно выразить в виде:

Из уравнения (7) следует, что сигнал напряжения VВЫХ является функцией отношения RH к RОП входного сигнала данных х[n], опорного межпорогового напряжения VОП и масштабного коэффициента А, объединяющего в себе различные коэффициенты. Масштабный коэффициент А содержит масштабные коэффициенты α1 и α2, связанные с токовыми зеркалами 534 и 542 соответственно. Эти масштабные коэффициенты можно задавать точно, поскольку они определяются отношениями размеров транзисторов, которые можно согласовать (обычно с точностью в несколько процентов), применяя методы хорошей компоновки схемы. Обычно опорное межпороговое напряжение VОП и внешний опорный резистор RОП можно задавать точно.

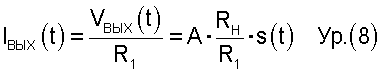

Согласно вышесказанному, значение внутреннего резистора RH нельзя задать с высокой степенью точности, и оно может варьироваться в пределах 30 или более процентов от ИС к ИС в силу различий в процессе. Таким образом, сигнал напряжения VВЫХ может варьироваться в широких пределах от ИС к ИС. Однако сигнал напряжения VВЫХ обычно преобразуется в токовый сигнал VВЫХ для использования в последующей схеме, и преобразование V-I достигается за счет подачи VВЫХ через другой внутренний резистор R1. Токовый сигнал VВЫХ можно выразить следующим образом:

Из уравнения (8) следует, что токовый сигнал VВЫХ является функцией отношения внутренних резисторов RH к R1, которое обычно можно задать с точностью в один процент, следуя принципам хорошей компоновки схемы.

Для вариантов реализации, в которых сигнал напряжения VВЫХ используется напрямую (т.е. без преобразования V-I), точное VВЫХ при изменениях процесса можно генерировать с использованием внутреннего опорного резистора ROH. Согласно уравнению (7), сигнал напряжения VВЫХ зависит от отношения резисторов RH к RОП, которые можно точно задать в пределах нескольких процентов, если оба резистора внутренне реализованы на одной и той же ИС.

Таким образом, опорный резистор RОП может быть внутренним или внешним, в зависимости от требуемых характеристик схемы. Сигнал напряжения VВЫХ или сигнал тока VВЫХ можно генерировать так, чтобы они зависели, главным образом, от коэффициентов, которые можно точно задавать и которые, в основном, не подвержены влиянию изменений процесса. Для генерации сигнала напряжения VВЫХ, который остается точным при изменениях процесса, используется внешний опорный резистор, а для генерации сигнала тока VВЫХ, который остается точным при изменениях процесса, используется внутренний опорный резистор.

Согласно конкретному варианту осуществления модулятора 524, изображенного на фиг.5, источник 558а тока обеспечивает «сток» тока для дифференциального смесителя (состоящего из транзисторов 562а и 562b) и токовый сигнал IДАННЫЕ+ через резистор 554а. Согласно вышеуказанному, токовый сигнал IДАННЫЕ связан с опорным током IОП. Если токовый сигнал IДАННЫЕ возрастает вследствие увеличения опорного тока IОП, величина тока через дифференциальный смеситель соответственно снижается, если ток смещения IСМ остается постоянным, что приводит к запиранию смесителя при положительных значениях IДАННЫЕ. Характеристики (например, полоса пропускания, линейность и т.п.) дифференциального смесителя могут ухудшаться в случае малого тока смещения.

Согласно варианту осуществления, чтобы характеристики не ухудшались вследствие изменений опорного тока IОП, ток смещения ICM должен быть пропорционален опорному току IОП (например, IСМ≅2IОП или некоторым другим значениям). Этого можно добиться с использованием токового зеркала, подавая опорный ток IОП на опорный тракт токового зеркала и снимая ток смещения IСМ с зеркального тракта.

Конкретный вариант осуществления, показанный на фиг.5, обеспечивает многочисленные преимущества. Во-первых, для обеспечения сопряжения по модулирующим сигналам I и Q требуется всего пять линий сигнала (т.е. четыре линии для сигналов I и Q и одна для опорного сигнала). Таким образом, для сопряжения ИС требуется меньшее количество ножек, чем в традиционной конструкции, предусматривающей использование десяти линий сигнала. Уменьшение количества ножек позволяет осуществлять более плотную компоновку и, таким образом, уменьшать размер. Во-вторых, дифференциальный токовый сигнал IДАННЫЕ требует меньшего импеданса, что приводит к снижению размаха сигнала сопряжения, а следовательно, к снижению шума, генерируемого этим сигналом. Низкий импеданс также обеспечивает снижение помех. В-третьих, использование дифференциального токового сигнала позволяет упростить устройство цифровой и аналоговой ИС. Согласно фиг.5, схема 512 сопряжения (по своей природе) генерирует сигнал тока, который можно напрямую, без преобразования сигнала, подавать на аналоговую ИС. Модулятор 524 принимает и может непосредственно обрабатывать дифференциальный токовый сигнал. Таким образом, обеспечивая сопряжение по току, можно исключить схемы преобразования I-V и V-I. В-четвертых, совместное использование опорного сигнала IОП цифровой и аналоговой ИС позволяет осуществлять согласование параметров между двумя ИС. Согласно фиг.5, токовый сигнал IДАННЫЕ, выдаваемый схемой 512 сопряжения, зависит от опорного тока IОП. Кроме того, можно сделать так, чтобы ток смещения IСМ был согласован с опорным током IОП, согласно описанному выше, что позволяет согласовывать модулятор со схемой сопряжения. Это сопряжение также обеспечивает возможность совместного использования тока между ЦАП и смесителем, если IДАННЫЕ генерируется источником тока на основе n-канального МОП.

Конкретный вариант осуществления, представленный на фиг.5, допускает различные модификации. Например, схема 522 опорного сигнала может быть реализована в цифровой ИС 500. В таком случае опорный сигнал IОП поступает с ИС 500 на ИС 502. Реализовать схему опорного сигнала в цифровой ИС обычно труднее ввиду большого коммутационного шума на цифровой ИС, хотя такая реализация достижима и может быть полезна в некоторых приложениях.

Можно создать такую схему 522 опорного сигнала, чтобы она действовала как программируемый источник опорного сигнала. Например, источник тока 532 может содержать ЦАП, выдающий различные опорные токи в зависимости от значения входного сигнала управления. Использование программируемого источника опорного сигнала особенно полезно, например, для обеспечения возможности регулировки характеристик схемы (например, уровня выходного сигнала, для учета изменений процесса) или для изменения уровня входного сигнала для обеспечения переменного усиления.

Изобретение было описано применительно к сопряжению по модулирующим сигналам I и Q, поступающим с цифровой ИС на аналоговую ИС. Изобретение можно также использовать применительно к сигналам управления, например смещению, и сигналам регулировки усиления, показанным на фиг.1. Ток смещения и коэффициент усиления схемных элементов на тракте передачи сигнала обычно регулируется, если вообще регулируется, методом приращений. Например, стандарт IS-95-A требует регулировки уровня выходной мощности передатчика с приращениями в 0,5 дБ. Для обеспечения регулировки усиления с приращениями 0,5 дБ, отвечающей техническим условиям IS-95-A, обычно используют многоуровневый сигнал управления.

Как и модулирующие сигналы, многоуровневый сигнал управления можно обеспечивать с использованием множественных линий цифрового сигнала. Однако это, в общем случае, нежелательно по причине большого количества необходимых ножек, большой величины генерируемого шума и по другим причинам. Аналоговый сигнал управления генерирует меньший шум и может обеспечивать множественные уровни управления с использованием меньшего количества ножек.

Коэффициент усиления усилительного элемента (например, УРУ) зависит от различных факторов, например, от конструкции усилительного элемента, значений компонентов, характеристик активных устройств и пр. Многие из этих факторов зависят от процесса, используемого для изготовления ИС, и изменения процесса обычно приводят к широкому разбросу значений компонентов. Например, значения резисторов могут варьироваться в пределах 30 или более процентов от ИС к ИС. Аналогично, коэффициент бета транзисторов может изменяться вдвое при переходе от одной ИС к другой. Для обеспечения уровня согласования между схемой управления и управляемым элементом можно обеспечивать опорный сигнал, совместно используемый схемами.

На фиг.6 показана блок-схема варианта осуществления схем, используемых для генерации сигнала управления согласно изобретению. Схема управления реализуется на ИС 600, а схемный элемент, подлежащий управлению, реализуется на ИС 602. ИС 602 содержит схему 622 опорного сигнала, которая генерирует опорный сигнал ОС. Опорный сигнал может представлять собой опорное межпороговое напряжение или опорный ток, определяемый, например, межпороговым напряжением. Опорный сигнал ОС поступает с ИС 602 на ИС 600.

На ИС 600 опорный сигнал ОС буферизуется буфером 612 и поступает на схему 614 управления. Схема 614 управления также принимает входной сигнал управления и генерирует сигнал управления на основании буферизованного опорного сигнала и входного сигнала управления. Согласно варианту осуществления, сигнал управления является токовым сигналом IУПР. Сигнал управления поступает с ИС 600 на ИС 602.

На ИС 602 сигнал управления буферизуется буфером 624 и поступает на схемный элемент 626. Буфер 624 может, при необходимости, генерировать управляющее напряжение из принятого сигнала тока, пропуская сигнал тока через резистор. Этот резистор может быть внешним резистором или внутренним резистором, изготовленным на ИС 602.

Согласно конкретному варианту осуществления, схема 622 опорного сигнала генерирует опорный ток IОП на основании опорного межпорогового напряжения и резистора. Схема 614 сопряжения генерирует управляющий сигнал IУПР, который является масштабированной версией опорного тока. Масштабирование определяется, отчасти, входным сигналом управления. Управляющий токовый сигнал можно выразить следующим образом:

где y[n] - входной управляющий сигнал и К - общий масштабный коэффициент, объединяющий в себе масштабные коэффициенты для схем опорного сигнала и управления (например, токовых зеркал, входящих в состав схем опорного сигнала и управления). Управляющий токовый сигнал буферизуется буфером 624, и буферизованный сигнал поступает на схемный элемент 626. Схемный элемент 626 может представлять собой, например, УРУ, смеситель, ПУМ или иной схемный элемент.

На фиг.6 показан конкретный вариант осуществления сопряжения по сигналу управления между ИС. Изобретение можно применять к генерации сигналов управления для передатчика и приемника сотового телефона, а также для других схем. Например, согласно настоящему изобретению, аналоговые сигналы управления можно генерировать для управления, например аттенюаторами, смесителями, усилителями мощности, генераторами в схемах стабилизации фазы, регулируемых фильтрах и других схемах. Изобретение особенно полезно, когда управляемая схема изготовлена на первой интегральной схеме, имеющей первый набор характеристик, а управляющая схема изготовлена на второй интегральной схеме, имеющей второй набор характеристик, которые могут изменяться независимо от характеристик первой интегральной схемы.

Некоторые варианты осуществления были описаны применительно к схемам, реализованным с использованием БПТ (биполярных плоскостных транзисторов) и МОП-транзисторов. Изобретение также можно реализовать.применительно к другим схемам, содержащим полевые транзисторы, полевые транзисторы с затвором Шотки, биполярные гетеротранзисторы, ВПЭ-транзисторы с р-каналом и пр. Кроме того, для реализации изобретения можно использовать Р-МОП и N-МОП. Используемый здесь термин «транзистор», в общем случае, относится к любой активной схеме и не ограничивается БПТ или МОП-транзисторами.

Вышеприведенное описание предпочтительных вариантов осуществления позволяет специалистам в данной области применять настоящее изобретение. Специалисты могут предложить разнообразные модификации этих вариантов осуществления, и раскрытые здесь основополагающие принципы можно применять к другим вариантам осуществления, не используя изобретательства. Таким образом, описанные здесь варианты осуществления не являются ограничением настоящего изобретения, которое следует рассматривать в более широком объеме, согласующимся с раскрытыми здесь принципами и отличительными признаками.

| название | год | авторы | номер документа |

|---|---|---|---|

| СХЕМА ИЗМЕРЕНИЯ ТОКА | 1995 |

|

RU2160903C2 |

| УСТРОЙСТВО ЛИНЕАРИЗАЦИИ ДЛЯ УСИЛИТЕЛЯ С ПЕРЕМЕННЫМ УСИЛЕНИЕМ | 2001 |

|

RU2273949C2 |

| КАЛИБРОВКА ПОДАВЛЕНИЯ ИСКАЖЕНИЙ | 2003 |

|

RU2315423C2 |

| ПОЛУПРОВОДНИКОВАЯ ИНТЕГРАЛЬНАЯ СХЕМА | 1991 |

|

RU2104601C1 |

| УСИЛИТЕЛЬ С ПЕРЕМЕННЫМ УСИЛЕНИЕМ И ВЫСОКИМ ДИНАМИЧЕСКИМ ДИАПАЗОНОМ | 1997 |

|

RU2209504C2 |

| МНОГОРЕЖИМНОЕ УСТРОЙСТВО РАДИОСВЯЗИ И МНОГОРЕЖИМНЫЙ СОТОВЫЙ РАДИОТЕЛЕФОН | 1993 |

|

RU2128886C1 |

| ИНФРАКРАСНЫЙ РАДИОМЕТР | 1999 |

|

RU2172476C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С УПРАВЛЯЕМЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2008 |

|

RU2384935C1 |

| АНАЛОГОВЫЙ ПЕРЕМНОЖИТЕЛЬ НАПРЯЖЕНИЙ | 2008 |

|

RU2383053C1 |

| ЦЕПЬ ЕМКОСТНОГО ДАТЧИКА | 2007 |

|

RU2401987C2 |

Схема, генерирующая сигнал сопряжения между первой и второй интегральными схемами (ИС). Технический результат заключается в усовершенствовании сопряжения между ИС с использованием меньшего количества линий сигнала, генерирующих пониженный шум. Схема содержит схему опорного сигнала (622), которая выдает спорный сигнал, схему сопряжения (600) и аналоговую схему передачи сигнала (626). Схема сопряжения реализована на первой ИС (600), в ходе эксплуатации подключается к схеме опорного сигнала (622), принимает опорный сигнал и входной сигнал данных и генерирует сигнал сопряжения. Аналоговая схема передачи сигнала (626) реализована на второй ИС, в ходе эксплуатации подключается к схеме управления (614), принимает сигнал сопряжения и выдает выходной сигнал. Опорный сигнал может представлять собой сигнал напряжения или сигнал тока и может генерироваться на первой или второй ИС. Схема сопряжения может быть реализована содержащей токовое зеркало, подключенное к массиву переключателей, и работать в режиме передискретизации для упрощения требований к фильтрации. Сигнал сопряжения может представлять собой дифференциальный токовый сигнал, имеющий разрешение в несколько (например, четыре, восемь или более) бит. Аналоговая схема передачи сигнала (626) может представлять собой, например, УРУ, модулятор или иную схему. 9 н. и 65 з.п. ф-лы, 6 ил.

| US 5847623 А, 08.12.1998 | |||

| US 5258758 А, 02.11.1993 | |||

| US 5811984 А, 22.09.1998 | |||

| US 5712635 А, 27.01.1998 | |||

| US 5880631 А, 09.03.1999 | |||

| US 5515014 A, 07.05.1996 | |||

| Механизм запуска газогенератора и привода щетки снегоочистительной машины | 1975 |

|

SU587207A1 |

| Приспособление в пере для письма с целью увеличения на нем запаса чернил и уменьшения скорости их высыхания | 1917 |

|

SU96A1 |

Авторы

Даты

2008-01-20—Публикация

2000-10-17—Подача