Изобретение относится к аппаратным средствам персонального компьютера /ПК/ и может быть использовано как монитор в ПК.

Прототипом принят цифровой монитор [1], содержащий элемент И, с первого по десятый ключи, делитель частоты, триггер, с первого по шестой накопители кодов сигналов R, G, В, три блока импульсных усилителей, блок модуляции излучений, первый усилитель и первый пьезодефлектор с отражателем на торце, второй усилитель и второй пьезодефлектор с отражателем на торце, проекционный объектив, матовый экран, блоки строчной и кадровой разверток. Недостаток прототипа: при безинерционном луче и отсутствии излучающего покрытия на матовом экране яркость изображения на экране будет недостаточна для комфортного восприятия его пользователем.

Цель изобретения - увеличить яркость воспроизводимого на экране изображения.

Результатом является достаточное увеличение яркости воспроизводимого изображения на экране. Достигается результат применением плоскопанельного светодиодного экрана из светодиодных ячеек /СД-ячеек/ по числу разрешаемых элементов /пикселов/ в кафе, формирующих изображение постоянным излучением СД-ячейками в течение всего кадра. Коды кадров частотой 60 Гц, формируемые в видеоадаптере ПК, поступают на входы монитора, экран которого из соответствующего числа электронно-управляемых СД-ячеек, каждая из которых является источником излучения трех основных цветов и формирует пиксел кадра.

Сущность заявляемого изобретения в том, что в монитор, содержащий накопители кодов R, G, В, введены три блока формирователей импульсов и плоскопанельный светодиодный экран /СД-экран/ из светодиодных ячеек по числу разрешающих элементов в кадре, каждая СД-ячейка содержит непрозрачный корпус, матрицу светодиодов трех основных цветов и микролинзу в выходном торце корпуса, матрица содержит число светодиодов каждого цвета по числу разрядов в коде, а каждый светодиод имеет нейтральный светофильтр, плотность которого определяется принадлежностью светодиода к соответствующему двоичному разряду кода.

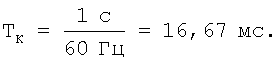

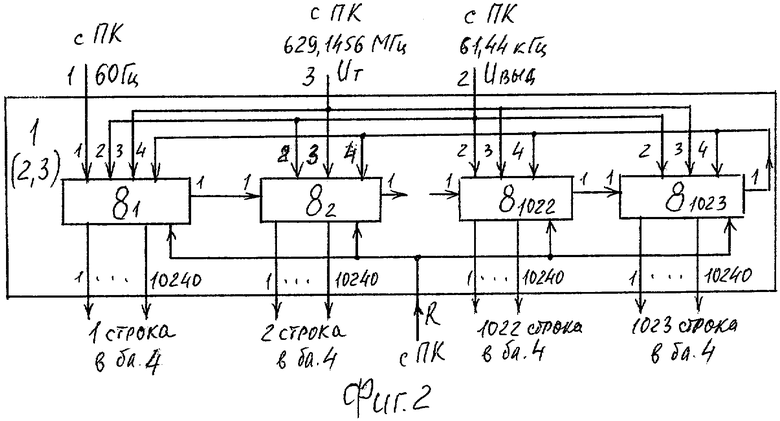

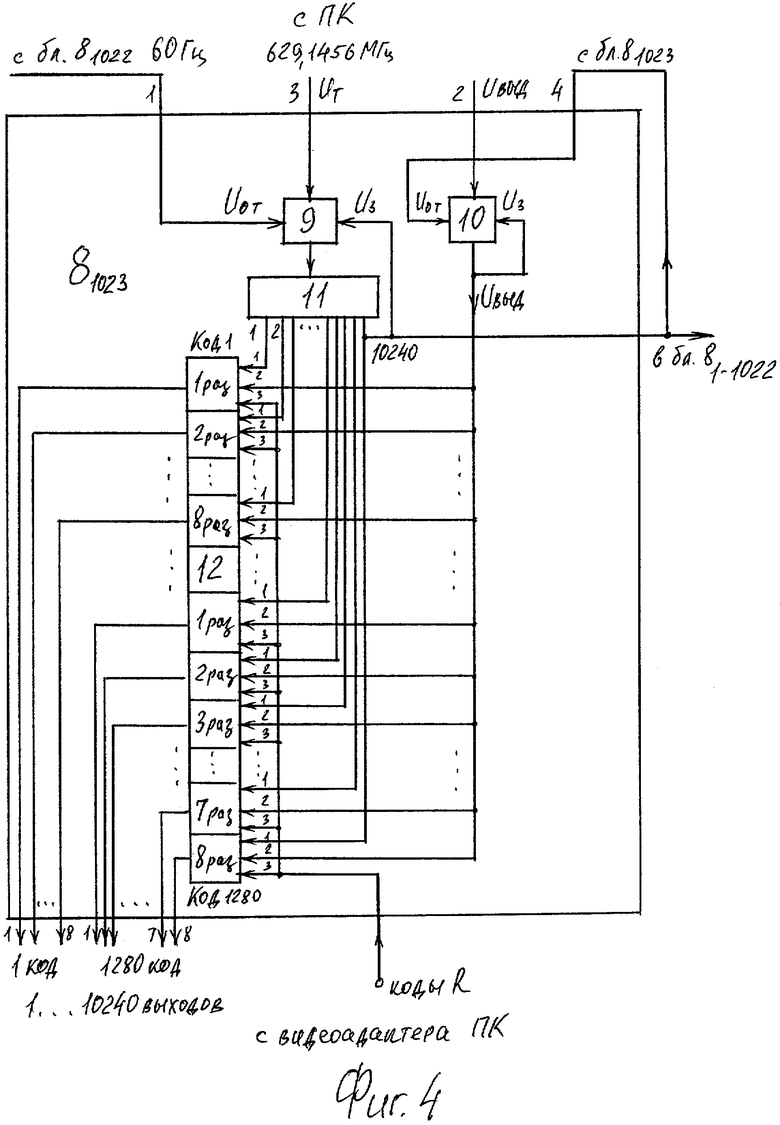

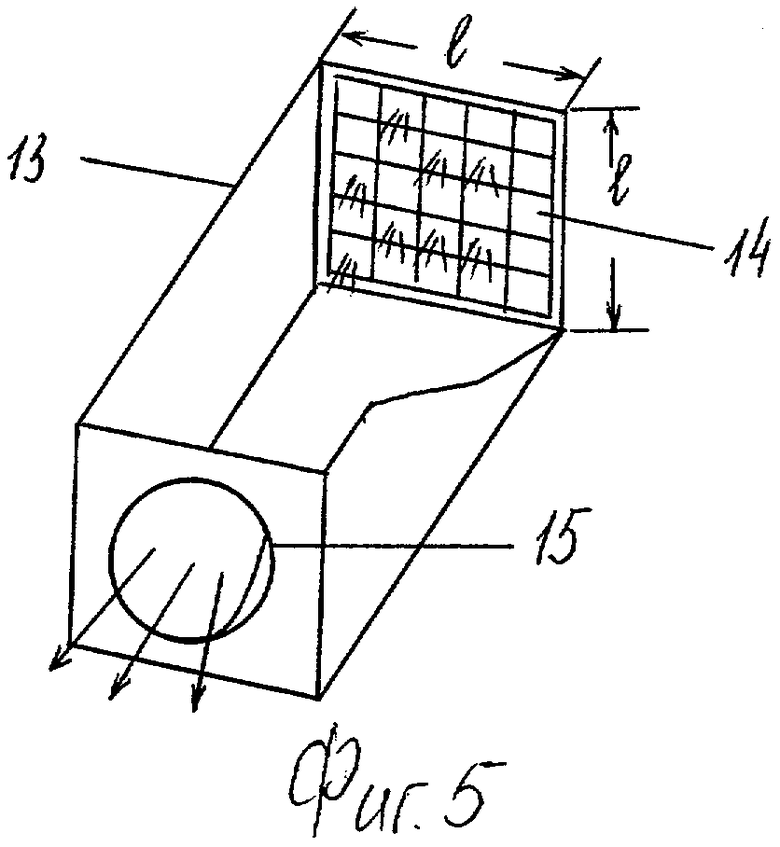

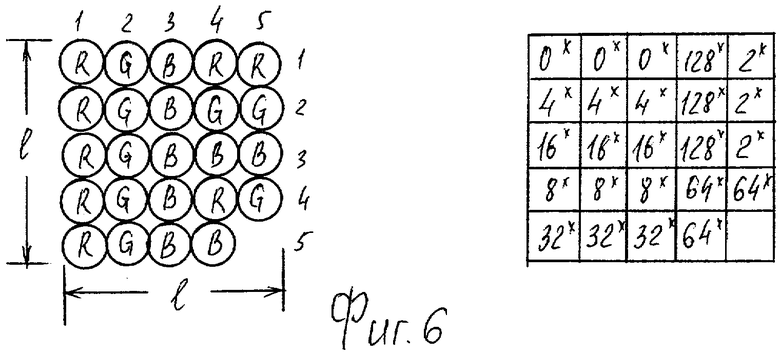

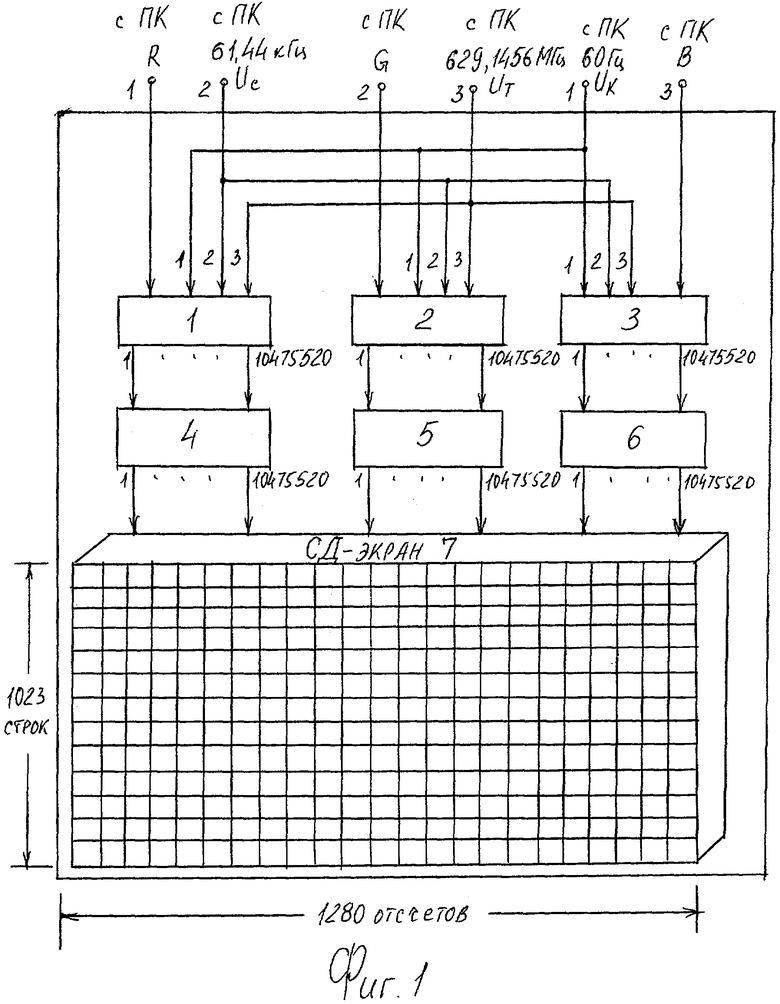

Блок-схема монитора приведена на фиг.1, накопитель кодов - на фиг.2, блок регистра - на фиг.3 и 4, СД-ячейка - на фиг.5, матрица светодиодов и расположение нейтральных светофильтров - на фиг.6.

Заявляемый монитор воспроизводит с видеоадаптера ПК видеорежим 1280×1024×60 Гц. Тактовая частота следования сигналов разрядов в последовательных кодах с ПК:

fТ=1280×1024×60 Гц×8=629,1456 МГц,

где 1280 - число отсчетов в строке,

1024 - число строк в кадре,

60 Гц - частота кадров,

8 - число разрядов в коде.

Частота дискретизации кодов fД = 1280×1024×60 Гц=78,6432 МГц.

Частота строк fС=1024×60 Гц=61,44 кГц.

Длительность строки

Длительность кадра

Монитор включает /фиг.1/ накопитель 1 кодов R, накопитель 2 кодов G, накопитель 3 кодов В, первый 4, второй 5, третий 6 блоки формирователей импульсов и плоскопанельный светодиодный экран 7 /СД-экран/. Накопители кодов идентичны /фиг.2/, каждый включает блоки 8 регистра по числу строк в кадре без одной: 81-1023. Информационным входом каждого накопителя 1 /2, 3/ кодов являются объединенные информационные входы блоков 8 регистра, первым управляющим входом является первый вход /60 Гц/ первого блока 8 регистра, вторым - объединенные вторые управляющие входы /Uвыд 61,44 кГц/ блоков регистра, третьим - объединенные третьи управляющие входы /UД/ блоков регистра. Каждый управляющий выход предыдущего блока регистров является первым управляющим входом последующего блока 8 регистра. Управляющий выход последнего блока регистра 81023 подключен параллельно к четвертым управляющим входам всех блоков 8 регистра. Выходами каждого накопителя кодов являются выходы всех блоков регистра. Первым, вторым и третьим информационными входами монитора являются информационные входы соответственно накопителя кодов R, накопителя кодов G и накопителя кодов В, подключенные к соответствующим выходам ПК. Первым, вторым и третьим управляющими входами монитора являются объединенные первые управляющие входы накопителей 1, 2, 3 кодов R, G, В, подключенные к выходу кадровых синхроимпульсов в видеоадаптере ПК, объединенные вторые управляющие входы накопителей 1, 2, 3 кодов R, G, В, подключенные к выходу строчных синхроимпульсов в видеоадаптере ПК, объединенные третьи управляющие входы накопителей кодов R, G, В, подключенные к соответствующему выходу ПК. Выходы накопителя 1 кодов R подключены к входам первого блока 4 формирователей импульсов, выходы накопителя 2 кодов G подключены к входам второго блока 5 формирователей импульсов, выходы накопителя 3 кодов В подключены к входам третьего блока 6 формирователей импульсов. Выходы блоков 4, 5, 6 подключены к соответствующим входам плоскопанельного СД-экрана 7. Блоки 8 регистра идентичны /фиг.3/, каждый включает первый 9 и второй 10 ключи, распределитель 11 импульсов и регистр 12. Информационным входом блока 8 являются объединенные третьи /информационные/ входы разрядов регистра 12. Выходы разрядов регистра 12 являются параллельными с первого по 10240 выходами блока 8 регистра. Первым управляющим входом блока 6 является первый управляющий вход первого ключа 9, вторым - сигнальный вход второго ключа 10, третьим - сигнальный вход первого ключа 9, четвертым - первый управляющий вход второго ключа 10, подключенный к управляющему выходу последнего блока 81023 регистра. Выход первого ключа 9 подключен к входу распределителя 11 импульсов, выходы которого последовательно с первого по последний /10240/ подключены к первым управляющим входам разрядов регистра 12 с. Последний выход подключен также к второму управляющему входу первого ключа 9 и является управляющим выходом блока 81 регистра. Выход второго ключа 10 подключен параллельно к вторым управляющим входам всех разрядов регистра 12 и к второму управляющему входу ключа 10. Блоки 4, 5, 6 формирователей импульсов каждый включает формирователей импульсов по числу элементов разрешения в кадра и по числу разрядов в коде 10475520 /1280×1023×8/. Назначение формирователей импульсов выдавать управляющие сигналы на запитывание светодиодов в СД-ячейках соответствующей амплитуды и длительности для непрерывного излучения ими своего цвета в течение длительности кадра /16 мс/. Амплитуда сигнала соответствует напряжению срабатывания светодиода, длительность управляющего сигнала равна длительности кадра /16 мс/. Форма управляющего сигнала прямоугольная.

СД-экран 7 представляет совокупность светодиодных ячеек по числу элементов /пикселов/ разрешения в кадре 1309440 /1023×1280/. Каждая СД-ячейка формирует один пиксел изображения и состоит из /фиг.5/ непрозрачного корпуса 13, матрицы 14 светодиодов трех основных цветов /R, G, В/ и микролинзы 15, выполняющей суммирование потоков излучения от светодиодов матрицы 11 и формирование из них пиксела требуемого размера. Светодиодов красного излучения в матрице 8 /по числу разрядов в коде/, зеленого - восемь, синего тоже восемь. Время отклика светодиодов на управляющий сигнал практически нулевое, менее 1 мкс [4, с.9]. Матрица 14 расположена в фокальной плоскости микролинзы 15 и включает 24 микроминиатюрных светодиода. Светодиоды микроминиатюрного исполнения с диаметром излучающей части 0,1 мм расположены /фиг.6/ в пять рядов по пять колонок. Форма матрицы - квадрат l со стороной 0,6 мм, площадью 0,36 мм2. Форма корпуса 13 СД-ячейки - прямоугольный параллелепипед, торцевые стороны квадрата по 0,7 мм. Глубина корпуса соответствует фокусному расстоянию микролинзы 15 /несколько миллиметров/. Излучаемые матрицей три цветовых потока модулируются по яркости преобразованием "код - яркость излучения". Модуляция выполняется применением на каждом светодиоде ослабляющего нейтрального светофильтра, плотность которого соответствует весу разряда в коде, к которому принадлежит светодиод. Кратность ослабления излучения светодиодов осуществляется соответственно коэффициентов двоичных разрядов кода, к которым принадлежит светодиод. Светодиод первого /старшего/ разряда кода не имеет светофильтра, т.е. его светофильтр кратности 0Х, светодиод второго разряда кода имеет светофильтр плотностью 2Х, светодиод третьего разряда кода имеет светофильтр 4Х и т.д., светодиод восьмого /младшего/ разряда имеет светофильтр 128Х.

Вариант расположения светодиодов трех цветов и их светофильтров изображен на фиг.6. Распределение коэффициентов двоичных разрядов кода, соответствующая им плотность нейтральных светофильтров и вес разряда приведены в таблице.

Излучения светодиодов матрицы 14 суммируются микролинзой 15, на выходе которой яркость, насыщенность и цветовой тон результирующего излучения определяются взаимным соотношением составляющих трех цветов соответственно кодов сигналов R, G и В. В СД-экране 7 при разрешении 1280×1023 используются 10475520 светодиодов одного цвета, а трех цветов /R, G, В/ 31426560. Исключение из процесса получения изображения на экране строчной и кадровой разверток упрощает процесс, но обязывает обеспечить каждый светодиод индивидуальным формирователем импульса. Светодиод обслуживается своим формирователем импульса, поэтому каждый из блоков 4, 5, 6 включает по 10475520 формирователей импульса. Но настоящий уровень технологий позволяет изготавливать микросхемы с десятками миллионов транзисторов [2, с.65; 3, с.26], есть возможность и блоки формирователей импульсов каждый изготовить в одной микросхеме. При размере корпуса СД-ячейки 0,7×0,7 мм размеры СД-экрана составят:

по горизонтали 1280×0,7 мм = 896 мм,

по вертикали 1023×0,7 мм = 716 мм,

по диагонали 1147 мм или 45 дюймов.

С соответствующих выходов видеоадаптера ПК на информационный вход накопителя 1 кодов поступают в последовательном виде 8-разрядные коды сигнала R, на информационный вход накопителя 2 кодов поступают коды сигнала G, на информационный вход накопителя 3 кодов поступают коды сигнала В. С соответствующих управляющих выходов видеоадаптера ПК на первый, второй и третий управляющие входы накопителей 1, 2, 3 кодов поступают соответственно синхроимпульсы /60 Гц/ частоты кадров, частоты строк 61,44 кГц и тактовая частота UT /629,1456 МГц/. За время первого кадра регистры 12 /фиг.3/ последовательно заполняются кодами первого кадра. Каждый блок 8 регистра сосредотачивает коды одной игроки, поэтому их в каждом накопителе кодов по 1023, по числу строк в кадре без одной. За кадр в каждом накопителе кодов накапливаются по 10475520 кодов. Управляющий импульс с последнего блока 81023 регистра поступает на четвертые управляющие входы блоков 8, выдает из них синхронно и параллельно все коды в блоки 4, 5, 6 формирователей импульсов и обнуляет разряды регистров 12 для приема следующего кадра. Время 1024-й строки /16,27 мкс/ используется на выдачу кодов в блоки 4, 5, 6, на обнуление разрядов регистров 12 и начало срабатывания схем формирователей импульса. В течение кадра /16 мс/ идет неменяющееся по яркости излучение СД-ячеек, а на СД-экране неменяющаяся картинка изображения. По заполнению 1023 блоков 8 регистра кодами второго кадра следует параллельная выдача кодов в блоки 4, 5, 6. На экране 7 в течение 16 мс воспроизводится картинка второго кадра. Далее идет повторение этих процессов.

Работа блоков 8 регистра /фиг.3/

Сигналы разрядов кода последовательно поступают на третьи /информационные/ входы разрядов регистра 12 с соответствующего цифрового выхода ДV1 видеоадаптера ПК. Заполнение регистров 12 кодами строки начинается с открытием импульсом 60 Гц первого ключа 9, который пропускает тактовые импульсы 629,1456 МГц на вход распределителя 11 импульсов. Тактовые импульсы с выходов блока 11 последовательно поступают на первые управляющие входы, разрядов регистра 12. По заполнении регистра 12 сигнал с последнего /10240/ выхода блока 11 закрывает ключ 9 и в качестве управляющего выходного сигнала открывает ключ 9 во втором блоке 82 регистра, который аналогично заполняется кодами второй строки. Также заполняются регистры 12 остальных блоков 83-1023. По заполнении всех регистров в блоках 81-1023 выходной сигнал с блока 81023 открывает ключи 10 во всех блоках 8 регистра. Ключи 10 пропускают один импульс Uвыд, который выдает одновременно и параллельно из всех блоков 8 коды кадра /10475520/ в блоки 4, 5, 6 формирователей импульсов и обнуляет разряды регистров 12 для приема ими кодов следующего кадра.

Работа монитора

На 1-3 управляющие входы монитора с выходов видеоадаптера ПК поступают синхроимпульсы Uк 60 Гц кадров, синхроимпульсы строк Uc 61,44 кГц и тактовая частота 629,1456 МГц. С информационных выходов ПК на 1-3 информационные входы монитора поступают последовательные коды сигналов R, G, В. За первый период кадра накопители кодов производят накопление кодов R, G, В первого кадра, по окончании которого идет выдача синхронно и параллельно всех кодов кадра в блоки 4, 5, 6 формирователей импульса. А накопители 1, 2, 3 кодов ведут накопление кодов второго кадра. Сигналы разрядов первого кадра параллельно поступают в свои формирователи импульсов, где формируются по амплитуде и длительности /16 мс/ и поступают в соответствующие СД-ячейки, вызывая излучение светодиодов в течение длительности кадра. На СД-экране в течение 16 мс представляется картинка первого кадра. По окончании второго кадра из накопителей кодов выдаются коды второго кадра в блоки 4, 5, 6, и на СД-экране воспроизводится в течение 16 мс картинка второго кадра, параллельно идет накопление блоками 1, 2, 3 кодов третьего кадра. Далее процессы повторяются.

Заявляемый монитор с применением в нем плоскопанельного светодиодного экрана следует выполнять в плоскопанельном варианте, а учитывая большое число соединительных проводов от накопителей кодов к блокам формирователей импульсов и от них к светодиодам в СД-ячейках, весь монитор желательно исполнять в единой, монолитной и неразборной конструкции и для мобильных, и для настольных вариантов. Результат уменьшения яркости против прототипа в 1309440 раз (1023×1280).

Литература

1. Патент №2265286, кл. Н04N 9/18, бюл.33 от 27.11.05 г. - прототип.

2. Энциклопедический справочник: персональный компьютер. М., 2004, с.65.

3. Мураховский В. Железо ПК. Новые возможности. - СПб, Питер, 2005, с.26, 357, 359, 360.

4. Иванов и др. Полупроводниковые оптоэлектронные приборы. Справочник. М., 1984, с.9 /18 строка сверху/.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПЛОСКОПАНЕЛЬНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2316133C1 |

| ШИРОКОФОРМАТНЫЙ ЭКРАН | 2006 |

|

RU2316141C1 |

| СВЕТОДИОДНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2316139C1 |

| СИСТЕМА ВИРТУАЛЬНОЙ РЕАЛЬНОСТИ | 2007 |

|

RU2338333C1 |

| УСТРОЙСТВО ОТОБРАЖЕНИЯ ОБЪЕМНОЙ ВИДЕОИНФОРМАЦИИ | 2009 |

|

RU2413388C1 |

| ПЛОСКОПАНЕЛЬНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2320095C1 |

| ПЛОСКОПАНЕЛЬНЫЙ ДИСПЛЕЙ | 2009 |

|

RU2390104C1 |

| СПОСОБ ФОРМИРОВАНИЯ ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2313920C1 |

| ЦИФРОВОЙ ПЛОСКОПАНЕЛЬНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2316138C1 |

| ВИДЕОКАМЕРА | 2007 |

|

RU2358412C1 |

Изобретение относится к аппаратным средствам персонального компьютера (ПК) и может быть использовано как монитор в ПК. Техническим результатом является существенное (в 1309440 раз) увеличение яркости изображения на экране, достигаемое применением плоскопанельного светодиодного экрана из светодиодных ячеек (СД-ячеек) по числу разрешающих элементов (пикселов) в кадре. При этом в монитор вводятся три блока формирователей импульсов и плоскопанельный светодиодный экран (СД-экран) из светодиодных ячеек по числу разрешающих элементов в кадре, каждая СД-ячейка включает корпус, матрицу светодиодов трех основных цветов и микролинзу в выходном торце корпуса, а матрица включает светодиодов каждого цвета R, G, В по числу разрядов в коде. 6 ил., 1 табл.

Монитор, содержащий накопитель кодов R, накопитель кодов G, накопитель кодов В, отличающийся тем, что в него введены три блока формирователей импульсов и плоскопанельный светодиодный экран, первым, вторым и третьим информационными входами монитора являются соответственно информационные входы накопителя кодов R, накопителя кодов G и накопителя кодов В, подключенные к соответствующим информационным выходам видеоадаптера персонального компьютера (ПК), управляющими входами монитора являются: первым - объединенные первые управляющие входы накопителей кодов R, G, В, подключенные к выходу кадровых синхроимпульсов в видеоадаптере ПК, вторым - объединенные вторые вправляющие входы накопителей кодов R, G, В, подключенные к выходу строчных синхроимпульсов в видеоадаптере ПК, третьим - объединенные третьи управляющие входы накопителей кодов R, G, В, подключенные к соответствующему выходу ПК, накопители кодов R, G, В идентичны, каждый включает блоки регистра по числу строк в кадре без одной, информационным входом каждого накопителя кодов являются объединенные входы блоков регистра, первым управляющим входом является управляющий вход первого блока регистра, вторым - объединенные вторые управляющие входы блоков регистра, третьим - объединенные третьи управляющие входы блоков регистра, каждый управляющий выход предыдущего блока регистра является первым управляющим входом последующего блока регистра, управляющий выход последнего блока регистра подключен параллельно к четвертым управляющим входам всех блоков регистра, выходами каждого накопителя кодов R, G, В являются выходы всех блоков регистра, выходы накопителя кодов R подключены к соответствующим входам первого блока формирователей импульсов, выходы накопителя кодов G подключены к соответствующим входам второго блока формирователей импульсов, выходи накопителя кодов В подключены к соответствующим входам третьего блока формирователей импульсов, выходы первого - третьего блоков формирователей импульсов подключены к соответствующим входам плоскопанельного светодиодного экрана (СД-экрана), состоящего из светодиодных ячеек (СД-ячеек) по числу разрешающих элементов (пикселов) в кадре, каждая СД-ячейка содержит непрозрачный корпус; матрицу из соответствующего числа светодиодов трех основных цветов (R, G, В) и микролинзу в выходном торце корпуса СД-ячейки, матрица светодиодов расположена в фокальной плоскости микролинзы и содержит число светодиодов каждого цвета по числу разрядов в коде, а каждый светодиод имеет нейтральный светофильтр, плотность которого определяется принадлежностью светодиода к двоичному разряду кода, блоки регистра идентичны, каждый включает первый и второй ключи, распределитель импульсов и регистр, информационным входом блока регистра являются объединенные третьи (информационные) входы разрядов регистра, выходы разрядов регистра являются параллельными выходами блока регистра, первым управляющим входом блока регистра является первый управляющий вход первого ключа, вторым - сигнальный вход второго ключа, третьим - сигнальный вход первого ключа, четвертым - первый управляющий вход второго ключа, подключенный к управляющему выходу последнего блока регистра, выход первого ключа подключен к входу распределителя импульсов, выходы которого последовательно с первого по последний подключены к первым управляющим входам разрядов регистра, последний выход также подключен к второму управляющему входу первого ключа и является управляющим выходом блока регистра, выход второго ключа подключен параллельно к вторым управляющим входам всех разрядов регистра и к второму управляющему входу второго ключа, каждый блок формирователей импульсов содержит формирователей импульсов по числу разрешающих элементов (пикселов) в кадре и по числу разрядов в коде.

Авторы

Даты

2008-01-27—Публикация

2006-04-17—Подача