Изобретение относился к аппаратным устройствам компьютерного оборудования и используется совместно с персональным компьютером /ПК/ для получения трехмерного изображения. Аналогом является кибершлем V8 фирмы Virtual Research Sistems [1 c.557], содержащий блок управления, два соединительных кабеля и шлем, включающий две ЖК-матрицы с диагональю 1,3″ и разрешением в 307200 элементов /640×480/. В качестве входного сигнала используется выходной сигнал видеоадаптера VGA в режиме 640×480 при построчной развертке и частоте кадров 60 Гц. Блок управления выполняет функции коммутирующего устройства. Стереосигнал поступает в блок управления по двум кабелям, оба видеосигнала поступают в экраны шлема независимо друг от друга. Шлем соединяется с блоком управления с помощью 50-контактного SCSI-разъема. Недостатки аналога: низкое разрешение ЖК-матриц [1, C.558], частота кадров ограничена 60 Гц.

Прототипом принята Система виртуальной реальности [2], содержащая блок управления, шесть строчных накопителей кодов, шесть блоков импульсных усилителей, блоки строчной и кадровой развертки, два блока модуляции излучений, первый усилитель и первый пьезодефлектор с отражателем на торце, два источника опорных напряжений, второй усилитель и второй пьезодефлектор, третий и четвертый источники опорных напряжений, третий усилитель и третий пьезодефлектор, пятый и шестой источники опорных напряжений, четвертый усилитель и четвертый пьезодефлектор с седьмым и восьмым источниками опорных напряжений и два матовых экрана. Развертка изображения на каждом экране выполняется двумя пьезодефлекторами. Трехмерное изображение воспринимается раздельным наблюдением левого кадра стереопары левым глазом зрителя на левом экране, правого кадра стереопары правым глазом на правом экране. Размер каждого экрана 40×30 мм, по диагонали 50 мм /1,97″/. Разрешение на каждом экране 480000 элементов /800×600/. Частота кадров 85 Гц. Недостатки прототипа: недостаточная яркость изображения из-за развертки изображения на матовом экране, не имеющем послесвечения, электронно-оптическое выполнение развертки строк и кадра на экранах ведет к увеличению размеров, веса шлема и серьезно усложняет всю конструкцию шлема.

Цель изобретения - упрощение процесса получения изображений на экранах и увеличение их яркости. Техническим результатом являются получение изображения на экранах без строчной и кадровой разверток, достигаемое введением в систему виртуальной реальности накопителей кодов кадра каждого цветового сигнала и блоков формирования управляющих сигналов, и увеличение их яркости введением плоскопанельных светодиодных экранов.

Сущность изобретения в том, что в систему виртуальной реальности, содержащую блок управления, два соединительных кабеля и шлем, введены канал левого кадра стереопары и канал правого кадра стереопары, каждый из которых включает три идентичных канала цветовых сигналов R, G, B и плосокпанельный СД-экран, а каждый канал цветового сигнала содержит последовательно соединенные накопитель кодов кадра и блок формирования управляющих сигналов, выходы которых подключены к входам своего плосокпанельного светодиодного экрана /СД-экрана/.

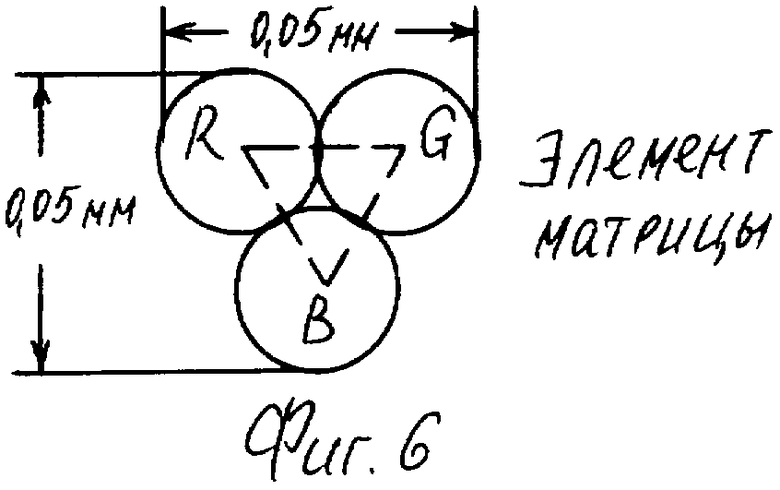

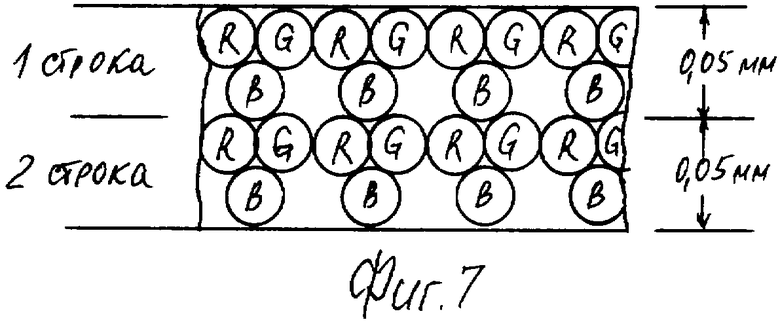

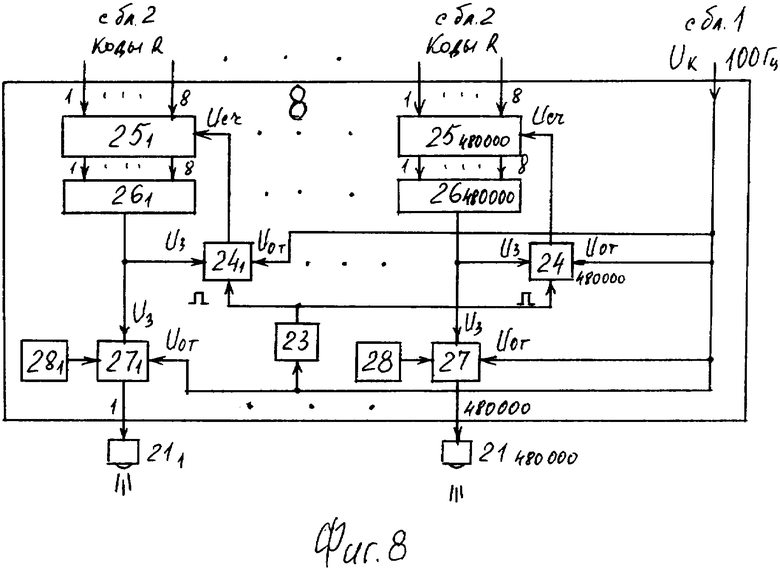

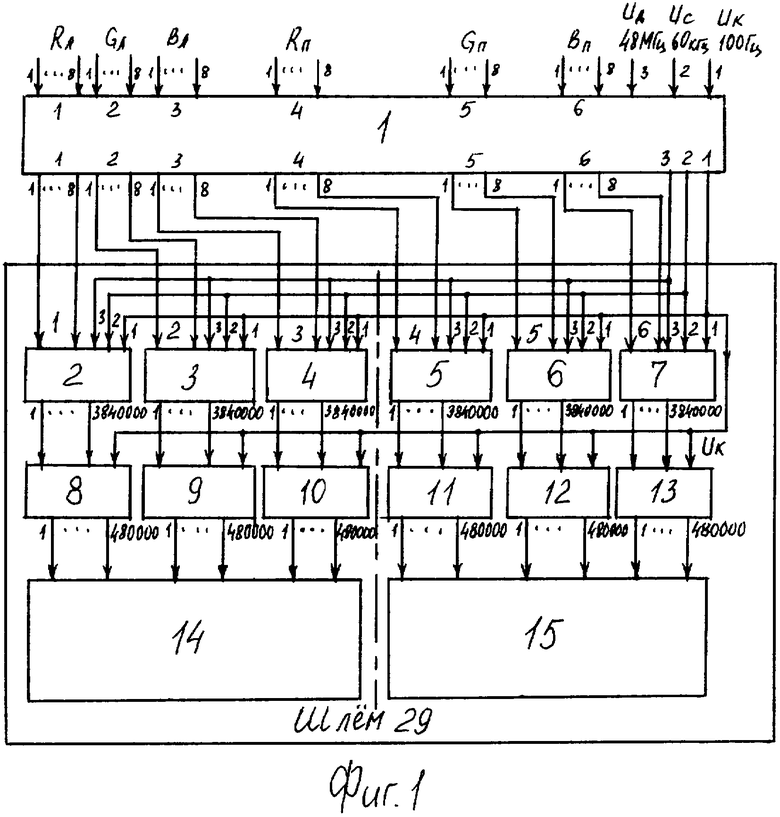

Стереокадр формируется видеоадаптером ПК из левого и правого кадров стереопары. Используется видеорежим 800 отсчетов × 600 строк × 100 Гц. С блока управления коды левого и правого кадров раздельно по цветам сигналов R, G, В поступают в накопитель кодов кадра, в котором сосредотачиваются все коды кадра. По окончании периода кадра все коды кадра синхронно и параллельно выдаются в свои блоки формирования отправляющих сигналов, которые запитывают в светодиодных ячейках /СД-ячейках/ светодиоды на длительность, прямо пропорциональную величине каждого кода. Уровень яркости от каждого светодиода формируется из скважности излучения и неизлучения за период кадра: отношение времени, когда светодиод излучает /получает питание/, ко времени, когда он не излучает /не запитывается/. Число элементов матриц в СД-экране соответствует разрешению экрана 480000 /800×600/, а каждый элемент матрицы включает по три светодиода, которые излучением основных цветов R, Q, В формируют один пиксел. Функциональная схема системы показана на фиг.1, накопитель кодов кадра - на фиг.2, блок регистров - на фиг.3 и 4, СД-ячейка - на фиг.5, состав одного элемента матрицы и его форма - на фиг.6, расположение элементов матрицы в экране - на фиг.7, блок формирования управляющих сигналов - на фиг.8.

Система виртуальной реальности включает /фиг.1/ блок 1 управления, канал левого кадра стереопары, включающий канал цветового сигнала RЛ из последовательно соединенных накопителя 2 кодов кадра и блока 8 формирования управляющих сигналов, канал цветового сигнала GЛ из последовательно соединенных накопителя 3 кодов кадра и блока 9 формирования управляющих сигналов, канал цветового сигнала ВЛ из последовательно соединенных накопителя 4 кодов кадра и блока 10 формирования управляющих сигналов, выходы блоков 8, 9, 10 подключены к соответствующим входам первого плоскопанельного светодиодного экрана 14, система включает канал правого кадра стереопары, включающий канал цветового сигнала RП из последовательно соединенных накопителя 5 кодов кадра и блока 11 формирования управляющих сигналов, канал цветового сигнала GП из последовательно соединенных накопителя 6 кодов кадра и блока 12 формирования управляющих сигналов, канал цветвого сигнала ВП из последовательно соединенных накопителя 7 кодов кадра и блока 13 формирования управляющих сигналов, выходы блоков 11, 12, 13 подключены к соответствующим входам второго плоскопанельного СД-экрана 15.

На 1-6 информационные входы блока 1 /фиг.1/ с соответствующих выходов видеоадаптера ПК /поддерживающего выход на два дисплея/ поступают два цифровых видеосигнала: левого и правого кадров, представляемые 8-разрядными кодами цветовых сигналов R, G, В. На управляющие 1-3 входы блока 1 с видеоадаптера ПК при видеорежиме 800×600×100 Гц поступают: частота дискретизации 48 МГц, строчные 60 кГц и кадровые 100 Гц синхроимпульсы. Частота дискретизации кодов цветовых сигналов составляет:

600 строк × 100 Гц × 800 отчетов = 48 МГц.

Частота строчных синхроимпульсов: 600×100 Гц=60 кГц.

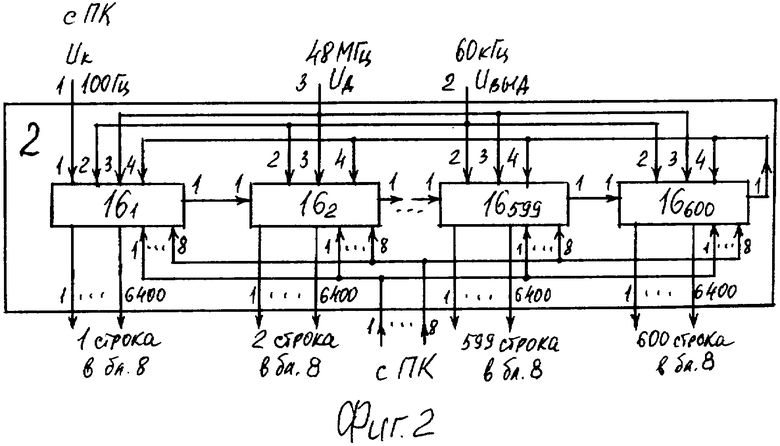

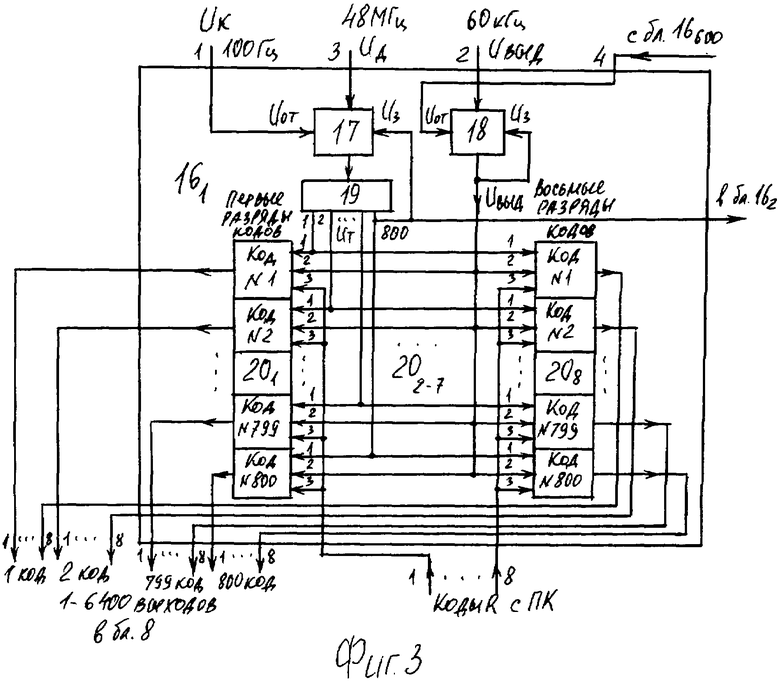

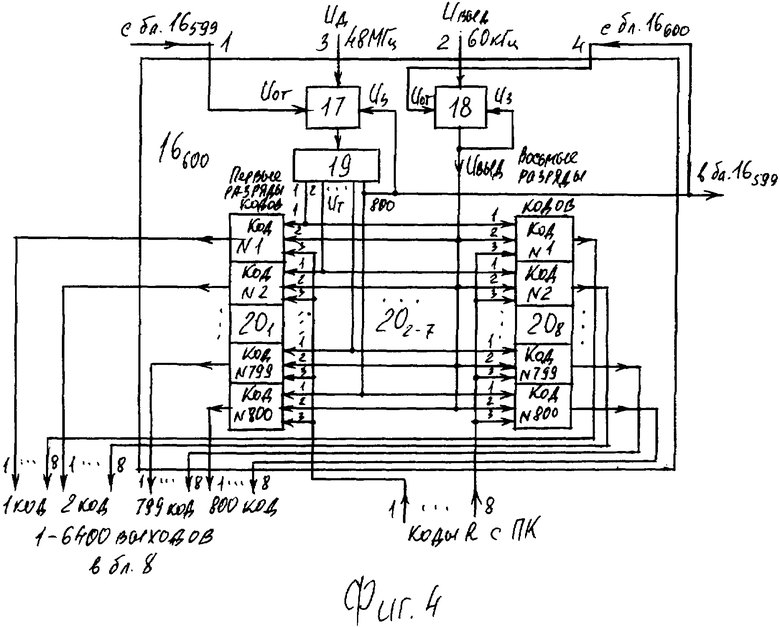

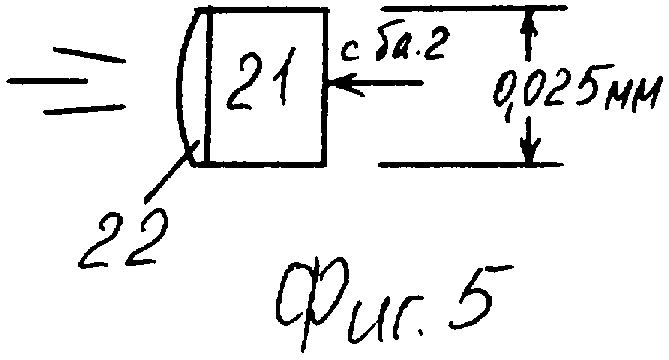

Накопители с 2 по 7 кодов кадра идентичны /фиг.2/, каждый включает блоки 16 регистров по числу строк в кадре 161-600. Информационным входом накопителя кодов кадра являются поразрядно объединенные с первого по восьмой входы блоков 16 регистров. Управляющими входами являются: первым - первый управляющий вход UК /100 Гц/ блока 161, вторым - объединенные вторые управляющие входы Uвыд /60 кГц/ блоков 161-600, третьим - объединенные третьи управляющие входы Uд /48 МГц/ блоков 161-600. Каждый управляющий выход предыдущего блока 16 регистров является первым управляющим входом каждого последующего блока 16 регистров. Управляющий выход последнего блока 16600 регистров подключен параллельно к четвертым управляющим входам всех блоков 161-600. Выходами накопителя кодов кадра являются параллельные выходы всех разрядов восьми регистров всех блоков 161-600 регистров, всего выходов 3840000 /800×8×600/. Блоки 16 регистров идентичны /фиг.3, 4/, каждый включает первый 17 и второй 18 ключи, распределитель 19 импульсов и восемь регистров 201-8. Информационным входом блока 16 являются поразрядно объединенные третья входы разрядов восьми регистров 20. Выходами блока 16 регистров являются параллельные выходы всех разрядов восьми регистров 20. С каждого блока 16 регистров 6400 выходов, 800×8. Управляющими входами являются: первым - первый управляющий вход Uк /100 Гц/ первого ключа 17, вторым - сигнальным вход Uвыш /60 кГц/ второго ключа 18, третьим - сигнальный вход Uд /48 МГц/ первого ключа 17, четвертым - первый управляющий вход второго ключа 18, подключенный к управляющему выходу последнего 16600 блока регистров. Последний выход распределителя 19 импульсов подключен к второму управляющему входу первого ключа 17 и является управляющим выходом блока 161 в следующий блок 162, где подключен к первому управляющему входу первого ключа 17. Выход первого ключа 17 подключен к входу распределителя 19 импульсов, выходы которого последовательно с первого по последний 800-й подключены к первым управляющим входам разрядов параллельно восьми регистрам 201-8. Выход второго ключа 18 подключен параллельно к вторым управляющим входам всех разрядов восьми регистров 20. Блоки с 8 по 13 идентичны и предназначены для формирования длительности излучения каждого светодиода 21 /фиг.8/, т.е. для запитывания светодиодов на длительность прямо пропорционально величине кода цветового сигнала. Плосокпанельные светодиодные экраны 14 и 15 /СД-экраны/ идентичны, каждый представляет совокупность элементов матрицы, которых при разрешении /800×600/ 480000 штук, каждый элемент матрицы содержит три светодиодные ячейки /СД-ячейки/, включающие три микросветодиода, излучающих три основных цвета R, G, В. СД-ячека включает /фиг.5/ последовательно расположенные микросветодиод 21 белого свечения и цветной светофильтр 22 одного из основных цветов СД-ячеек 1440000 /300×600×3/. Три СД-ячейки составляют один элемент матрицы /фиг.6/, формирующий один пиксел на экране. Расположение элементов матрицы в экране на фиг.7. В качестве светодиодов применяются сверхьяркие светодиоды белого свечения, например, фирм "Nichia", "Ledtronics", "Kingbright" [3, c.47], которые выполняются методом микроэлектронной технологии микросветодиодами без корпусов непосредственно в материале экрана 14 /15/. Размер отдельного микросветодиода 0,025×0,625 мм, размер элемента матрицы 0,05×0,05 мм /фиг.6/. При разрешении 800×600 размеры экрана 14 /15/ составляют:

по горизонтали 800×0,05 мм = 40 мм,

по вертикали 600×0,05 мм = 30 мм, по диагонали 50 мм, 1,97″.

Уровень яркости СД-ячейки в периоде кадра определяется величиной кода. своего цветового сигнала: чем больше код, тем дольше излучает микросветодиод ячейки за период кадра, тем ярче воспринимается зрением зрителя уровень яркости. А яркость и цветовой тон пиксела определяются скважностью излучений трех микросветодиодов в элементе каждой матрицы. А длительность излучения микросветодиода определяется длительностью его запитывания от источника 28 /фиг.8/ питания, формируемого соответствующим преобразователем "код - длительность излучения" /в блоках 8-13 формирования управляющих сигналов/.

Блоки с 8 по 13 идентичны, каждый включает /фиг.8/ генератор 23 импульсов и с первого по 480000-й преобразователи "код - длительность излучения", которые идентичны и каждый включает последовательно соединенные первый ключ 24, вычитающий счетчик 25 импульсов, дешифратор 26 и второй ключ 27, и источник 28 питания. Генератор 23 является умножителем частоты, при частоте кадров 100 Гц выполняет умножение 100 Гц × 270=27 кГц, которые выдает на сигнальные входы первых ключей 241-480000. Сигнал Uк /100 Гц/ открывает все ключи 24, 27 и поступает на вход генератора 23 импульсов. Коды цветового сигнала параллельно поступают на 1-8 входы вычитающих счетчиков 25 импульсов. Напряжение /3 В/ с источника 28 питания через открытый ключ 27 запитывает свой микросветодиод 21, а на счетный вход вычитающего счетчика 25 через открытый ключ 24 поступают импульсы 27 кГц с генератора 23. Пока длится процесс вычитания, в счетчике 25 длится и излучение микпосветодиода 21. Процесс вычитания длится до появления в счетчике 25 кода 00000000, с приходом которого в дешифратор 26 он выдает сигнал Uз, закрывающий ключи 24, 27. Питание микросветодиода 21 прекращается, излучение его заканчивается. При длительности кадра 10 мс /100 Гц/ коду 00000001 соответствует длительность излучения в один импульс 37 мкс / /, коду 00000010 соответствует длительность в два импульса 74 мкс, коду 00000011 - три импульса 111 мкс и т.д, коду 11111110 - 254 импульсов 9,398 мс, коду 11111111 - 255 импульсов 9,435 мс. Инерционность срабатывания микросветодиода менее 1 мкс. Излучения трех цветов R, G, В от трех микросветодиодов /три субпиксела/, составляющих один элемент матрицы экрана, формируют изображение /яркость и цветовой тон/ пиксела. Синхронное высвечивание всеми элементами матрицы всех пикселов кадра /1440000/ в совокупности составляет изображение кадра. Из процесса получения изображения на экране исключаются строчная и кадровая развертки. Процесс упрощается, при инерцицонности срабатывания микросветодиодов в 1 мкс частота кадров может быть повышена до 1000 Гц. Однотипность применяемых в блоках 2-7 и в блоках 8-13 электронных схем позволяет каждий из них выполнить в одной микросхеме.

/, коду 00000010 соответствует длительность в два импульса 74 мкс, коду 00000011 - три импульса 111 мкс и т.д, коду 11111110 - 254 импульсов 9,398 мс, коду 11111111 - 255 импульсов 9,435 мс. Инерционность срабатывания микросветодиода менее 1 мкс. Излучения трех цветов R, G, В от трех микросветодиодов /три субпиксела/, составляющих один элемент матрицы экрана, формируют изображение /яркость и цветовой тон/ пиксела. Синхронное высвечивание всеми элементами матрицы всех пикселов кадра /1440000/ в совокупности составляет изображение кадра. Из процесса получения изображения на экране исключаются строчная и кадровая развертки. Процесс упрощается, при инерцицонности срабатывания микросветодиодов в 1 мкс частота кадров может быть повышена до 1000 Гц. Однотипность применяемых в блоках 2-7 и в блоках 8-13 электронных схем позволяет каждий из них выполнить в одной микросхеме.

Работа системы.

Блок 1 управления подключается к двум соответствующим выходам видеоадаптера ПК. На 1-/3 информационные входы блока 1 управления поступают коды цветовых сигналов левого кадра стереопары, на 4-6 информационные входы поступают коды цветовых сигналов правого кадра стереопары, на 1 и 2 управляющие входы поступают кадровые и строчные синхроимпульсы, на третий управляющий вход поступают импульсы дискретизации 48 МГц. Блок 1 управления распределяет выдачу кодов цветовых сигналов стереопары на входы накопителей 2-7 кодов кадра. За время первого кадра регистры 16 в накопителях 2-7 кодов кадра заполняются /фиг.2/ кодами левого и правого кадров стереопары. За период кадра в каждом из накопителей 2-7 кодов сосредотачиваются по 480000 кодов одного из цветовых сигналов. По окончании первого периода кадра сигнал Uвыд / при открытии вторых ключей в блоках 161-600 /фиг.3, 4/ синхронно и параллельно выдает коды кадра в параллельном виде в соответствущие блоки 8-13 формирования управляющих сигналов. Преобразователи "код - длительность излучения" преобразуют величины кодов в интервалы запитывания микросветодиодов 21 /фиг.8/, излучения которых /1440000/ в совокупности составляют изображение левого и правого кадров стереопары. Одновременное получение изображений всех пикселов кадра на экранах 14 и 15 исключает необходимость в строчной и кадровой развертках.

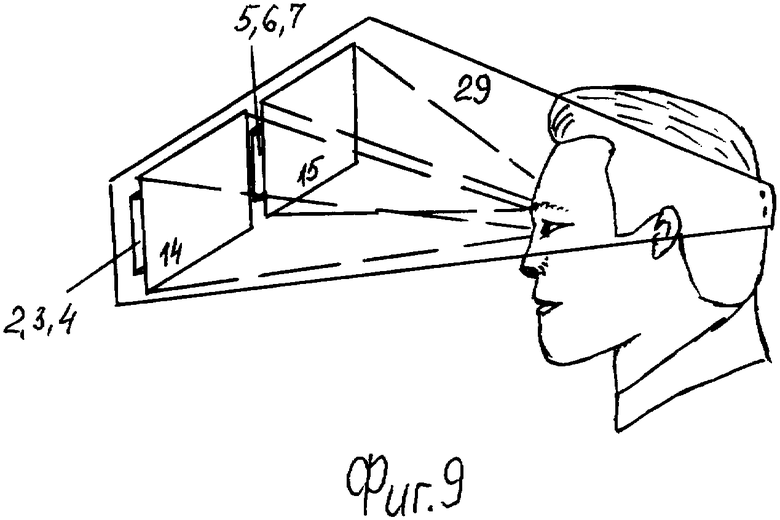

Ввиду большого числа соединений для надежной и длительной работы микросхемы накопителей 2-4 кодов кадра и блоков 8-10 формирования управляющих сигналов со своим СД-экраном 14, а также микросхемы накопителей 5-7 кодов кадра и блоков 11-13 со своим СД-экраном 15 выполняются каждые в одной неразъемной конструкции и размещаются соответствующем образом в шлеме 29 /фиг.9/. Для восприятия трехмерного пространства зритель надевает шлем на голову и наблюдает левым глазом левый экран 14, правым глазом - правый экран 15. Входы накопителей 2, 3, 4 кодов кадра 48 /24×2/, входы накопителей 5, 6, 7 кодов кадра 48 /24×2/ и 1-3 управляющие входы 6 штук /3×2/ соединяются с выходами блока 1 управления многожильным кабелем. Размер каждого экрана 40×30 мм, диагональ 50 мм /1,97″/. Разрешение кадра 480000 элементов, частота кадров 100 Гц.

Источники информации

1. Колесниченко О.В., Шишигин И.В. Аппаратные средства PC. 5-е издание, СПб., 2004, с.557, 558.

2. Патент №2281615, кл. Н04N 15/00, Бюл. №22 от 10.08.06, прототип.

3. "Радио" №9, 2004, с.47.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРИКЛАДНАЯ ТЕЛЕВИЗИОННАЯ СИСТЕМА | 2007 |

|

RU2352082C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2007 |

|

RU2334370C1 |

| ВИДЕОКАМЕРА | 2007 |

|

RU2358412C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОБЪЕМНОГО ИЗОБРАЖЕНИЯ И СИСТЕМА ТЕЛЕВИДЕНИЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2384011C1 |

| СИСТЕМА ВИРТУАЛЬНОЙ РЕАЛЬНОСТИ | 2005 |

|

RU2281615C1 |

| ПЛОСКОПАНЕЛЬНЫЙ ДИСПЛЕЙ | 2006 |

|

RU2316133C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2375841C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2369041C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2006 |

|

RU2326508C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2384012C1 |

Изобретение относится к аппаратным устройствам компьютерного оборудования и используется совместно с персональным компьютером для получения трехмерного изображения. Техническим результатом являются получение изображений на экранах без строчной и кадровой разверток и увеличение яркости изображений. Результат достигается тем, что в систему виртуальной реальности вводятся каналы левого и правого кадров стереопары, каждый из которых включает по три идентичных канала цветовых сигналов R, G, В и плосокпанельный светодиодный экран, а каждый канал цветового сигнала содержит последовательно соединенные накопитель кодов кадра и блок формирования управляющих сигналов, выходы которого подключены к входам своего плоскопанельного светодиодного экрана. 9 ил.

Система виртуальной реальности, содержащая блок управления, два соединительных кабеля и шлем, отличающаяся тем, что в нее введены канал левого кадра стереопары и канал правого кадра стереопары, каждый из которых включает по три идентичных канала цветовых сигналов R, G, В и плоскопанельный светодиодный экран, каждый канал цветового сигнала содержит последовательно соединенные накопитель кодов кадра и блок формирования управляющих сигналов, выходы которых подключены к соответствующим входам своего плоскопанельного светодиодного экрана (СД-экрана), накопители кодов кадра идентичны, каждый включает блоки регистров по числу строк в кадре, информационным входом накопителя кодов кадра являются поразрядно объединенные с первого по восьмой входы всех блоков регистров, выходами накопителя кодов кадра являются параллельные выходы всех разрядов регистров всех блоков регистров, управляющими входами являются: первым - первый управляющий вход первого блока регистров, вторым - объединенные вторые управляющие входы всех блоков регистров, третьим - объединенные третьи управляющие входы всех блоков регистров, каждый управляющий выход предыдущего блока регистров является первым управляющим входом каждого последующего блока регистров, управляющий выход последнего блока регистров подключен параллельно к четвертым управляющим входам всех блоков регистров, блоки регистров идентичны, каждый включает первый и второй ключи, распределитель импульсов и восемь регистров, информационным входом блока регистров являются поразрядно объединенные третьи входы разрядов восьми регистров, выходами блока регистров являются параллельные выходы всех разрядов восьми регистров, управляющими входами являются: первым - первый управляющий вход первого ключа, вторым - сигнальным вход второго ключа, третьим - сигнальный вход первого ключа, четвертым - первый управляющий вход второго ключа, выход первого ключа подключен к входу распределителя импульсов, выходы которого последовательно с первого по последний подключены к первым управляющим входам разрядов параллельно восьми регистров, последний выход распределителя импульсов также подключен к второму управляющему входу первого ключа и является управляющим выходом блока регистров в следующий блок регистров, выход второго ключа подключен параллельно к вторым управляющим входам всех разрядов восьми регистров и к второму управляющему входу второго ключа, блоки формирования управляющих сигналов идентичны, каждый включает генератор импульсов и преобразователи "код - длительность излучения" соответственно разрешению кадра (800×600), преобразователи "код - длительность излучения" идентичны, каждый включает последовательно соединенные первый ключ, вычитающий счетчик импульсов, дешифратор и второй ключ, и источник питания, выход которого подключен к сигнальному входу второго ключа, сигнальные входы первых ключей параллельно подключены к выходу генератора импульсов, выход первого ключа подключен к счетному входу вычитающего счетчика импульсов, выход дешифратора подключен к вторым управляющим входам первого и второго ключей, выход второго ключа является выходом преобразователя "код - длительность излучения", информационными входами которого являются с первого по восьмой входы вычитающего счетчика импульсов, информационными входами блока формирования управляющих сигналов являются входы всех вычитающих счетчиков импульсов, выходами являются выходы преобразователей "код - длительность излучения", которые подключены к соответствующим входам своего СД-экрана, управляющим входом блока формирования управляющих сигналов являются объединенные первые управляющие входы всех первых и вторых ключей преобразователей "код - длительность излучения" и вход генератора импульсов, управляющие входы всех блоков формирования управляющих сигналов объединены и подключены к первым управляющим входам накопителей кодов кадра, плоскопанельные светодиодные экраны (СД-экраны) идентичны, каждый включает элементы матрицы по числу разрешения кадра (800×600), а каждый элемент матрицы содержит три светодиодные ячейки (СД-ячейки), каждая из которых включает последовательно расположенные микросветодиод белого свечения и цветной светофильтр одного из основных цветов R, G, В, СД-ячейки в элементе матрицы образуют треугольник и выполнены методом микроэлектронной технологии микросветодиодами с соответствующими цветными светофильтрами R, G, В непосредственно в материале СД-экрана, вход каждой СД-ячейки подключен к соответствующему выходу в соответствующем блоке формирования управляющих сигналов, накопители кодов кадра и блоки формирования управляющих сигналов канала левого кадра стереопары со своим СД-экраном и накопители кодов кадра и блоки формирования управляющих сигналов канала, правого кадра стереопары со своим СД-экраном каждые выполнены одной неразъемной конструкцией и расположены соответствующим образом в шлеме, объединенные одноименные первые, вторые, третьи управляющие входы накопителей кодов кадра каналов левого и правого кадров стереопары и с первого по шестой информационные входы накопителей кодов кадра этих же каналов соединены с соответствующими выходами блока управления многожильным кабелем.

| СИСТЕМА ВИРТУАЛЬНОЙ РЕАЛЬНОСТИ | 2005 |

|

RU2281615C1 |

| US 6518939 B1, 11.02.2003 | |||

| УСТРОЙСТВО ДЛЯ ВОСПРОИЗВЕДЕНИЯ ИЗОБРАЖЕНИЯ НА ЭКРАНЕ | 1994 |

|

RU2151471C1 |

| US 5083199 A1, 21.01.1992. | |||

Авторы

Даты

2008-11-10—Публикация

2007-02-28—Подача