Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage» или «комплементарных дифференциальных усилителей (КДУ)») [1-20]. По такой архитектуре, на модификации которой выдано около 100 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Однако в практических схемах известных КДУ коэффициент ослабления входного синфазного сигнала (Кос.сф) получается небольшим (50÷60 дБ). Это связано с тем, что выходное сопротивление классических источников опорного тока на основе токовых зеркал, обеспечивающих наиболее широкий диапазон изменения входных синфазных напряжений КДУ, оказывается небольшим (30÷60 кОм).

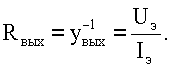

Действительно выходное сопротивление (Rвых) современных транзисторов в схеме с общим эмиттером определяется напряжением Эрли [21] (Uэ) и статическим током эмиттера Iэ:

Необходимо подчеркнуть, что уменьшение горизонтальных и вертикальных размеров интегральных биполярных транзисторов, направленное на увеличение граничной частоты усиления и степени интеграции микросхем, приводит к более сильному влиянию коллекторного напряжения на толщину активной базы, результатом чего является уменьшение напряжения Эрли и выходного дифференциального сопротивления. Так если напряжение Эрли для дискретных n-р-n транзисторов составляет Uэ.N=80...200 В, a p-n-p - Uэ.N=40...150 В, то транзисторы современных интегральных устройств имеют гораздо меньшее напряжение Эрли: Uэ.N=20...40 В, Uэ.P=15...30 В [21].

Кроме этого, напряжение Эрли интегральных горизонтальных p-n-p транзисторов (Uэ.P) обычно меньше, чем для транзисторов n-р-n - Uэ.P.<Uэ.N. Это объясняется тем, что концентрация примеси в базе горизонтального p-n-p транзистора (эпитаксиальная пленка n-типа) меньше, чем в р-базе транзисторов n-p-n [21].

Таким образом, небольшие напряжения Эрли современных транзисторов не позволяют получить (при миллиамперных токах) их выходные сопротивления больше 10-30 кОм, что отрицательно сказывается на многих параметрах КДУ и, в частности, на его коэффициенте ослабления входного синфазного сигнала (Кос.сф.).

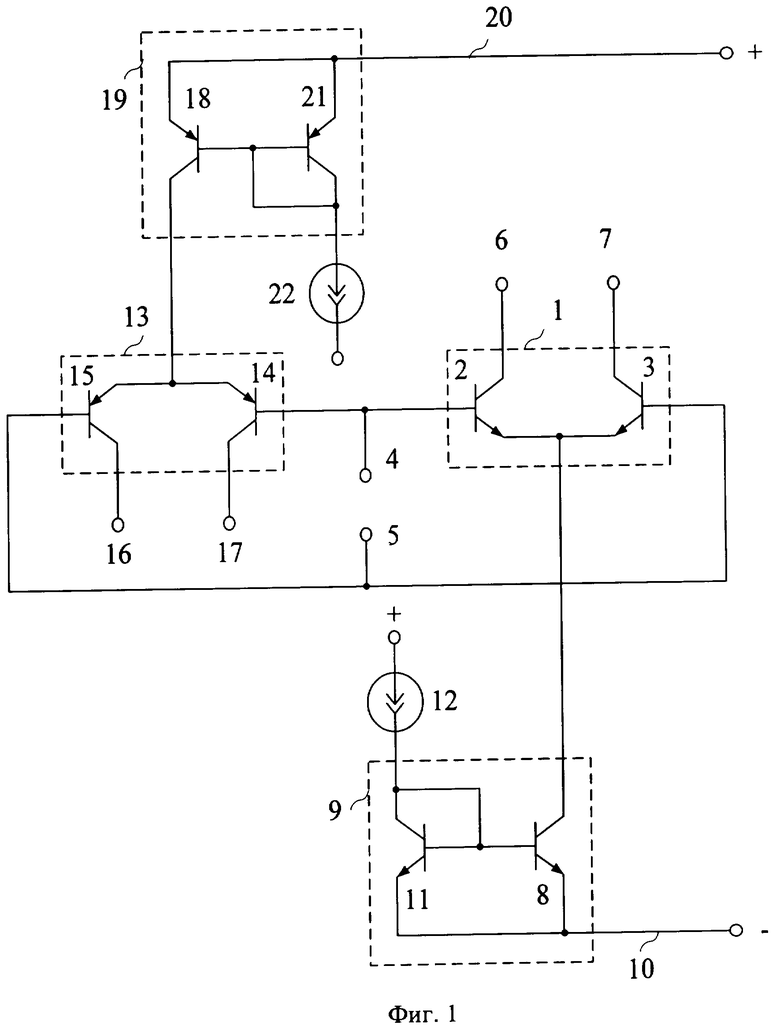

Ближайшим прототипом (фиг.1) заявляемого устройства является комплементарный дифференциальный усилитель, описанный в патенте фирмы Motorola (США) №5153529 Н 03 F 3/45, содержащий первый 1 входной дифференциальный каскад на n-p-n входных транзисторах 2 и 3, базы которых соединены с первым 4 и вторым 5 входами комплементарного дифференциального усилителя, коллекторы связаны с первой группой выходов 6 и 7 комплементарного дифференциального усилителя, а эмиттеры соединены с коллектором первого 8 выходного транзистора первого 9 источника опорного тока, причем эмиттер первого 8 выходного транзистора первого 9 источника опорного тока связан с шиной 10 отрицательного источника питания, база подключена к базе второго 11 транзистора первого 9 источника опорного тока и связана с первым 12 токостабилизирующим двухполюсником, а эмиттер второго 11 транзистора первого источника опорного тока 9 соединен с шиной отрицательного источника питания, второй 13 дифференциальный каскад на p-n-p входных транзисторах 14 и 15, базы которых соединены с первым 4 и вторым 5 входами комплементарного дифференциального усилителя, коллекторы подключены ко второй группе выходов 16 и 17 комплементарного дифференциального усилителя, а эмиттеры соединены с коллектором первого 18 выходного транзистора второго 19 источника опорного тока, причем эмиттер первого 18 выходного транзистора второго 19 источника опорного тока соединен с шиной 20 положительного источника питания, база подключена к базе второго 21 транзистора второго источника опорного тока 19 и связана со вторым 22 токостабилизирующим двухполюсником, а эмиттер второго 21 транзистора второго 19 источника опорного тока соединен с шиной 20 положительного источника питания.

Существенный недостаток известного КДУ состоит в том, что он имеет невысокое ослабление входных синфазных сигналов. В значительной степени этот недостаток проявляется в схемах без «токовых зеркал» в цепях первой (6, 7) и второй (16, 17) групп выходов [6], когда Кос.сф. получается не более чем 60 дБ.

где Ку>>1 - коэффициент усиления входного дифференциального сигнала КДУ;

Ксф.<<1 - коэффициент передачи входного синфазного сигнала КДУ.

Основная цель предлагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов.

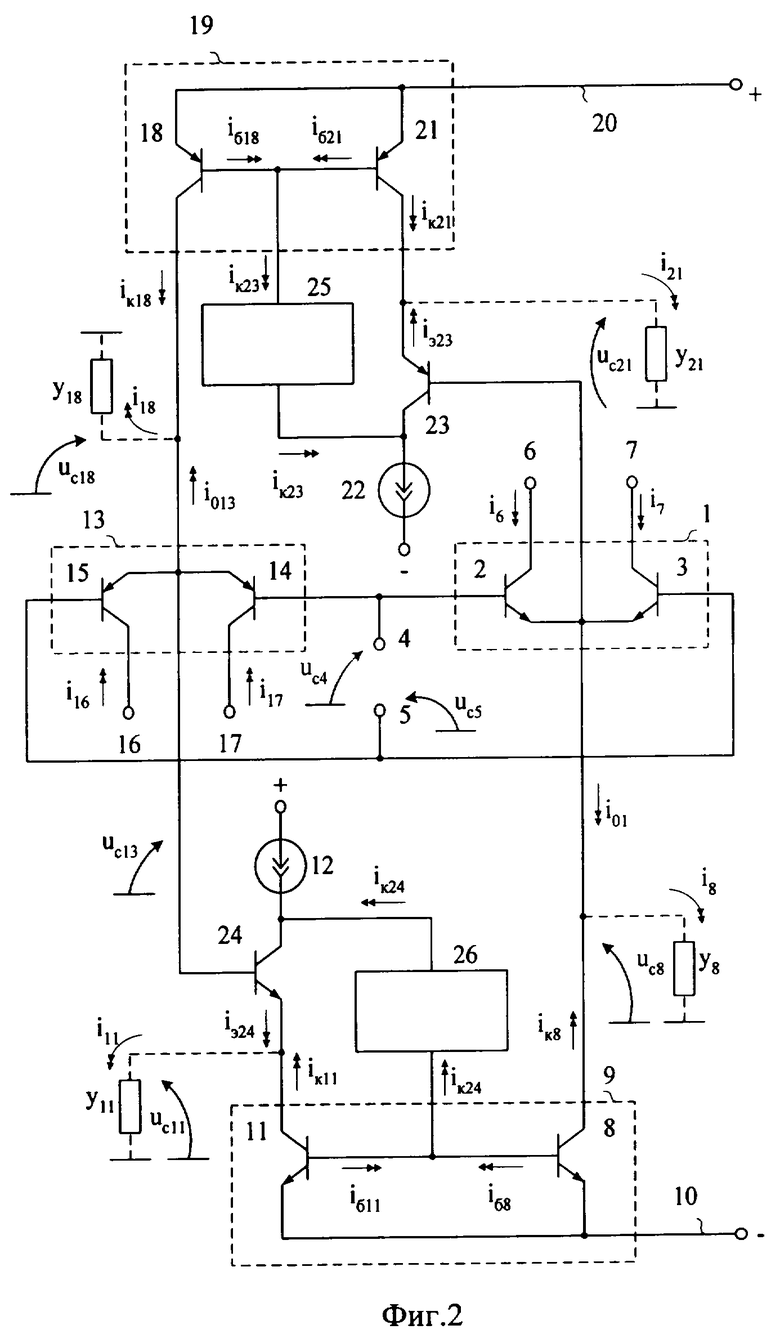

Поставленная цель достигается тем, что в комплементарном дифференциальном усилителе фиг.1, содержащем первый 1 входной дифференциальный каскад на n-p-n входных транзисторах 2 и 3, базы которых соединены с первым 4 и вторым 5 входами комплементарного дифференциального усилителя, коллекторы связаны с первой группой выходов 6 и 7 комплементарного дифференциального усилителя, а эмиттеры соединены с коллектором первого 8 выходного транзистора первого 9 источника опорного тока, причем эмиттер первого 8 выходного транзистора первого 9 источника опорного тока связан с шиной 10 отрицательного источника питания, база подключена к базе второго 11 транзистора первого 9 источника опорного тока и связана с первым 12 токостабилизирующим двухполюсником, а эмиттер второго 11 транзистора первого источника опорного тока 9 соединен с шиной отрицательного источника питания, второй 13 дифференциальный каскад на р-n-р входных транзисторах 14 и 15, базы которых соединены с первым 4 и вторым 5 входами комплементарного дифференциального усилителя, коллекторы подключены ко второй группе выходов 16 и 17 комплементарного дифференциального усилителя, а эмиттеры соединены с коллектором первого 18 выходного транзистора второго 19 источника опорного тока, причем эмиттер первого 18 выходного транзистора второго 19 источника опорного тока соединен с шиной 20 положительного источника питания, база подключена к базе второго 21 транзистора второго источника опорного тока 19 и связана со вторым 22 токостабилизирующим двухполюсником, а эмиттер второго 21 транзистора второго 19 источника опорного тока соединен с шиной 20 положительного источника питания, предусмотрены новые элементы и связи между ними (фиг.2) - в схему введены первый р-n-р 23 и второй n-р-n 24 дополнительные транзисторы, коллектор первого р-n-р дополнительного транзистора 23 соединен со вторым токостабилизирующим двухполюсником 22, который связан с базой первого 18 выходного транзистора второго 19 источника опорного тока и через первую 25 цепь согласования статического потенциала, а база первого р-n-р 23 дополнительного транзистора соединена с эмиттерами n-р-n входных транзисторов 2 и 3 первого дифференциального каскада 1, коллектор второго n-р-n дополнительного транзистора 24 соединен с первым токостабилизирующим двухполюсником 12, который связан с базой первого 8 выходного транзистора первого источника опорного тока 9 и через вторую 26 цепь согласования статического потенциала, а база второго n-р-n 24 дополнительного транзистора соединена с эмиттерами р-n-р входных транзисторов 14 и 15 второго дифференциального каскада 13.

Схема устройства в соответствии с п.1 формулы изобретения показана на фиг.2.

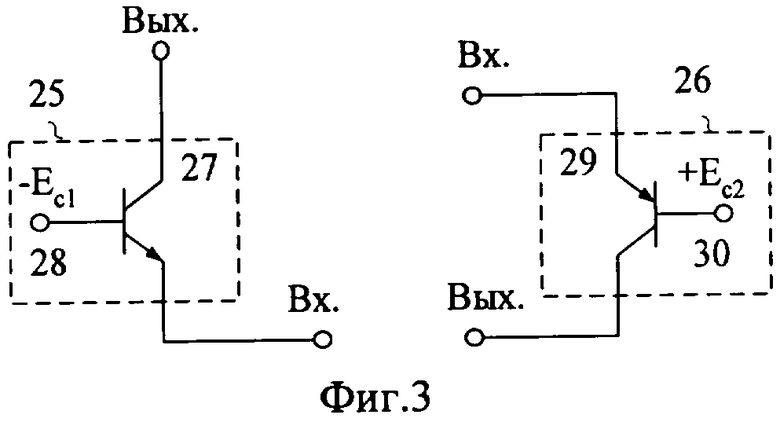

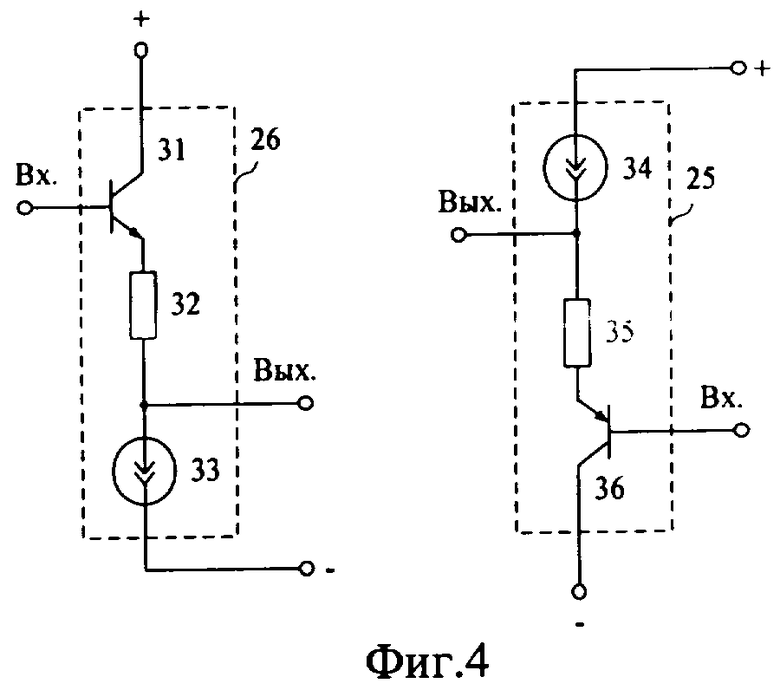

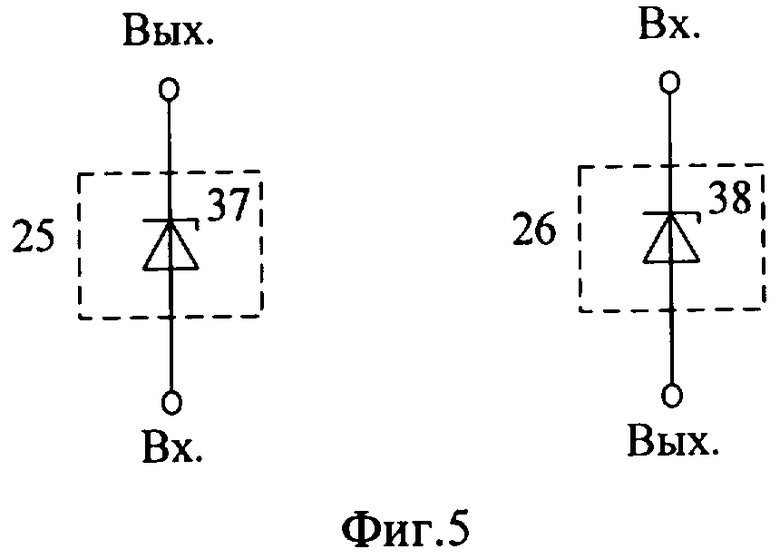

На фиг.3-5 показаны частные случаи выполнения цепей согласования статического потенциала 25 и 26.

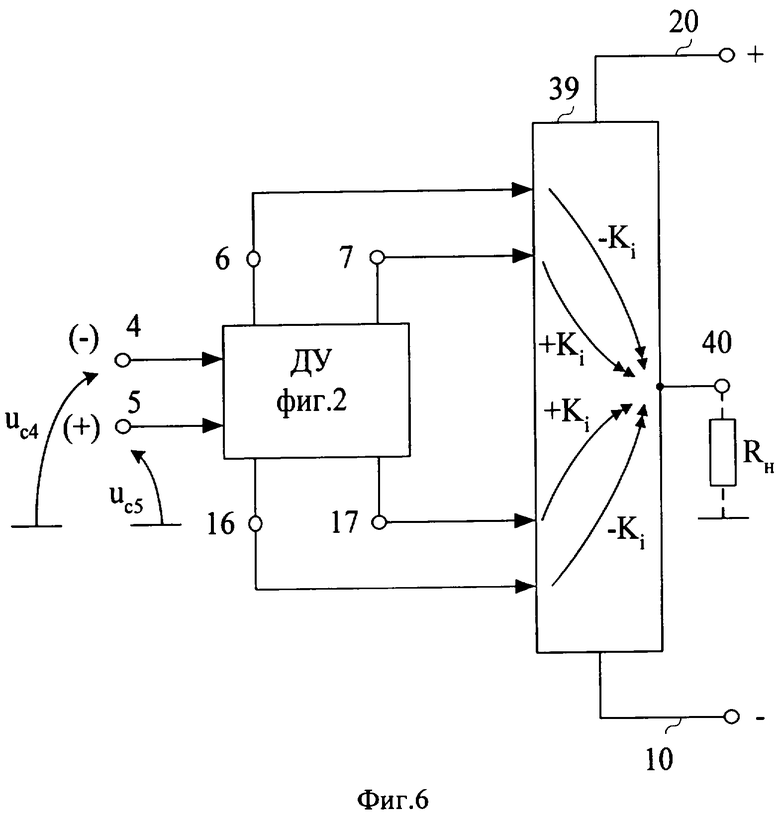

На фиг.6 приведена схема заявляемого КДУ в соответствии с ПЗ формулы изобретения.

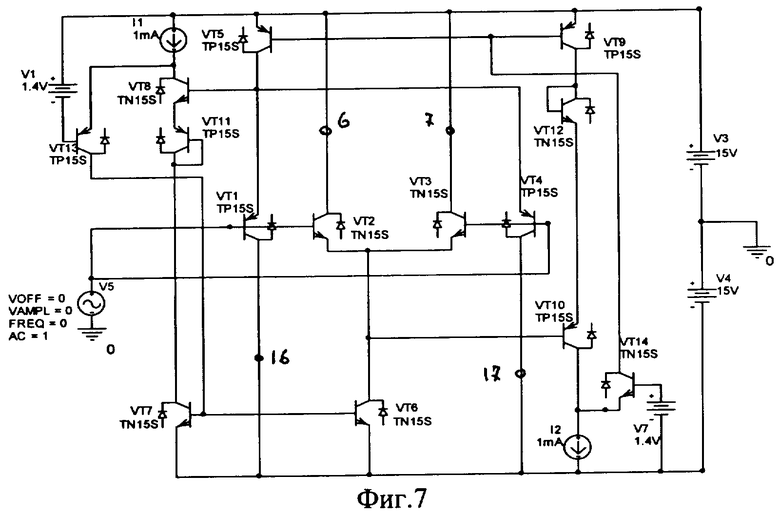

На фиг.7 показана схема заявленного устройства в среде компьютерного моделирования PSpice для режима расчета коэффициента передачи по синфазному сигналу КДУ (Ксф.).

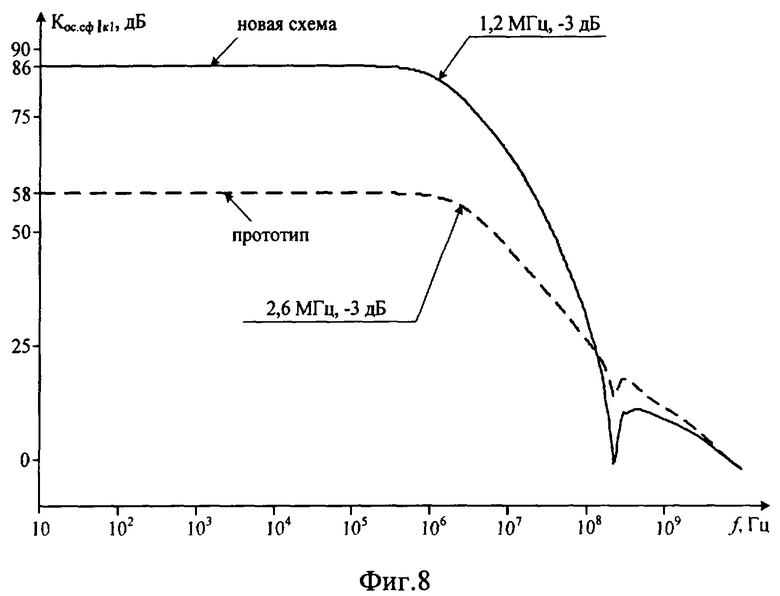

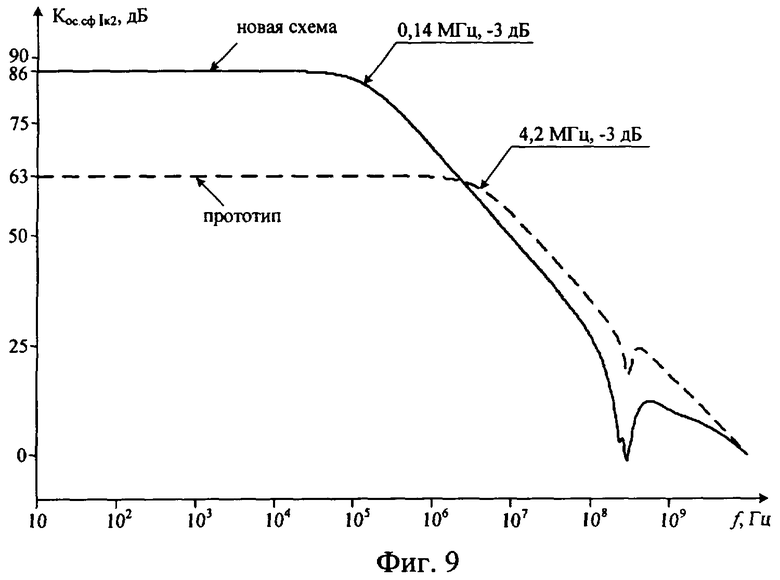

На фиг.8-9 показаны результаты компьютерного моделирования Кос.сф. сравниваемых ДУ фиг.1 и 2 в среде PSpise на моделях интегральных транзисторов ФГУП НПП «Пульсар» для второй (16 или 17, фиг.8) и первой (6, 7, фиг.9) групп выходов.

Комплементарный дифференциальный усилитель фиг.2 содержит первый 1 входной дифференциальный каскад на n-р-n входных транзисторах 2 и 3, базы которых соединены с первым 4 и вторым 5 входами комплементарного дифференциального усилителя, коллекторы связаны с первой группой выходов 6 и 7 комплементарного дифференциального усилителя, а эмиттеры соединены с коллектором первого 8 выходного транзистора первого 9 источника опорного тока, причем эмиттер первого 8 выходного транзистора первого 9 источника опорного тока связан с шиной 10 отрицательного источника питания, база подключена к базе второго 11 транзистора первого 9 источника опорного тока и связана с первым 12 токостабилизирующим двухполюсником, а эмиттер второго 11 транзистора первого источника опорного тока 9 соединен с шиной отрицательного источника питания, второй 13 дифференциальный каскад на p-n-p входных транзисторах 14 и 15, базы которых соединены с первым 4 и вторым 5 входами комплементарного дифференциального усилителя, коллекторы подключены ко второй группе выходов 16 и 17 комплементарного дифференциального усилителя, а эмиттеры соединены с коллектором первого 18 выходного транзистора второго 19 источника опорного тока, причем эмиттер первого 18 выходного транзистора второго 19 источника опорного тока соединен с шиной 20 положительного источника питания, база подключена к базе второго 21 транзистора второго источника опорного тока 19 и связана со вторым 22 токостабилизирующим двухполюсником, а эмиттер второго 21 транзистора второго 19 источника опорного тока соединен с шиной 20 положительного источника питания. В схему введены первый р-n-р 23 и второй n-р-n 24 дополнительные транзисторы, коллектор первого р-n-р дополнительного транзистора 23 соединен со вторым токостабилизирующим двухполюсником 22, который связан с базой первого 18 выходного транзистора второго 19 источника опорного тока и через первую 25 цепь согласования статического потенциала, а база первого р-n-р 23 дополнительного транзистора соединена с эмиттерами n-р-n входных транзисторов 2 и 3 первого дифференциального каскада 1, коллектор второго n-р-n дополнительного транзистора 24 соединен с первым токостабилизирующим двухполюсником 12, который связан с базой первого 8 выходного транзистора первого источника опорного тока 9 и через вторую 26 цепь согласования статического потенциала, а база второго n-р-n 24 дополнительного транзистора соединена с эмиттерами р-n-р входных транзисторов 14 и 15 второго дифференциального каскада 13.

Выходные проводимости транзисторов в схеме с общим эмиттером 18, 21, а также транзисторов 11 и 8 отражены на чертеже фиг.2 элементами y18, y21, y11, y8, на которых выделяется синфазная составляющая входных сигналов.

На чертеже фиг.3 первая цепь 25 согласования статического потенциала выполнена на вспомогательном n-р-n транзисторе 27, база которого соединена с первым источником напряжения смещения 28, а вторая цепь 26 согласования статического потенциала реализована на вспомогательном р-n-р транзисторе 29, база которого соединена со вторым источником напряжения смещения 30.

Цепи согласования статического потенциала 26 и 25, показанные на чертеже фиг.4, реализованы на транзисторе 31, резисторе 32, источнике тока 33, а также источнике тока 34, резисторе 35, транзисторе 36.

В простейшем случае роль цепей согласования статического потенциала 25 и 26 могут выполнять источники опорного напряжения 37 и 38 (фиг.5).

В соответствии с П3 формулы изобретения первая 6, 7 и вторая 16, 17 группы выходов дифференциального усилителя соединены со входами суммирующего каскада 39, выход 40 которого является основным выходом дифференциального усилителя.

Рассмотрим работу заявляемого ДУ фиг.2.

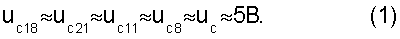

При изменении синфазного сигнала на входах 4 и 5 uc=uc5=uc4 (например, uc=5 В) на величину uc изменяются напряжения на коллекторах транзисторов 18 и 21, 11 и 8:

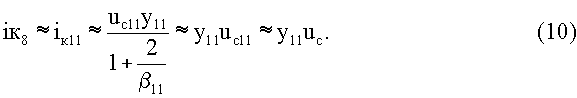

Это приводит к изменению токов через выходные проводимости y18, y21, y11, y8 транзисторов 18, 21, 11, 8

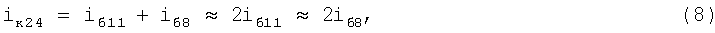

На основании первого закона Кирхгофа для токов транзисторов 24, 11 и 8 справедливы следующие соотношения:

где β11≈β8>>1 коэффициент усиления по току базы транзисторов 11 и 8.

Из уравнений (1)-(8) можно найти, что при β11>>1 ток коллектора транзистора 8 приблизительно равен току коллектора транзистора 11

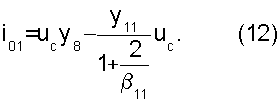

Поэтому в заявленной схеме суммарный ток i01 общей эмиттерной цепи дифференциального каскада 1, обусловленный синфазным сигналом uc, значительно меньше, чем аналогичный ток i01 в ДУ - прототипе:

После преобразований формулу (12) можно привести к виду:

где Кн1 - коэффициент неидентичности выходных проводимостей транзисторов 11 и 8. Причем

Учитывая что статический режим транзисторов 11 и 8 практически одинаков, a β11>>1, можно считать, что у11≈y8, и поэтому Кн1=1.

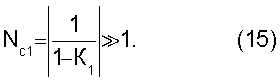

Как следствие, токи на выходах 6 и 7, обусловленные синфазным сигналом на входах КДУ 4 и 5, существенно уменьшаются. Так как коэффициенты усиления дифференциальных сигналов сравниваемых КДУ одинаковы, то это повышает коэффициент ослабления входных синфазных сигналов КДУ фиг.2 (в сравнении с КДУ - прототипом) в Nc1 - раз, где

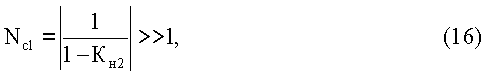

Аналогично можно показать, что Кос.сф. КДУ для второй группы выходов 16 и 17 также улучшается в Nc2 - раз, где

где

Компьютерное моделирование Кос.сф заявленного (фиг.2) и известного (фиг.1) КДУ на моделях интегральных транзисторов ФГУП НПП «Пульсар» подтверждает полученные выше теоретические выводы: Кос.сф. улучшается для каждого из выходов (6, или 7, или 16, или 17) более на порядок. Более значительное улучшение Кос.сф. наблюдается в КДУ, реализованном в соответствии с П3 формулы изобретения (фиг.6).

Следует заметить, что повышение Кос.сф в заявленном устройстве обеспечивается без ухудшения энергетических характеристик (токопотребления), а также диапазона изменения входных синфазных сигналов (Uc.max).

Кроме этого КДУ фиг.2 может работать при малых напряжениях питания. Это является существенным достоинством заявленной схемы.

Источники информации

1. Патент РФ №2193273, H03F 3/45.

2. Патент Японии №53-25232, H03F 3/26, 98(5) А332.

3. Патент US 2001/0052818 A1, H03F, 3/45.

4. Патент Японии №JP 8222972.

5. Авт. свид. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М. Радио и связь, 1989. - стр.103, Рис.6.11.

7. Патент США №6366170 B1, H03F3/45.

8. Патент США №6268769, H03F3/45.

9. Патент США №3974455, H03F3/45.

10. Патент США №3968451, H03F3/45.

11. Патент США №4837523, H03F3/45.

12. Патент США №5291149, H03F3/45.

13. Патент США №4636743, H03F3/45.

14. Патент США №4783637, H03F3/45.

15. Патент США №5515005, H03F3/45.

16. Патент США №5291149, H03F3/45.

17. Патент США №5140280, H03F3/45.

18. Патент США №5455535, H03F3/45.

19. Патент США №5523718, H03F3/45.

20. Патент США №4600893, H03F3/45.

21. Дворников О.В. Схемотехника биполярно-полевых аналоговых микросхем. Chip News, #10 (93), 2004, стр.41.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2320078C1 |

| КОМПЛЕМЕНТАРНЫЙ ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2370879C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321159C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319291C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321158C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2011 |

|

RU2441314C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2319294C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ ПИТАНИЯ | 2008 |

|

RU2384934C2 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2393629C1 |

Устройство относится к области радиотехники и связи и может быть использовано в различных микроэлектронных устройствах усиления и преобразования аналоговых сигналов с малым напряжением питания. Техническим результатом изобретения является повышение коэффициента ослабления входного синфазного сигнала. Комплементарный дифференциальный усилитель (КДУ) содержит входной дифференциальный каскад (ДК) (1) на n-p-n транзисторах (Т) (2) и (3), базы которых соединены с первым (4) и вторым (5) входами КДУ, коллекторы - связаны с первой группой выходов (6) и (7) КДУ, а эмиттеры - соединены с коллектором выходного Т (8) источника опорного тока (ИОТ) (9), причем эмиттер Т (8) связан с шиной (10) отрицательного источника питания (ИП), база -подключена к базе Т (11) ИОТ (9) и связана с токостабилизирующим двухполюсником (ТД) (12), а эмиттер Т (11) соединен с шиной отрицательного ИП. А также содержит второй входной ДК (13) на p-n-р Т (14) и (15), коллекторы которых подключены ко второй группе выходов (16) и (17) КДУ, а эмиттеры соединены с коллектором Т (18) второго ИОТ (19), база - подключена к базе второго Т (21) ИОТ (19) и связана со вторым ТД (22). Введены p-n-р Т (23) и n-p-n Т (24), коллектор Т (23) соединен с ТД (22), который связан с базой Т (18) через цепь согласования статического потенциала (Ц) (25), а база Т (23) соединена с эмиттерами Т (2) и (3) ДК (1). Коллектор Т (24) соединен с ТД (12), который связан с базой Т (8) через вторую Ц (26), а база Т (24) соединена с эмиттерами Т (14) и (15) ДК (13). 2 з.п. ф-лы, 9 ил.

| US 5153529 А, 06.10.1992 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| Дифференциальный усилитель | 1988 |

|

SU1608784A2 |

| US 4272728, 09.06.1981 | |||

| СПОСОБ ОРГАНИЗАЦИИ ТОПОЧНОГО ПРОЦЕССА—Б i^TCu:^.;....:• ^^^; -JiJHTKa -^|'сМ:ИЧ^г--;Л!::.5A;:aiJi:A | 0 |

|

SU173370A1 |

Авторы

Даты

2008-03-10—Публикация

2006-08-31—Подача