Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения (например, операционных усилителях (ОУ)).

Известны схемы дифференциальных усилителей (ДУ), реализованных на основе двух параллельно включенных комплементарных дифференциальных каскадов (ДК) с источниками опорного тока в эмиттерных цепях входных транзисторов (так называемые «dual input stage», или «комплементарные дифференциальные усилители (КДУ)») [1-21]. По такой архитектуре, на модификации которой выдано около 50 патентов различных стран, выполнены операционные усилители ведущих микроэлектронных фирм (AD8631, AD8632, НА2539 и др.). Однако в практических схемах известных КДУ напряжение смещения нуля измеряется единицами милливольт. Это связано с несимметрией архитектуры КДУ.

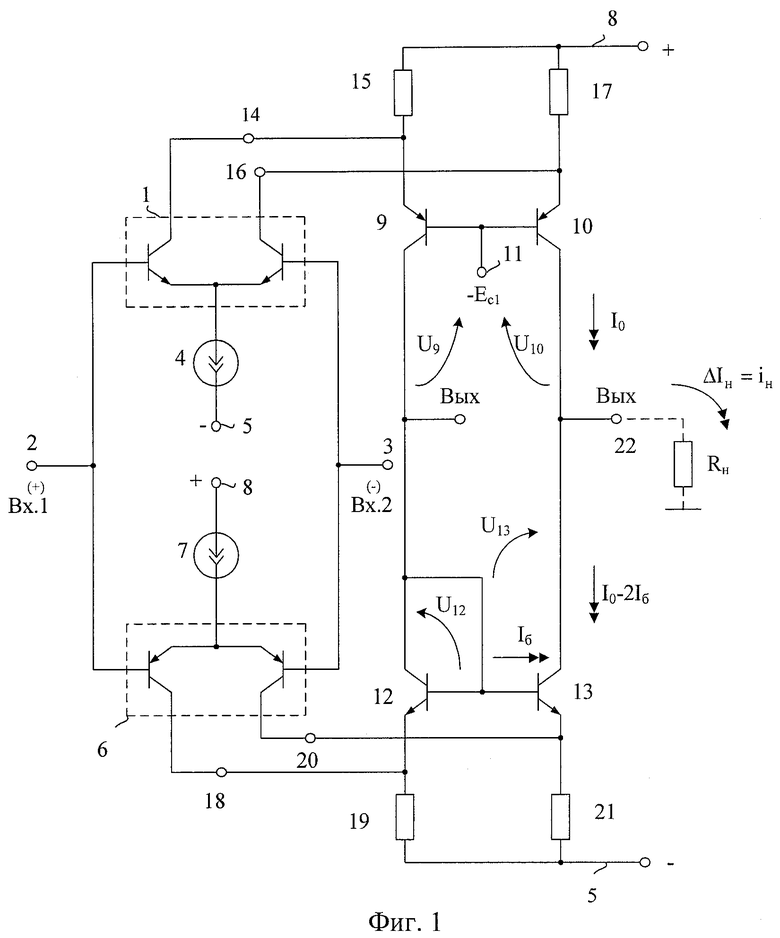

Ближайшим прототипом (фиг.1) заявляемого устройства является комплементарный каскодный дифференциальный усилитель AD8631, описанный в патенте фирмы Analog Devices, США, №4.649.352, fig.1, содержащий первый дифференциальный каскад 1 на n-p-n транзисторах, базы которых подключены ко входам 2 и 3 комплементарного каскодного дифференциального усилителя, а эмиттеры связаны с первым источником опорного тока 4, согласованного с шиной 5 отрицательного источника питания, второй дифференциальный каскад 6 на p-n-p транзисторах, базы которых подключены ко входам 2 и 3 комплементарного каскодного дифференциального усилителя, а эмиттеры связаны со вторым источником опорного тока 7, согласованного с шиной 8 положительного источника питания, первый 9 и второй 10 выходные p-n-p транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения 11, первый 12 и второй 13 выходные n-p-n транзисторы, базы которых объединены, причем эмиттер первого 9 выходного p-n-p транзистора соединен с первым 14 токовым выходом первого дифференциального каскада 1 на n-p-n транзисторах и через первый 15 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер второго 10 выходного p-n-p транзистора связан со вторым 16 токовым выходом первого дифференциального каскада 1 на n-p-n транзисторах и через второй 17 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер первого 12 выходного n-p-n транзистора соединен с первым 18 токовым выходом второго дифференциального каскада 6 на p-n-p транзисторах и через третий 19 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, эмиттер второго 13 выходного n-p-n транзистора соединен со вторым 20 токовым выходом второго дифференциального каскада 6 на p-n-p транзисторах и через четвертый 21 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, коллектор второго 10 выходного p-n-p транзистора и коллектор второго 13 выходного n-p-n транзистора подключены к выходу 22 комплементарного каскодного дифференциального усилителя, а коллекторы первого 9 выходного p-n-p и первого 12 выходного n-p-n транзисторов связаны друг с другом.

Существенный недостаток известного КДУ состоит в том, что он имеет сравнительно большое напряжение смещения нуля Uсм. Это связано с особенностями его архитектуры.

Основная цель предлагаемого изобретения состоит в уменьшении напряжения смещения нуля.

Поставленная цель достигается тем, что в комплементарном каскодном дифференциальном усилителе, фиг.1, содержащем первый дифференциальный каскад 1 на n-p-n транзисторах, базы которых подключены ко входам 2 и 3 комплементарного каскодного дифференциального усилителя, а эмиттеры связаны с первым источником опорного тока 4, согласованного с шиной 5 отрицательного источника питания, второй дифференциальный каскад 6 на p-n-p транзисторах, базы которых подключены ко входам 2 и 3 комплементарного каскодного дифференциального усилителя, а эмиттеры связаны со вторым источником опорного тока 7, согласованного с шиной 8 положительного источника питания, первый 9 и второй 10 выходные p-n-p транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения 11, первый 12 и второй 13 выходные n-p-n транзисторы, базы которых объединены, причем эмиттер первого 9 выходного p-n-p транзистора соединен с первым 14 токовым выходом первого дифференциального каскада 1 на n-p-n транзисторах и через первый 15 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер второго 10 выходного p-n-p транзистора связан со вторым 16 токовым выходом первого дифференциального каскада 1 на n-p-n транзисторах и через второй 17 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер первого 12 выходного n-p-n транзистора соединен с первым 18 токовым выходом второго дифференциального каскада 6 на p-n-p транзисторах и через третий 19 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, эмиттер второго 13 выходного n-p-n транзистора соединен со вторым 20 токовым выходом второго дифференциального каскада 6 на p-n-p транзисторах и через четвертый 21 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, коллектор второго 10 выходного p-n-p транзистора и коллектор второго 13 выходного n-p-n транзистора подключены к выходу 22 комплементарного каскодного дифференциального усилителя, а коллекторы первого 9 выходного p-n-p и первого 12 выходного n-p-n транзисторов связаны друг с другом, предусмотрены новые связи - коллектор первого 9 выходного p-n-p транзистора соединен со входом первого 23 дополнительного токового зеркала, коллектор первого 12 выходного транзистора соединен со входом второго 24 дополнительного токового зеркала, выход первого 23 дополнительного токового зеркала соединен с эмиттером второго 10 выходного p-n-p транзистора, выход второго 24 дополнительного токового зеркала соединен с эмиттером второго 13 n-p-n выходного транзистора, а объединенные базы первого 12 и второго 13 выходных n-p-n транзисторов подключены к дополнительному отрицательному источнику напряжения смещения 25.

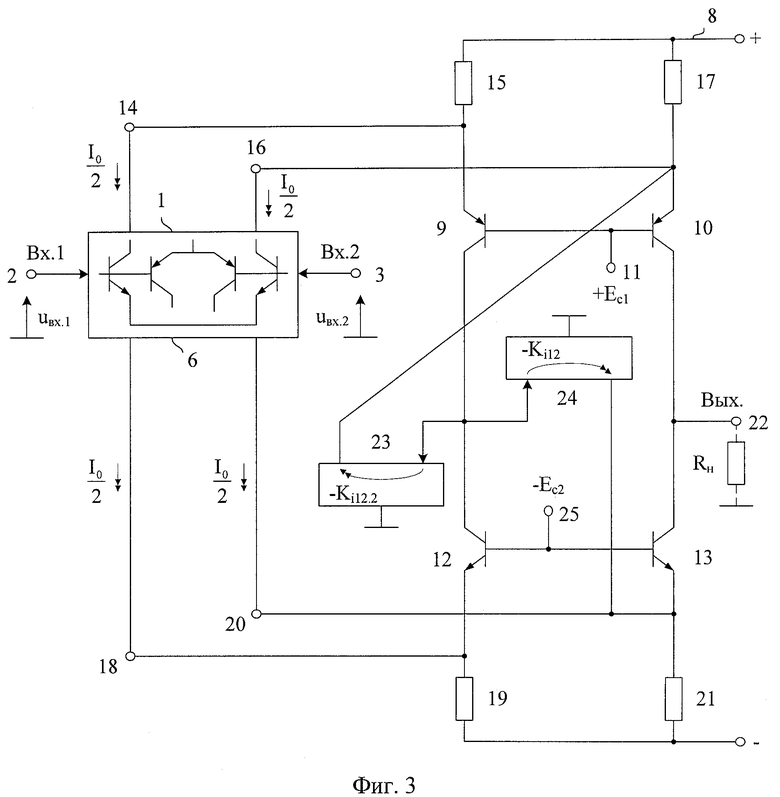

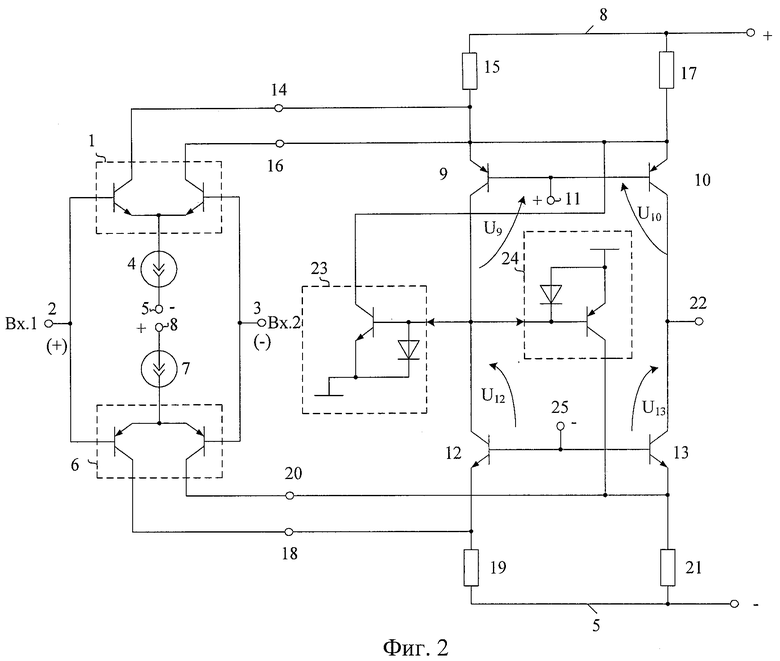

Схема заявляемого устройства в соответствии с формулой изобретения показана на фиг.2.

На фиг.3 показана обобщенная схема заявляемого устройства фиг.2.

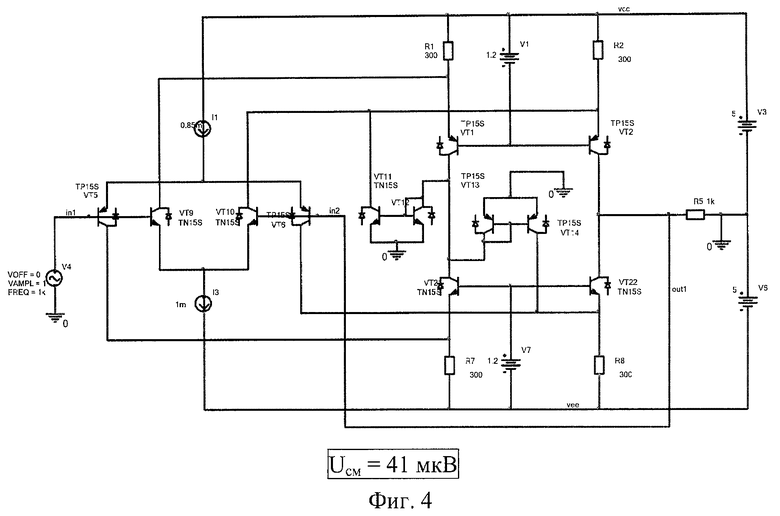

На фиг.4 показана схема фиг.2 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

На фиг.5 показана схема КДУ-прототипа фиг.1 в среде компьютерного моделирования PSpice на моделях интегральных транзисторов ФГУП НПП «Пульсар».

Комплементарный каскодный дифференциальный усилитель, фиг.2, содержит первый дифференциальный каскад 1 на n-p-n транзисторах, базы которых подключены ко входам 2 и 3 комплементарного каскодного дифференциального усилителя, а эмиттеры связаны с первым источником опорного тока 4, согласованного с шиной 5 отрицательного источника питания, второй дифференциальный каскад 6 на p-n-p транзисторах, базы которых подключены ко входам 2 и 3 комплементарного каскодного дифференциального усилителя, а эмиттеры связаны со вторым источником опорного тока 7, согласованного с шиной 8 положительного источника питания, первый 9 и второй 10 выходные p-n-p транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения 11, первый 12 и второй 13 выходные n-p-n транзисторы, базы которых объединены, причем эмиттер первого 9 выходного p-n-p транзистора соединен с первым 14 токовым выходом первого дифференциального каскада 1 на n-p-n транзисторах и через первый 15 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер второго 10 выходного p-n-p транзистора связан со вторым 16 токовым выходом первого дифференциального каскада 1 на n-p-n транзисторах и через второй 17 токостабилизирующий двухполюсник связан с шиной 8 положительного источника питания, эмиттер первого 12 выходного n-p-n транзистора соединен с первым 18 токовым выходом второго дифференциального каскада 6 на p-n-p транзисторах и через третий 19 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, эмиттер второго 13 выходного n-p-n транзистора соединен со вторым 20 токовым выходом второго дифференциального каскада 6 на p-n-p транзисторах и через четвертый 21 токостабилизирующий двухполюсник связан с шиной 5 отрицательного источника питания, коллектор второго 10 выходного p-n-p транзистора и коллектор второго 13 выходного n-p-n транзистора подключены к выходу 22 комплементарного каскодного дифференциального усилителя, а коллекторы первого 9 выходного p-n-p и первого 12 выходного n-p-n транзисторов связаны друг с другом. Коллектор первого 9 выходного p-n-p транзистора соединен со входом первого 23 дополнительного токового зеркала, коллектор первого 12 выходного транзистора соединен со входом второго 24 дополнительного токового зеркала, выход первого 23 дополнительного токового зеркала соединен с эмиттером второго 10 выходного p-n-p транзистора, выход второго 24 дополнительного токового зеркала соединен с эмиттером второго 13 n-p-n выходного транзистора, а объединенные базы первого 12 и второго 13 выходных n-p-n транзисторов подключены к дополнительному отрицательному источнику напряжения смещения 25.

Проведем сравнительный анализ КДУ фиг.1 и фиг.2 на постоянном токе.

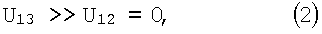

Первая «схемотехническая» причина повышенных значений напряжения смещения нуля Uсм в КДУ-прототипе, фиг.1, - асимметричные режимы работы транзисторов 12 и 13, а также транзисторов 9, 10 по напряжению коллектор-база. Действительно, для КДУ, фиг.1

где U10, U9, U13, U12 - напряжение коллектор-база транзисторов 10, 9, 13 и 12.

Неодинаковые напряжения коллектор-база транзисторов 10 и 9, 13 и 12 подчеркивают влияние эффекта Эрли (внутренней обратной связи в транзисторах) на напряжение смещения нуля. Особенно сильно это проявляется при низкоомных резисторах 15 и 17, 19 и 21.

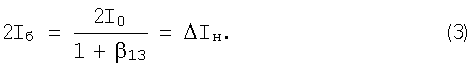

Вторая «схемотехническая» причина повышенного напряжения смещения нуля Uсм в КДУ-прототипе, фиг.1, - статическая ошибка в токовом зеркале на транзисторах 12 и 13, зависящая от коэффициента усиления по току базы (β) транзистора 13 (β13). Действительно, статический коллекторный ток транзистора 13 (Iк13=I0-2Iб) меньше коллекторного тока I0 транзистора 10 на величину

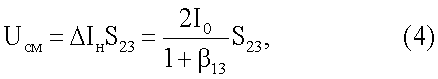

Это создает смещение нуля КДУ:

где  - крутизна преобразования входного напряжения КДУ uвх=u23 в ток его нагрузки Rн(iн).

- крутизна преобразования входного напряжения КДУ uвх=u23 в ток его нагрузки Rн(iн).

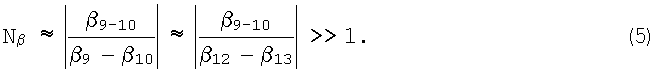

В заявляемом устройстве указанные выше эффекты минимизированы из-за высокой симметрии его схемы по координатам статического режима. Действительно, все транзисторы 9, 10, 12 и 13 работают при почти одинаковых напряжениях коллектор-база (U9≈U10, U12≈U13), что минимизирует составляющую Uсм, обусловленную эффектом Эрли. Кроме этого, вследствие высокой симметрии схемы абсолютное значение коэффициента усиления по току базы β транзисторов 9 и 10, 12 и 13 влияет здесь на Uсм в Nβ раз слабее, где

Необходимо отметить, что токовые зеркала 23 и 24 в схеме фиг.2 включаются в работу только при появлении разницы токов коллектора транзисторов 9 и 12. Если эти токи равны, то токовые зеркала 23 и 24 обесточены и не влияют на работу схемы.

Компьютерное моделирование заявляемого и известного КДУ на моделях интегральных транзисторов ФГУП НПП «Пульсар» подтверждает полученные выше теоретические выводы: Uсм улучшается более чем в 20 раз.

Следует заметить, что уменьшение Uсм в заявляемом устройстве обеспечивается без ухудшения энергетических характеристик (токопотребления), а также диапазона изменения входных синфазных сигналов (Uc.max).

Кроме этого, КДУ, фиг.2, может работать при малых напряжениях питания. Это является существенным достоинством заявляемой схемы.

Источники информации

1. Патент РФ №2193273, H03F 3/45.

2. Патент Японии №53-25232, H03F 3/26, 98(5) А332.

3. Патент US 2001/0052818 А1, H03F, 3/45.

4. Патент Японии №JP8222972.

5. Авт. свид. СССР №611288.

6. Матавкин В.В. Быстродействующие операционные усилители. - М.: Радио и связь, 1989, стр.103, рис.6.11.

7. Патент США №6.366.170 B1, H03F/45.

8. Патент США №6.268.769, H03F/45.

9. Патент США №3.974.455, H03F/45.

10. Патент США №3.968.451, H03F/45.

11. Патент США №4.837.523, H03F/45.

12. Патент США №5.291.149, H03F/45.

13. Патент США №4.636.743, H03F/45.

14. Патент США №4.783.637, H03F/45.

15. Патент США №5.515.005, H03F/45.

16. Патент США №5.291.149, H03F/45.

17. Патент США №5.140.280, H03F/45.

18. Патент США №5.455.535, H03F/45.

19. Патент США №5.523.718, H03F/45.

20. Патент США №4.600.893, H03F/45.

21. Дворников О.В. Схемотехника биполярно-полевых аналоговых микросхем. Chip News, 2004, #10 (93), стр.41.

| название | год | авторы | номер документа |

|---|---|---|---|

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412536C1 |

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| КОМПЛЕМЕНТАРНЫЙ ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2370879C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2007 |

|

RU2331966C1 |

| КОМПЛЕМЕНТАРНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411640C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2412529C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2416145C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2009 |

|

RU2411642C1 |

| КОМПЛЕМЕНТАРНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2374758C1 |

| КАСКОДНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2009 |

|

RU2402157C1 |

Изобретение относится к радиотехнике и связи для усиления аналоговых сигналов в микросхемах различного функционального назначения. Технический результат: уменьшение напряжения смещения нуля. Каскодный дифференциальный усилитель (КДУ) содержит соединенные параллельно по входу дифференциальный каскад (ДК) (1) на n-p-n транзисторах (Т) и второй ДК (6) на p-n-p Т, выходные p-n-p Т (9) и Т (10), базы которых подключены к положительному источнику напряжения смещения (ИНС) (11), а также выходные n-p-n Т (12) и Т (13), базы которых объединены, причем эмиттер Т (9) соединен с первым токовым выходом (14) ДК (1) и через токостабилизирующий двухполюсник (ТД) (15) связан с шиной (8) положительного источника питания (ИП), эмиттер Т (10) связан со вторым токовым выходом (16) ДК (1) и через второй ТД (17) связан с шиной (8) ИП, эмиттер Т (12) соединен с токовым выходом (18) второго ДК (6) и через третий ТД (19) связан с шиной (5) отрицательного ИП, эмиттер Т (13) соединен с токовым выходом (20) ДК (6) и через четвертый ТД (21) связан с шиной (5) ИП, коллекторы Т (10) и Т (13) подключены к выходу (22) КДУ, а коллекторы Т (9) и Т (12) связаны друг с другом. Коллектор Т (9) соединен со входом (23) дополнительного токового зеркала (ТЗ), коллектор Т (12) соединен со входом ТЗ (24), выход первого ТЗ (23) соединен с эмиттером Т (10), выход второго ТЗ (24) соединен с эмиттером Т (13), а объединенные базы Т (12) и Т (13) подключены к дополнительному отрицательному ИНС (25). 5 ил.

Комплементарный каскодный дифференциальный усилитель, содержащий первый дифференциальный каскад (1) на n-p-n транзисторах, базы которых подключены ко входам (2) и (3) комплементарного каскодного дифференциального усилителя, а эмиттеры связаны с первым источником опорного тока (4), согласованного с шиной (5) отрицательного источника питания, второй дифференциальный каскад (6) на p-n-p транзисторах, базы которых подключены ко входам (2) и (3) комплементарного каскодного дифференциального усилителя, а эмиттеры связаны со вторым источником опорного тока (7), согласованного с шиной (8) положительного источника питания, первый (9) и второй (10) выходные p-n-p транзисторы, базы которых объединены и подключены к положительному источнику напряжения смещения (11), первый (12) и второй (13) выходные n-p-n транзисторы, базы которых объединены, причем эмиттер первого (9) выходного p-n-p транзистора соединен с первым (14) токовым выходом первого дифференциального каскада (1) на n-p-n транзисторах и через первый (15) токостабилизирующий двухполюсник связан с шиной (8) положительного источника питания, эмиттер второго (10) выходного p-n-p транзистора связан со вторым (16) токовым выходом первого дифференциального каскада (1) на n-p-n транзисторах и через второй (17) токостабилизирующий двухполюсник связан с шиной (8) положительного источника питания, эмиттер первого (12) выходного n-p-n транзистора соединен с первым (18) токовым выходом второго дифференциального каскада (6) на p-n-p транзисторах и через третий (19) токостабилизирующий двухполюсник связан с шиной (5) отрицательного источника питания, эмиттер второго (13) выходного n-p-n транзистора соединен со вторым (20) токовым выходом второго дифференциального каскада (6) на p-n-p транзисторах и через четвертый (21) токостабилизирующий двухполюсник связан с шиной (5) отрицательного источника питания, коллектор второго (10) выходного p-n-p транзистора и коллектор второго (13) выходного n-p-n транзистора подключены к выходу (22) комплементарного каскодного дифференциального усилителя, а коллекторы первого (9) выходного p-n-p и первого (12) выходного n-p-n транзисторов связаны друг с другом, отличающийся тем, что коллектор первого (9) выходного p-n-p транзистора соединен со входом первого (23) дополнительного токового зеркала, коллектор первого (12) выходного транзистора соединен со входом второго (24) дополнительного токового зеркала, выход первого (23) дополнительного токового зеркала соединен с эмиттером второго (10) выходного p-n-p транзистора, выход второго (24) дополнительного токового зеркала соединен с эмиттером второго (13) n-p-n выходного транзистора, а объединенные базы первого (12) и второго (13) выходных n-p-n транзисторов подключены к дополнительному отрицательному источнику напряжения смещения (25).

| US 4649352 А, 10.03.1987 | |||

| ДВУХТАКТНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2000 |

|

RU2193273C2 |

| US 5294893 А, 15.03.1994 | |||

| US 5455535 А, 03.10.1995. | |||

Авторы

Даты

2010-06-27—Публикация

2009-03-19—Подача