Изобретение относится к радиотехнике и может быть использовано в системах наблюдения за радиотехнической обстановкой в составе комплекса или как автономное устройство измерения несущей частоты импульсных сигналов. Как расширение функций можно рассматривать измерение мощности и длительности входного импульсного сигнала.

В статье Бабинцева Д.В. и др. «Широкополосное цифровое приемное устройство для мгновенного измерения частоты импульсных и квазинепрерывных сигналов» (Материалы XIV отраслевого координационного семинара по СВЧ технике, Нижний Новгород, 2005 год), изложено построение цифрового измерителя частоты с усилителем-ограничителем на входе и фазовым методом обработки сигнала. Такое построение считается самым распространенным в различных пассивных системах.

Известен мгновенный измеритель частоты (МИЧ), совмещенный с обнаружителем синхронных наложенных импульсных сигналов (James B.Y., patent №4547727, Oct.15.1985, US Patent). В нем изложено построение с использованием видеосигналов, образующихся после усилителя-ограничителя, и, следовательно, имеющее ограниченные возможности по обнаружению наложенного сигнала. Кроме этого в таком устройстве отсутствует возможность измерения мощности и длительности входного импульсного сигнала.

Недостатками описанных выше МИЧ являются низкая помехозащищенность и ограниченные функциональные возможности.

Целью изобретения является повышение помехозащищенности с одновременным расширением функциональных возможностей устройства.

Поставленная цель достигается тем, что в цифровой измеритель частоты, содержащий последовательно соединенные усилитель высокой частоты, полосно-пропускающий фильтр, частотный дискриминатор с четырьмя выходами, а также аналого-цифровые преобразователи (АЦП) и вычислитель, причем вход усилителя является входом устройства, выход каждого АЦП соединен с входами вычислителя, дополнительно введены логарифмические видеоусилители (ЛВУ), аналоговый сумматор, обнаружитель импульсных сигналов, блок формирования кода мощности, блок формирования кода коррекции и цифровой сумматор, при этом вход каждого ЛВУ соединен с выходами частотного дискриминатора, выход каждого ЛВУ соединен с входом соответствующего АЦП и входами сумматора, выход сумматора соединен с входом обнаружителя, выход обнаружителя соединен с тактовым входом всех АЦП, выход каждого АЦП соединен с входами вычислителя и входами формирования кода мощности, выход вычислителя соединен с входом блока формирования кода коррекции и входом цифрового сумматора, выход блока формирования кода мощности соединен с другим входом блока формирования кода коррекции, выход блока формирования кода коррекции соединен с другим входом цифрового сумматора, выход цифрового сумматора является выходом измерителя частоты.

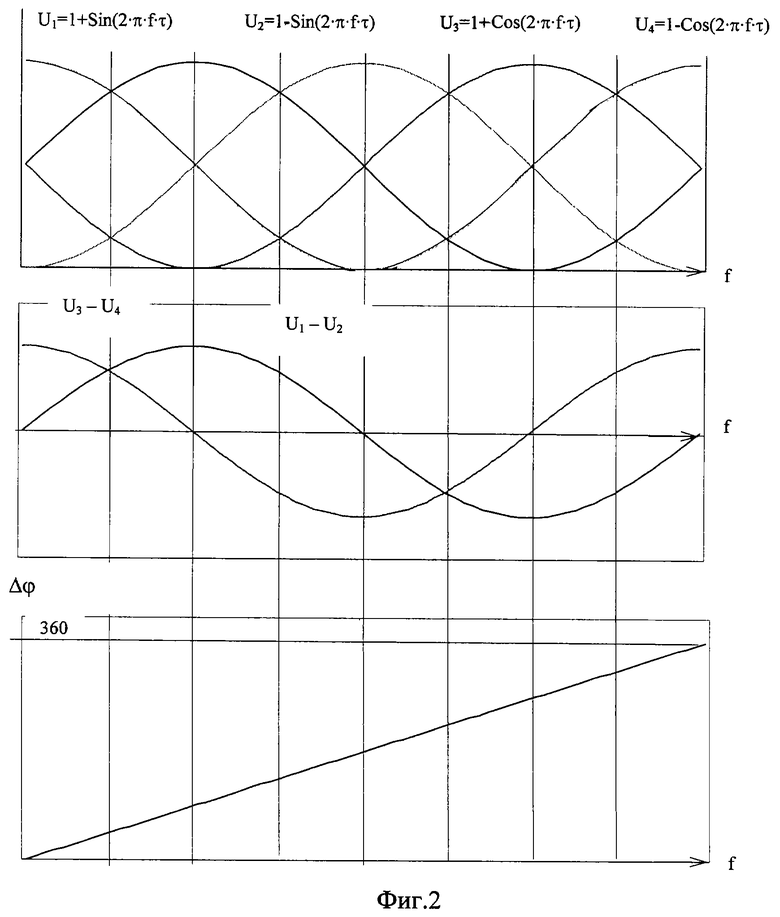

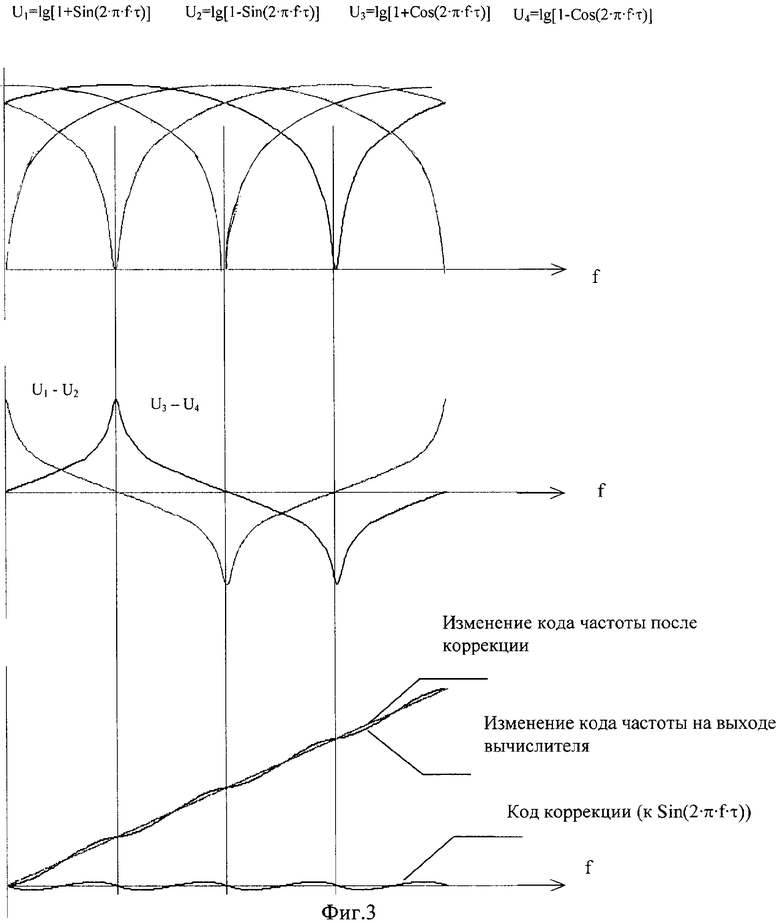

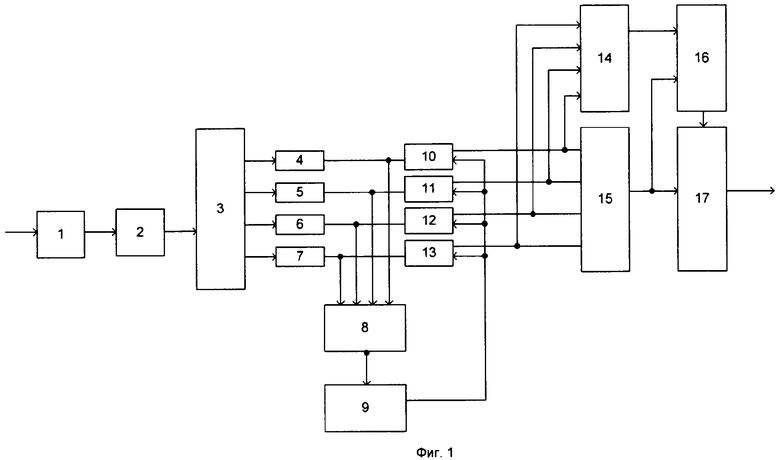

На фиг.1 приведена структурная схема МИЧ, на фиг.2, 3 - диаграммы, поясняющие работу измерителя.

Цифровой измеритель частоты содержит усилитель 1, полосно-пропускающий фильтр 2, частотный дискриминатор 3, ЛВУ 4-7, аналоговый сумматор 8, обнаружитель импульсных сигналов 9, АЦП 10-13, блок формирования кода мощности 14, вычислитель 15, блок формирования кода коррекции 16, цифровой сумматор 17.

Выход усилителя 1 соединен с входом полоснопропускающего фильтра 2, выход фильтра 2 с входом частотного дискриминатора 3, выходы дискриминатора 3 соединены с входом каждого ЛВУ 4-7, выход каждого ЛВУ 4-7 соединен с входами аналогового сумматора 8, выход сумматора 8 соединен с входом обнаружителя 9, выход обнаружителя 9 соединен с тактовым входом каждого АЦП 10-13, выход каждого АЦП 10-13 соединен с входами блока формирования кода мощности 14 и входами вычислителя 15, выход блока формирования кода мощности 14 соединен с первым входом блока коррекции 16, выход вычислителя 15 соединен с первым входом цифрового сумматора 17 и вторым входом блока формирования кода коррекции 16, выход блока формирования кода коррекции 16 соединен с вторым входом цифрового сумматора 17.

Аппаратурная реализация усилителя высокой частоты 1, полоснопропускающего фильтра 2, частотного дискриминатора 3, ЛВУ 4-7, аналогового сумматора 8, АЦП 10-13, цифрового сумматора 17 не вызывает сомнений и, в большинстве случаев, имеются даже готовые микросхемы, выполняющие требуемые функции.

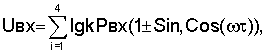

На вход обнаружителя 9 приходит сумма сигналов, пропорциональных логарифму входной мощности и функциям  и

и

, где

, где

- знак суммирования по четырем сигналам;

- знак суммирования по четырем сигналам;

k - коэффициент пропорциональности;

Рвх - уровень мощности входного сигнала;

f - несущая частота входного сигнала;

τ - величина задержки в частотном дискриминаторе.

В связи с тем, что существует зависимость от мощности входного сигнала, возможно обнаружение одиночных и наложенных (синхронизированных) сигналов в большом динамическом диапазоне входных сигналов. Обнаружитель может быть построен по принципу превышения над порогом продифференцированной суммы сигналов или по принципу превышения над порогом суммы сигналов, образующихся в результате дифференцирования перед ЛВУ. Принципиальной особенностью такого построения является то, что усилитель 1 на входе имеет небольшой коэффициент усиления, и, следовательно, динамический диапазон логарифмирования и обнаружения имеет значительную величину. В предельном случае, если не требуется высокая чувствительность обнаружения и измерения, усилитель 1 может отсутствовать. Другой особенностью является то, что обнаружение осуществляется по тем же сигналам, что и измерение, поэтому существует строгая синхронизация отсчетов, формируемых АЦП и обеспечивается, таким образом высокая точность в сочетании с высокой помехоустойчивостью, а также существует возможность измерения мощности и длительности входного сигнала.

Блок формирования кода мощности 14, блок формирования блока коррекции 16, вычислитель 15 и цифровой сумматор 17 - это обычные цифровые устройства, реализующие алгоритмы вычисления в параллельном двоичном коде, чтобы обеспечить требуемое быстродействие. Эти устройства могут быть реализованы различными широко известными цифровыми микросхемами с использованием постоянных запоминающих устройств (ПЗУ), например, в блоке формирования кода коррекции 16.

Измерение частоты осуществляется следующим образом.

Входной импульсный сигнал усиливается усилителем высокой частоты 1 и фильтруется полоснопропускающим фильтром 2, полоса пропускания которого определяется диапазоном заданных измеряемых частот. В частотном дискриминаторе осуществляется перемножение прямого и задержанного сигнала и формирование выходных видеосигналов, пропорциональных величине

и мощности Рвх входного сигнала. После усиления каждого из четырех сигналов на выходе ЛВУ формируются сигналы, пропорциональные lg[Рвх

и мощности Рвх входного сигнала. После усиления каждого из четырех сигналов на выходе ЛВУ формируются сигналы, пропорциональные lg[Рвх )] и lg[Рвх

)] и lg[Рвх )]. Эти сигналы суммируются аналоговым сумматором 8, а обнаружителем 9 формируются сигналы обнаружения и синхронизации (тактирования) АЦП 10-13.

)]. Эти сигналы суммируются аналоговым сумматором 8, а обнаружителем 9 формируются сигналы обнаружения и синхронизации (тактирования) АЦП 10-13.

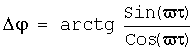

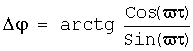

АЦП преобразуют аналоговые сигналы в цифровой двоичный код, по которому вычислителем 15 вычисляется величина  а в блоке формирования кода мощности - мощность входного сигнала в логарифмическом масштабе.

а в блоке формирования кода мощности - мощность входного сигнала в логарифмическом масштабе.

При малом входном сигнале, когда ЛВУ работает в линейном режиме, вычислитель формирует код, пропорциональный частоте входного сигнала. Для этого коды АЦП вначале вычитаются попарно и формируются коды, пропорциональные величине  и

и  . Затем из старших разрядов продуктов вычитания формируется октантная логика (три старших разряда выходного кода

. Затем из старших разрядов продуктов вычитания формируется октантная логика (три старших разряда выходного кода  ). Из оставшихся разрядов в вычислителе формируются коды, пропорциональные

). Из оставшихся разрядов в вычислителе формируются коды, пропорциональные  или

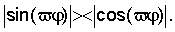

или  в зависимости от результата сравнения кодов:

в зависимости от результата сравнения кодов:  Таким образом, формируется монотонный код частоты, соответствующий изменению фазы Δϕ от 0 до 360°.

Таким образом, формируется монотонный код частоты, соответствующий изменению фазы Δϕ от 0 до 360°.

Код коррекции в линейном режиме работы ЛВУ, то есть при малом уровне мощности входного сигнала, равен нулю и, следовательно, частота входного сигнала измеряется без систематической ошибки (см. фиг.2).

По мере увеличения мощности входного сигнала и переходе на участок логарифмирования ЛВУ возникает систематическая ошибка измерения на выходе вычислителя. Для ее устранения в блоке формирования кода коррекции формируется код коррекции. После суммирования кода с выхода вычислителя с кодом коррекции в цифровом сумматоре эта систематическая ошибка исчезает, и зависимость кода частоты от частоты входного сигнала становиться линейно (см. фиг.3).

Отсчет блока формирования кода мощности можно использовать как выходной сигнал для измерения мощности входного сигнала с систематической ошибкой не более двух дБ.

В обнаружителе 9 можно реализовать функцию измерения длите входного сигнала, используя, например, результат сравнения с положительными и отрицательным порогами положительного и отрицательного продифференцированного сигнала.

Возможность измерения мощности и длительности входного сигнала относятся к дополнительным функциям устройства и формируют признак расширения функциональных возможностей в устройстве.

| название | год | авторы | номер документа |

|---|---|---|---|

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2007 |

|

RU2362179C1 |

| ЦИФРОВОЙ ИЗМЕРИТЕЛЬ ПАРАМЕТРОВ ИМПУЛЬСНЫХ СВЧ СИГНАЛОВ С ШИРОКИМ ДИАПАЗОНОМ РАБОЧИХ ЧАСТОТ | 2021 |

|

RU2775355C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2013 |

|

RU2543065C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2018 |

|

RU2682165C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2013 |

|

RU2536440C1 |

| ЦИФРОВОЙ ЧАСТОТОМЕР | 2015 |

|

RU2585513C1 |

| РАДИОПЕЛЕНГАТОР | 2012 |

|

RU2505831C2 |

| СИСТЕМА ОБНАРУЖЕНИЯ РАДИОЛОКАЦИОННЫХ СИГНАЛОВ | 2003 |

|

RU2256937C1 |

| ФАЗОВЫЙ ПЕЛЕНГАТОР | 2021 |

|

RU2776155C1 |

| СПОСОБ И УСТРОЙСТВО СЕЛЕКЦИИ СИГНАЛОВ НАДВОДНОЙ ЦЕЛИ В МОНОИМПУЛЬСНОЙ РЛС | 2004 |

|

RU2278397C2 |

Предложенное изобретение относится к радиотехнике и может быть использовано в системах наблюдения за радиотехнической обстановкой в составе комплекса или как автономное устройство измерения несущей частоты импульсных сигналов. Целью изобретения является повышение помехозащищенности с одновременным расширением функциональных возможностей устройства. Как расширение функций можно рассматривать измерение мощности и длительности входного импульсного сигнала. Цифровой измеритель частоты содержит усилитель высокой частоты, полоснопропускающий фильтр, частотный дискриминатор с четырьмя выходами, аналого-цифровые преобразователи, вычислитель, логарифмические видеоусилители, аналоговый сумматор, обнаружитель импульсных сигналов, блок формирования кода мощности, блок формирования кода коррекции и цифровой сумматор, соответствующим образом соединенные между собой. 3 ил.

Цифровой измеритель частоты, содержащий последовательно соединенные усилитель высокой частоты, полосно-пропускающий фильтр, частотный дискриминатор с четырьмя выходами, а также аналого-цифровые преобразователи (АЦП) и вычислитель, причем вход усилителя является входом устройства, выход каждого АЦП соединен с входами вычислителя, отличающийся тем, что введены логарифмические видеоусилители (ЛВУ), аналоговый сумматор, обнаружитель импульсных сигналов, блок формирования кода мощности, блок формирования кода коррекции и цифровой сумматор, при этом вход каждого ЛВУ соединен с выходами частотного дискриминатора, выход каждого ЛВУ соединен с входом соответствующего АЦП и входами аналогового сумматора, выход аналогового сумматора соединен с входом обнаружителя, выход обнаружителя соединен с тактовым входом всех АЦП, выход каждого АЦП соединен с входами вычислителя и входами формирования кода мощности, выход вычислителя соединен с входом блока формирования кода коррекции и входом цифрового сумматора, выход блока формирования кода мощности соединен с другим входом блока формирования кода коррекции, выход блока формирования кода коррекции соединен с другим входом цифрового сумматора, выход цифрового сумматора является выходом измерителя частоты.

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ МГНОВЕННОЙ ЧАСТОТЫ | 1991 |

|

RU2022278C1 |

| Способ прессования изделий из эбонитовой пыли и тому подобных пластических масс | 1933 |

|

SU34751A1 |

| Устройство для измерения частоты | 1975 |

|

SU636552A1 |

| US 4547727 A, 15.10.1985 | |||

| Пресс для выдавливания из деревянных дисков заготовок для ниточных катушек | 1923 |

|

SU2007A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

2008-05-27—Публикация

2006-10-05—Подача