Изобретение относится к шифрованию информации и может быть использовано в устройствах передачи информации для обеспечения адаптивной скрытой связи с применением ключа, передаваемого по закрытому каналу связи.

Наиболее близким по технической сущности к предлагаемому является способ, заключающийся в зашифровании на передающей стороне данных путем поразрядного суммирования по модулю 2 в сумматоре с гаммой шифра, снимаемой с выходов генератора ключа, и в расшифровании данных на приемной стороне путем суммирования зашифрованных данных поразрядно по модулю 2 с гаммой шифра [1].

Недостатком способа является отсутствие адаптивности к архитектуре микропроцессора и объемам закрываемой информации, к необходимости резкого увеличения (в разы) скорости шифрования информации (без увеличения тактовой частоты), а также относительно низкая криптостойкость.

Техническим результатом изобретения является повышение криптостойкости, скорости шифрования, а также обеспечение адаптивности к архитектуре микропроцессора и объемам закрываемой информации.

Указанный технический результат достигается тем, что в известном способе, заключающемся в том, что зашифровывают на передающей стороне данные путем поразрядного суммирования по модулю 2 с гаммой шифра и расшифровывают данные на приемной стороне, согласно изобретению на передающей и принимающей сторонах соответственно вырабатывают и вводят в соответствии с ключом сменные примитивные полиномы степени n и сменное значение расширения поля Галуа GF(2q)n, в соответствии с которыми осуществляют перенастройку генератора ключа.

Известно устройство, содержащее на передающей стороне последовательно соединенные источник информации, блок ввода, шифрующий блок, распределитель и выходной блок, а на приемной стороне последовательно соединенные входной блок, распределитель, наборный блок, дешифратор и выходной блок, соединенный с потребителем информации [2].

Недостатком устройства является отсутствие адаптивности к архитектуре микропроцессора и объемам закрываемой информации, к необходимости резкого увеличения (в разы) скорости шифрования информации (без увеличения тактовой частоты), а также относительно низкая криптостойкость.

Наиболее близким по технической сущности к предлагаемому является устройство, содержащее на передающей стороне последовательно соединенные источник информации и шифратор, а также генератор случайных чисел и рандомизатор, выходы которых соединены с соответствующими входами шифратора, а на приемной стороне - последовательно соединенные шифратор и получатель информации, а также канал связи, входы которого соединены с выходами шифратора и генератора ключа, а выход соединен с входом дешифратора [3].

Недостатком устройства является отсутствие адаптивности к архитектуре микропроцессора и объемам закрываемой информации, к необходимости резкого увеличения (в разы) скорости шифрования информации (без увеличения тактовой частоты), а также относительно низкая криптостойкость.

Технический результат изобретения также достигается тем, что в известное устройство шифрования, содержащее на передающей и приемной сторонах генератор ключа и шифрующий и дешифрующий блоки, согласно изобретению дополнительно введены на передающей и приемной сторонах соответственно последовательно соединенные блок управления, вход которого соединен с выходом источника ключевой информации, блок выработки примитивных полиномов, осуществляющий выработку полиномов заданной степени и заданного количества, блок памяти, осуществляющий выборку конкретного полинома заданной степени, другой вход которого соединен со вторым выходом блока управления, а выход соединен со входом генератора ключа, осуществляющим синтез рекуррентных регистров сдвига, второй вход которого соединен с третьим выходом блока управления, при этом на передающей стороне выход генератора ключа соединен с шифрующим блоком, другой вход которого является информационным входом устройства, а на приемной стороне выход генератора ключа соединен со входом дешифрующего блока, второй вход которого соединен с выходом канала связи, а выход является информационным выходом устройства.

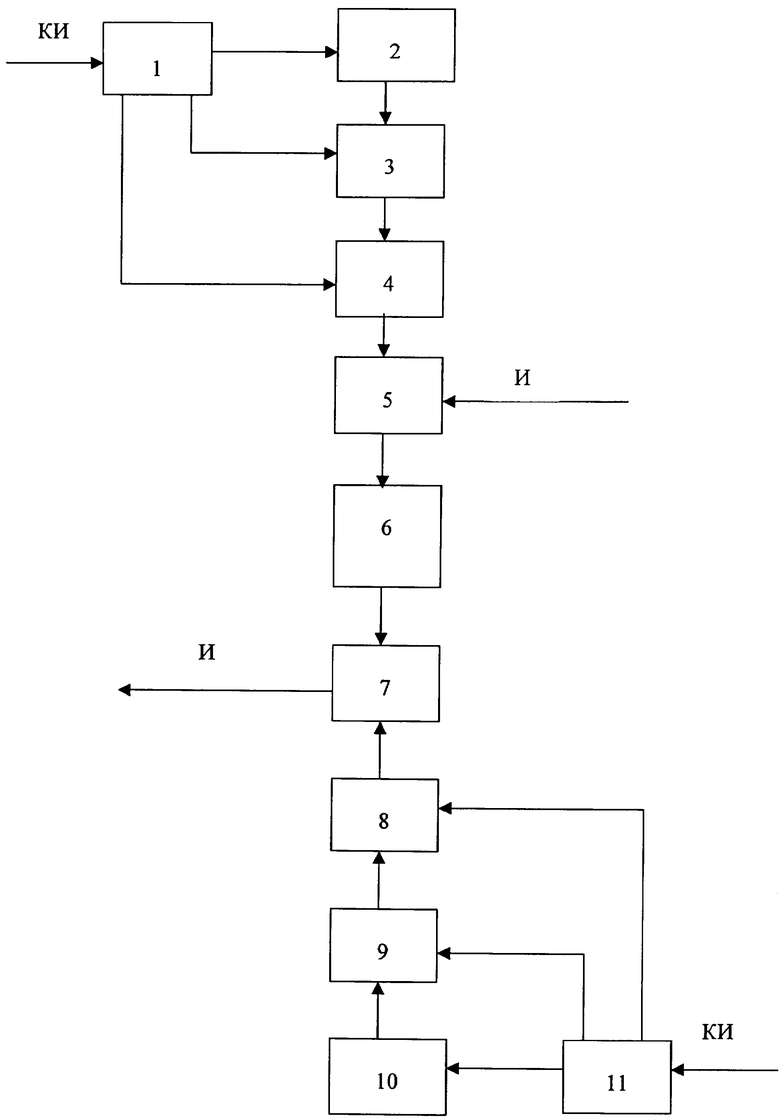

На чертеже представлена структурная схема устройства.

Устройство содержит на передающей стороне последовательно соединенные блок управления 1, вход которого соединен с выходом источника ключевой информации, блок выработки примитивных полиномов 2, блок памяти 3, другой вход которого соединен со вторым выходом блока управления, генератор ключа 4, второй вход которого соединен с третьим выходом блока управления, шифрующий блок 5, второй вход которого является информационным входом устройства, и канал связи 6, а на приемной стороне устройство содержит последовательно соединенные блок управления 11, вход которого соединен с выходом источника ключевой информации, блок выработки примитивных полиномов 10, блок памяти 9, другой вход которого соединен со вторым выходом блока управления, генератор ключа 8, второй вход которого соединен с третьим выходом блока управления, дешифрующий блок 7, второй вход которого соединен с выходом канала связи 6, а выход является информационным выходом устройства. Блоки 1, 2, 3, 7, 8, 9 могут быть выполнены в виде ПЗУ (постоянное запоминающее устройство), информация для программирования которых приведена в [5] и при описании примера реализации способа, блоки 4 и 8 в виде стандартных генераторов [4, 6], в которых рекуррентные регистры сдвига реализованы на программируемых логических интегральных схемах (ПЛИС), информация для программирования которых приведена в [5] и при описании примера реализации способа.

Способ адаптивного поточного шифрования заключается в следующем. Блок управления 1 и 11, в зависимости от содержания ключевой информации, задает конкретные значения следующих управляющих входных параметров: для алгоритма работы блока выработки примитивных полиномов 2 и 10 - определяющих выработку полиномов заданной степени и их количество; для алгоритма работы блока памяти 3 и 9 - определяющих выборку конкретного полинома заданной степени; для алгоритма работы генератора ключа 4 и 8 - определяющих перепрограммирование ПЛИС (реализующих рекуррентные регистры сдвига генератора ключа) в соответствии с выбранным полиномом степени n и значением расширения поля Галуа GF(2q)n, а также начальное заполнение рекуррентных регистров сдвига.

Управляющий сигнал с блока управления 1 поступает на вход блока выработки примитивных полиномов 2, который по алгоритму [5] производит выработку заданного количества примитивных полиномов соответствующей степени, которые затем поступают на вход блока памяти 3, где по управляющему сигналу с блока управления 1 осуществляется выборка гаммообразующего примитивного полинома, параметры которого, а также значение расширения поля Галуа GF(2q)n, поступают на вход генератора ключа 4, в соответствии с этими параметрами по сигналу с блока управления осуществляется синтез линейных рекуррентных регистров сдвига генератора ключа путем перепрограммирования ПЛИС, а затем их начальное заполнение. В шифраторе 5 поступающая на его вход двоичная информационная последовательность складывается по модулю два с гаммой шифра и поступает на вход канала связи 6. На приемной стороне аналогично при вводе ключевой информации блок управления 11 вырабатывает соответствующие управляющие сигналы, в соответствии с которыми блок выработки примитивных полиномов 10 по алгоритму [5] производит выработку заданного количества примитивных полиномов соответствующей степени, которые затем поступают на вход блока памяти 9, где по управляющему сигналу с блока управления 11 осуществляется выборка гаммообразующего примитивного полинома, параметры которого, а также значение расширения поля Галуа GF(2q)n поступают на вход генератора ключа 8, в соответствии с этими параметрами по сигналу с блока управления осуществляется перепрограммирование (синтез) линейных рекуррентных регистров сдвига (ЛРРС) генератора ключа, выполненных на ПЛИС, а затем их начальное заполнение. В дешифраторе 7 поступающая на его вход с выхода канала связи 6 двоичная зашифрованная последовательность складывается по модулю два с гаммой шифра, и с выхода дешифратора двоичная информационная последовательность поступает потребителю.

В предлагаемом устройстве криптостойкость повышается на Nn·GF(2q)n бит, где N - количество примитивных полиномов в кольце степени n, из которого осуществляется выборка сменного примитивного гаммообразующего полинома, а GF(2q)n - выбранное значение расширения поля Галуа, над которым рассматривается выбранный примитивный полином степени n. Так, например, если выбран сменный примитивный полином степени n=127, то при построении линейного рекуррентного регистра сдвига по полиному этой степени мощность ключевой системы такого устройства без учета нелинейных узлов усложнения будет равна количеству вариантов начального заполнения ЛРРС - 2127-1. В предлагаемом устройстве за счет выбора значения расширения поля Галуа, например, 24 количество вариантов начального заполнения ЛРРС возрастет до (24)127-1=2508-1, а с учетом осуществления выборки гаммообразующего примитивного полинома из кольца полиномов степени n=127 мощность ключевой системы возрастет на 1,3·1036≈2120. Криптостойкость в этом случае увеличится до 2628 бит. Выбор расширенного поля (24=16 вместо 2) также позволяет увеличить скорость шифрования в восемь раз при той же тактовой частоте [5], так как при этом за один такт работы шифратора шифруется не бит, а байт. При этом выбор конкретного значения расширения поля Галуа (24, 25, 26, 27 и т.д.), как правило, ориентирован на соответствующую архитектуру применяемого процессора (16-, 32-, 64-, 128-разрядного и т.д.). Следовательно, при быстро коммутируемых обратных связях ЛРРС путем перепрограммирования ПЛИС данную криптосхему можно существенно усилить (повысить криптостойкость) и сделать адаптивной к архитектуре процессора, объемам закрываемой информации, необходимости резкого увеличения (в разы) скорости шифрования информации (без увеличения тактовой частоты) за счет использования сменного значения расширения поля Галуа и, рассмотренного над ним, сменного примитивного полинома степени n в качестве дополнительных ключевых элементов.

Таким образом, благодаря введению дополнительных операций существенно расширяются возможности способа, поскольку существенно повышается криптостойкость и скорость шифрования, а также обеспечивается адаптивность к архитектуре используемого процессора и объемам закрываемой информации, что позволяет достигнуть требуемого технического результата.

Источники информации

1. Иванов М.А. Криптографические методы защиты информации в компьютерных системах и сетях. - М.: КУДИЦ-ОБРАЗ, 2001, с.34.

2. Копничев Л.Н. Принципы построения аппаратуры для передачи дискретной информации. - М.: Связь, 1972, с.52, 72.

3. Месси Дж. Л. Введение в современную криптологию. - ТИИЭР, т.76, N 5, май 1988, с.27, прототип.

4. Лидл Р., Нидеррайтер Г. Конечные поля. Т.2. - М.: Мир, 1988.

5. Бардаев Э.А., Ловцов Д.А. Ситуационное управление защищенностью ИПО АСУ СДО. НТИ РАН (Сер. 2. Информационные процессы и системы), 1999. №11. - С.10-21.

6. Иванов М.А., Чугунков И.В. Теория, применение и оценка качества генераторов псевдослучайных последовательностей. - М.: КУДИЦ-ОБРАЗ, 2003. - 240 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ АДАПТИВНОГО ПОТОЧНОГО ШИФРОВАНИЯ С УПРАВЛЯЕМОЙ КРИПТОСТОЙКОСТЬЮ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2574804C2 |

| УСТРОЙСТВО ШИФРОВАНИЯ ИНФОРМАЦИИ | 2008 |

|

RU2389141C2 |

| ШИФРУЮЩЕЕ-ДЕШИФРУЮЩЕЕ УСТРОЙСТВО | 1996 |

|

RU2108002C1 |

| СПОСОБ МУЛЬТИПОТОЧНОГО ШИФРОВАНИЯ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2016 |

|

RU2656689C2 |

| УСТРОЙСТВО АУТЕНТИФИКАЦИИ ПРОГРАММНЫХ МОДУЛЕЙ | 1998 |

|

RU2146834C1 |

| СПОСОБ ШИФРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК КАНАЛА СВЯЗИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2204886C2 |

| УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО ФОРМИРОВАНИЯ q-ЗНАЧНЫХ ПСЕВДОСЛУЧАЙНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ НА АРИФМЕТИЧЕСКИХ ПОЛИНОМАХ | 2021 |

|

RU2762209C1 |

| СПОСОБ ШИФРОВАНИЯ ДВОИЧНОЙ ИНФОРМАЦИИ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2091983C1 |

| СПОСОБ ТРАНСЛЯЦИОННОГО УСЛОЖНЕНИЯ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ В ВИДЕ КОДОВ КВАДРАТИЧНЫХ ВЫЧЕТОВ, СУЩЕСТВУЮЩИХ В ПРОСТЫХ ПОЛЯХ ГАЛУА GF(p), И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2669506C1 |

| Способ защиты информации в облачных вычислениях с использованием гомоморфного шифрования | 2017 |

|

RU2691874C2 |

Изобретение относится к шифрованию информации. Техническим результатом изобретения является увеличение скорости шифрования и повышение криптозащиты. На передающей и приемной сторонах соответственно вырабатывают и вводят в соответствии с ключом сменные примитивные полиномы степени n и сменное значение расширения поля Галуа GF(2q)n, в соответствии с которыми осуществляют перенастройку генератора ключа. Устройство содержит на передающей и приемной сторонах соответственно блок управления, вход которого соединен с выходом источника ключевой информации, блок выработки примитивных полиномов, осуществляющий выработку полиномов заданной степени и заданного количества, блок памяти, осуществляющий выборку конкретного полинома заданной степени, генератор ключа, осуществляющий синтез рекуррентных регистров сдвига, шифратор и дешифратор. 2 н.п. ф-лы, 1 ил.

| ИВАНОВ М.А | |||

| Криптографические методы защиты информации в компьютерных системах и сетях | |||

| - М.: КУДИЦ-ОБРАЗ, 2001, с.34 | |||

| МЕССИ ДЖ | |||

| Л | |||

| Введение в современную криптологию | |||

| - ТИИЭР, т.76, № 5, май 1988, с.27 | |||

| СПОСОБ ШИФРОВАНИЯ/ДЕШИФРОВАНИЯ СООБЩЕНИЙ ХЭШИРУЮЩЕЙ ФУНКЦИЕЙ И УСТРОЙСТВО, ЕГО РЕАЛИЗУЮЩЕЕ | 1998 |

|

RU2138126C1 |

| УСТРОЙСТВО И СПОСОБ ШИФРОВАНИЯ, УСТРОЙСТВО И СПОСОБ ДЕШИФРОВАНИЯ, УСТРОЙСТВО И СПОСОБ ОБРАБОТКИ ИНФОРМАЦИИ | 1998 |

|

RU2239954C2 |

| US 5483598 А, 09.01.1996. | |||

Авторы

Даты

2008-07-20—Публикация

2006-05-19—Подача