Изобретение относится к области контроля и защиты информационно-программного обеспечения автоматизированных систем от несанкционированной модификации и может быть использовано в автоматизированных системах обработки данных.

Известно устройство, содержащее источник информации, блок хранения информации, блок формирования эталона, приемник информации, блок обработки контролируемых значений, блок хранения эталонов и блок сравнения, причем источник информации соединен с блоком хранения информации и блоком формирования эталона, блок хранения информации соединен с приемником информации и блоком выработки контролируемых значений, а блок формирования эталона соединен через блок хранения эталонов с блоком сравнения (1).

Недостатком устройства является относительно низкая способность к обнаружению преднамеренных (злоумышленных) модификаций кода программных модулей.

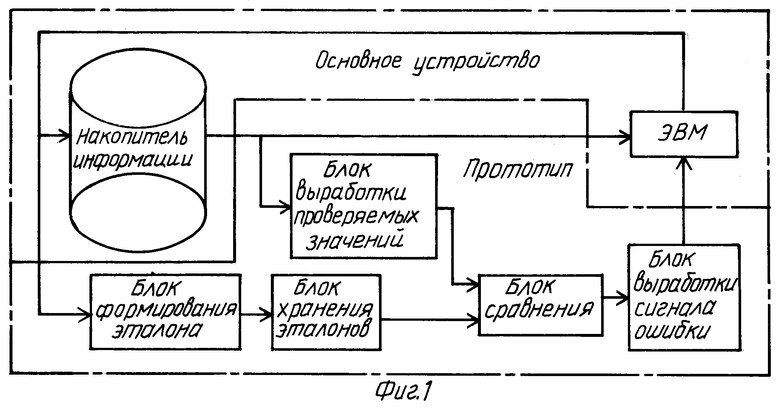

Наиболее близким по технической сущности к данному изобретению является устройство (фиг.1), содержащее последовательно соединенные источник информации, накопитель информации, блок выработки проверяемых значений, блок сравнения и блок выработки сигнала ошибки, выход которого соединен со входом приемника информации, выход которого соединен через последовательно соединенные блок формирования эталона и блок хранения эталона с другим входом блока сравнения, причем выход накопителя информации соединен с другим входом приемника информации, который совместно с источником информации выполнен в виде ЭВМ (2).

Недостатком устройства является его относительно низкая способность к обнаружению ошибок преднамеренной (злоумышленной) модификации кода программных модулей.

Устранение этого недостатка является актуальным для автоматизированных систем критического применения, в которых несанкционированная модификация кода программных модулей может привести не только к срыву решаемой задачи, но и к трагическим последствиям.

В автоматизированных системах обработки данных (фиг.2) такая угроза особенно опасна для программных модулей, реализующих алгоритмы шифрования-дешифрования обрабатываемой информации. Известно (3), что для обеспечения заданной стойкости шифрования обрабатываемой информации необходимо сохранять в тайне от злоумышленника только ключ шифрования, а сам алгоритм шифрования предполагается ему известным. При этом для программно-загруженных криптоалгоритмов появляется новая угроза, заключающаяся в том, что с учетом знания алгоритма потенциальными злоумышленником у него появляется возможность без знания ключа, только лишь посредством незначительной модификации кода программного модуля снизить стойкость шифрования и, тем самым, получить доступ к защищаемой информации. Этого можно добиться, например, с помощью специальной программы-закладки (4).

Технический результат, достигаемый при осуществлении данного изобретения, заключается в выделении контролируемого программного модуля из общего потока информационных массивов, обнаружении любых несанкционированных модификаций кода контролируемого программного модуля и блокировании при этом его запуска.

Для достижения указанного технического результата в устройство аутентификации программных модулей, содержащее формирователь эталона, оперативный запоминающий узел (ОЗУ) хранения эталонов, блок сравнения, накопитель информации и контроллер, введены блок блокирования, преобразователь кода, буфер записи эталона, дешифратор адреса, дешифратор команд и блок начальной установки.

Сущность изобретения поясняется фиг. 3, на которой представлена структурная схема устройства аутентификации.

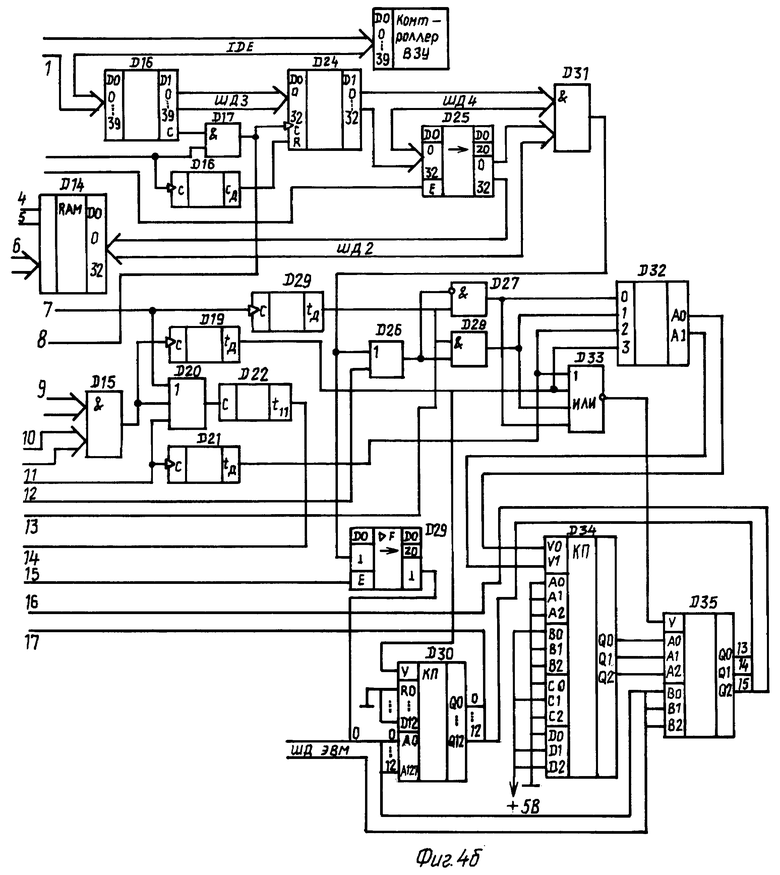

Устройство аутентификации содержит дешифратор адреса 1, на входы которого подключены шина адреса ЭВМ и шина управления ЭВМ, а на выходах дешифратора адреса 1 формируются сигнал чтения и сигнал записи, которые поступают на шину управления, регистр команд 2, на вход которого поступает код команд по шине данных, на вход управления - стробирующий сигнал записи кодов команд с шины управления, на выходах регистра команд 2 старшие три разряда кодов команд поступают на шину команд, а младшие разряды кодов команд поступают на шину адреса, блок начальной установки 3 соединен с шиной данных ЭВМ, с шиной управления и с шиной данных, а на вход управления поступает сигнал управления с шины управления ЭВМ, дешифратор команд 4, вход которого соединен с выходом кода команд регистра команд, а выход соединен с шиной управления, блок блокировки 5, включенный между накопителем информации 6 на жестких магнитных дисках и контроллером 7, вход сигнала разрешения коммутации блока блокировки 5 соединен с шиной управления, энергозависимый ОЗУ 8 хранения эталонов, выход которого соединен с соответствующим входом блока сравнения 12, вход данных ОЗУ 8 хранения эталонов соединен с выходом формирователя эталона 10 через буфер записи эталона 11, вход адреса ОЗУ 8 хранения эталонов соединен с выходом адреса регистра команд 2 и с соответствующим входом блока начальной установки 3, а вход управления и выход запись/чтение ОЗУ 8 хранения эталонов соединены с шиной управления, преобразователь кода 9, вход которого соединен с блоком блокировки 5, выход данных - со входом данных формирователя эталона 10, а выход сигнала стробирования данных - с шиной управления, с которой соединены вход сигнала истинности данных и вход сигнала начальной установки формирователя эталона 10, выход которого соединен со входом данных буфера записи эталона 11, вход сигнала разрешения выдачи данных которого соединен с шиной управления, выход данных буфера записи эталона 11 соединен со входом данных ОЗУ 8 и с одним из входов блока сравнения, другой вход которого соединен с выходом формирователя эталона 10, вход управления блока сравнения соединен с шиной управления, а выход блока сравнения 12 соединен с первым разрядом шины данных ЭВМ, модуль питания 13, на вход которого подано напряжение питания с ЭВМ, а с его выходов постоянно подается напряжение питания в блок начальной установки 3 и в ОЗУ 8 хранения эталонов.

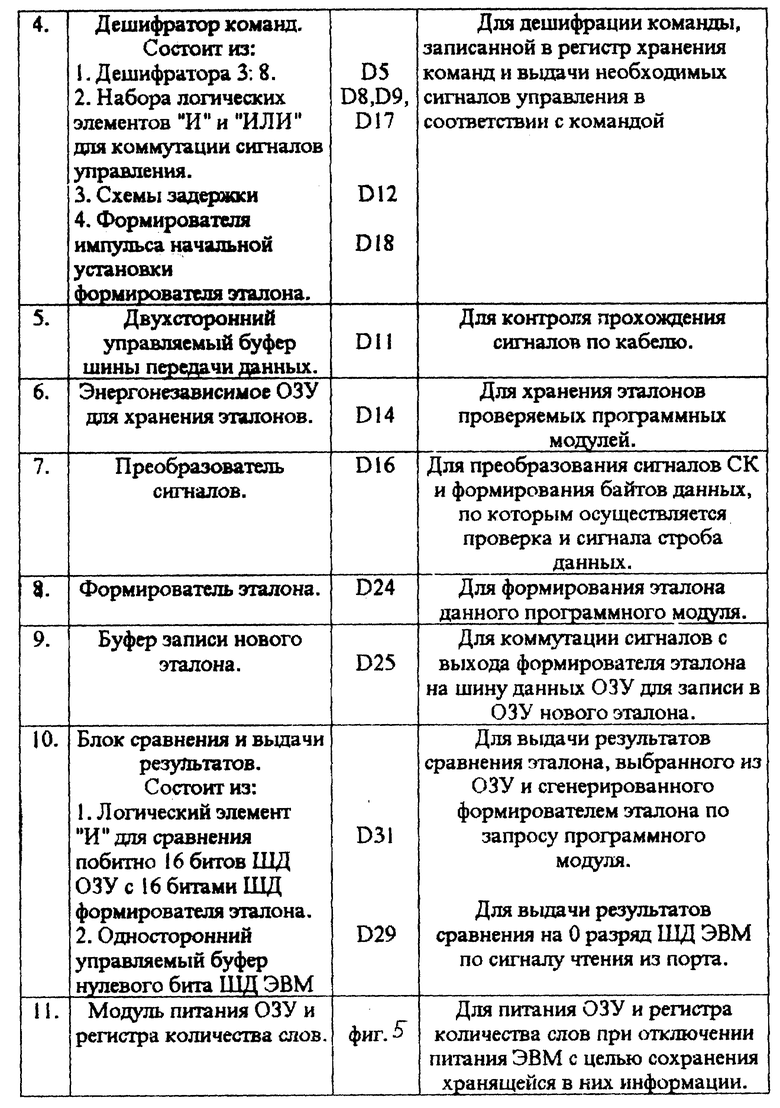

Возможная реализация перечисленных функциональных блоков приведена в табл. 1.

Устройство аутентификации работает следующим образом.

Начальная установка устройства производится следующим образом. При загрузке ядра операционной системы с управляющей программой выполняется команда формирования эталона по определенному количеству слов ядра операционной системы и управляющей программы. Затем выполняется команда записи нового эталона по адресу нулевого эталона и команда записи количества контролируемых слов операционной системы и управляющей программы с указанием количества слов, по которым формировался эталон операционной системы и управляющая программа. Полное описание команд приведено в табл. 3.

Устройство работает в следующих режимах: управление доступом к накопителю информации, при котором выполняется команда разрешения работы с накопителем информации 6 или команда запрещения работы с накопителем информации 6, и формирование и запись эталона программного модуля, причем возможны два варианта ввода эталона в ОЗУ 8. Первый вариант состоит в автономной выработке эталонов из поставляемого сертифицированного программного обеспечения, осуществляемая в следующей последовательности: при загрузке программного модуля выполняется команда формирования эталона, а затем после окончания загрузки программного модуля выполняется команда записи нового эталона с указанием номера эталона, по адресу которого будет храниться записываемый эталон.

Второй вариант ввода эталона заключается в том, что эталоны к сертифицированному программному обеспечению критического применения формируются на отдельном устройстве типа Touch-memory или флеш-карты и записываются в ОЗУ непосредственно через соответствующее устройство считывания, которое может входить в состав ОЗУ.

Третий режим работы устройства - аутентификация программного модуля, при котором при вызове программного модуля управляющая программа выдает команду выработки контролируемого значения, а после окончания загрузки программного модуля управляющая программа выдает команду проверки контролируемого значения и на основании результата проверки разрешает или запрещает дальнейшую работу с накопителем информации 6 и передачу управления на проверенный программный модуль.

При первом запуске или перегрузке ЭВМ блок начальной проверки при помощи сигналов управления устанавливает устройство в режим разработки контролируемых значений загружаемых программ ядра операционной системы, в том числе и управляющей программы устройства аутентификации. Для этого блок блокировки 6 коммутирует свой информационный вход с выходом, разрешая передачу данных по соединительному кабелю между накопителем информации 6 и ЭВМ, а формирователь эталона 10 вырабатывает проверяемое значение загружаемых программных модулей операционной системы и управляющей программы. После считывания количества слов, определяемого в блоке начальной установки 3, на блоке сравнения производится сравнение контролируемого значения с нулевым эталоном из ОЗУ 8. В случае несовпадения контролируемого значения с нулевым эталоном блок блокировки 6 блокирует дальнейшую загрузку операционной системы и управляющей программы. Если контролируемое значение и нулевой эталон совпали /операционная система и управляющая программа не модифицированы/, то дальнейшая загрузка операционной системы происходит под контролем управляющей программы, которой передается управлением устройством аутентификации.

Достижение требуемого технического результата осуществляется посредством блокировки передачи управления модифицированному модулю, а также обращенной со стороны ЭВМ к накопителю информации 6 в следующих случаях: при обнаружении модификации ядра загружаемой операционной системы /в том числе и управляющей программы/ блокировка осуществляется автономно аппаратной частью устройства; после загрузки и проверки ядра операционной системы и управляющей программы управление передается на эту программу, которая начинает отслеживать момент вызова очередного программного модуля и при наступлении такого события дает команду аппаратной части на проведение его аутентификации, в случае обнаружения модификации проверяемого программного модуля аппаратная часть осуществляет блокировку доступа к накопителю информации 6 и выдает сигнал для управляющей программы, которая блокирует передачу управления модифицированной программе; при попытке обращения к накопителю информации в обход управляющей программы устройства.

Возможный вариант технической реализации данного устройства и подробное описание алгоритма его работы, алгоритма управляющей программы и ее команд приведены в табл. 1 - 3.

Указанный технический результат достигается за счет всей совокупности признаков, которая в таком сочетании не обнаружена при анализе известного уровня техники, а поэтому данное предложение отвечает условию изобретательского уровня. При этом конструкция всех функциональных блоков раскрыта до уровня стандартного инженерного решения, а поэтому данное предложение отвечает условию промышленной применимости.

Устройство аутентификации исполняемых программных модулей

Состав и назначение компонентов устройства аутентификации представлены в табл. 1.

Позиционные обозначения функциональных элементов, представленные в табл. 1, соответствуют обозначениям функциональной схемы, изображенным на фиг. 4а, 4б.

1. Дешифратор адреса

Анализирует шину управления и шину адреса ЭВМ и в случае чтения из порта или записи в порт, по которому находится данное устройство, выдает в шину управления сигнал чтения из устройства или записи в него.

В целях гибкости использования желательно реализовывать таким образом, чтобы возможно было изменение адреса порта, по которому будет работать данное устройство.

Реализуется на основе дешифратора и логических элементов И, ИЛИ.

2. Регистр команд

Хранит код команды до записи новой команды.

Младшие 13 бит кода команды являются номером эталона в командах "проверка эталона" и "запись нового эталона" и являются количеством проверяемых слов ОС и УП УА в команде "запись количества проверяемых слов ОС и УП УА", в остальных командах эти биты значения не имеют.

Старшие 3 бита являются непосредственно кодом команды, по которому формируются сигналы управления.

В качестве регистра команд можно использовать любой регистр, в котором имеется тактовый управляющий вход, по фронту сигнала на котором будет производиться запись данных, находящихся на входе, и который будет обеспечивать хранение 16 разрядных слов.

3. Блок начальных установок

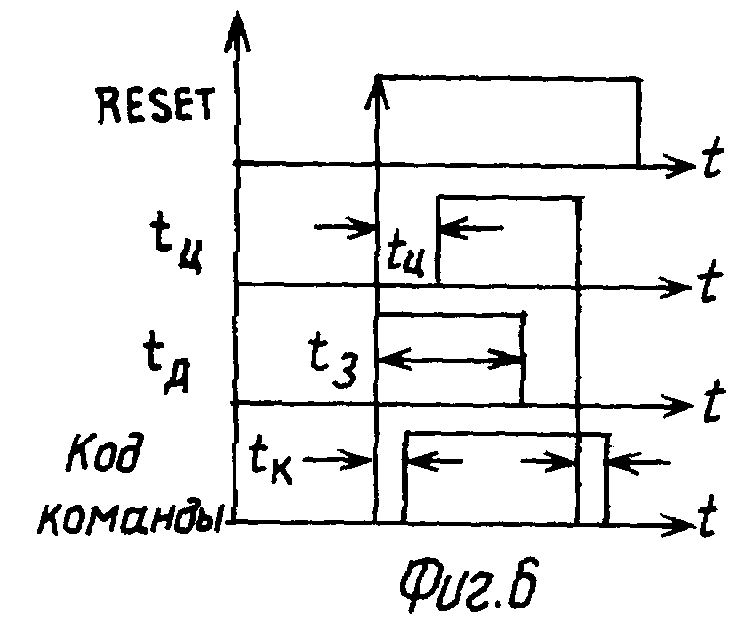

При первом запуске ЭВМ или при перезапуске по сигналу RESET с шины управления ЭВМ устанавливаются в нулевое состояние счетчик считанных слов (вход RD13), в единичное состояние триггер проверки ОС и УП слов (вход SD6), также данный сигнал попадает на схему задержки (вх. CD22) через лог. элемент ИЛИ (D2) и задерживается на время tц (график фиг. 6), затем попадает через логический элемент ИЛИ (D2) на вход строба записи регистра команд (вход CD3) и по фронту этого импульса производится запись кода команды с ШД1, одновременно с приходом сигнала на схему задержки этот сигнал приходит на формирователь импульса (вх. CD21), который по фронту сигнала RESET выдает импульс длительностью tд (график фиг. 6), этот импульс поступает на шифратор (вх. 3 D32), который преобразует пришедший сигнал в логические единицы на выходах A0 и A1, эти единицы попадают на управляющие входы V0, V1 коммутатора команд (D34). Коммутатор команд устанавливает на выходе сигналы в соответствии со входом D (D0-0, D1-1, D2-1), одновременно с приходом импульса на вход 4 шифратора (D32) с формирователя импульса (D21) этот импульс попадает на вход логического элемента ИЛИ (D33), сбрасывая его выход в нулевое состояние, этот логический 0 поступает на выход V коммутатора старших 3 разрядов ШД2 (D35), устанавливая коммутацию сигналов с выхода коммутатора команд, таким образом на 13, 14, 15 битах ШД1 установлен код команды формирования эталона, который записывается в регистр команд (D2) по фронту сигнала со схемы задержки (D22). После записи команды в регистр команд (D2) выполняется команда формирования эталона. Сигнал строба данных, приходящий на вход C формирователя эталона (D24), поступает на 1 вход логического элемента И (D10) и если триггер проверки ОС и УП (D6) установлен в единичное состояние, то сигнал строба данных поступает на вход C счетчика считанных слов (D13), таким образом производится подсчет количества слов, по которым производится формирование эталона. Счетчик считанных слов выдает количество считанных слов на элемент И (D15) для поразрядного сравнения 13 разрядов, пришедших со счетчика и с регистра количества слов (D4). В случае совпадения сигналов, приходящих с регистра количества слов и со счетчика считанных слов, на выходе данного элемента выдается логическая единица, которая поступает на формирователь импульса (D19) и через логический элемент ИЛИ (D20) на схему задержки импульса. По фронту данного импульса формирователь импульса (D19) формирует импульс длительностью tд (график фиг. 6), который приходит на вход 3 шифратора (D32), на вход элемента ИЛИ-НЕ (D33) и на вход V коммутатора 2:1 (D30). Коммутатор 2:1 устанавливает на 0 - 12 разряды ШД1 (N эталона в команде сравнения эталона) логические нули, поступающие на вход B. Шифратор устанавливает свои выходы A0, A1 в единичное состояние, которое поступает на управляющие входы V0, V1 коммутатора 4:1 (D34). Коммутатор при установке в единичное состояние управляющих входов V0, V1 коммутирует код команды сравнения эталона со входа D на вход A коммутатора 2:1 (D35). С выхода D34 поступает логический 0 на управляющий вход V коммутатора 2:1 (D35). Коммутатор выдает на 13, 14, 15 разряды ШД1 код команды сравнения эталонов, поступающий с выхода коммутатора 4: 1 (D34). Таким образом на ШД1 установлен код команды проверки нулевого эталона. Одновременно с этим логическая единица, поступающая на вход D22, задерживается на время tц (график фиг. 6), большее времени установки кода команды проверки нулевого эталона, и поступает через логический элемент ИЛИ (D2) на вход C регистра команд (D3). По фронту этого сигнала код команды проверки нулевого эталона записывается в регистр команд. В результате после формирования эталона по количеству слов, записанному в регистр количества проверяемых слов, производится проверка сформированного эталона с нулевым. После дешифрации данного кода команды логическая единица поступает на вход формирователя импульса (D23). С выхода формирователя импульса (D23) импульс длительностью tд (фиг. 6) поступает на логические элементы И (D27, D28) и на вход R триггера начальной проверки (для отключения БНУ при дальнейшей работе). Одновременно с этим после поразрядного сравнения в случае полного совпадения логическая единица поступает через логический элемент ИЛИ (D26) на 2 вход логического элемента И (D28) и на выходе логического элемента появляется логическая единица. Так же в случае, если количество проверяемых слов равно 0 (первая установка устройства), на выходе D7 формируется логическая 1, поступающая через элемент ИЛИ (D27) на второй вход D29. В случае несовпадения и количества проверяемых слов больше 0, логический ноль поступает с элемента ИЛИ (D26), инвертируется в логическую единицу на втором входе логического элемента И, и на выходе этого элемента появляется логическая 1. Далее логическая 1 поступает на 0 или 1 входы шифратора (D32), который устанавливает на выходе код 00 или 01. Этот код поступает на управляющие входы V0, V1 коммутатора 4:1 (D34), который устанавливает на выходе Q код команды запрещения работы с НЖМД (вход A) или код команды разрешения работы с НЖМД (вход B). Логический 0 с выхода D34 поступает на управляющий вход V коммутатора 2:1 (D36), который устанавливает на 13, 14, 15 разрядах ШД1 код команды запрещения работы с НЖМД или разрешения работы с НЖМД, поступивший с выхода Q коммутатора 4:1 (D34). Одновременно с этим логическая 1, поступившая на вход D22, задерживается на время tд (фиг. 6), большее времени сравнения эталонов и времени установки кода команды, и поступает через логический элемент ИЛИ (D2) на вход с регистра команд (D3). По фронту этого сигнала код команды разрешения или запрещения работы с НЖМД записывается в регистр команд.

В результате произведена проверка загружаемой ОС и по результату проверки разрешается или запрещается дальнейшая работа с НЖМД.

4. Дешифратор команд

В зависимости от кода команды коммутирует сигналы в соответствии с табл. 3.

Реализуется на дешифраторе 3:8 и логических элементах И и ИЛИ.

5. Двухсторонний управляемый буфер соединительного кабеля

Должен отвечать требованиям:

Количество коммутируемых разрядов должно быть не меньше разрядности СК (в данном примере 40 разрядов - разрядность СК типа IDE).

Время коммутации - меньше длительности сигнала истинности данных (сигнал стробирования данных), передаваемых по СК.

Коммутация сигналов должна осуществляться в две стороны и по управляющему сигналу (E).

6. ОЗУ для хранения эталонов

Должно удовлетворять требованиям:

Для хранения эталонов при отключении питания ЭВМ питание ОЗУ осуществляется по схеме фиг. 5, как видно из схемы при отключении питания ОЗУ автоматически напитывается от встроенного аккумулятора (потребление ОЗУ в режиме хранения должно быть минимальным).

Разрядность ШД ОЗУ должна быть равна размеру эталонов, формируемых формирователем эталона (в данном примере 32 разрядная ШД).

Разрядность ША ОЗУ равна 13 разрядам, что позволяет хранить до 213 эталонов ПМ (может быть увеличена увеличением разрядности регистра команд путем деления команд по 16 разрядов и записи частей команд по разным портам).

7. Преобразователь сигналов

Из 40 разрядов СК формирует 16 бит данных, считываемых с диска, и сигнал строба этих данных для выдачи этих данных в формирователь эталона и формирования эталона по ним.

Для каждого стандарта интерфейса должен быть свой преобразователь сигналов.

Сигнал строба формируется в соответствии с графиком фиг. 7, где:

tк - время коммутации сигналов данных с СК на ШД3,

tф - время гарантированной установки истинных данных на ШД3.

8. Формирователь эталона

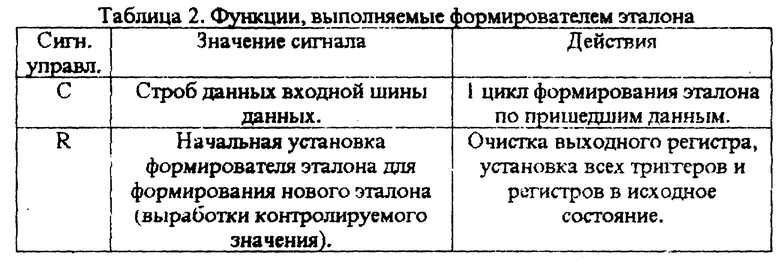

Осуществляет действия по сигналам управления в соответствии с табл. 2.

Вывод сформированного (формируемого) эталона (содержимое выходного регистра) на выходную ШД производится постоянно.

Особенности формирователя эталона.

1. Позволяет осуществлять достаточную криптостойкость с целью не допустить возможности подбора такой модификации ПМ, при которой эталон модифицированного ПМ будет соответствовать эталону не модифицированного ПМ.

2. Так как необходимо производить формирование эталона ПМ, можно значительно упростить его, использовав особенности ПМ, реализующие алгоритмы шифрования, такие как (эти задачи можно возложить на преобразователь сигналов):

а) т. к. программы, использующие 32 разрядные команды процессора имеют длину от 2 до 10 байт, то при использовании для формирования эталона с ПМ каждого второго байта ПМ каждая команда становится связанной с эталоном, это позволяет уменьшить количество обрабатываемой информации до 50% от длины ПМ;

б) т. к. многие программы-вирусы при заражении программ изменяют адреса переходов, то для контроля на модификацию будет достаточно производить формирование эталона по командам передачи управления (их порядковый номер во всей последовательности или адрес, по которому осуществляется переход). Для их поиска достаточно проверять определенные биты т.к. они предельно формализованы.

Работа устройства аутентификации программных модулей

Включает выполнение команд, представленных в табл. 3.

При записи в регистр команд данного кода команды дешифратор команд дешифруют данный код команды и на его 0 выходе появляется логическая единица, попадает на вход E буфера соединительного кабеля, который, в свою очередь, производит коммутацию сигналов СК и до записи в регистр команд нового кода команды состояние системы не изменяется.

При записи в регистр команд какого-либо другого кода команды новый код команды попадает на вход дешифратора команд. Дешифратор команд переводит в единичное состояние соответствующий номер команды свой выход, а все остальные и в том числе 1-ый выход переводит в нулевое состояние.

2. Запрещение работы с НЖМД

При записи в регистр команд данного кода команды дешифратор команд переводит в единичное состояние свой 1 выход, который не связан ни с какой частью УA, на всех выходах, в том числе 0, 2, 3, 4, ДК лог. 0, который приходит на все управляющие входы частей УA, в том числе на вход E буфера СК, который переводит свои выводы в L состояние (отключено) и сигналы, подаваемые на СК через буфер не проходят.

3. Формирование эталона

При записи в регистр команд данного кода команды дешифратор команд переводит в единичное состояние свой 2 выход, с которого лог. 1 попадает на вход E буфера СК (разрешая коммутацию сигналов СК), на логический элемент И, на второй вход которого поданы сигналы стробирования данных, выдаваемых на его выходе (разрешая прохождение этого сигнала на вход C формирователя эталона), на формирователь импульса сброса формирователя эталона, формирователь эталона в момент записи команды формирования эталона по сигналу R производит начальные установки для формирования нового эталона. По каждому фронту сигнала C (строб данных) производит 1 цикл формирования эталона по 16 битам, пришедшим с преобразователя.

4. Проверка эталона

При записи в регистр команд данного кода команды дешифратор команд переводит в единичное состояние свой 3 выход, с которого лог. 1 попадает на вход E буфера СК (разрешая коммутацию сигналов СК), на вход CS через схему задержки и RD/WR ОЗУ, так же на шину адреса ОЗУ поступают младшие 13 бит с регистра команд (номер эталона), таким образом на шине данных ОЗУ выдан эталон ПМ, номер которого установлен в младших 13 битах команды формирования эталона, на выходной ШД формирователя эталона установлен сформированный эталон, эти два эталона сравниваются на логическом элементе И и если они совпадают, на выходе элемента И формируется лог. 1. При чтении программной части из порта с адресом, по которому осуществляется запись команд управления устройства аутентификации, на буфер нулевого бита ШД приходит сигнал разрешения коммутации выхода лог. элемента И на нулевой разряд ШД ЭВМ.

5. Запись нового эталона

При записи в регистр команд данного кода команды дешифратор команд переводит в единичное состояние свой 4 выход, с которого лог. 1 попадает на вход E буфера СК (разрешая коммутацию сигналов СК), на вход E буфера записи нового эталона (разрешая коммутацию выходной ШД формирователя эталона на ШД ОЗУ), на CS ОЗУ через схему задержки (на входе RD/WR - лог. 0 - запись), так же на шину адреса ОЗУ поступают младшие 13 бит с регистра команд (номер нового эталона). Таким образом, на шину данных ОЗУ поступает новый эталон ПМ, сформированный формирователем эталона, на ША - адрес нового эталона, номер которого установлен в младших 13 битах команды формирования эталона, и по фронту сигнала CS производится запись нового эталона в ОЗУ.

6. Запись количества проверяемых слов ОС и УП УА

При записи в регистр команд данного кода команды дешифратор команд переводит в единичное состояние свой 5 выход, с которого лог. 1 попадает на вход C регистра количества проверяемых слов ОС и УП УА, в младших 13 разрядах ШД установлено количество проверяемых слов ОС и УП УА. Таким образом по фронту сигнала C количество проверяемых слов записывается в регистр.

Управляющая программа

Требования:

1. Для избежания чтения лишних байтов данных во время формирования эталона во время чтения проверяемого программного модуля (ПМ) должны быть выполнены действия:

1) Отключено программное кэширование НЖМД

2) Отмено обращение других программ к НЖМД.

2. Для определения необходимости включения разрешения обращения к диску программная часть должна контролировать прерывание работы с ПЖМД (для MS DOS-13h).

3. Для определения необходимости контроля загрузки и выполнения программного модуля программная часть должна контролировать прерывание работы с файлами (для MS DOS-21h).

4. Для защиты файла с именами ПМ и номерами их эталонов:

1). Зарезервировать любой номер эталона под файл с таблицей имен ПМ.

2). При загрузке файла с таблицей имен ПМ он проверяется на модификацию при помощи блока проверки ПМ на модификацию.

3) При каждом изменении файла с таблицей имен ПМ по нему создается новый эталон, который записывается под номером, который был зарезервирован.

7. При чтении с НЖМД информации по СК передается различная служебная информация, которая не меняется при одинаковом месте хранения ПМ на НЖМД, но в случае изменения места хранения (при дефрагментации диска) эта информация может меняться, в таких случаях необходимо создать новые эталоны по ПМ и перезаписать их в ОЗУ устройства.

Алгоритм работы управляющей программы:

1. При инициализации - в устройство аутентификации записывается код команды запрещения работы с НЖМД.

2. При обращении к прерыванию работы с файлами проверяется производится ли загрузка и выполнение ПМ, загрузку и выполнение которого необходимо контролировать (имя ПМ берется из таблицы контролируемых ПМ, в которой содержатся номера эталонов ПМ).

Если ДА - проверка ПМ на модификацию:

а). В начале загрузки ПМ - в порт записывается код команды формирования эталона.

б). По окончании загрузки ПМ - в порт записывается код команды проверки сгенерированного эталона с образцовым.

в). Из порта читается результат проверки.

г). В порт записывается код команды запрещения работы с НЖМД.

д). По результатам проверки передается управление ПМ или выдается сообщение о модификации ПМ.

Если НЕТ - простое обращение к НЖМД:

а). В начале обращения к НЖМД - в порт записывается код команды разрешения работы с НЖМД.

б). В конце обращения к НЖМД - в порт записывается код команды запрещения работы с НЖМД.

Защита управляющей программы от разрушающих воздействий

1. Так как блокировка СК производится аппаратно, то в случае уничтожения программной части доступ к диску будет невозможен.

2. Так как проверка на модификацию ПМ производится аппаратно, то программным методом невозможно будет вмешаться в процесс проверки с целью выдать модифицированный ПМ за немодифицированный.

3. Так как при первой загрузке ОС и УП УА проверяется сама загружаемая ОС и УП УА, то становится невозможной начальная загрузка другой ОС и УП УА или загрузка перед ОС других программ (защита от BOOT вирусов).

Источники информации

1. Иыуду К.А. Надежность, контроль и диагностика вычислительных машин и систем. - М.: Высшая школа, 1989, с. 66.

2. Ловцов Д.А. Контроль и защита информации в АСУ. - М.: МО СССР, 1991, с. 40 - прототип.

3. Конхейм А.Г. Основы криптографии. - М.: Радио и связь, 1987, 412 с.

4. Щербаков А.Ю. Разрушающие программные воздействия. - М.: Эдель, 1993. 64 с.

5. ГОСТ P 34.11-94 Информационная технология. Криптографическая защита информации. Функция хэширования.

6. Расторгуев С.П. Программные методы защиты информации в компьютерах и сетях. М.: Яхстмен, 1993, с. 188.

7. Чернега В.С., Василенко В.А., Бондарев В.Н. Расчет и проектирование технических средств обмена и передачи информации. - М.: Высшая школа, 1990, 223 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для сопряжения ЭВМ с накопителем на магнитной ленте | 1988 |

|

SU1667085A1 |

| СПОСОБ АДАПТИВНОГО ПОТОЧНОГО ШИФРОВАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2006 |

|

RU2329544C2 |

| Устройство для имитации неисправностей | 1987 |

|

SU1444775A1 |

| Устройство для контроля данных электронной вычислительной машины при прерываниях питания | 1983 |

|

SU1129615A1 |

| Устройство для автоматизированного управления процессом налива емкостей | 1987 |

|

SU1588710A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

| УСТРОЙСТВО ОГРАНИЧЕНИЯ ДОСТУПА К СЕКТОРАМ ЖЕСТКОГО ДИСКА | 2007 |

|

RU2359317C2 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

| СПОСОБ И УСТРОЙСТВО ОГРАНИЧЕНИЯ ДОСТУПА К ЗАПИСАННЫМ НА НОСИТЕЛЕ ЦИФРОВЫМ ДАННЫМ | 2004 |

|

RU2277720C2 |

Изобретение относится к области контроля и защиты информационно-программного обеспечения автоматизированных систем от несанкционированного доступа. Техническим результатом является выделение контролируемого программного модуля из общего потока информационных массивов, обнаружение любых несанкционированных модификаций кода контролируемого программного модуля и блокирование при этом его запуска. Устройство содержит накопитель информации, формирователь эталона, оперативный запоминающий узел хранения эталонов, блок блокировки, преобразователь кода, дешифратор команд, блок начальной установки, дешифратор адреса, регистр команд, буфер записи эталона. 7 ил., 3 табл.

Устройство аутентификации программных модулей, содержащее формирователь эталона и оперативный запоминающий узел (ОЗУ) хранения эталонов, выходы которых соединены с соответствующими входами блока сравнения, а также накопитель информации, отличающееся тем, что в него введены последовательно соединенные блок блокировки и преобразователь кода, дешифратор команд, выход которого соединен с блоком начальной установки через шину управления, а также дешифратор адреса, регистр команд и буфер записи эталона, при этом накопитель информации соединен с блоком блокировки, выход преобразователя кода соединен со входом данных формирователя эталона, выход которого через буфер записи эталона соединен со входом данных ОЗУ хранения эталонов, блок начальной установки соединен через шину данных с регистром команд, выход кода команды которого соединен со входом дешифратора команд, а выход адреса - с соответствующими входами ОЗУ хранения эталонов и блока начальной установки, входом данных которого является шина данных ЭВМ, к которой подключен выход блока сравнения, входами дешифратора адреса являются соответственно шина адреса ЭВМ и шина управления ЭВМ, с которой соединен вход управления блока начальной установки, а выходы сигналов чтения и записи дешифратора адреса соединены с шиной управления, с которой соединен вход управления регистра команд, вход сигнала разрешения коммутации блока блокировки, вход сигнала истинности данных и вход сигнала начальной установки формирователя эталона, вход сигнала разрешения выдачи данных буфера записи эталона, вход управления блока сравнения, вход управления и вход запись/чтение ОЗУ хранения эталонов и выход сигнала стробирования данных преобразователя кода.

| Ловцов Д.А | |||

| Контроль и защита информации в АСУ | |||

| - М.: МО СССР, 1991, с.38 - 40, рис.1.12 | |||

| Иыуду К.А | |||

| Надежность, контроль и диагностика вычислительных машин и систем | |||

| - М.: Высшая школа, 1989, с.66 | |||

| Щербаков А.Ю | |||

| Разрушающие программные воздействия, - Эдель, 1993, с.51 - 64 | |||

| Расторгуев С.П | |||

| Программное методы защиты информации в компьютерах и сетях | |||

| - М.: Яхтсмен, 1993, с.23 - 188 | |||

| Конхейм А.Г | |||

| Основы криптографии | |||

| - М.: Радио и связь, 1987, с.408 - 412 | |||

| УСТРОЙСТВО ДЛЯ ЛАЗЕРНОЙ ТЕРАПИИ В ОФТАЛЬМОЛОГИИ (ВАРИАНТЫ) | 1998 |

|

RU2204971C2 |

| US 5579479 A, 26.11.96 | |||

| Способ управления системой двухдвигательного привода передвижения механизма подвижной коксовой машины | 1973 |

|

SU667577A1 |

Авторы

Даты

2000-03-20—Публикация

1998-06-15—Подача