Изобретение относится к электросвязи и может быть использовано для передачи информации.

Известна многоканальная цифровая система передачи и приема информации, содержащая генераторы тактовых импульсов, блок цикловой синхронизации, передающие и приемные блоки, распределитель импульсов, блок слежения за задержкой, блоки переключения, распределитель группового сигнала, блок управления и усилитель мощности (см. патент РФ №2013012, кл. Н04J 3/24, 1994 г.).

Недостатком данной системы является низкая помехозащищенность из-за отсутствия возможности перераспределения скорости передачи информации в отдельных каналах при неизменной скорости группового сигнала.

Наиболее близким по технической сущности к заявляемому изобретению относится система передачи многоканальных цифровых сигналов с преобразованием скоростей, содержащая на передающей стороне выделитель тактовой частоты, регенератор, преобразователь последовательного кода в параллельный и блок цикловой синхронизации, а на приемной стороне - преобразователь параллельного кода в последовательный, каналы обработки сигналов и блок синхронизации (см. авторское свидетельство СССР №1706048, кл. Н04J 3/18, опубл. 15.01.1992 в бюл. №2). Данная система взята в качестве прототипа.

Недостатком указанной системы является низкая защищенность уплотняемых каналов по отношению к преднамеренным помехам со стороны системы подавления с ограниченным энергетическим ресурсом. Это обусловлено тем, что на каждый канал при его временном уплотнении выделяется временной интервал, обеспечивающий скорость передачи информации в групповом канале, без учета степени его поражения прицельной помехой.

Основной задачей, на решение которой направлено заявляемое изобретение, является повышение помехозащищенности многоканальной передачи информации в условиях ограниченных энергетических ресурсов постановщика помех.

Технический результат изобретения - повышение помехозащищенности многоканальной передачи информации.

Указанный технический результат достигается тем, что в известное устройство, содержащее выделитель тактовой частоты, регенератор, блок цикловой синхронизации, умножитель импульсов, блок задержки, блок ячеек памяти и блок ключей, дополнительно введены: первый измеритель мощности и блок оперативной памяти - для измерения и запоминания мощности процесса сигнал + помеха на длительности цикла группового сигнала; второй измеритель мощности - для измерения мощности процесса сигнал + помеха на длительности элемента сигнала уплотняемого канала; блок мультиплексоров - для управления канальной скоростью передачи информации в зависимости от относительного уровня помехи в канале (чем выше уровень помехи, тем меньше скорость передачи информации - этим достигается требуемый уровень помехозащиты, а следовательно, достоверности поэлементного приема информации).

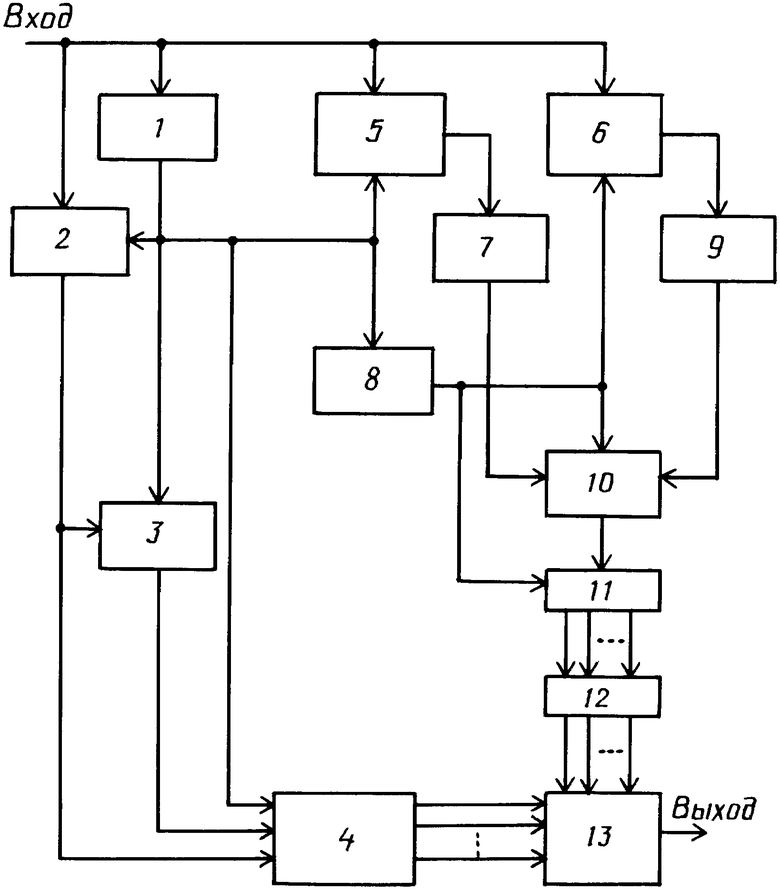

На чертеже изображена структурная электрическая схема предложенного устройства.

Устройство передачи многоканальных цифровых сигналов с преобразованием скоростей содержит выделитель 1 тактовой частоты, регенератор 2, блок 3 цикловой синхронизации, преобразователь 4 последовательного кода в параллельный, первый и второй измерители 5 и 6 мощности, блок 7 оперативной памяти, умножитель 8 импульсов, блок 9 задержки, делитель 10, блок 11 ячеек памяти, блок 12 ключей и блок 13 мультиплексоров.

Устройство работает следующим образом.

Многоканальный (групповой) сигнал, включающий и цикловой синхронизирующий сигнал, поступает на входы выделителя 1 тактовой частоты и регенератора 2, образующие в совокупности обычное стыковое оборудование. Выделитель 1 тактовой частоты на своем выходе вырабатывает синхронно-синфазную тактовую последовательность из многоканального сигнала, а в регенераторе 2 производится восстановление формы многоканального цифрового сигнала.

Регенерированный многоканальный цифровой сигнал и тактовая последовательность параллельно поступают на соответствующие входы блока 3 цикловой синхронизации и преобразователя 4 последовательного кода в параллельный. Блок 3 цикловой синхронизации фиксирует регулярно следующий цикловой синхронизирующий сигнал, имеющийся в составе многоканального цифрового сигнала, и вырабатывает на своем выходе сигнал, поступающий на управляющий вход преобразователя 4, в котором исходный многоканальный цифровой сигнал преобразуется в М компонентных последовательностей со скоростью в М раз ниже, чем в исходном сигнале.

Многоканальный сигнал поступает также на входы первого и второго измерителей 5 и 6 мощности. Первый измеритель 5 предназначен для измерения мощности входного процесса сигнал + помеха на длительности цикла группового сигнала Тц, по окончании которого при поступлении с выделителя 1 тактовой частоты импульса на тактовый вход измерителя 5 мощности результат измерения Рц поступает в блок 7 оперативной памяти.

Второй измеритель 6 предназначен для измерения мощности входного процесса сигнал + помеха на длительности элемента сигнала tэ, т.е. сигнала одного из уплотняемых каналов. С этой целью импульсы с выделителя 1 тактовой частоты поступают на умножитель 8 импульсов, коэффициент М умножения которого равен числу уплотняемых каналов. С выхода умножителя 8 импульсы длительностью tэ поступают на тактовые входы измерителя 6 мощности, обеспечивая измерение мощности процесса рm на длительности элемента каждого канального сигнала, причем

Результаты измерения с выхода измерителя 6 мощности через блок 9 задержки поступают на первый информационный вход делителя 10, на второй информационный вход которого с блока 7 оперативной памяти подается результат измерения мощности Рц. Блок 9 обеспечивает синхронность поступления информации на оба входа делителя 10 за счет задержки результатов измерения мощностей pm=1,..., М, на время Тц.

Результаты деления δm=pm/Рц, поступающие с выхода делителя 10 в блок 11, записываются в соответствующие ячейки памяти. Очередность записи в соответствии с анализируемым каналом обеспечивается импульсами, подаваемыми с умножителя 8 на тактовые входы делителя 10 и блока 11 памяти. С первого выхода ячейки памяти блока 11 поступает управляющий сигнал на блок ключей, производящий переключение каждой ячейки памяти блока 11 информации об относительных уровнях мощностей δm на соответствующие входы блока 12 ключей.

В зависимости от значения уровня δm блок 12 ключей подает на управляющие входы блока 13 мультиплексоров соответствующий сигнал, обеспечивающий подключение к канальному информационному входу блока 13 определенного числа мультиплексоров. Многоступенчатые мультиплексоры блока 13 осуществляют объединение нескольких входных потоков информации в единый выходной поток.

Чем больше значение δm, тем больше уровень помехи, действующей на сигнал анализируемого канала. Для того чтобы обеспечить требуемый уровень помехозащищенности данного канала (отношение сигнал/помеха), следует увеличить длительность элемента сигнала, т.е. уменьшить скорость передачи. Таким образом, предлагаемое устройство за счет перераспределения скоростей канальных сигналов при неизменной групповой скорости цифрового потока позволяет выровнять пороги помехозащиты (обеспечить постоянство уровней δm=const(m) для различных каналов), а следовательно, увеличить помехозащищенность многоканальной передачи информации в условиях ограниченных энергетических ресурсов постановщика помех.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1994 |

|

RU2085046C1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| Устройство синхронизации по циклам | 1980 |

|

SU886289A1 |

| Система передачи дискретной информации | 1984 |

|

SU1411983A1 |

| СПОСОБ ОТВЕТВЛЕНИЯ КАНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2193821C2 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| СПОСОБ ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2181527C1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| Система передачи цифровой информации | 1982 |

|

SU1083380A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИЕМОПЕРЕДАЧИ ДАННЫХ | 2001 |

|

RU2209524C2 |

Изобретение относится к электросвязи и может быть использовано для передачи информации. Достигаемый технический результат - повышение помехозащищенности. Устройство содержит выделитель тактовой частоты, регенератор, блок цикловой синхронизации, преобразователь последовательного кода в параллельный, умножитель импульсов, блок задержки, блок ячеек памяти, блок ключей, первый измеритель мощности, блок оперативной памяти, второй измеритель мощности, делитель, блок мультиплексоров. 1 ил.

Устройство передачи многоканальных цифровых сигналов с преобразованием скоростей, содержащее последовательно соединенные регенератор и преобразователь последовательного кода в параллельный блок цикловой синхронизации, выделитель тактовой частоты, выход которого соединен с тактовыми входами регенератора, блока цикловой синхронизации и преобразователя последовательного кода в параллельный, управляющий вход которого подключен к выходу блока цикловой синхронизации, информационный вход которого подключен к выходу регенератора, вход которого объединен с входом выделителя тактовой частоты и является входом устройства, умножитель импульсов, последовательно соединенные блок задержки, делитель, блок ячеек памяти и блок ключей, отличающееся тем, что дополнительно введены блок мультиплексоров, информационные входы которого соединены с выходами преобразователя последовательного кода в параллельный, а управляющие входы блока мультиплексоров подключены к выходам блока ключей, последовательно соединенные первый измеритель мощности и блок оперативной памяти, выход которого подключен к второму информационному входу делителя, и второй измеритель мощности, информационный вход которого вместе с информационным входом первого измерителя мощности подключены к входу устройства, выход второго измерителя мощности соединен с входом блока задержки, тактовые входы второго измерителя мощности, делителя и блока ячеек памяти подключены к выходу умножителя импульсов, вход которого вместе с тактовым входом первого измерителя мощности подключены к выходу выделителя тактовой частоты.

| Система передачи многоканальных цифровых сигналов с преобразованием скоростей | 1989 |

|

SU1706048A1 |

| Огнетушитель | 0 |

|

SU91A1 |

| US 5487035 A, 23.01.1996 | |||

| US 5509007 A, 16.04.1996. | |||

Авторы

Даты

2008-10-27—Публикация

2007-07-10—Подача