Изобретение относится к многоканальной электросвязи и может использовано в аппаратуре временного объединения и разделения высших ступеней в иерархии ЦСП с асинхронным вводом цифровых сигналов и двусторонним согласованием скорости.

Известна асинхронная цифровая система передачи, в которой для двустороннего согласования скорости в передающей части при появлении двух импульсов записи за период частоты считывания производится исключение тактового интервала из поступающего цифрового сигнала с отдельная передача символа, содержащегося в исключенном тактовом интервале этого сигнала, а при отсутствии импульсов записи за период частоты считывания производится введение в поступающий цифровой сигнал согласующих тактовых интервалов. Одновременно с выполнением согласования скорости поступающего сигнала производится формирование и передача на выделенных тактовых интервалах группового цифрового сигнала активной команды управления согласованием скорости, несущей информацию о необходимости и знаке производственного согласования для восстановления на приемной стороне исходной скорости поступающего сигнала. Защита команд управления согласованием скорости от искажений производится помехоустойчивыми кодами (см. Левин Л. С. Плоткин М. А. Цифровые системы передачи информации. М.: Радио и связь, 1982, с. 55-72, рис. 3.2).

Однако известная система имеет низкую пропускную способность, поскольку для передачи символов, содержащихся в исключенных тактовых интервалах, а также команд управления согласованием скорости требуются выделенные тактовые интервалы.

Наиболее близкой к предлагаемой системе является система для асинхронного сопряжения импульсных потоков, содержащая на передающей стороне выделитель тактовой частоты, временной детектор, блок динамической памяти, генератор тактовых импульсов, логический блок, селектор синхросигнала, блок управления и делитель частоты, а на приемной стороне - приемник синхросигнала, логический блок, блок фазовой автоподстройки частоты, блок динамической памяти, блок управления и делители частоты.

В этом устройстве для передачи команд управления согласованием формируются "дублирующие посылки" на определенных временных позициях цикла и передаются на приемную станцию для коррекции импульсных потоков, а для индикации импульсных потоков используется вводимая в групповой сигнал дополнительная избыточность (сигнал цикловой синхронизации).

Недостатками прототипа являются низкая помехоустойчивость поскольку при искажении команд управления согласованием скорости происходит истинный сбой циклового синхронизма аппаратуры временного группообразования нижней ступени иерархии, в результате которого в канал связи до восстановления синхронизма по циклам поступают ошибочные символы, а также сложность, обусловленная наличием части устройства передачи и приема команд управления согласованием.

Целью изобретения является повышение помехозащищенности с одновременным упрощением системы.

Это достигается тем, что на передающей стороне введены последовательно соединенные формирователь циклового сигнала и переключатель, причем выходы временного детектора через формирователь циклового синхросигнала соединен с дополнительными входами приемника циклового синхросигнала, сигнальный вход которого соединен с соответствующим входом блока памяти, три выхода которого соединены с соответствующими входами переключателя, к двум управляющим входам которого подключены соответствующие выходы формирователя циклового синхросигнала, а на приемной стороне приемник циклового синхросигнала выполнен в виде последовательно соединенных выделителя тактового сигнала, регистра сдвига, первого дешифратора и канального распределителя, тактовый вход которого соединен с выходом выделителя тактового сигнала, вход которого соединен с сигнальным входом регистра и является сигнальным входом приемника циклового синхросигнала, причем дополнительные выходы разрядов регистра сдвига соответственно через второй и третий дешифраторы соединены с соединенными между собой входами накопителя по входу в цикловой синхронизм и накопителя по выходу из циклового синхронизма и с соответствующим входом канального распределителя, другой вход которого соединен с первым выходом накопителя по выходу из циклового синхронизма, управляющий вход которого соединен с управляющим входом накопителя по входу в цикловой синхронизм и с соответствующим выходом канального распределителя, причем выход и второй вход накопителя по входу в цикловой синхронизм соединены соответственно с вторым входом и вторым выходом накопителя по выходу из циклового синхронизма.

Суть изобретения заключается в том, что отрицательное согласование скорости поступающего сигнала на передающей станции производится исключением одного символа из его циклового синхросигнала, а положительное согласование скорости поступающего сигнала производится добавлением одного символа к его цикловому синхросигналу, восстанавливает же исходную скорость передачи поступающего сигнала на приемной станции приемник измененного циклового синхросигнала, нечувствительный к изменениям длины и структуры синхрогруппы, устанавливаемый вместо используемого в прототипе приемника циклового синхросигнала в аппаратуру временного разделения поступающего сигнала.

Повышение помехозащищенности предложенной цифровой системы передачи по сравнению с аналогичными устройствами и прототипом достигается исключением канала передачи команд управления, согласованием скоростей передачи цифровых сигналов и схемным решением приемника измененного циклового синхросигнала. Это устраняет влияние искажений команд на качество связи. Введением в приемник второго и третьего дешифраторов, передатчика измененного циклового синхросигнала и переключателя согласование скорости передачи обеспечивается изменением числа символов в синхрогруппе.

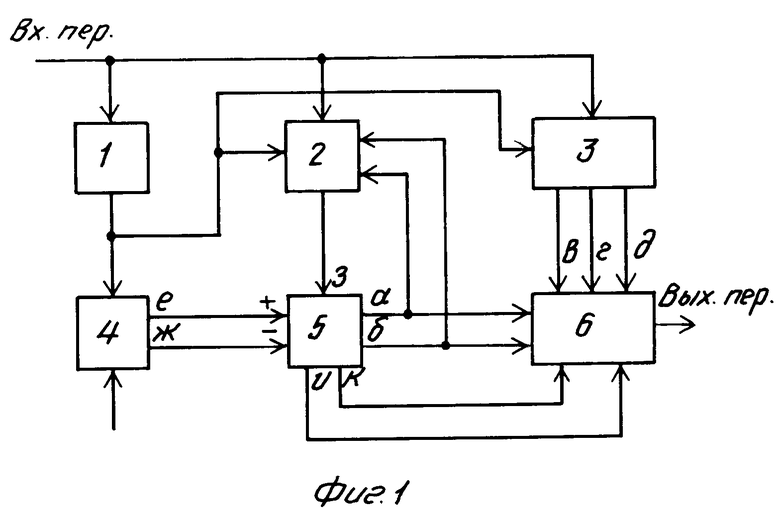

На фиг. 1 представлена схема передающей части цифровой системы передачи; на фиг. 2 - схема приемной части цифровой системы передачи.

Передающая часть системы (см. фиг. 1) содержит выделитель тактового синхросигнала 1, приемник циклового синхросигнала 2, блок памяти 3, временной детектор 4, формирователь 5, циклового синхросигнала, переключатель 6.

Объединенные входы выделителя тактового синхросигнала 1, приемника 2 и блока памяти 3 являются входом передающей части. Выход выделителя тактового синхросигнала 1 соединен с входом временного детектора 4 и с вторыми входами приемника 2 и блока памяти 3. Выходы блока памяти 3 соединены с соответствующими входами переключателя 6. Первый и второй выходы временного детектора 4 соединены с соответствующими входами формирователя 5, первый и второй выходы которого соединены соответственно с четвертым и пятым входами переключателя 6. Третий и четвертый выходы формирователя 5 соединены соответственно с шестым и седьмым входами переключателя 6 и с третьим и четвертым входами приемника 2, выход которого соединен с третьим входом передатчика 5.

Приемная часть системы представляющая приемник циклового синхросигнала (см. фиг. 2), содержит регистр сдвига 7, выделитель 8 тактового синхросигнала 8, первый дешифратор 9, накопитель 10 по входу в цикловой синхронизм, накопитель 11 по выходу из циклового синхронизма, канальный распределитель 12, дешифраторы 13 и 14.

Входом приемника измененного циклового синхросигнала являются объединенные входы регистра сдвига 7 и выделителя 8 тактового синхросигнала, выход которого соединен с первым входом канального распределителя 12 и вторым входом регистра сдвига 7, первая группа выходов которого соединена с соответствующими входами дешифратора 9, выход которого соединен с первыми входами накопителей 10 и 11. Выход и второй вход накопителя 10 соединены соответственно с вторым входом и выходом накопителя 11, второй выход которого соединен с вторым входом канального распределителя 12, выход которого соединен с третьими входами накопителей 10 и 11. Входы дешифраторов 13 и 14 соединены соответственно с второй и третьей группами выходов регистра сдвига 7, а выходы - соответственно с третьим и четвертым входами канального распределителя 12.

Устройство работает следующим образом.

Поступающий на вход передающей части системы сигнал записывается в блок памяти 3 с частотой записи f3, формируемой выделителем тактового синхросигнала 1. Сравнение этой частоты с частотой считывания fсч, поступающей от генераторного оборудования (передающей части) ГОпер. обеспечивается во временном детекторе 4. Генераторное оборудование для упрощения схемы на чертеже не показано.

Если мгновенные значения частот f3 и fсч равны, то сигналы на выходах временного детектора 4 отсутствуют. При отсутствии сигналов на входах "+" и "-" формирователя 5 сигналы на его выходах а и б устанавливают переключатель 6 в средне положение. При среднем положении переключателя 6 на его выход проходит сигнал, поступающий на его вход 2. Кроме того, сигнал на выходах а и б формирователя 5 циклового синхросигнала воздействует на приемник 2 циклового синхросигнала, что отклик на цикловой синхросигнал на выходе последнего вырабатывается в момент появления первого импульса синхрогруппы (СГ) на выходе г блока памяти 3, а значит и на выходе передающей части системы двустороннего согласования скорости. Таким образом, в цикловой синхросигнал и в цикл передачи поступающего сигнала передающая часть системы двустороннего согласования скорости никаких изменений не вносит.

Сигналы на выходах канального распределителя формируются в моменты появления в групповом сигнале символов соответствующих канальных интервалов. При несовпадении циклового синхросигнала (ЦСС), вырабатываемого канальным распределителем 12, с сигналом с выхода дешифратора 9, заполняется накопитель по выходу из циклового синхронизма 11, сбрасывается накопитель по входу 10. Когда заполнен накопитель по выходу 1, каждая синхрогруппа вызывает сброс канального распределителя 12. Если же моменты прихода СГ и появления ЦСС совпадут, начинает заполняться накопитель по входу 10. При заполнении накопителя по входу 10 происходит сброс накопителя по выходу 11, после чего канальный распределитель 12 не сбрасывается ложными синхрогруппами.

Пусть в некоторый момент времени на вход частоты записи временного детектора за один период частоты считывания поступили два импульса записи (f3 > fсч), что требует отрицательного согласования скорости поступающего сигнала. В этом случае на выходе временного детектора 4 появляется сигнал "минус", поступающий на вход ж формирователя 5 циклового синхросигнала. Этот сигнал сразу же изменит состояние выходов а, б формирователя 5 циклового синхросигнала, а через него - и состояние переключателя 6: теперь на выход переключателя 6 поступает сигнал с выхода д блока памяти 3. Произведенное таким образом увеличение времени задержки поступающего сигнала на один тактовый интервал в блоке памяти 3 препятствует пропуску символа при его продвижении с частотой считывания в схеме объединения (СО).

Кроме того, сигнал с выходов а, б формирователя 5 циклового синхросигнала воздействует на приемник циклового синхросигнала 2, который вырабатывает ЦСС на один период f3 позднее, т.е. в момент появления первого импульса синхрогруппы на выходе д блока памяти 3. По данному ЦСС, поступившему на вход з формирователя 5 циклового синхросигнала, последний выработает синхрогруппу короче номинальной на один символ, сигналом с выхода и переключит переключатель 6 на соединение со схемой объединения своего выхода и с частотой записи ведет ее в поступающий сигнал на место номинальной, после чего все сигналы на выходах передатчика измененного циклового синхросигнала 5 вернутся к исходному состоянию, и на выход переключателя 6 снова будет подключен сигнал с выхода г блока памяти 3.

Если же в некоторый момент времени за один период частоты записи на другой вход временного детектора 4 поступает два импульса частоты считывания (f3 < fсч), то на его выходе е появится сигнал "плюс", поступающий на вход в формирователя 5 циклового синхросигнала. Этот сигнал сразу изменит также состояние выходов а, в формирователя 5 циклового синхросигнала, а через него - и состояние переключателя 6: теперь на его выход поступает сигнал выхода в блока памяти 3, время задержки сигнала в блоке памяти сократится на один тактовый интервал частоты записи. Кроме того, сигнал с выходов а и б формирователя 5 циклового синхросигнала воздействует на приемник циклового синхросигнала 2, заставляя последний выработать ЦСС на один период f3 раньше, т.е. в момент появления первого импульса синхрогруппы на выходе в блока памяти. По этому ЦСС, поступившему на вход з формирователя 5 циклового синхросигнала, последний выработает синхрогруппу длиннее номинальной на один символ, сигналом с выхода к переключит переключатель 6 на соединение со СО своего выхода в и с частотой записи ведет ее в поступающий сигнал на место номинальной, после чего все сигналы на выходах формирователя 5 циклового синхросигнала вернутся к исходному состоянию и на выходе переключателя 6 снова появится сигнал с выхода г блока памяти.

Таким образом, в передающей части системы при выполнении отрицательного согласования скорости синхрогруппа поступающего сигнала укорачивается на один символ и ее последний символ передается на один тактовый интервал частоты записи раньше последнего символа номинальной синхрогруппы, или при выполнении положительного согласования скорости синхрогруппа удлиняется на один символ и ее последний символ передается на один тактовый интервал позднее последнего символа номинальной синхронизации. С выхода СР приемной части системы сигнал поступает на вход измененного циклового синхросигнала и выделителя колебания тактовой частоты. При выполнении в передающей части отрицательного согласования скорости третий дешифратор 14 выделит синхрогруппу короче номинальной на один символ на один тактовый интервал раньше момента генерации канальным распределителем 12 ЦСС, тем самым вызовет принудительный сброс последнего и последующую генерацию им канальных синхросигналов (КС) в соответствии с появлением в поступающем сигнале канальных интервалов. Положительное согласование скорости поступающего сигнала в передающей части вызовет повторный сброс канального распределителя 12 через один тактовый интервал после момента генерации им ЦСС при выделении вторым дешифратором 13 синхрогруппы длиннее номинальной на один символ, в результате чего канальные синхросигналы на выходе канального распределителя 12 также будут совпадать с моментами появления в поступающем сигнале соответствующих канальных интервалов.

Повышение помехозащищенности предлагаемого устройства по сравнению с прототипом достигается тем, что из-за изменения числа символов в цикле при согласовании скорости сдвигается во времени момент выделения циклового синхросигнала как в "измененном" цикле, так и в последующих циклах. Искажение "измененного" циклового синхросигнала может быть обнаружено по сдвигу последующих синхрогрупп теми же дешифраторами "удлиненного" и "укороченного" циклового синхросигнала. Например, цикловой синхросигнал поступающего сигнала, в соответствии с Рекомендацией МККТТ G.704, имеет вид 0011011, тогда "укороченный" цикловой синхросигнал (синхрогруппа СГк) будет 011011, а "удлиненный" - (СГд) - 00011011. Видно, что при настройке дешифратора 13 на номинальную синхрогруппу - 0011011, а дешифратора 14 - на СГк - 011011, дешифратор 13 будет срабатывать при появлении как СГд, так и "отставшей" на один тактовый интервал СГ, а третий дешифратор 14 - как при появлении СГк, так и "опережающей" на один тактовый интервал СГ.

Применение предложенной системы позволяет исключить канал передачи команд управления согласованием скорости и предотвратить истинный сбой циклового синхронизма, например, в системе ИКМ-30 за счет искажений команд управления согласованием скорости в системе ИКМ-120. Это обеспечивается заменой передающей части устройства согласования скорости в аппаратуре ИКМ-120 на передающую часть предложенной системы, а также приемника циклового синхронизма ИКМ-30 на приемник циклового синхронизма. При этом приемная часть устройства согласования скорости в ИКМ-120 может быть исключена.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для синхронизации по циклам | 1988 |

|

SU1690209A1 |

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ и КАНАЛЬНОЙ СИНХР011ИЗАЦИИ | 1970 |

|

SU259136A1 |

| СИНХРОННЫЙ АДАПТИВНЫЙ МУЛЬТИПЛЕКСОР | 1993 |

|

RU2078401C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2021 |

|

RU2782473C1 |

| Устройство цикловой синхронизации | 1981 |

|

SU987836A1 |

| СПОСОБ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ ДЛЯ СИГНАЛОВ С СОСРЕДОТОЧЕННОЙ ИЛИ РАСПРЕДЕЛЕННОЙ ПО ЦИКЛУ СИНХРОГРУППОЙ | 2021 |

|

RU2780048C1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

Использование: в многоканальной электросвязи в аппаратуре временного объединения и разделения высших ступеней иерархии цифровой системы передачи с асинхронным вводом цифрового сигнала и двусторонним согласованием скорости. Сущность изобретения: цифровая система передачи с двусторонним согласованием скорости содержит на передающей стороне выделитель тактового синхросигнала, приемник циклового синхросигнала, блок памяти, временной детектор, формирователь циклового синхросигнала и переключатель, а на приемной стороне приемник циклового синхросигнала выполнен в виде регистра сдвига, выделителя тактового синхросигнала, первого дешифратора, накопителя по входу в цикловой синхронизм, накопителя по выходу из циклового синхронизма, канального распределителя и дешифраторов. Цель изобретения - повышение помехозащищенности с одновременным упрощением системы. 2 ил.

ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ, содержащее на передающей стороне последовательно соединенные выделитель тактового сигнала и приемник циклового синхросигнала, причем выход выделителя тактового сигнала соединен с входами записи временного детектора и блока памяти, а вход - с сигнальным входом приемника циклового сигнала и является сигнальным входом системы, а на приемной стороне - приемник циклового синхросигнала, отличающаяся тем, что, с целью повышения помехозащищенности с одновременным упрощением системы, на передающей стороне введены последовательно соединенные формирователь циклового синхросигнала и переключатель, причем выходы временного детектора через формирователь циклового синхросигнала соединены с дополнительными входами приемника циклового синхросигнала, сигнальный вход которого соединен с соответствующим входом блока памяти, три выхода которого соединены с соответствующими входами переключателя, к двум управляющим входам которого подключены соответствующие выходы формирователя циклового синхросигнала, а на приемной стороне приемник циклового синхросигнала выполнен в виде последовательно соединенных выделителя тактового синхросигнала, регистра сдвига, первого дешифратора и канального распределителя, тактовый вход которого соединен с выходом выделителя тактового сигнала, вход которого соединен с сигнальным входом регистра и является сигнальным входом приемника циклового синхросигнала, причем дополнительные выходы разрядов регистра сдвига соответственно через второй и третий дешифраторы соединены с соединенными между собой входами накопителя по входу в цикловой синхронизм и накопителя по выходу из циклового синхронизма и с соответствующим входом канального распределителя, другой вход которого соединен с первым выходом накопителя по выходу из циклового синхронизма, управляющий вход которого соединен с управляющим входом накопителя по входу в цикловой синхронизм и с соответствующим выходом канального распределителя, причем выход и второй вход накопителя по входу в цикловой синхронизм соединены соответственно с вторым входом и вторым выходом накопителя по выходу из циклового синхронизма.

| Система для асинхронного сопряжения импульсных потоков | 1986 |

|

SU1420670A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1994-10-30—Публикация

1991-01-11—Подача