1

Изобретение относится к технике электросвязи и может быть использовано в аппаратуре цифровых систем передачи информации и центров коммутации при приеме и обработке синфазных по тактовой частоте цифровых потоков информации

известно устройство синхронизации по циклам,содержащее объединенные по информационному входу блёк опознавания синхросигнала и .распределитель, а также анализатор, накопитель, первый и второй блоки управления и делитель частоты, выходы кОТОР0ГО подключены к управляющим входам распределителя, при этом выход блока опознавания синхросигнала подключен к первым входам анализатора,первого и второго блоков управления, причем выход второго блока управления подключен к управляющему входу дел теля частоты , а первый выход анализатора подключен к первому входу накопителя, первый выход которого подключен к второму входу второго блока управления, второй выход анализатора подключ:ен ко входу сброса накопителя и второму входу первого блока управления 13.

Однако устройство обеспечивает цикловую синхронизацию только по одному цифровому потоку информации. Цель изобретения - обеспечение цикловой синхронизации при увеличении числа цифровых потоков информации.

Для достижения поставленной цели в устройство синхронизации по циклам,

10 содержсццее объединейные по информационному входу блок опознавания синхросигнала и распределитель, а также анализатор, накопитель, первый и второй блоки управления и делитель

15 частоты, выходы которого подключены к управляющим входам распределителя, при этом выход блока опознавания синхросигнала подключен к первым входам анализатора, первого и второ20го блоков управления, причем выход второго блока управления подключен к управляющему -входу делителя частоты, а первый выход анализатора подключен к первому входу накопителя,

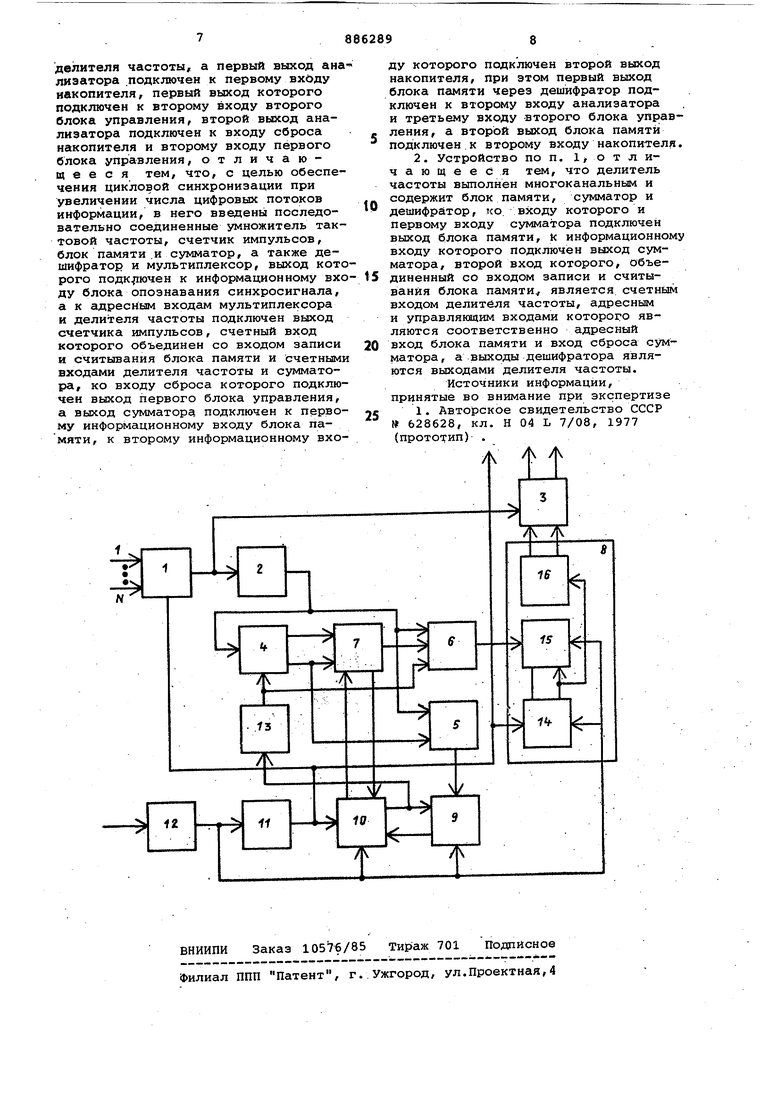

25 первый выход которого подключен к второму входу второго блока управления, второй выход анализатора подключен ко входу сброса накопителя и второму входу первого блока управления,введены последовательно сое.диненные умножитель тактовой частоты, счетчик импульсов, блок памяти и сумматор, а также дешифратор и мультиплексор, выход которого подключен к информационному входу блок опознавания синхросигнала, а к адре HfcBwi входам мультиплексора и делителя частоты подключен выход счетчика 1№тульсов, счетный вход которого {объединен со входом записи и считывания блока памяти и счетными входа ми делителя частоты и сумматора, ко входу сброса которого подключен выход первого блока управления, а выход сумматора подключен к первому информационному входу блока памяти, к второму, информационному входу кот рого подключен второй выход на.копителя, при этом первый выход блока памяти через дешифратор подключен к второму входу анализатора и треть му входу второго блока управления, а второй выход блока памяти, .подключен к второму входу накопителя. Кроме того, делитель частоты выполнен многоканальным и содержит блок памяти, сумматор и дешифратор, ко входу которого и первому входу сумматора подключен выход блока памяти к информационному входу которого -подключен выход сумматора, вто рой вход которого, объединенный со входом записи и считывания блока памяти, является счетным делителя частоты, адресным и. управляю щим входами которого являются соответственно адресный вход блока памя ти и вход сброса сумматора, а выход дешифратора являются выходами делителя частоты. На чертеже представлена структур ная схема предлагаемого устройства. Устройство содержит мультиплексор 1, блок 2 опознавания синхросигнала, распределитель 3, анализатор 4, первый 5 и второй б блоки управления, накопитель 7, делитель частоты, сумматор 9, блок 10 памяти счетчик 11 импульсов, умножитель 12 тактовой частоты/ дешифратор 13, блок 14 памяти делителя частоты, : сумматор ,15 делителячастоты и дешифратор i б делителя частоты. Предлагаемое устройство работае следующим образом. Независимо от состояния синхронизма в отдельных цифровых потоках общий сигнал тактовой.частоты сигналов fс поступает на вхоД умножителя 12 тактовой частоты, на выходе которого формируется сигнал тактовой частоты устройства Nfj. . В счетчике 11 импульсов обеспечивается пересчет числа импульсов так товой частоты fj с коэффициентом NU, на выходе формируется параллель ный двоичный код, являющийся кодом номера обрабатываемого в данный момент цифрового потока, который поступает на адресные входы делителя 8 частоты, мультиплексора 1, блока 10 памяти. Мультиплексор 1 осуществляет коммутацию на выход символа цифрового потока, номер которого задается кодом на его адресном входе, в результате чего на вы- ходе мультиплексора 1 образуется групповой сигнал с посимвольным временным уплотнением цифровых потоков.. Весь процесс обработки сигналов i-го цифрового потока () в устройстве осуществляется за соответствующий период тактовой частоты устройства f , а за период тактовой частоты цифровых потоков f обеспечивается поочередная обработка сигналов всех N цифровых потоков. В первой половине-периода тактовой частоты f, задаваемой,например, выЬоким уровнем сигнала тактовой частоты, осуществляется считывание информации из блока 10 памяти по адресу, задаваемому счетчиком 11 импульсов. Данные о текущем номере символа обрабатываемого цифрового .потока в цикле синхронизации с первого выхода блока 10 памяти поступает на второй .вход сумматора 9, где к номеру символа прибавляется единица, задаваемая сигналом тактовой частоты f на первом входе сумматора 9. При поступлении на вход сумматора 9 кода, соответстсвующего значению К-1j он переходит в нулевое состояние, в которое он устанавливается также сигналом сброса, поступающим с первого блока 5 управления. Данные о состояний накопителя 7 в предьщущем тактовом интервале со второго вьохода блока 10 памяти поступают на второй вход накопителя 7, где в зависимости от выходных сигналов анализатора 4 осуществляется обновление информации о состоянии накопителя 7 или же она остается там без изменений. Обновленные данные о номере последующего символа в цикле синхронизации и состоянии накопителя 7 с выхода сумматора 9 и второго выхода накопителя 7 соответственно поступают на первый и второй информационные входы блока 10 памяти и во второй половине периода тактовой частоты f осуществляется запись этих данных по тому же адресу, по которому была считана информация в первой .половине периода. В дешифраторе 13 осуществляется декодирование нулевой кодовой комбинации, соответствующей позиций синхросигнала в цикле синхронизации, т.е. началу цикла синхронизации, и формирование соответствукядего импульса, поступающего на второй вход анали.затора 4 и на третий вход второго блока б управления.

Работа делителя 8 частоты заключается в том, что в первой половине периода тактовой частоты осуществляется считывание из блока 14 памяти по адресу, задаваемому счетчиком и импульсов, данных о номере текущего символа в цикле синхронизации, прибавление к этим данным в сумматоре 15 единицы, задаваемой сигналом тактовой частоты на втором входе сумматора 15, и последующая во второй половине периода запись обновленных данных с выхода сумматора /15 14 памяти. Сумматор 15 из состояния К-1 переходит в нулевое состояние. В это же состояние он устанавливается сигналом сброса, поступающим с выхода второго блока б управления. В дешифраторе 16 осуществляется декодирование кодовых комбинаций определенных номеров символов в цикле синхронизации, сигналы которых с выхода его поступают на управляющие входы распределителя 3.

Блок 2 опознавания синхросигнала осуществляет анализ символов группо,вого сигнала, относящихся к обрабатываемому цифровому потоку, R при поступлении кодовой комбинации синхросигнала формирует импульсный сигнал, поступающий на первые входы анализатора 4, первого 5 и второго 6 блоков управления.

В состоянии установившегося синхронизма по i-му цифровому потоку сигналы, поступающие на первый и второй входы анализатора 4 сблока 2 опознавания синхросигнала и дешифратора 13, совпадают во времени . При этом формируется сигнал на первом выходе анализатора 4, поступающий на первый вход накопителя 7 и обеспечивающий поддержание его в состоянии насыщения. Выходной сигнал с накопителя 7, поступающий на второй вход второго блока б управления, разрешает работу его,.и выходным сигналом этого блока обеспечивается установка сумматора 15 делителя 8 частоты в нулевое состояние и, следовательно, Финфазность работы делителя 8 частоты по i-му цифровому потоку. Распределитель 3, управляемый дешифратором 16 делителя 8 частоты. Обеспечивает правильную селекцию сигналов, которые поступают на выход устройства совместно с кодом номера цифрового потока, к которому они относятся, формируемым счетчиком И импульсов. .

При искажении синхросигнала или сбое синхронизма, т.е. при возникновении ошибки типа временного сдвига, на.очередной импульс дешифратора 13 импульс с блока 2 опознавания синхросигнала не поступает. При этом анализатор 4 на втором.входе формирует импульс, поступающий на вход сброса накопителя 7 и на второй вход первого блока 5 управления. При этом выходным сигналом накопителя 7 блокируется работа второго блока 6 управления, что обеспечивает делителю 8 частоты возможность продолжать работу с сохранением прежней фазы. Сигнал о состоянии накопителя с первого выхода накопителя 7 записывается по i-му адресу в блоке 10 i памяти. Выходным сигналом первого блока.5 управления сумматор 9 уста0навливается в нулевое состояние и с него в блок 10 памяти записывается нулевая комбинация. В следующем . периоде тактовой частоты f из блока 10 памяти считывается нулевая кодо-

5 вая комбинация и тем самым обеспечивается начало процесса поиска синхронизма по i-му потоку при сохранении неизменности фазы делителя .8 частоты. При обнаружении синхросиг0нала в процессе,поиска синхронизма сигнал с первого выхода анализатора 4 поступает на первый вход накопителя 7, который к коду предыдущего состояния, считанного из блока 10 памяти, прибавляет единицу, и обнов5ленная информация о состоянии накопителя 7 переписывается в блок 10 памяти. При достижении накопителем 7 заданного состояния, характеризующего окончание поиска синхронизма,

0 с первого выхода накопителя 7 поступает разреша1садий сигнал на второй вход второго блока 6 управления, который в момент, определяемый сигналом на третьем входе, выходным сигналом

5 осуществляет сброс сумматора 15 делителя 8 частоты в нулевое состоя- . ние, и тем самым устанавливает требуемую фазу делителя 8 частоты по обрабатываемому цифровому потоку, в

0 результате чего устанавливается также соответствующая фаза.работы распределителя 3.

Устройство:обеспечивает цикловую синхронизацию при увеличении числа цифровых потоков информации, а также

5 позволяет снизить затраты на реализацию аппаратуры синхронизации, уменьшить габариты и вес -аппаратуры.

Формула изобретения

1. Устройство синхронизации по циклам, содержащее объединенные по информационному входу блок опознавания синхросигнала и распределитель, а также анализатор, накопитель, первый и .второй блоки управления и делитель частЬты, выходы которого подключены к управляющим входам распределителя, при этом выход блока опознавания синхросигнала подключен к первым входам анализатора, первого и второго блоков управления, причем выход второго блока управления подключен к управляющему входу

делителя частоты, а первый выход анализатора .подключен к первому вхбду иакопителя, первый выход которого подключен к второму входу второго блока управления, второй выход анализатора подключен к входу сброса накопителя и второму входу первого блока управления, отличающееся тем, что, с целью обеспечения цикловой синхронизации при увеличении числа цифровых потоков информации, в него введены последовательно соединенные умножитель тактовой частоты, счетчик импульсов, блок памяти .и сумматор, а также дешифратор и мультиплексор, выход которого подключен к информационному входу блока опознавания синхросигнала, а к адресным входам мультиплексора и делителя частоты подключен выход счетчика импульсов, счетный вход которого объединен со входом записи и считывания блока памяти и счетными входами делителя частоты и сумматора, ко входу сброса которого подключен выход первого блока управления, а выход сумматора подключен к первому информационному входу блока памяти, к второму информационному входу которого подключен второй выход накопителя, при этом первый выход блока памяти через дешифратор подключен к второму входу анализатора и третьему входу второго блока упраления, а второй выход блока памяти подключен.к второму входу накопител

2. Устройство по п. 1j о т л ичающееСя тем, что делитель частоты выполнен многоканальным и содержит блок памяти, сумматор и дешифратор, ко входу которого и первому входу сумматора подключен выход блока памяти, к информационно входу которого подключен выход сумматора, второй вход которого, объединенный со входом записи и считывания блока памяти является счетны входом делителя частоты, адресным и управляющим входами которого являются соответственно адресный вход блока памяти и вход сброса сумматора, а выходы дешифратора являются выходами делителя частоты.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 628628, кл. Н 04 L 7/08, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОКАНАЛЬНОЕ ПРИЕМОПЕРЕДАЮЩЕЕ УСТРОЙСТВО С ВРЕМЕННЫМ РАЗДЕЛЕНИЕМ ЦИФРОВЫХ АСИНХРОННЫХ КАНАЛОВ | 1989 |

|

RU2033695C1 |

| УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 1999 |

|

RU2173027C2 |

| Устройство для цикловой синхронизации | 1981 |

|

SU1107317A1 |

| Устройство синхронизации по циклам | 1977 |

|

SU628628A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2009 |

|

RU2450465C2 |

| Устройство цикловой синхронизации | 1981 |

|

SU949832A1 |

| ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ С ДВУСТОРОННИМ СОГЛАСОВАНИЕМ СКОРОСТИ | 1991 |

|

RU2022476C1 |

| УСТРОЙСТВО ВРЕМЕННОГО ГРУППООБРАЗОВАНИЯ | 2006 |

|

RU2306674C1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Декодирующее устройство | 1985 |

|

SU1339894A1 |

Авторы

Даты

1981-11-30—Публикация

1980-03-21—Подача