Изобретение относится к технике защиты различных объектов от доступа посторонних лиц, в частности, к электронным кодовым замкам.

Известно устройство управления электронного замка (см. авт. свид. СССР №1339229 от 08.04.86 г., МКИ: Е05В 47/00, "Кодовый замок" авторов М.Н.Бобова, В.В.Епихина и А.А.Обуховича, опубл. 23.09.87 г., БИ №35), содержащее блок выявления ложного кода, блок приема кода, блок приема кода разблокировки, триггер, элемент И, счетчик, коммутатор, реле времени, элемент НЕ, дополнительный элемент И, исполнительный блок, три входные и две выходные шины. Первые входы блока приема кода и блока выявления ложного кода соединены соответственно с первой и второй входными шинами устройства. Первый вход блока приема кода разблокировки соединен с третьей входной шиной устройства, второй вход - с выходом триггера и первым входом элемента И, выход - с вторым входом элемента И. Выход элемента И соединен с установочным входом счетчика, своим счетным входом соединенного с выходом блока выявления ложного кода и первым входом коммутатора, вторым входом соединенного с выходом счетчика. Первый выход коммутатора соединен со вторым входом блока приема кода и первым входом триггера, второй выход - с первым входом реле времени, второй вход которого подключен к первому выходу блока приема кода и второму входу триггера, первый выход соединен с третьим входом блока приема кода и вторым входом блока выявления ложного кода, второй выход - с первым входом исполнительного блока, второй вход которого соединен с вторым выходом блока приема кода, выход - с первой выходной шиной устройства. Третий выход реле времени соединен с первым входом дополнительного элемента И, к второму входу которого через элемент НЕ подключен выход триггера, а выход дополнительного элемента И соединен с второй выходной шиной устройства.

Недостатком устройства является низкий уровень защиты от целенаправленной быстрой блокировки его посторонними лицами, поскольку учитываются любые ошибки в наборе входного кода. Это может привести к недопустимой задержке открывания электронного замка постоянными пользователями (например, при необходимости своевременно попасть в помещение, где хранятся средства пожаротушения, химической или радиационной защиты, табельное оружие или боеприпасы личного состава военизированных подразделений и т.п.).

Наиболее близким по технической сущности к заявляемому объекту является устройство управления электронного замка (см. пат. РФ №2239037, МКИ: Е05В 49/00 "Устройство управления электронного замка" авторов Р.Ф.Зубаерова, С.В.Панкратова, Г.И.Шишкина, опубл. 27.10.2004 г., Бюл. №30), содержащее коммутатор, два блока приема и сравнения кодов, реле времени, блок приема кода разблокировки, три элемента И, счетчик несовпадений кодов, две входные и две выходные шины. Первый вход сброса счетчика несовпадений кодов подключен к выходу первого элемента И. Первая входная (информационная) шина соединена с первым входом блока приема и сравнения кодов, второй вход которого подключен к первому выходу коммутатора, третий вход соединен с первым входом второго блока приема и сравнения кодов, вторым входом коммутатора и подключен к первому выходу реле времени, входом подключенного ко второму выходу коммутатора, вход которого соединен со второй входной (тактовой) шиной устройства, третий выход - с вторым входом второго блока приема и сравнения кодов, третьим входом соединенного с первой входной шиной устройства. Второй выход реле времени соединен с четвертым входом второго блока приема и сравнения кодов и со входом блока приема кода разблокировки, первая и вторая группы входов которого подключены к соответствующим выходам соответственно первого и второго блоков приема и сравнения кодов. Выход второго элемента И соединен с первой выходной шиной устройства и первым входом первого элемента И, первый вход - с выходом первого блока приема и сравнения кодов и с первым входом третьего элемента И, второй вход - с первым выходом второго блока приема и сравнения кодов, вторым выходом соединенного с вторым входом третьего элемента И, выход которого соединен со счетным входом счетчика несовпадений кодов, второй вход сброса которого соединен с выходом блока приема кода разблокировки, выход счетчика несовпадений кодов соединен со вторым входом первого элемента И, третьими входами второго и третьего элементов И и второй выходной шиной устройства.

Коммутатор содержит счетчик тактов, RS-триггер и четвертый, пятый и шестой элементы И, выходы которых являются соответственно первым, вторым и третьим выходами коммутатора, а первые входы соединены со счетным входом счетчика и первым входом коммутатора, второй вход которого соединен с R-входами счетчика и RS-триггера, S-вход которого подключен к первому выходу счетчика несовпадений кодов, второй выход которого соединен со вторым входом пятого элемента И, вторые входы четвертого и шестого элементов И соединены соответственно с инверсным и прямым выходами RS-триггера.

Первый блок приема и сравнения кодов содержит постоянное запоминающее устройство, схему сравнения и сдвиговый регистр, D, С и R-входы которого являются соответственно первым, вторым и третьим входами блока приема и сравнения кодов, выход которого подключен к выходу схемы сравнения, входы которой соединены с соответствующими выходами постоянного запоминающего устройства и сдвигового регистра. Выходы сдвигового регистра составляют группу выходов блока приема и сравнения кодов.

Реле времени содержит инвертор, интегрирующую RC-цепь и триггер Шмитта, выход которого является первым выходом реле времени, а первый и второй входы которого подключены к выходам соответственно интегрирующей RC-цепи и инвертора, входы которых соединены со входом и вторым выходом реле времени.

Данное устройство обеспечивает при анализе входного кода защиту от целенаправленной быстрой блокировки, поскольку учитываются только ошибки в наборе его второй части при условии правильного предварительного набора первой части.

Недостатком устройства является высокая вероятность открывания замка путем подбора кода, поскольку в случае, когда в процессе подбора кода присутствуют ошибки в наборе первой части кода или количество ошибочных наборов второй части при правильном наборе первой части не превышает допустимое значение, блокировка замка не производится и процесс открывания замка не усложняется. При этом в случае правильного набора второй части кода ошибки в наборе первой части не учитываются, что создает дополнительные возможности открывания замка путем подбора кода.

Задачей, решаемой предлагаемым изобретением, является создание устройства управления электронного замка, обеспечивающего малую вероятность его открывания путем подбора кода при сохранении защищенности от целенаправленной быстрой блокировки.

Технический результат, заключающийся в уменьшении вероятности открывания замка путем подбора кода, достигается тем, что в устройство управления электронного замка, содержащее счетчик тактов, счетчик несовпадений кодов, постоянное запоминающее устройство, RS-триггер, триггер Шмитта, интегрирующую RC-цепь и пять элементов И, выход первого из которых соединен с R-входом счетчика несовпадений кодов, выход второго элемента И соединен с выходной шиной, а первый и второй входы соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен со счетным входом счетчика несовпадений кодов, выход RC-цепи соединен с входом триггера Шмитта, выход которого соединен с R-входом счетчика тактов, счетный вход которого соединен с тактовой шиной устройства, введены счетчик совпадений кодов, мультиплексор и элемент "исключающее ИЛИ", первый и второй входы которого соединены соответственно с информационной шиной устройства и с выходом мультиплексора, первый и второй вход которого соединены соответственно с первым и вторым выходами постоянного запоминающего устройства, адресные входы которого подключены к выходам соответствующих разрядов счетчика тактов, выход которого соединен с входом интегрирующей RC-цепи и первым входом второго элемента И, второй вход которого соединен с инверсным выходом счетчика несовпадений кодов, прямой выход которого соединен с управляющим входом мультиплексора и первым входом четвертого элемента И, второй вход которого соединен с третьим входом второго элемента И, третьим инверсным входом третьего элемента И и выходом А счетчика совпадений кодов, выход Б которого соединен с четвертым входом третьего элемента И, выход четвертого элемента И соединен с S-входом RS-триггера, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера Шмитта, R-входом RS-триггера и R-входом счетчика совпадений кодов, С-вход которого соединен с выходом пятого элемента И, первый вход которого соединен с тактовой шиной, а второй вход - с инверсным выходом элемента "исключающее ИЛИ".

Указанная совокупность признаков позволяет уменьшить вероятность открывания замка путем подбора кода при сохранении защищенности от целенаправленной быстрой блокировки путем последовательного сравнения с эталоном состояния всех разрядов входного кода, суммирования количества совпадений и разрешения переключения счетчика несовпадений только после набора заданного количества совпадений по всем разрядам входного кода, а не только первой его части.

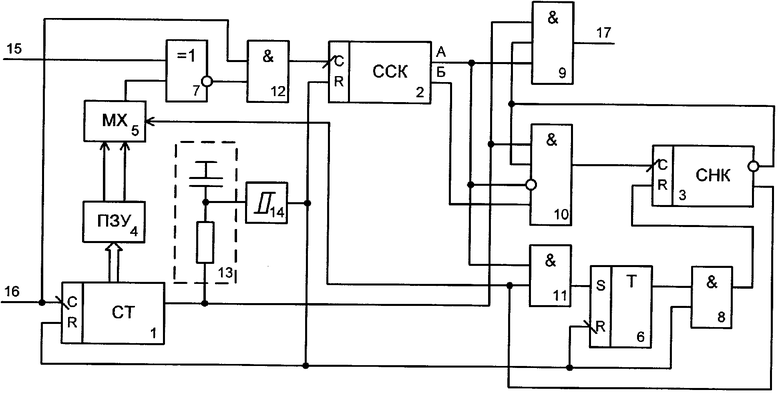

На чертеже приведена структурная схема устройства управления электронного замка.

Устройство управления электронного замка содержит счетчик 1 тактов (СТ), счетчик 2 совпадений кодов (ССК), счетчик 3 несовпадений кодов (СНК), постоянное запоминающее устройство (ПЗУ) 4, мультиплексор 5 (MX), RS-триггер 6, элемент "Исключающее ИЛИ" 7 (ИИ), первый 8, второй 9, третий 10, четвертый 11 и пятый 12 элементы И, интегрирующую RC-цепь 13, триггер Шмитта 14, информационную 15 и тактовую 16 шины, выходную шину 17.

Счетный вход СТ1 соединен с тактовой шиной 16 и первым входом элемента И 12, R-вход СТ1 соединен с выходом триггера Шмитта 14, R-входом ССК2, R-входом RS-триггера 6 и вторым входом элемента И8. Выход СТ1 соединен с входом RC-цепи 13 и первыми входами элементов И9 и И 10. Выходы разрядов СТ1 соединены с соответствующими адресными входами ПЗУ4. Счетный вход ССК2 соединен с выходом элемента И12. Выход А ССК2 соединен с инверсным третьим входом элемента И 10, третьим входом элемента И9 и вторым входом элемента И11, выход Б ССК2 соединен с четвертым входом элемента И10, выход которого соединен со счетным входом СНК3, R-вход СНК3 соединен с выходом элемента И8. Прямой выход СНКЗ соединен с управляющим входом МХ5 и первым входом элемента И11, инверсный выход СНК3 соединен со вторыми входами элементов И9 и И10. Первый и второй выходы ПЗУ4 соединены соответственно с первым и вторым входами МХ5, выход которого соединен со вторым входом элемента ИИ7. Выход элемента И11 соединен с S-входом RS-триггера 6, выход которого соединен с первым входом элемента И8. Информационная шина 15 соединена с первым входом элемента ИИ7, инверсный выход которого соединен со вторым входом элемента И 12. Выход элемента И9 соединен с выходной шиной 17. Выход RC-цепи 13 соединен с входом триггера Шмитта 14.

СТ1, ССК2 и СНК3 могут быть выполнены на микросхемах 564ИЕ10, сигнал переноса на выходе счетчиков может при необходимости формироваться с помощью дешифратора состояния. Модуль счета СТ1 должен соответствовать разрядности эталонных кодов, СНК3 - допустимому количеству несовпадений. Модуль счета для выхода А ССК2 должен соответствовать разрядности эталонных кодов, для выхода Б - пороговому количеству совпадений. ПЗУ4 может быть реализовано на ЗУ типа 556РТ4А, 558РР2, 1623РТ1. Элементы ИИ7, И8-И12 могут быть выполнены на соответствующих базовых элементах микросхем серии 564, триггер Шмитта 14 - на 564ТЛ1, RS-триггер 6 - на 564ТМ2, МХ5 - на 564КП1. Уровень логического нуля (сигнал низкого уровня) на управляющем входе МХ5 разрешает прохождение на выход сигнала с первого входа, уровень логической единицы (сигнал высокого уровня) - со второго входа.

Устройство управления электронного замка работает следующим образом.

В исходном состоянии на шинах 15 и 16 поддерживается уровень логического нуля, на шине 17 также присутствует уровень логического нуля, СТ1, ССК2, СНК3 и RS-триггер 6 установлены в состояние логического нуля, на управляющем входе МХ5 присутствует сигнал низкого уровня.

Предположим, что на информационную шину 15 поступает код, соответствующий эталонному значению кода открывания, на тактовую шину 16 - тактовые импульсы. СТ1, отсчитывая тактовые импульсы, формирует сигналы для последовательного поразрядного вывода из ПЗУ4 эталонных значений кодов открывания и разблокировки замка, поступающих на первый и второй входы МХ5 соответственно. Так как на управляющем входе МХ5 присутствует сигнал низкого уровня, на выход МХ5 и далее на второй вход элемента ИИ7 поступает эталонное значение кода открывания замка.

Вследствие соответствия входного кода и эталонного значения кода открывания замка при их последовательном поразрядном сравнении на инверсном выходе элемента ИИ7 будет постоянно присутствовать уровень логической единицы. Следовательно, на выходе элемента И12 на время действия тактового импульса также будет появляться сигнал высокого уровня, ССК2 будет отсчитывать количество совпадений значений разрядов, и при достижении порогового количества совпадений на выходе Б ССК2 появится сигнал высокого уровня. По переднему фронту импульса, соответствующего последнему импульсу входного кода, на выходе А ССК2 появляется сигнал высокого уровня, поступающий на третий вход элемента И9, третий инверсный вход элемента И10 и на второй вход элемента И11, на первом входе которого присутствует сигнал низкого уровня, следовательно, на S-входе RS-триггера 6 присутствует сигнал низкого уровня, и RS-триггер 6 останется в состоянии логического нуля.

По заднему фронту тактового импульса, соответствующего последнему разряду входного кода, на выходе СТ1 появится сигнал высокого уровня, который поступает на первые входы элементов И9 и И10. Вследствие того, что ССК2 зафиксировано соответствие входного кода эталонному значению кода открывания и на инверсном выходе СНК3 присутствует сигнал высокого уровня, элементом И9 на выходной шине 17 формируется сигнал открывания замка. Так как на инверсном третьем входе элемента И 10 присутствует сигнал высокого уровня, формирование сигнала счета СНК3 элементом И10 не производится.

Выходной сигнал высокого уровня СТ1 также поступает на вход RC-цепи 13 и далее на вход триггера Шмитта 14. С задержкой, определяемой постоянной времени RC-цепи 13 и порогом срабатывания триггера Шмитта 14, на выходе триггера Шмитта 14 формируется сигнал высокого уровня, поступающий на R-входы СТ1, ССК2 и RS-тригтера 6 и на второй вход элемента И8, при этом вследствие того, что RS-триггер 6 установлен в состояние логического нуля и на его выходе присутствует сигнал низкого уровня, элементом И8 сигнал сброса СНК3 не формируется. Сигнал высокого уровня с выхода триггера Шмитта 6 обнуляет СТ1 и ССК2, на выходе СТ1 появится уровень логического нуля, блокирующий дальнейшее формирование сигнала открывания замка. Выходной сигнал низкого уровня СТ1, поступая на вход RC-цепи 13 и далее на вход триггера Шмитта 14 с задержкой, определяемой постоянной времени RC-цепи 13 и порогами срабатывания и отпускания триггера Шмитта 14, переключает триггер Шмитта 14 в состояние логического нуля.

Следовательно, при входном коде, соответствующем эталонному значению кода открывания, на выходной шине 17 происходит формирование сигнала открывания замка, состояние СНК3 не изменяется.

Предположим, что на информационную шину 15 поступает код, у которого количество совпадающих с эталонным значением кода открывания разрядов меньше порогового. Так как на управляющем входе МХ5 присутствует сигнал низкого уровня, на выход МХ5 и далее на второй вход элемента ИИ7 поступает эталонное значение кода открывания замка.

При поразрядном сравнении входного кода и эталонного значения кода открывания в случае совпадения значений разрядов на инверсном выходе элемента ИИ7 будет присутствовать сигнал высокого уровня. Следовательно, на выходе элемента И 12 на время действия тактового импульса также появится уровень логической единицы, и ССК2 будет производить счет совпадающих разрядов. В случае несовпадения значений разрядов на инверсном выходе элемента ИИ7 будет присутствовать уровень логического нуля, на выходе элемента И 12 также будет присутствовать уровень логического нуля, и ССК2 не будет переключаться. Так как количество совпадающих значений разрядов входного кода и эталонного значения кода открывания меньше порогового, то поступлении последнего тактового импульса на выходах А и Б ССК2 будет присутствовать уровень логического нуля. На входах элемента И11 также присутствует сигналы низкого уровня, и RS-триггер 6 останется в состоянии логического нуля.

По заднему фронту тактового импульса, соответствующего последнему разряду входного кода, на выходе СТ1 появится сигнал высокого уровня, поступающий на первые входы элементов И9 и И10. Вследствие того что на третьем входе элемента И9 присутствует уровень логического нуля, формирование сигнала открывания замка на выходной шине 17 не произойдет. Так как на четвертом входе элемента И 10 присутствует сигнал низкого уровня, формирование сигнала счета СНК3 элементом И10 не происходит.

Выходной сигнал высокого уровня СТ1 также поступает на вход RC-цепи 13 и далее на вход триггера Шмитта 14. На выходе триггера Шмитта 14 формируется сигнал высокого уровня, поступающий на R-входы СТ1, ССК2 и триггера 6 и на второй вход элемента И8, при этом вследствие того, что RS-триггер 6 установлен в состояние логического нуля, сигнал сброса СНК3 элементом И8 не формируется. Сигнал высокого уровня с выхода триггера Шмитта 6 обнуляет СТ1 и ССК2. Выходной сигнал низкого уровня СТ1, поступая на вход RC-цепи 13 и далее на вход триггера Шмитта 14, переключает триггер Шмитта 14 в состояние логического нуля.

Следовательно, при входном коде, у которого количество совпадающих с эталонным значением кода открывания разрядов меньше порогового, сигнал открывания замка не формируется, состояние СНКЗ не изменяется.

Предположим, что на шину 15 поступает код, не совпадающий с эталонным значением кода открывания, у которого количество совпадающих значений разрядов больше порогового.

Так как на входе управления МХ5 присутствует сигнал низкого уровня, на выход МХ5 и далее на второй вход элемента ИИ7 поступает эталонное значение кода открывания замка.

При поразрядном сравнении значений разрядов входного кода и эталонного значения кода открывания при их совпадении на инверсном выходе элемента ИИ7 будет присутствовать уровень логической единицы, на выходе элемента И 12 на время действия тактового импульса - уровень логической единицы, и ССК2 будет производить счет совпадающих разрядов.

Вследствие того, что количество соответствующих значений разрядов входного кода и эталонного значения открывания больше модуля счета ССК2 по выходу Б, но меньше, чем по выходу А, то по переднему фронту последнего импульса входного кода на выходе А ССК2 будет присутствовать уровень логического нуля, на выходе Б - уровень логической единицы, следовательно, на входах элемента И11 присутствует сигналы низкого уровня, и RS-триггер 6 останется в состоянии логического нуля.

По заднему фронту тактового импульса, соответствующего последнему разряду входного кода, на выходе СТ1 появится сигнал высокого уровня, поступающий на первые входы элементов И9 и И10. Вследствие того, что на третьем входе элемента И9 присутствует уровень логического нуля, формирование сигнала открывания замка на выходной шине 17 не произойдет. Так как на четвертом входе элемента И10 присутствует сигнал высокого уровня, происходит формирование элементом И10 сигнала счета СНК3.

Если количество зафиксированных совпадений меньше допустимого, на инверсном выходе СНК3 продолжает присутствовать уровень логической единицы, на прямом выходе и, как следствие, на входе управления МХ5 будет присутствовать уровень логического нуля.

В случае если после переключения состояние СНК3 соответствует допустимому количеству несовпадений, на его выходе присутствует уровень логического нуля, который, поступая на вторые входы элементов И9 и И10, блокирует формирование сигнала открывания замка и прохождение счетных импульсов на вход СНК3. На прямом выходе СНК3 будет присутствовать уровень логической единицы, поступающий на вход управления МХ5 и на первый вход элемента И11, состояние которого не изменяется и не вызывает изменение состояния RS-триггера 6.

Выходной сигнал высокого уровня СТ1 также поступает на вход RC-цепи 13 и далее с задержкой на вход триггера Шмитта 14. На выходе триггера Шмитта 14 формируется сигнал высокого уровня, поступающий на R-входы СТ1, ССК2 и RS-триггера 6 и на второй вход элемента И8, при этом вследствие того, что RS-триггер 6 установлен в состояние логического нуля, сигнал сброса СНК3 элементом И8 не формируется. Сигнал высокого уровня с выхода триггера Шмитта 6 обнуляет СТ1 и ССК2. Выходной сигнал низкого уровня СТ1, поступая на вход RC-цепи 13 и далее на вход триггера Шмитта 14, переключает триггер Шмитта 14 в состояние логического нуля.

Следовательно, при входном коде, у которого количество совпадающих с эталонным значением кода открывания разрядов больше порогового, сигнал открывания не формируется, состояние СНК3 увеличивается на единицу. В случае достижения состояния СНК3 состояния, соответствующего допустимому количеству несовпадений, СНК3 блокируется от дальнейших переключении и блокирует формирование сигнала открывания замка.

Следует отметить, при наличии одной или нескольких неудачных попыток открыть замок, количество которых не привело к самоблокировке устройства, ввод входного кода, совпадающего с эталонным значением кода открывания замка, обеспечивает формирование сигнала открывания замка.

Рассмотрим работу устройства в случае, если СНК3 находится в состоянии блокировки. При этом на входе управления МХ5 присутствует уровень логической единицы, следовательно, на второй вход элемента ИИ7 поступает эталонное значение кода разблокировки.

В случае если на шину 15 поступает код, не соответствующий эталонному значению кода разблокировки, при поразрядном сравнении входного кода и эталонного значения кода разблокировки на выходе элемента ИИ7 в случае совпадения значений разрядов будет появляться уровень логической единицы. На выходе элемента И12 в момент действия тактового импульса также появится уровень логической единицы, и ССК2 будет производить счет. Вследствие того, что количество соответствующих значений разрядов входного кода и эталонного значения кода разблокировки меньше модуля счета ССК2 по выходу А, то после поступления последнего импульса входного кода на выходе А будет присутствовать уровень логического нуля.

По заднему фронту тактового импульса, соответствующему последнему разряду входного кода, на выходе СТ1 появится уровень логической единицы. Вследствие присутствия на втором и третьем входах элемента И9 уровня логического нуля формирование сигнала открывания замка на выходной шине 17 не происходит. Вследствие присутствия на втором входе элемента И10 уровня логического нуля формирования сигнала счета СНКЗ не происходит. Так как на втором входе элемента И11 установлен уровень логического нуля, формирование сигнала сброса СНК3 элементом И 11, RS-триггером 6 и элементом И8 не происходит.

Выходной сигнал высокого уровня СТ1 поступает на вход RC-цепи 13 и далее с на вход триггера Шмитта 14, на выходе которого формируется сигнал высокого уровня, устанавливающий СТ1 и ССК2 в состояние логического нуля. На выходе СТ1 появится уровень логического нуля, поступающий на вход RC-цепи 13 и далее на вход триггера Шмитта 14, переключающий триггер Шмитта 14 в состояние логического нуля.

Рассмотрим работу устройства в случае, если СНКЗ находится в состоянии блокировки и на информационную шину 15 поступает код, соответствующий эталонному значению кода разблокировки.

При поразрядном сравнении входного кода и эталонного значения кода разблокировки на выходе элемента ИИ7 при совпадении значений разрядов будет появляться уровень логической единицы. На выходе элемента И12 в момент действия тактового импульса также появится уровень логической единицы, и ССК2 будет производить счет. Вследствие соответствия входного кода и эталонного значения кода разблокировки после поступления последнего импульса входного кода на выходах А и Б ССК2 будет присутствовать уровень логической единицы.

Так как на обоих входах элемента И11 установлен уровень логической единицы, на выходе элемента И11 появится сигнал высокого уровня, устанавливающий RS-триггер 6 в состояние логической единицы, на его выходе появится сигнал высокого уровня.

По заднему фронту тактового импульса, соответствующего последнему разряду входного кода, на выходе СТ1 появится уровень логической единицы. Вследствие присутствия на втором входе элемента И9 уровня логического нуля формирование сигнала открывания замка на выходной шине 17 не происходит.

Выходной сигнал высокого уровня СТ1 поступает на вход RC-цепи 13 и далее на вход триггера Шмитта 14, на выходе которого формируется сигнал высокого уровня, который поступает на R-входы СТ1, ССК2 и на второй вход элемента И8. На выходах СТ1 и ССК2 появится сигнал низкого уровня, который, поступая на входы элементов И9 и 10, запрещает формирование сигнала открывания замка и счетного импульса СНК3. Элемент И9 вследствие того, что на его входах присутствует уровень логической единицы, формирует сигнал сброса СНК3, на прямом выходе которого появляется сигнал низкого уровня, поступающий на вход управления МХ5 и второй вход элемента И11. На инверсном выходе СНК3 появляется уровень логической единицы, разрешающий формирование элементами И9 и И10 счетного импульса СНК3 и сигнала открывания замка соответственно.

Выходной сигнал низкого уровня СТ1 также поступает на вход RC-цепи 13 и далее на вход триггера Шмитта 14, который на выходе установит сигнал низкого уровня, по фронту которого RS-триггер 6 установится в состояние логического нуля, и на его выходе появится сигнал низкого уровня, запрещающий формирование элементом И8 сигнала сброса СНК3.

Следовательно, в случае блокировки СНК3 только при входном коде, соответствующем эталонному коду разблокировки, СНК3 обнуляется, и устройство управления электронного замка приводится в исходное состояние. Дальнейший ввод кода, соответствующего эталонному значению кода открывания, приводит к формированию сигнала открывания замка.

Таким образом, устройство управления электронного замка формирует сигнал открывания только в случае приема кода, полностью соответствующего эталонному значению кода открывания. Ошибки в наборе входного кода, как и в прототипе, учитываются только после правильного набора определенного порогового количества разрядов, характеризующего допустимую степень приближения входного кода к эталонному значению. Однако в отличие от прототипа в заявленном устройстве при определении степени приближения анализируется состояние всех разрядов входного кода, а не только его части, что позволяет перекрыть все возможные пути приближения входного кода к эталонному значению, количество которых можно определить как число сочетаний С из N по n, где N - количество разрядов входного кода, а n - пороговое количество разрядов, состояние которых совпали с эталонными значениями (М.Я.Выгодский. Справочник по элементарной математике. - М.: Наука, 1976 г., с 200).

.

.

При N=16 и фактическом количестве разрядов, состояние которых совпало с эталонным значением, равным пороговому значению n=8,

.

.

В заявленном устройстве при анализе учитывается все указанное количество входных кодов, соответствующих пороговому количеству совпадений разрядов, а в прототипе - только один код.

Тем самым в заявленном устройстве обеспечивается уменьшение вероятности открывания замка путем подбора кода при сохранении защищенности от целенаправленной быстрой блокировки.

Изготовлен лабораторный макет устройства управления электронного замка, испытания которого подтвердили работоспособность и практическую ценность заявляемого объекта.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2006 |

|

RU2345203C2 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2015 |

|

RU2582450C1 |

| ЭЛЕКТРОННЫЙ КОДОВЫЙ ЗАМОК | 2015 |

|

RU2582451C1 |

| УСТРОЙСТВО КОНТРОЛЯ СОСТОЯНИЙ ПЕРЕГОННЫХ РЕЛЬСОВЫХ ЛИНИЙ | 2020 |

|

RU2746536C1 |

| ЭЛЕКТРОННО-МЕХАНИЧЕСКИЙ ЗАМОК | 2001 |

|

RU2224075C2 |

| СДВИГАЮЩИЙ РЕГИСТР | 2014 |

|

RU2566946C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМИ ЗАМКАМИ | 2001 |

|

RU2198276C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| ЭЛЕКТРОННО-МЕХАНИЧЕСКИЙ ЗАМОК | 2003 |

|

RU2246601C2 |

| ЭЛЕКТРОННО-МЕХАНИЧЕСКИЙ ЗАМОК | 2002 |

|

RU2221125C1 |

Изобретение относится к технике защиты различных объектов от доступа посторонних лиц, в частности к электронным кодовым замкам. Устройство управления электронного замка содержит счетчик 1 тактов (СТ), счетчик 2 совпадений кодов (ССК), счетчик 3 несовпадений кодов (СНК), постоянное запоминающее устройство (ПЗУ) 4, мультиплексор 5 (MX), RS-триггер 6, элемент "Исключающее ИЛИ" 7 (ИИ), первый 8, второй 9, третий 10, четвертый И и пятый 12 элементы И, интегрирующую RC-цепь 13, триггер Шмитта 14, информационную 15 и тактовую 16 шины, выходную шину 17. Счетный вход СТ1 соединен с тактовой шиной 16 и первым входом элемента И 12, R-вход СТ1 соединен с выходом триггера Шмитта 14, R-входом ССК2, R-входом RS-триггера 6 и вторым входом элемента И8. Выход СТ1 соединен с входом RC-цепи 13 и первыми входами элементов И9 и И10. Выходы разрядов СТ1 соединены с соответствующими адресными входами ПЗУ 4. Счетный вход ССК2 соединен с выходом элемента И 12. Выход А ССК2 соединен с инверсным третьим входом элемента И10, третьим входом элемента И9 и вторым входом элемента И11, выход Б ССК2 соединен с четвертым входом элемента И10, выход которого соединен со счетным входом СНКЗ, R-вход СНКЗ соединен с выходом элемента И8. Прямой выход СНКЗ соединен с управляющим входом МХ5 и первым входом элемента И11, инверсный выход СНКЗ соединен со вторыми входами элементов И9 и И10. Первый и второй выходы ПЗУ 4 соединены соответственно с первым и вторым входами МХ5, выход которого соединен со вторым входом элемента ИИ7. Выход элемента И11 соединен с S-входом RS-триггера 6, выход которого соединен с первым входом элемента И8. Информационная шина 15 соединена с первым входом элемента ИИ7, инверсный выход которого соединен со вторым входом элемента И12. Выход элемента И9 соединен с выходной шиной 17. Выход RC-цепи 13 соединен с входом триггера Шмитта 14. Изобретение позволяет повысить защищенность замка. 1 ил.

Устройство управления электронного замка, содержащее счетчик тактов, счетчик несовпадений кодов, постоянное запоминающее устройство, RS-триггер, триггер Шмитта, интегрирующую RC-цепь и пять элементов И, выход первого из которых соединен с R-входом счетчика несовпадений кодов, выход второго элемента И соединен с выходной шиной, а первый и второй входы соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен со счетным входом счетчика несовпадений кодов, выход RC-цепи соединен с входом триггера Шмитта, выход которого соединен с R-входом счетчика тактов, счетный вход которого соединен с тактовой шиной устройства, отличающееся тем, что в него введены счетчик совпадений кодов, мультиплексор и элемент Исключающее ИЛИ, первый и второй входы которого соединены соответственно с информационной шиной устройства и с выходом мультиплексора, первый и второй вход которого соединены соответственно с первым и вторым выходами постоянного запоминающего устройства, адресные входы которого подключены к выходам соответствующих разрядов счетчика тактов, выход которого соединен с входом интегрирующей RC-цепи и первым входом второго элемента И, второй вход которого соединен с инверсным выходом счетчика несовпадений кодов, прямой выход которого соединен с управляющим входом мультиплексора и первым входом четвертого элемента И, второй вход которого соединен с третьим входом второго элемента И, третьим инверсным входом третьего элемента И и выходом А счетчика совпадений кодов, выход Б которого соединен с четвертым входом третьего элемента И, выход четвертого элемента И соединен с S-входом RS-триггера, выход которого соединен с первым входом первого элемента И, второй вход которого соединен с выходом триггера Шмитта, R-входом RS-триггера и R-входом счетчика совпадений кодов, С-вход которого соединен с выходом пятого элемента И, первый вход которого соединен с тактовой шиной, а второй вход - с инверсным выходом элемента Исключающее ИЛИ.

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2239037C1 |

| Устройство управления кодовым замком | 1989 |

|

SU1663165A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| КОДОВОЕ УСТРОЙСТВО | 1992 |

|

RU2015282C1 |

| СПОСОБ МАГНИТНОЙ ОБРАБОТКИ ЖИДКОСТЕЙ | 1997 |

|

RU2118614C1 |

| WO 8904904 А1, 01.06.1989. | |||

Авторы

Даты

2009-01-27—Публикация

2006-08-15—Подача