Изобретение относится к области вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны сумматоры накапливающего типа, см., например, книгу М.А. Карцева, Арифметика цифровых машин, М., Наука 1969, стр. 247-252, а также Накапливающий сумматор по а.с. №1418701. Недостатками противопоставляемых устройств является наличие в каждом разряде трех RS-триггеров и выполнение только одной операции - сложения (вычитания).

Наиболее близким аналогом, принятым за прототип, является Накапливающий сумматор по а.с. №1291968. Прототип выполнен на основе трех логических элементов И, ИЛИ, НЕ и содержит только один RS-триггер в каждом разряде. Недостатком прототипа является ограниченный перечень выполняемых операций, что не позволяет его использовать при выполнении операций умножения (деления) и основных логических операций.

Задачей изобретения является устранение указанных недостатков известных сумматоров.

Для этого предложен объект, содержащий в каждом разряде один RS-триггер, восемь элементов И, семь элементов ИЛИ, три элемента НЕ и девять шин управления, причем вход и выход первого элемента НЕ i-го разряда соединены первыми входами восьмого и седьмого элементов И i-1-го разряда соответственно, вторые входы упомянутых элементов И подключены к четвертой шине, выходы седьмого и восьмого элементов И соединены с первыми входами пятого и шестого элементов И, при этом выход первого элемента ИЛИ подключен к вторым входам пятого и шестого элементов ИЛИ, выходы которых связаны с вторыми входами третьего и четвертого элементов И.

В устройство введены пятая, шестая, седьмая и восьмая шина управления, при этом в каждом разряде пятая шина подключена к третьему входу пятого элемента И, шестая шина подключена к третьему входу второго элемента ИЛИ, седьмая и восьмая шины соединены с третьими входами пятого и шестого элементов ИЛИ. В каждый разряд устройства введен третий элемент НЕ, при этом вход упомянутого элемента соединен с выходом третьего элемента И, а его выход подключен к нулевому входу первого триггера. Кроме того, выход второго элемента НЕ соединен с «единичным» входом триггера.

Отметим основные отличительные признаки объекта и покажем, что позволяет получить каждый из признаков.

1. Введенные в состав оборудования пятый и шестой элементы ИЛИ, седьмой и восьмой элементы И, четвертая шина управления и соответствующие связи обеспечивают выполнение операции сдвиг кода вправо.

2. Введение пятой, шестой, седьмой и восьмой шин управления с подключением этих шин к соответствующим логическим элементам позволяют обеспечить выполнение элементарных операций (ЭО) логического сложения, логического умножения, установки триггера в «нуль», прием в триггер кода «единицы», а также инвертирования и сдвига кода влево.

3. Введение третьего элемента НЕ и соединение его выходов с нулевым входом первого триггера, а также подключение выхода второго элемента НЕ к «единичному» входу триггера повышает надежность работы устройства, т.к. исключает возможные «гонки» сигналов на входах пятого логического элемента И.

Указанные отличия объекта от прототипа и других известных устройств расширяют перечень выполняемых операций (дополнительно выполняются операции сдвиг вправо, сдвиг влево, инвертирование, логическое сложение, логическое умножение, сложение по модулю два, прием кода «1»), повышают надежность работы и снижают потребление электроэнергии объекта. Указанные отличия объекта обеспечиваются при минимальных затратах оборудования. Например, операции логического сложения и умножения выполняются только за счет увеличения входов логических элементов в каждом разряде на один вход. В известных устройствах для выполнения этих операций требуется по три входа на каждую операцию и каждый двоичный разряд. Операция сдвига кода влево не требует дополнительного оборудования. Снижение числа триггеров в каждом разряде с трех единиц до двух позволяет снизить потреблении электроэнергии, несколько повысить быстродействие за счет исключения времени приема информации в триггер второго слагаемого и уменьшить суммарное число входов логических элементов, на основе которых построен объект, т.е. снизить потребное оборудование.

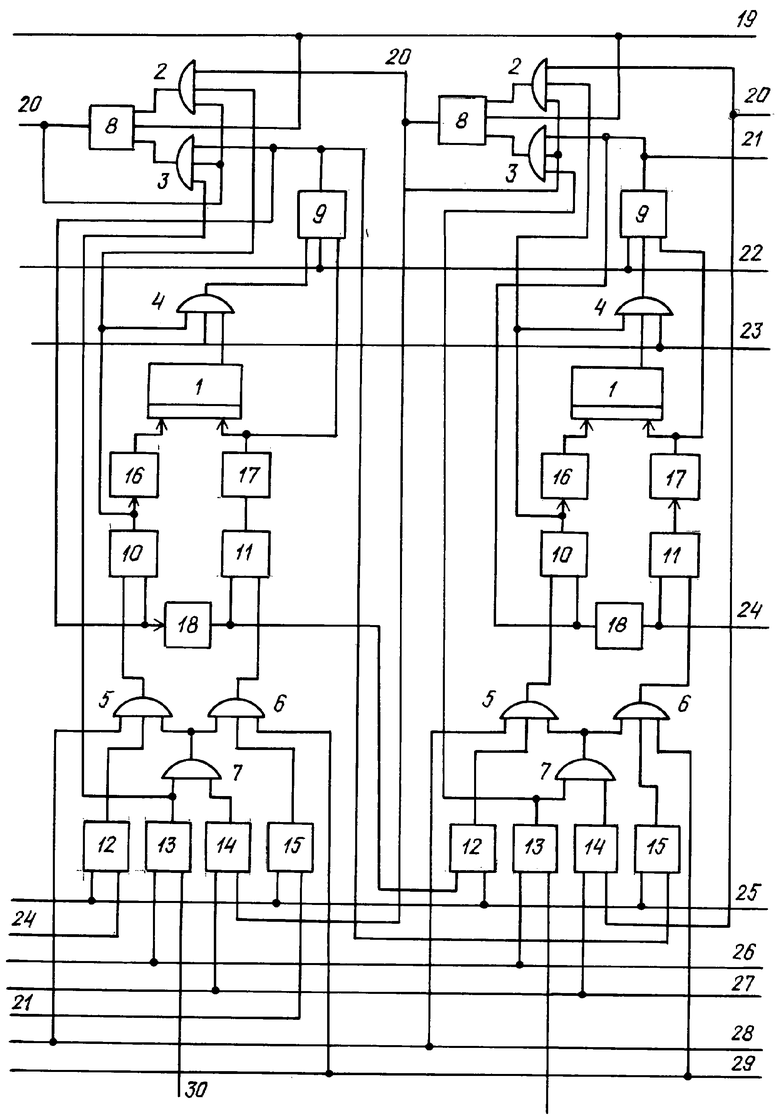

Для пояснения работы описываемого объекта на чертеже приведена функциональная схема двух разрядов сумматора. Каждый разряд объекта содержит RS-триггер 1, элементы ИЛИ2-7, элементы И8-15, элементы НЕ16-18, вход гашения переносов 19, вход переноса из младшего разряда 20, "единичный" выход триггера 21, вход управления операцией логического сложения 22, вход управления операцией логического умножения 23, "нулевой" выход триггера 24, вход управления сдвигом вправо 25, вход 26 управления выполнением первого сложения по модулю два, вход 27 управления вторым сложением по модулю два, вход 28 установки "нуля" триггера, вход 29 установки "единицы" триггера, вход 30 приема информации в рассматриваемый разряд.

Рассмотрим работу объекта при выполнении арифметических (сложение, вычитание) и логических операций. 1. Операция сложения

Операция выполняется за четыре временных такта - t1,2,3,4 (под тактом будем понимать исполнительный импульс с длительностью tИ). Будем считать, что код первого слагаемого (Ai) хранится в триггерах 1 как результат выполнения предыдущей операции, а код второго слагаемого поступает по входу 30.

По t1 выполняется одновременно ЭО приема второго слагаемого (Bi), первое сложение по модулю два, формирование и "запоминание" возможных потенциалов переносов в разрядах объекта. Для выполнения этих ЭО на входы 19 и 26 подаются высокие потенциалы, причем на входе 19 потенциал сохраняется в течение трех тактов t1,2,3, а на вход 26 подается импульс только по t1. Если на входе 30i-ого разряда присутствует высокий потенциал, соответствующий коду "единица", то исполнительный импульс проходит по цепи И13, ИЛИ7, ИЛИ6, И11, НЕ17 на "единичный" вход триггера 1, если до прихода импульса триггер хранил код "нуля". Если же в триггере хранился код "единицы", то исполнительный импульс проходит по цепи ИЛИ3, И10, НЕ16 на "нулевой" вход триггера. Другими словами, произойдет инвертирование значения кода триггера. Если на входе 30 нет высокого потенциала, то значение кода триггера 1 не меняется. Отметим важную особенность переключения RS-триггеров в предлагаемом объекте. Если триггер переключается из одного состояния в другое без существенной временной задержки по сравнению с длительностью исполнительного импульса, то "единичный"(выход 21) и "нулевой"(выход 24) выходы "задержаны" на время tи, равное длительности импульса, поступившего на вход 26 и выходы И10, И11. Эта задержка обеспечивается за счет выключения элемента И9, если триггер переключается из "нулевого" состояния в "единичное", и продолжения на время t1, включения элемента И9 за счет поступления исполнительного импульса через элемент ИЛИ4 на вход И9, если триггер переключается из состояния "единицы" в "нуль".

Одновременно с переключением триггера 1 формируется и "запоминается" потенциал переноса на элементах ИЛИ2, 3, И8. При переключении триггера из "единицы" в "нуль" исполнительный импульс с выхода И13 поступит на вход ИЛИ3, а с выхода элемента И10 поступит на вход ИЛИ2. На выходе элемента И8 будет выработан сигнал переноса в старший разряд. За счет связи с выхода И8 с входами ИЛИ2, 3 этот потенциал будет храниться в течение трех тактов (t1,2,3). При наличии кода "единицы" в i-м разряде и поступлении сигнала переноса из младшего (i-1-го) разряда в i-м разряде также будет выработан перенос в старший (i+1-й) разряд.

По t2 будет продолжаться распространение и "запоминание" сигналов переносов во всех разрядах объекта.

По t3, после завершения максимального времени распространения сквозного переноса выполняется ЭО второго сложения по модулю два. Для выполнения этой ЭО на вход 27 подается исполнительный импульс. Если в рассматриваемый разряд из младшего разряда по входу 20 поступил сигнал переноса, то исполнительный импульс по цепи И14, ИЛИ7, ИЛИ5, 6 поступит на входы И10, 11 и проинвертирует триггер 1. В случае отсутствия переноса из младшего разряда состояние триггера 1 не меняется. На этом операция сложения закончена. Результат суммирования будет занесен в триггеры 1, но для подготовки объекта к выполнению новых операций требуется устранить потенциалы переносов, хранящихся в цепи переносов.

По t4 выполняется гашение переносов во всех разрядах одновременно. Для этого с входа 19 снимается высокий потенциал, за счет чего выключается И8.

2. Операция вычитания положительных чисел выполняется аналогично выполнению сложения. Отличие состоит только в том, что на входы 30 поступает инверсный код второго слагаемого.

3. ЭО сдвига кода вправо выполняется за два временных такта на каждый двоичный разряд (t1,2).

По t1 на вход 25 подается импульс сдвига кода, хранящегося в триггерах 1, вправо. Если в i-м разряде до начала выполнения операции хранился код "единица", то высокий потенциал с единичного выхода триггера по цепи элементов ИЛИ4, И9 поступает на вход 21, И15, ИЛИ6, И11, НЕ17 младшего разряда и устанавливает триггер 1 в "единицу". Если в i-м разряде хранится код "нуля", то высокий потенциал с выхода НЕ 18 поступит на второй вход И12 и по цепи элементов ИЛИ5, И10, НЕ16 поступит на "нулевой" вход триггера 1. На этом операция сдвига кода на один разряд вправо закончена. Второй такт (t2) не используется. Для сдвига кода вправо еще на один разряд на выход 25 подается очередной исполнительный импульс (такт).

4. ЭО сдвига кода влево. Операция выполняется за три временных такта. По t1 на вход 19 подается высокий потенциал операции, который сохраняется в течение первого и второго тактов, одновременно на вход 28 всех разрядов подается импульс установки "нуля" триггеров 1. Этот импульс по цепи элементов ИЛИ5, И10, НЕ16 установит триггер 1 в "нуль" и по цепи ИЛИ2 поступит на первый вход И8. Так как на второй вход И8 поступает высокий потенциал с входа 19, а на третий вход упомянутого элемента И поступает высокий потенциал с "единичного" выхода триггера 1 по цепи элементов ИЛИ4, И9, то на выходе И8 будет выработан высокий потенциал, который будет "запомнен" на элементах И8, И2,3 и передан на вход 20 старшего разряда. Если в триггере 1 до прихода импульса хранился код "нуля", то выработка и запоминание переноса не произойдет.

По t2 на вход 27 подается исполнительный импульс выполнения ЭО второго сложения по модулю два. Если в i-й разряд из i-1-го разряда по входу 20 поступает потенциал переноса, то исполнительный импульс по цепи И14, ИЛИ7, ИЛИ6, И11, НЕ17 поступит на "единичный" вход триггера 1 и установит его в "единицу". По t3 выполняется ЭО гашения переносов. Для чего с входа 19 снимается высокий потенциал. На этом выполнение ЭО сдвига кода влево на один разряд закончено (заметим, что для выполнения операции не требуется дополнительного оборудования).

5. ЭО инвертирования кода. Операция выполняется за два временных такта.

По t1 на входы 28 и 29 одновременно поступают исполнительные импульсы, которые по цепи ИЛИ5, 6 поступают на первые входы И10, 11. Если в триггере 1 до поступления импульсов инвертирования хранился код "единицы", то по цепи И10, НЕ16 импульс поступит на "нулевой" вход триггера и установит его в "нуль". Если же в триггере хранился код "нуля", то импульс по цепи И11, НЕ17 поступит на "единичный" вход и установит триггер в "единицу", т.е. произойдет инвертирование значения кода триггера. Второй временной такт используется для подготовки объекта к выполнению любой другой операции.

6. Операция логического сложения.

Операция выполняется за два временных такта. По t1 c входа 22 снимается высокий потенциал, что приводит к появлению высокого потенциала на выходе НЕ18 во всех разрядах одновременно. Одновременно на выход 26 поступает исполнительный импульс. Если в i-м разряде код второго слагаемого "единица", то исполнительный импульс по цепи элементов И13, ИЛИ7, 6, И11, НЕ17 поступает на единичный вход триггера 1. Второй такт используется для подготовки объекта к выполнению любой другой операции. (Заметим, что для выполнения ЭО логического сложения требуется увеличить оборудование всего на один вход элемента И на каждый двоичный разряд. В известных устройствах для выполнения этой операции требуется три входа на логические элементы в каждом разряде).

7. Операция логического умножения.

Операция выполняется за два временных такта. По t1 на входы 23 всех разрядов объекта подается высокий потенциал. Этот потенциал по цепи ИЛИ4, И9 поступает на первый вход И10. Одновременно по входам 30 поступает обратный код второго слагаемого, а на вход 26 подается исполнительный импульс. Если в i-м разряде инверсный код второго сомножителя равен "единице", то исполнительный импульс по цепи элементов ИЛИ7, 5, И10, НЕ16 поступит на "нулевой" вход триггера 1 и установит его в "нуль". Операция логического умножения двух кодов выполнена. Время второго такта используется для подготовки объекта к выполнению других операций. (Для выполнения ЭО требуется увеличить оборудование на один вход элемента ИЛИ. В известных устройствах требуется три входа).

8. ЭО приема кода "единицы".

Операция выполняется за два временных такта. По t1 на вход 29 поступает исполнительный импульс, который по цепи ИЛИ6, И11, НЕ17 поступает на "единичный" вход триггера 1 и устанавливает его в "единицу". Время второго такта используется для подготовки объекта к выполнению других операций.

9. Операции сложения кодов по модулю два и гашение переносов рассмотрены при выполнении операции сложения. Для выполнения этих ЭО не требуется дополнительного оборудования, кроме одного входа логического элемента И.

Таким образом, предлагаемый объект позволяет расширить перечень выполняемых операций по сравнению с прототипом в три раза при минимальных затратах оборудования.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР КОМБИНАЦИОННОГО ТИПА | 2004 |

|

RU2275676C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ АРИФМЕТИЧЕСКИХ И ЛОГИЧЕСКИХ ОПЕРАЦИЙ | 2005 |

|

RU2295751C2 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 2005 |

|

RU2288501C1 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

| СПОСОБ И УСТРОЙСТВО СУММИРОВАНИЯ | 2005 |

|

RU2308073C2 |

| СЧЕТЧИК ИМПУЛЬСОВ (СИ) | 2015 |

|

RU2579524C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| СПОСОБ И УСТРОЙСТВО ВЫПОЛНЕНИЯ ВЫЧИСЛИТЕЛЬНЫХ ОПЕРАЦИЙ ПРИ МИНИМАЛЬНЫХ ЗАТРАТАХ ОБОРУДОВАНИЯ | 2005 |

|

RU2287849C1 |

Изобретение относится к области вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является расширение перечня выполняемых операций, при минимальных затратах оборудования. Устройство содержит в каждом разряде восемь элементов И, шесть элементов ИЛИ, три элемента НЕ и восемь шин управления, один RS-триггер. 1 з.п. ф-лы, 1 ил.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Накапливающий сумматор | 1987 |

|

SU1418701A1 |

| US 5691931 A, 25.11.1995 | |||

| 1972 |

|

SU416869A1 | |

Авторы

Даты

2005-10-20—Публикация

2004-03-05—Подача