Изобретение относится к устройствам демодуляции частотно-модулированных сигналов путем подсчета или интегрирования периодов колебаний.

Известен импульсный детектор аналогового частотно-модулированного сигнала [Г.В.Горелов, А.А.Волков, В.И.Шелухин. Каналообразующие устройства железнодорожной телемеханики и связи. Учеб. для вузов ж.д. транспорта. - М.: Транспорт, 1997. - С.148-151], включающий ограничитель амплитуды, дифференцирующую цепь, двухполупериодный выпрямитель, одновибратор и демодулятор.

Недостатком данного устройства является то, что он обладает низкой помехоустойчивостью, из-за которой понижается разборчивость речи, потому что часть помех проникает в выходной сигнал низкой частоты.

Известен также импульсный частотно-фазовый детектор (Заявка РФ №2003108225, МПК 7 H03D 13/00) - прототип, включающий триггеры, логический элемент ИЛИ, логический элемент И и интегратор.

Недостатком данного устройства является низкая помехоустойчивость, из-за которой понижается разборчивость речи, потому что часть помех проникает в выходной сигнал низкой частоты.

Целью изобретения является повышение помехоустойчивости и разборчивости речи.

Указанная цель достигнута тем, что в предлагаемом устройстве импульсы, поступающие с ограничителя амплитуды, объединяют в один импульс, длительность которого прямо пропорциональна частоте частотно-модулированного сигнала.

Сущность изобретения заключается в том, что первый вход логического элемента И соединен с выходом дополнительно включенного в схему ограничителя амплитуды, а к выходу логического элемента И дополнительно присоединен счетчик, первый и последний выходы которого соединены со входами триггера, к прямому выходу которого последовательно подключены два последовательно соединенные друг с другом интегратора, выполненных на операционных усилителях, при этом в цепь обратной связи первого интегратора включен диод, а к инверсному выходу триггера подключен элемент времени, выход которого соединен со вторым входом логического элемента И.

На фиг.1 представлена схема помехоустойчивого импульсного детектора частотно-модулированных сигналов, состоящего из ограничителя амплитуды 1, выход которого соединен с первым входом логического элемента 2, к выходу которого подключен счетчик 3, первый 4 и последний 5 выходы которого соединены со входами триггера 6. К прямому выходу 7 триггера 6 последовательно подключены два интегратора 14 и 17, собранных на операционных усилителях 11 и 16, в цепь обратной связи первого интегратора 14 включен диод 13. К инверсному выходу 8 триггера 6 подключен элемент времени 9, выход соединен с вторым входом логического элемента 2.

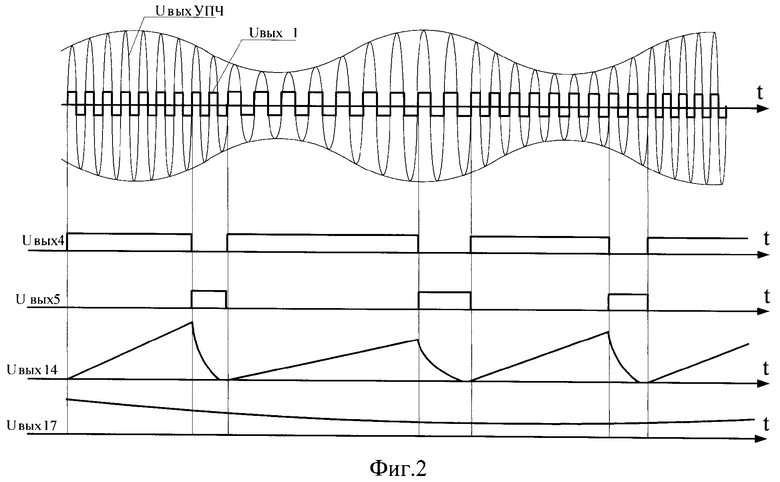

На фиг.2 представлена диаграмма преобразования сигнала при прохождении его через детектор частотно-модулированных сигналов с графиками зависимости сигнала от времени: UвыхУПЧ - с выхода усилителя промежуточной частоты УПЧ (на чертеже не представлен), Uвых1 - с выхода ограничителя амплитуды 1, Uвых7 - напряжения на прямом выходе триггера 6, Uвых8 - напряжения на инверсном выходе триггера 6, Uвых14 и Uвых17 - напряжения на выходах интеграторов 14 и 17.

Предлагаемое устройство работает следующим образом.

На ограничитель амплитуды 1 с усилителя промежуточной частоты УПЧ (на чертеже не представлен) поступает сигнал, искаженный паразитной амплитудной модуляцией UвыхУПЧ. Ограничитель амплитуды 1 превращает частотно-модулированный сигнал в последовательность прямоугольных разнополярных импульсов Uвых1 с частотой повторения, равной частоте частотно-модулированного сигнала.

Эти импульсы Uвых1 проходят через логический элемент 2 на вход счетчика 3, который настроен на заданное число импульсов N. При появлении единицы на выходе логического элемента 2 счетчик 3 начинает считать импульсы.

На выходах счетчика 3 последовательно появляются единичные сигналы. Первым единичным сигналом включается триггер 6, на его прямом выходе 7 появляется единица, начинает формироваться прямоугольный импульс Uвых7, который объединяет импульсы, поступающие на вход счетчика 3, в один импульс, длительность которого прямо пропорциональна частоте частотно-модулированного сигнала. Когда счетчик 3 досчитывает до заданного числа N, на его последнем выходе 5 появляется единица, по этому сигналу опрокидывается триггер 6, следовательно, на его инверсном выходе 8 появится единица Uвых8, а на прямом выходе 7 - ноль Uвых7.

С появлением единицы на инверсном выходе 8 триггера 6, она поступает на вход элемента времени 9. В течение фиксированного промежутка времени, равного, например, трем периодам частотно-модулированного сигнала, на выходе элемента времени 9 формируется нулевой сигнал, который поступает на второй вход логического элемента 2. На это же время прекращается поступление импульсов на вход счетчика 3.

При установлении нулевого сигнала на входе элемента времени 9 снова появляется единица на его выходе, и счетчик 3 возобновляет подсчет импульсов, то есть начинается формирование нового импульса.

К прямому выходу 7 триггера 6 последовательно подключены два интегратора 14 и 17, собранные на операционных усилителях 11 и 16. Интегратор 14 формирует пилообразное напряжение Uвых14, а диод 13, включенный в цепь обратной связи его, служит для того, чтобы при поступлении нуля с выхода 7 триггера 6 напряжение на выходе первого интегратора 14 резко падало до нуля. Второй интегратор 17 из пилообразного напряжения Uвых14, поступающего на его вход с выхода первого интегратора 14, формирует низкочастотный сигнал Uвых17, который поступает на усилитель низкой частоты УНЧ (на чертеже не представлен).

Таким образом, применение предлагаемого устройства позволяет повысить помехоустойчивость за счет объединения заданного числа импульсов N, поступающих на вход счетчика 3, в один импульс, длительность которого прямо пропорциональна частоте частотно-модулированного сигнала, при этом исключается возможность проникновения помехи в каждый импульс, сформированный на выходе 7 триггера 6, так как после срабатывания триггера 6 помехи перестают оказывать влияние на сигнал. За счет уменьшения уровня помех на выходе предлагаемого помехоустойчивого импульсного детектора частотно-модулированных сигналов повышается разборчивости речи.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2005 |

|

RU2288539C1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 2004 |

|

RU2262802C1 |

| Дискретный частотный демодулятор | 1981 |

|

SU987788A2 |

| Частотный дискриминатор | 1978 |

|

SU766035A1 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| РАДИОЛОКАЦИОННОЕ УСТРОЙСТВО ФИКСАЦИИ ДАЛЬНОСТИ С ЧАСТОТНОЙ МОДУЛЯЦИЕЙ | 2008 |

|

RU2379701C1 |

| УСТРОЙСТВО ДЛЯ ЗАДАНИЯ ПРОГРАММЫ ТЕРМОЦИКЛИЧЕСКИХ СТЕНДОВЫХ ИСПЫТАНИЙ ДИСКОВ ТУРБОАГРЕГАТОВ | 1989 |

|

SU1603953A1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2006 |

|

RU2320071C1 |

| Устройство для измерения средней мощности сигналов в каналах и трактах систем связи | 1983 |

|

SU1095083A1 |

| Измерительный преобразователь неэлектрических величин с емкостным датчиком | 1990 |

|

SU1795381A1 |

Изобретение относится к устройствам демодуляции частотно-модулированных сигналов путем подсчета или интегрирования периодов колебаний. Техническим результатом является повышение помехоустойчивости и разборчивости речи. В предлагаемом устройстве импульсы, поступающие с ограничителя амплитуды (ОА) (1), объединяют в один импульс, длительность которого прямо пропорциональна частоте частотно-модулированного сигнала. Сущность изобретения заключается в том, что первый вход логического элемента (ЛЭ) И (2) соединен с выходом дополнительно включенного в схему ОА (1), а к выходу ЛЭ И (2) дополнительно присоединен счетчик (СЧ) (3), первый и последний выходы которого соединены со входами триггера (Т) (6), к прямому выходу которого последовательно подключены два последовательно соединенные друг с другом интегратора (14, 17), выполненных на операционных усилителях (11, 16), при этом в цепь обратной связи первого интегратора (14) включен диод (13), а к инверсному выходу Т (6) подключен элемент времени (9), выход которого соединен со вторым входом ЛЭ И (2). Таким образом, повышение помехоустойчивости достигается за счет объединения заданного числа импульсов N, поступающих на вход СЧ (3), в один импульс, длительность которого прямо пропорциональна частоте частотно-модулированного сигнала, при этом исключается возможность проникновения помехи в каждый импульс, сформированный на выходе (7) Т (6), так как после срабатывания Т (6) помехи перестают оказывать влияние на сигнал. За счет уменьшения уровня помех повышается разборчивость речи. 2 ил.

Помехоустойчивый импульсный детектор частотно-модулированных сигналов, содержащий логический элемент И, логический элемент ИЛИ, триггеры и интегратор, отличающийся тем, что первый вход логического элемента И соединен с выходом дополнительно включенного в схему ограничителя амплитуды, а к выходу логического элемента И дополнительно присоединен счетчик, первый и последний выходы которого соединены со входами триггера, к прямому выходу которого последовательно подключены два последовательно соединенные друг с другом интегратора, выполненных на операционных усилителях, при этом в цепь обратной связи первого интегратора включен диод, а к инверсному выходу триггера подключен элемент времени, выход которого соединен со вторым входом логического элемента И.

| RU 2003108225 А, 10.10.2004 | |||

| Устройство для демодуляции частотно-модулированных сигналов при низком отношении несущей частоты к частоте модуляции | 1983 |

|

SU1138956A1 |

| Пломбировальные щипцы | 1923 |

|

SU2006A1 |

| US 4286223, 25.08.1981 | |||

| US 4084127, 11.04.1978. | |||

Авторы

Даты

2009-03-27—Публикация

2007-05-10—Подача