Изобретение относится к эпектросвязи и может испотьаоваться в устройствах преобразования сигналов аппаратуры передачи данных и устройствах измерения частоты и временных интервалов. Известен частотный дискриминатор, содержащий входной усилитепь-ограничитель, противофазные выходы которого соединены с входами первого и второго дифференцирующих блоков, и два элемеН та И, выходы которых через интегратор соединены с выходным пороговым блоком а входы - перекрестно подключены к прямым и инверсным выходам триггеров, к nepBbnvi входам которых подключен выход генератора тактовой частоты через первый и второй делители частоты, управ ляющий вход каждого из которых соединен с инверсным выходом соответствующего триггера . Однако известный дискриминатор имеет невысокую помехозащищенность. Цель изобретения - повышение пом&хозащищенности. Для этого в частотный дискриминатор, содержащий входной усилитель-ограничитель, противофазные выходы которого соединены с входами пе{жого и второго дифференцирующих блоков, и два i элемента И, выходы которых через интегратор соединены с выходным inoporoвым блоком, а входы-перекрестно подключены к прямым и шгоерсньтм выходам триггеров, к первым входам которых подключен выход генератора тактовой частоты через первый и второй делители частоты, управляющий вход каждого из которых соединен с инверсным выходом соответствующего триг гера, введены два элемента И-НЕ и . два элемента запрета, при этом выход первого дифференцирующего блока через первый элемент запрета соединен с вторым входом первого триггера, а выход второго дифференцирующего блока через второй элемент запрета соединен с вторым входом второго триггера, управлякнщий вход первого элемента запрета

3.76

соединен с выкодом второго эпемента И-НЕ, к одному из входов которого подключен дополнитеттьный выход второго депитепя частоты, а к другому входу подключен прямой выход второго тригг&ра, управляющий вход второго элемента запрета соединен с выходом первого элемента И-НЕ, к одному из входов которого подключен дополнительный выход первого делителя частоты, а к другому входу подключен прямой выход перво го триггера.

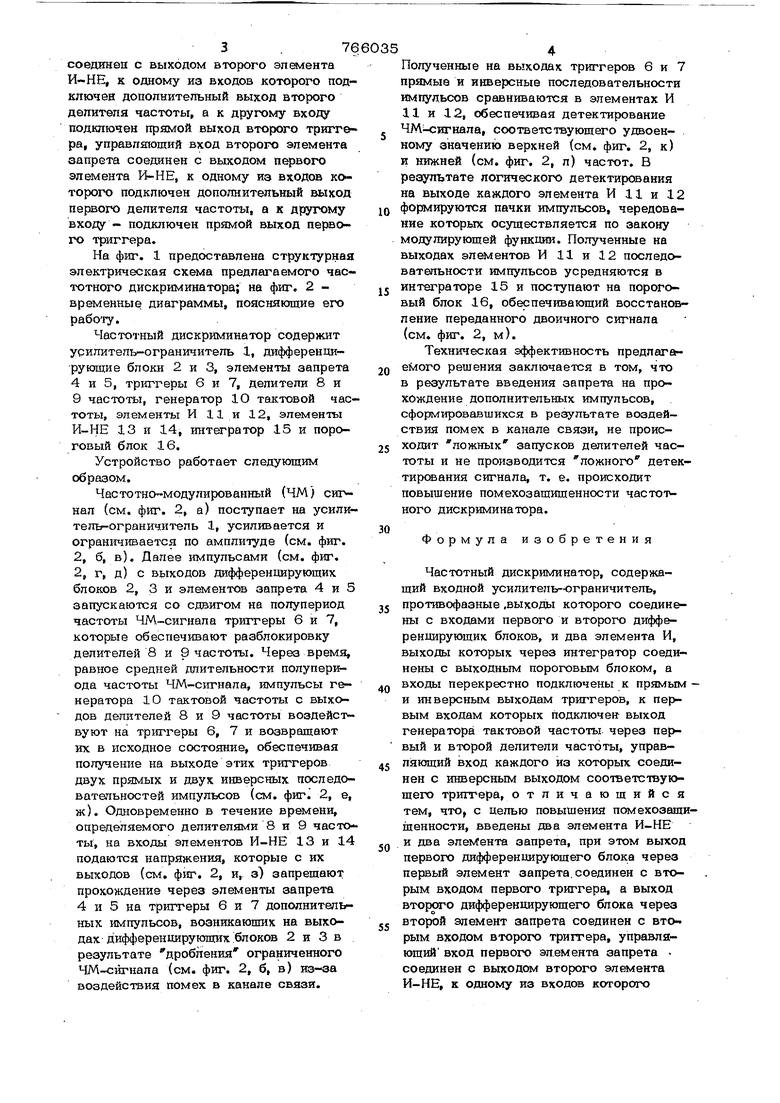

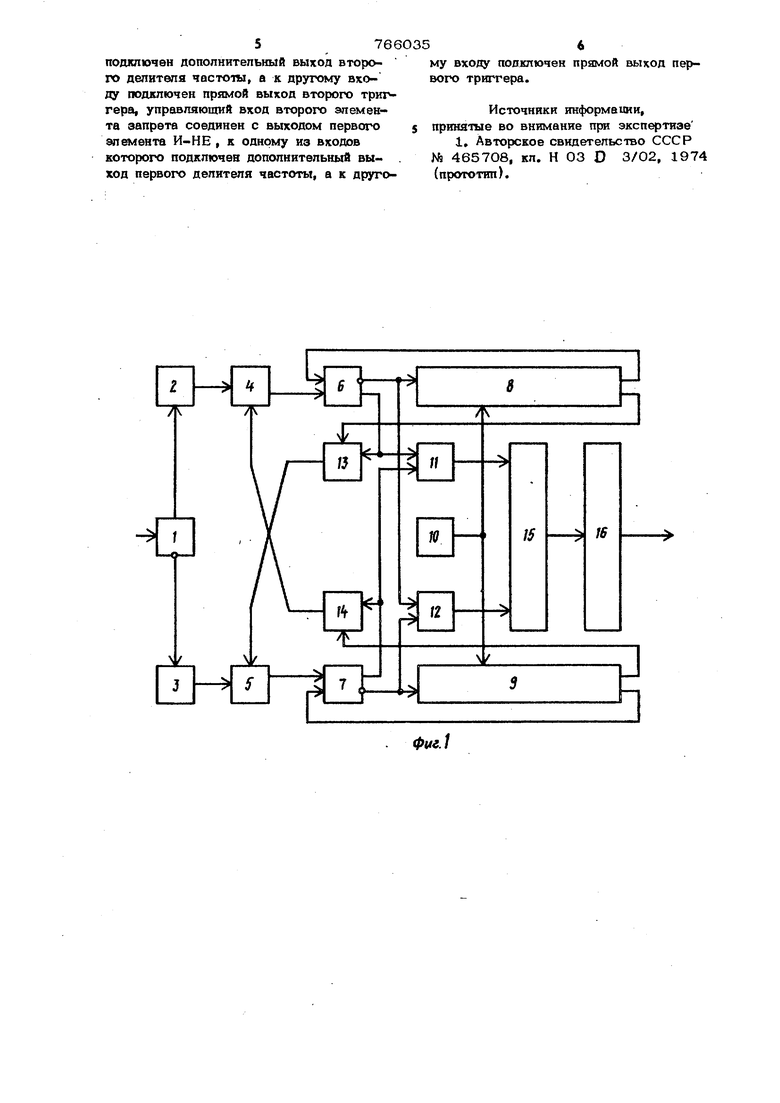

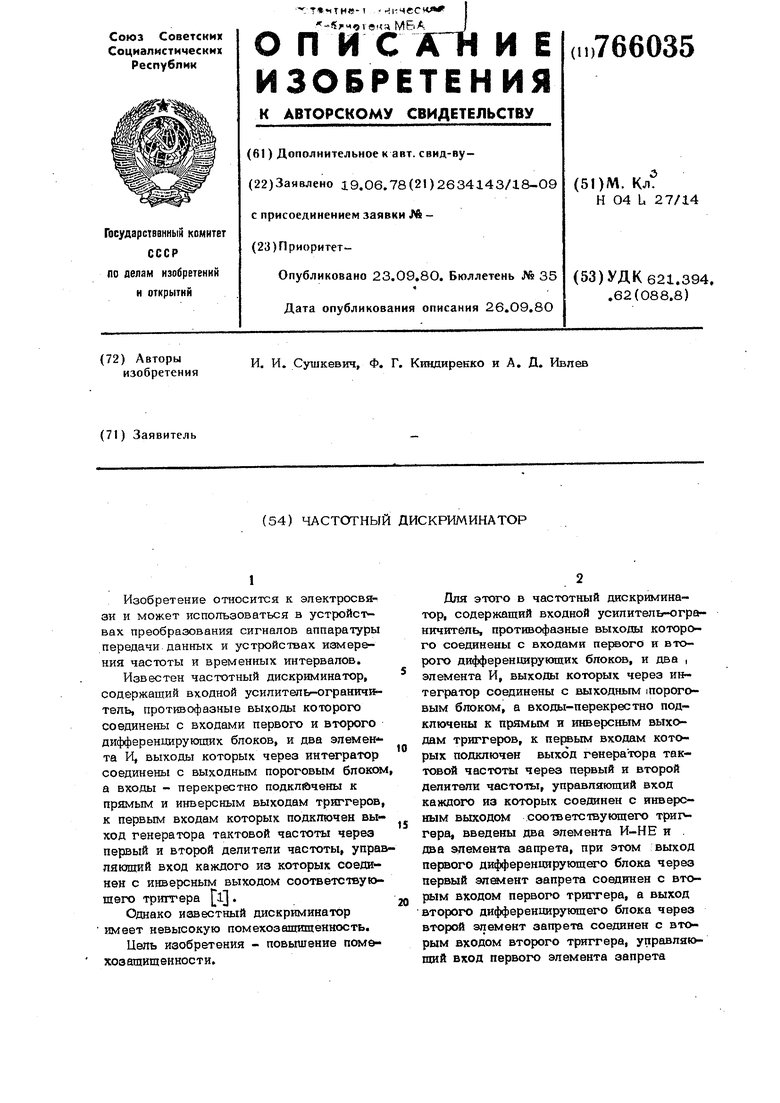

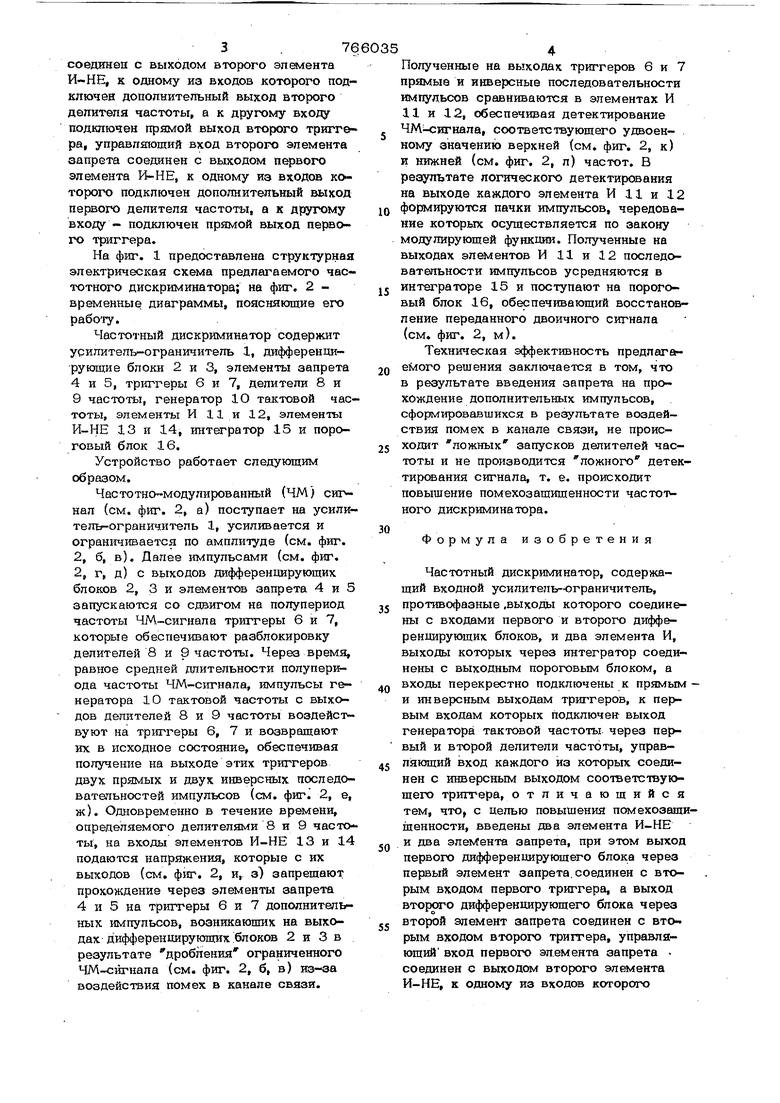

На фиг. 1 предоставлена структурная электрическая схема предлагаемого частотного дискриминатора; на фиг. 2 временные диаграммы, поясняющие его рабогу.

Частотный дискриминатор содержит усилитель-ограничитель 1, дифференцирующие блоки 2 и 3, элементы запрета 4 и 5, триггеры 6 и 7, делители 8 и 9 частоты, генератор Ю тактовой частоты, элементы И 11 и 12, элементы И-НЕ 13 и 14, тгатегратор 15 и пороговый блок 16.

Устройство работает следующим образом.

Частотно-модулированный (ЧМ) (см. фиг. 2, а) поступает на усилитель-ограничитель 1, усиливается и ограничивается по амплитуде (см. фиг. 2, б, в). Далее импульсами (см. фиг. 2, г, д) с вьгходов дифференцирующих блоков 2, 3 и элементов запрета 4 и 5 запускаются со сдвигом на поттупериод частоты ЧМ сигнала триггеры 6 и 7, которые обеспечивают разблокировку делителей 8 и 9 частоты. Через время, равное средней длительности полупериода частоты ЧМ-сигнала, импульсы г нератора Ю тактовой частоты с выходов делителей 8 и 9 частоты воздействуют на тргст геры 6, 7 и возвращают их в исходное состояние, обеспечивая получение на выходе этих триггеров двух прямых и двух инверсных последовательностей импульсов (см. фиг. 2, е, ж). Одновременно в течение времени, определяемого делителями 8 и 9 частоты, на входы элементов И-НЕ 13 и 14 подаются напряжения, которые с их выходов (см. фиг. 2, и, з) запрещают прохождение через элементы запрета 4 и 5 на триггеры 6 и 7 дополнител1 ных импульсов, возникающих на выходах дифференцирующих блоков 2 и 3 в результате дробления ограниченного ЧМ-сйгнала (см. фиг. 2, б, в) из-за воздействия помех в канале связи.

Полученные на выходах триггеров 6 и 7 прямые и инверсные последовательности импульсов сравниваются в элементах И 11 и 12, обеспечивая детектирование ЧМ-сигнала, соответствующего удвоенному значению верхней (см. фиг. 2, к) и нижней (см. фиг. 2, л) частот. В ре шьтате логического детектирования на выходе каждого элемента И 11 и 12 формируются пачки импульсов, чередование которых осуществляется по закону модулирующей функции. Полученные на выходах элементов И 11 и 12 последовательности импульсов усредняются в интеграторе 15 и поступают на пороговый блок 16, обеспечивающий восстановление переданного двоичного сигнала (см. фиг. 2, м).

Техническая эффективность предлагаемого решения заключается в том, что в результате введения запрета на прохождение дополнительных импульсов, сформировавшихся в результате воздействия помех в канале связи, не происходит ложных запусков делителей частоты и не производится ложного детектир жания сигнала, т. е. происходит повышение помехозащищенности частотного дискриминатора.

Формула изобретения

Частотный дискриминатор, содержащий входной усилитель-ограничитель, противофазные .выходы которого соединены с входами первого и второго дифференцирующих блоков, и два элемента И, выходы которых через интегратор соединены с ВЫХОДНЬПУ пороговым блоком, а входы перекрестно подключены к прямым и инверсным выходам триггеров, к первым входам которых подключен выход генератора тактовой частоты через и второй делители частоты, управляющий вход каждого из которых соединен с инверсным выходом соответствующего триггера, отличающийся тем, что с целью повышения помехозащщенности, введены два элемента И-НЕ и два элемента запрета, при этом выход первого дифференцирующего блока через первый элемент запрета, соединен с вторым входом первого триггера, а выход второго дифференцирующего блока через второй элемент запрета соединен с вторым входом второго триггера, управляющий вход первого элемента запрета соединен с выходом второго элемента И-НЕ, к одному из входов которого

подключен дополнительный выход второго делителя частоты, а к другому входу подключен npsiMoft выход второго триггера, управляющий вход второго элемента запрета соединен с выходом первого элемента И-НЕ , к одному из входов которого подключен дополнительный вы- . ход первого делителя частоты, а к другому входу подключен прямой выход первого триггера.

Источники информации, принятые во внимание прт экспертизе 1, Авторское свидетельство СССР N9 4657О8, кл. Н 03 О 3/02, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотный дискриминатор | 1979 |

|

SU836759A2 |

| Частотный дискриминатор | 1972 |

|

SU465708A1 |

| Устройство тактовой синхронизации | 1982 |

|

SU1104674A1 |

| Преобразователь электрического сигнала мостового датчика в частоту | 1982 |

|

SU1026301A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1099403A1 |

| Устройство для измерения параметров нелинейных элементов | 1980 |

|

SU924621A1 |

| Устройство для синхронного радиоприема частотноманипулированных сигналов | 1985 |

|

SU1275787A1 |

| УСТРОЙСТВО ПРИЕМА ДВОИЧНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 1972 |

|

SU433619A1 |

| УСТРОЙСТВО ДЛЯ ВЫДЕЛЕНИЯ ТАКТОВОГО СИНХРОСИГНАЛА ИЗ МНОГОУРОВНЕВОГО ЦИФРОВОГО СИГНАЛА | 1992 |

|

RU2033698C1 |

| Устройство тактовой синхронизации | 1981 |

|

SU1043832A1 |

Авторы

Даты

1980-09-23—Публикация

1978-06-19—Подача