Изобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания в формате разрешения НДТУ, Аналогами являются системы телевидения, претендующие на формат НДТУ [1, с.26-28]. Недостатками их являются недостаточная разрешающая способность и необходимость в широкополосных каналах для передачи сигналов. За прототип принята "Цифровая система телевидения высокой четкости" [2], содержащая на передающей стороне фотоэлектрический преобразователь /ФЭП/, формирующий три аналоговых цветовых сигнала R, G, В, три АЦП видеосигнала, задающий генератор и синтезатор частот, два АЦП сигнала звука, три формирователя кодов, два самоходных распределителя импульсов /СРИ/ и передатчик радиосигналов из трех каналов, использующий две несущие частоты, на приемной стороне содержащая блок управления, три тракта приема и обработки кодов, каждый из которых включает блок приема радиосигнала, усилитель радиочастоты, двухполярный амплитудный детектор и канал обработки кодов сигнала /R, G, В/, включающий первый и второй формирователи импульсов, два регистра, блок обработки кодов, первый блок задержек, сумматор и второй блок задержек, на приемной стороне шесть блоков импульсных усилителей, блок модуляции излучений, блоки строчной и кадровой разверток, два усилителя и два пьезодефлектора, матовый экран, канал формирования управляющих сигналов и два канала звукового сопровождения.

На передающей стороне кодируются сигналы R, G, В в 550-и строках кадра по 1000 отсчетов в строке. Частота кадров 25 Гц, каждый из двух полей. Информация передается тремя каналами, двумя несущими частотами. Приемная сторона принимает параллельно три радиосигнала тремя трактами, выделяет строчные и кадровые синхроимпульсы /ССИ и КСИ/, выполняет удвоение числа отсчетов в строке и удвоение числа строк в кадре. Видеорежим на приемной стороне 1100стр × 2000отс × 25 Гц. Изображение воспроизводится электронно-оптической разверткой /строчной и кадровой/ с проецированием кадра на матовый экран. Недостатки прототипа: передача информации по трем радиоканалам определяет высокую энергоемкость системы, сложность конструкции ФЭП, требующая прецизионной юстировки, недостаточная яркость изображения на матовом экране, не имеющем послесвечения. Цель изобретения - упрощение устройства фотоэлектрического преобразователя, снижение энергоемкости системы, увеличение яркости воспроизводимого изображения.

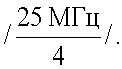

Техническими результатами являются: упрощение ФЭП исключением из него пьезодефлекторов, усилителей, источников опорных напряжений, блоков строчной и кадровой разверток и введением в него матрицы ПЗИ /прибора с зарядовой инжекцией по технологии ХЗ [3, с.552]/, снижение энергоемкости системы сокращением третьего канала радиопередачи и третьего тракта приема, увеличение яркости воспроизводимого изображения введением плоскопанельного светодиодного экрана /СД-экрана/. На передающей стороне применяется видеорежим 1000отсч × 1000строк × 25 Гц. Частота дискретизации при аналого-цифровом преобразовании: fАЦП=1000×25 Гц × 1000=25 МГц, где: 1000 - число кодируемых строк, 1000 - число отсчетов в строке, 25 Гц - частота кадров.

Частота отрок: 1000стр × 25 Гц=25 кГц.

Частота дискретизации после сжатия потока кодов кадра в 4 раза:  которая принимается при формировании кодов. Тактовая частота при формировании кодов в блоках формирования кодов:

которая принимается при формировании кодов. Тактовая частота при формировании кодов в блоках формирования кодов:

где: 4 - принимаемый коэффициент сжатия потока кодов в кадре,

9 - число разрядов в коде.

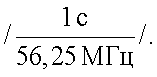

Период следования кодов при дискретизации 25 МГц 40 нс, при дискретизации fД2 6,25 МГц 160 нс

Несущая частота передатчика принимается fн=56,25 МГц × 15=843,75 МГц.

Верхняя боковая частота fв=843,75÷56,25=900 МГц,

нижняя боковая частота fниж=843,75-56,25=787,5 МГц.

На приемной стороне удваивается число отсчетов в строке, и воспроизводится видеорежим: 2000отс × 1000строк × 25 Гц. Разрешение кадра 2000×1000=2×106 пикселов.

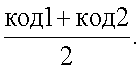

Сущность изобретения в том, что в систему телевидения, содержащую на передающей стороне ФЭП, три АЦП видеосигнала, синтезатор частот, два самоходных распределителя импульсов и передатчик радиосигналов, на приемной стороне тракты приема и обработки кодов видеосигналов, каждый из которых имеет один канал соответствующего цветового сигнала /R, G, В/, включающей устройство отображения видеоинформации и канал формирования управляющих сигналов, вводятся на передающей стороне два ключа, три кодера, в ФЭП вводится матрица ПЗИ и передатчик радиосигналов выполняется двухканальным, на приемной стороне в каждый канал цветового сигнала /R, G, В/ вводится декодер, накопитель кодов кадра и формирователь управляющих сигналов, и устройство отображения видеоинформации представляется плоскопанельным светодиодным экраном. Передающая сторона - на фиг.1, структура цифровых потоков кодов в эфире - на фиг.2, кодер - на фиг.3, диаграммы работы кодера - на фиг.4, первый формирователь кодов - на фиг.5, второй формирователь кодов - на фиг.6, приемная сторона - на фиг.7, двухполярный амплитудный детектор - на фиг.8, декодер - на фиг.9, блок обработки кодов - на фиг.10, накопитель кодов кадра - на фиг.11, блок регистров - на фиг.12, 13, формирователь управляющих сигналов - на фиг.14, СД-ячейка - на фиг.15, элемент матрицы - на фиг.16, расположение элементов матрицы в СД-экране - на фиг.17, блок выделения ССИ - на фиг.18, блок выделения КСИ - на фиг.19, спектры частот передатчика - на фиг.20, временные диаграммы работы системы - на фиг.21.

Передающая сторона включает /фиг.1/ фотоэлектрический преобразователь 1 /ФЭП/, являющийся датчиком трех основных цветов R, G, В и содержащий объектив 2, в фокальной плоскости которого расположена фоточувствительная сторона матрицы ПЗИ 3 - прибор с зарядовой инжекцией, выполненный по технологии Foreon Х3 из трехслойного КМОП-датчика [3, с.552, 4 c.832, 833, 835], с оптическим разрешением 2000×1000 и обеспечивающий 24-битную глубину цвета [4 с.835], с первого по третий выходы матрицы ПЗИ 3 подключены соответственно к входам предварительных усилителей 4 /R/, 5 /G/ и 6 /В/, передающая сторона включает первый 7, второй 8, третий 9 АЦП видеосигнала соответственно сигналов R, G, В, первый 10 и второй 11 АЦП сигнала звука, последовательно соединенные задающий генератор 12 синусоидальных колебаний и синтезатор 13 частот, первый 14, второй 15, третий 16 кодеры, первый формирователь 17 кодов, второй формирователь 18 кодов, первый самоходный распределитель 19 импульсов /СРИ/, формирующий код строчного синхроимпульса ССИ, второй самоходный распределитель 20 импульсов /СРИ/, формирующий код кадрового синхроимпульса КСИ, первый 21 и второй 22 ключи и передатчик 23 радиосигналов из двух каналов. Первый канал содержит последовательно соединенные усилитель 24 несущей частоты, первый формирователь 25 однополосного сигнала и выходной усилитель 26, второй канал содержит последовательно соединенные второй формирователь 27 однополосного сигнала, первый вход которого подключен к выходу усилителя 24 несущей частоты, и выходной усилитель 28. Каждый формирователь однополосного сигнала состоит из последовательно соединенных кольцевого модулятора и полосового фильтра [5 с.234]. В первом формирователе 25 однополосного сигнала подавляется несущая частота и отфильтровывается нижняя боковая частота, верхняя модулированная боковая частота излучается в эфир. Во втором формирователе 27 подавляется несущая частота и отфильтровывается верхняя боковая частота, нижняя модулированная боковая частота излучается в эфир. АЦП 7, 8, 9 выполнены идентично, принимаются без изменений из прототипа [2, с.9, фиг.3]. Кодеры 14, 15, 16 идентичны, каждый включает /фиг.3/ последовательно соединенные регистр 29, схему 30 сравнения /компаратор/, счетчик 31 импульсов и дешифратор 32, последовательно соединенные блок 33 элементов задержек, блок 34 ключей и буферный накопитель 35 кодов кадра. Информационными входами являются поразрядно объединенные 1-8 входы регистра 29, первые входы 1-8 схемы 30 сравнения и входы 1-8 блока 33 элементов задержек. Выходами являются с первого по девятый выходы буферного накопителя 35 кодов кадра, объем которого составляет 250×103 кодов кадра 9-разрядных.

Первый формирователь 17 кодов включает /фиг.5/ четыре канала, первый и второй каналы идентичны. Первый канал включает последовательно соединенные первый блок 36 элементов И, первый 37 и второй 38 элементы ИЛИ, первый выходной ключ 39, первый самоходный распределитель 40 импульсов, второй канал включает второй блок 41 элементов И, третий 42 и четвертый 43 элементы ИЛИ, второй выходной ключ 44 и второй самоходный распределитель 45 импульсов /СРИ/.

Третий канал включает третий блок 46 элементов И, пятый 47 элемент ИЛИ и третий СРИ 48, четвертый канал включает четвертый блок 49 элементов И, шестой элемент ИЛИ 50 и четвертый СРИ 51. Формирователь 17 кодов включает первый 52 и второй 53 ключи и последовательно соединенные счетчик 54 импульсов и дешифратор 55. Информационными входами блока 17 являются: первым - первые входы блока 36 элементов И первого канала, вторым - первые входы блока 41 элементов И второго канала, третьим - входы блоков 46 и 49 элементов И третьего и четвертого каналов соответственно, четвертым - объединенные третьи входы второго 38 и четвертого 43 элементов ИЛИ первого и второго каналов, подключенные к выходу первого СРИ 19. Первым выходом являются объединенные выходы выходных ключей 39, 44, третий выход дешифратора 55 является вторым выходом блока 17 и подключен к входу первого СРИ 19, подавая на его вход сигнал

Uп пуска. Управляющими входами являются: первым - объединенные входы /6,25 МГц/ ключей 52, 53 и счетный вход счетчика 54 импульсов, вторым - объединенные сигнальные входы /56,25 МГц/ выходных ключей 39, 44, третьим - управляющий вход /25 кГц/ счетчика импульсов. Первый выход дешифратора 55 подключен к первому управляющему входу ключа 52 и к второму управляющему входу ключа 53, второй выход подключен к второму управляющему входу ключа 52 и к первому управляющему входу ключа 53, третий выход дешифратора 55 является вторым выходом формирователя 17 кодов. Второй формирователь 18 кодов включает /фиг.6/ два канала. Первый канал содержит последовательно соединенные первый блок 56 элементов И, первый 57 и второй 58 элементы ИЛИ и первый выходной ключ 59, и первый самоходный распределитель 60 импульсов /СРИ/, второй канал включает последовательно соединенные второй блок 61 элементов И, третий 62 и четвертый 63 элементы ИЛИ и второй выходной ключ 64, и второй самоходный распределитель 65 импульсов, и включает последовательно соединенные третий блок 66 элементов И и пятый элемент ИЛИ 67, и третий 68 СРИ. А также включает первый 69 и второй 70 ключи, счетчик 71 импульсов и дешифратор 72. Информационными входами являются: первым - первые входы элементов И первого блока 56, вторым - первые входы элементов И блоков 61, 66 второго канала, третьим - третий вход второго элемента ИЛИ 58 в первом канале, четвертым - второй вход четвертого элемента ИЛИ 63 второго канала. Выходом являются объединенные выходы выходных ключей 59, 64. Управляющими входами являются: первым - объединенные входы /6,25 МГц/ первого 69 и второго 70 ключей и счетный вход счетчика 71 импульсов, вторым - объединенные сигнальные входы /56,25 МГц/ выходных ключей 59, 64, третьим - управляющий вход счетчика 71 импульсов. АЦП 10, 11 сигнала звука идентичны, применяются от прототипа без изменений [2, с.9, фиг.4], преобразуют сигналы звука в 16-разрядные коды, которые поступают с дискретизацией 75 кГц с АЦП 10 на третий вход формирователя 17 кодов, с АЦП 11 на второй вход формирователя 18 кодов /фиг.1/.

Приемная сторона включает /фиг.7/ антенну, блок 73 управления /выбора каналов/, первый и второй тракты приема и обработки кодов видеосигналов, устройство отображения видеоинформации, канал формирования управляющих сигналов и два канала звукового сопровождения. Первый тракт приема и обработки кодов видеосигналов производит прием и обработку кодов сигналов R и G и включает последовательно соединенные блок 74 приема радиосигнала, усилитель 75 радиочастоты, двухполярный амплитудный детектор 76, канал сигнала R и канал сигнала G. Канал сигнала R включает последовательно соединенные первый формирователь 77 импульсов, декодер 78, блок 79 обработки кодов, вновь введенные накопитель 80 кодов кадра и формирователь 81 управляющих сигналов. Канал сигнала G включает последовательно соединенные второй формирователь 82 импульсов, декодер 83, блок 84 обработки кодов, введенные накопитель 85 кодов кадра и формирователь 86 управляющих сигналов. Второй тракт приема и обработки кодов видеосигналов производит прием и обработку кодов сигнала В и включает последовательно соединенные блок 87 приема радиосигнала, усилитель 88 радиочастоты, двухполярный амплитудный детектор 89, второй формирователь 90 импульсов и канал сигнала В, содержащий последовательно соединенные первый формирователь 91 импульсов, декодер 92, блок обработки 93 кодов, введенные накопитель 94 кодов кадра и формирователь 95 управляющих сигналов. Выходы формирователей 81, 86, 95 управляющих сигналов подключены к соответствующим входам плоскопанельного светодиодного экрана 96 /СД-экрана/. Порядок работы приемной стороны определяет канал формирования управляющих сигналов, включающий последовательно соединенные блок 97 выделения строчных синхроимпульсов /ССИ/, синтезатор 98 частот, ключ 99, счетчик 100 импульсов и дешифратор 101, и блок 102 выделения кадрового синхроимпульса /КСИ/. Каналы звукового сопровождения идентичны, применяются без изменений, как в прототипе, каждый из них содержит преобразователь кодов звука в аналоговые сигналы /ЦАП/, усилитель мощности и громкоговоритель. Декодеры 78, 83, 92 идентичны, каждый включает /фиг.9/ последовательно соединенные первый девятиразрядный регистр 105, накопитель 106 кодов кадра емкостью на 250000 9-разрядных кодов

/250отсч × 1000строк/, второй 9-разрядный регистр 107, первый блок 108 ключей из 8 ключей и третий 8-разрядный регистр 109, последовательно соединенные второй блок 110 ключей из восьми ключей, 8-разрядный вычитающий счетчик 111 импульсов и дешифратор 112, первый 113, второй 114, третий 115 и четвертый 116 ключи. Информационным входом декодера 78 является информационный вход первого регистра 105, выходом - первый-восьмой выходы регистра 109. Управляющими взводами являются: первым - первый управляющий вход /56,25 МГц/ первого регистра 105, вторым - объединенные второй управляющий вход /6,25 МГц/ регистра 105 и сигнальный вход ключа 115, третьим - объединенный сигнальные входы /25 МГц/ первого 113, второго 114 и четвертого 116 ключей. Блоки 79, 84, 93 обработки кодов идентичны, каждый включает /фиг.10/ триггер 117, вход которого является управляющим входом блока, первый 118 и второй 119 блоки ключей, каждый из восьми ключей, первый 120, второй 121, третий 122, четвертый 123 регистры, сумматор 124, пятый 125 и шестой 126 регистры, выполняющие хранение кодов 40 нс и 16 диодов. Информационным входом являются объединенные поразрядно 1-8 входы блоков 118, 119 ключей. Выходом являются поразрядно объединенные выходы сумматора 124 /0-7/ и регистров 125, 126 /1-8/. Накопители 80, 85, 94 кодов кадра идентичны, каждый включает /фиг.11/ блоки 127 регистров по числу строк в кадре

1271-1000. Информационным входом накопителя кодов кадра являются поразрядно объединенные 1-8 входы всех блоков 1271-1000 регистров. Выходами являются выходы всех блоков 127 регистров, всего выходов 16×106 /2000×8×1000/. Управляющими входами являются: первым - первый управляющий вход /Uк 25 Гц/ первого блока 1271 регистров, вторым - объединенные вторые управляющие входы / Uвыд 25 кГц/ блоков 127, третьим - объединенные третьи управляющие входы /Uд 50 МГц/ блоков 127 регистров. Управляющий выход каждого предыдущего блока 127 регистров является первым управляющим входом каждого последующего блока 127 регистров. Управляющий выход последнего блока 1271000 регистров подключен параллельно к четвертым управляющим входам всех блоков 1271-1000 регистров.

Блоки 127 регистров идентичны, каждый включает /фиг.12, 13/ первый 128 и второй 129 ключи, распределитель 130 импульсов и восемь регистров 1311-8, каждый из них содержит по 2000 разрядов, по числу отсчетов в строке. Информационными входами блока регистров являются поразрядно объединенные с 1 по 8-й третьи входы разрядов восьми регистров 131. Выходами являются параллельные выходы всех разрядов восьми регистров 131, всего выходов с блока 16000 /2000×8/. Выходы 1000 блоков 127 являются выходами каждого накопителя кодов кадров 16×106 /16000×1000/. Управляющими входами являются: первым - первый управляющий вход /50 Гц/ первого ключа 128, вторым - сигнальный вход /Uвыд 25 кГц/ второго ключа 129, третьим - сигнальный вход /Uд 50 МГц/ первого ключа 128, четвертым - первый управляющий вход второго ключа 129. Последний выход блока 130 является управляющим выходом блока 127 для следующего блока 1272 регистров и подключен к первому управляющему входу его первого ключа 128. Выход первого ключа 128 подключен к входу распределителя 130 импульсов, выходы которого последовательно с первого по 2000-й подключены к первым /тактовым/ входам разрядов параллельно восьми регистров 131. Выход второго ключа 129 подключен параллельно к вторым входам разрядов восьми регистров 131 и к второму управляющему входу своего ключа 129, прошедший один импульс Uвыд закрывает ключ 129. Выходы накопителей 80, 85, 94 кодов кадра подключены /фиг.7/ к информационным входам своих формирователей 81, 86, 95 управляющих сигналов, назначение которых выполнять преобразования "код - число импульсов излучений" для получения скважности излучений светодиода за период кадра соответственно величине кода цветового сигнала. Каждый из блоков 81, 86, 95 включает преобразователей "код - число импульсов излучений" по числу отсчетов в отроке /2000/ и числу строк /1000/ в кадре, т.е. 2×106. Блоки 81, 86, 95 идентичны, каждый включает /фиг.14/ блок 132 формирователей импульсов, содержащий идентичных схем формирования импульсов по числу преобразователей /2×106/, вход которого является управляющим входом /Uк 25 Гц/ блока 81 /86, 95/, и преобразователи "код - число импульсов излучений", которых по числу разрешения в кадре 2×106. Каждый из преобразователей содержит последовательно соединенные дешифратор 133, информационные 1-8 входы которого являются и информационными входами преобразователя, блок 134 ключей из 255 ключей и выходной ключ 135, включает самоходный распределитель 136 импульсов /СРИ/ и источник 137 питания для своего светодиода в СД-экране. 255 выходов дешифратора 133 подключены к первым управляющим входам Uот ключей в блоке 134, выходы ключей блока 134 объединены, и объединенный выход подключен к управляющему входу Uот выходного ключа 135, сигнальный вход которого подключен к выходу источника 137 питания. Вход СРИ 136 подключен к своему выходу в блоке 132 формирователей импульсов, а сам СРИ 136 имеет 255 разрядов, выходы которых подключены к сигнальным входам соответствующих ключей в блоке 134 ключей /вход 2/. Информационными входами блока 81 /86, 95/ являются информационные входы всех дешифраторов 133, выходы выходных ключей 135 являются выходами блоков 81, 86, 95, которые подключены к соответствующим входам СД-экрана 96. Исходное состояние выходных ключей 135 и ключей в блоках 134 закрытое. На управляющий вход блока 132 поступает сигнал Uк 25 Гц, который в нем параллельно поступает на входы схем формирователей импульсов, формирующих импульсы соответствующей амплитуды и длительности и являющихся пусковыми Uп импульсами для СРИ 136. Каждый импульс блока 134 открывает Uот выходной ключ на время в 156 мкс:  40 мс длительность кадра, 255 - разрешение 8-разрядного кода, т.е. число выходов с блока 136. С приходом кода в дешифратор 133 сигналы с его выходов открывают соответствующие ключи в блоке 134, которые последовательно пропускают на выход блока 134 с соответствующих разрядов блока 136 сигналы Uот в выходной ключ 135, и светодиод в экране 96 за период кадра через равные интервалы времени выдает импульсы излучений прямо пропорционально величине кода цветового сигнала. Чем больше код, тем больше импульсов излучений от светодиода за период кадра. Пример распределения импульсов излучений в периоде кадра соответственно величинам кодов приведен в таблице 1.

40 мс длительность кадра, 255 - разрешение 8-разрядного кода, т.е. число выходов с блока 136. С приходом кода в дешифратор 133 сигналы с его выходов открывают соответствующие ключи в блоке 134, которые последовательно пропускают на выход блока 134 с соответствующих разрядов блока 136 сигналы Uот в выходной ключ 135, и светодиод в экране 96 за период кадра через равные интервалы времени выдает импульсы излучений прямо пропорционально величине кода цветового сигнала. Чем больше код, тем больше импульсов излучений от светодиода за период кадра. Пример распределения импульсов излучений в периоде кадра соответственно величинам кодов приведен в таблице 1.

1, 2, 3…255 - номера следования излучений в периоде кадра.

Следование излучений в периоде кадра через равномерные интервалы времени обеспечивает достоверность восприятия зрением человека цветопередачи и яркости изображения на экране. Инерционность светодиодов должна быть до 1 мкс или меньше. По окончании накопления кодов кадра блоками 80, 85, 94 коды сигналов R, G, В синхронно выдаются из них в формирователи 81, 86, 95 управляющих сигналов, где коды преобразуются в соответствующее число излучений светодиодами за период кадра. Современный технологии позволяют выполнить каждые из блоков 80, 85, 94, и 81, 86, 95 в одной микросхеме.

Плоскопанельный светодиодный экран 96 представляет совокупность излучающих элементов в матрице по числу разрешения кадра 2×106, которые выполняются в стекле СД-экрана 96. СД-экран включает экранное стекло и матрицу из излучающих элементов по числу разрешения кадра. Каждый излучающий элемент включает три светодиодных ячейки /СД-ячейки/, каждая из которых излучает один из основных цветов R, G, В. СД-ячейка содержит /фиг.15/ светодиод 138 белого свечения и соответствующий цветной светофильтр 139. Три СД-ячейки составляют излучающий элемент матрицы /фиг.16/, расположение элементов матрицы и СД-ячеек в СД-экране 96 - на фиг.17. Уровень яркости излучения СД-ячейки воспринимается зрением пропорционально числу импульсов излучения светодиода за период кадра и может быть в диапазоне от одного /156 мкс/ до 255 /40 мс/ излучений. Суммарное излучение трех основных цветов тремя СД-ячейками формирует для зрения яркость и цветовой тон одного пиксела экрана. В качестве светодиодов применяются сверхъяркие светодиоды фирм "Nichia", "Ledtronics", "Kingbright" [6, с.47]. Светодиоды исполняются в экранном стекле методом микроэлектронной технологии. Размеры светодиодов принимаются диаметром в 0,5 мм /фиг.15/. Размер одного элемента матрицы 1×1 мм /фиг.16/. Размер СД-экрана 96 составляет: по горизонтали 2000×1 мм=2000 мм, по вертикали 1000×1 мм=1000 мм, по диагонали 2236 мм, 88". Блок 97 выделения строчных синхроимпульсов ССИ включает /фиг.18/ первый 140, второй 141, третий 142 счетчики импульсов, первый 143, второй 144 элементы И, первый 145, второй 146 и третий 147 элементы НЕ и диод. Входами блока являются счетные входы счетчиков импульсов, выходом - выход второго элемента И 144, который через диод подключен параллельно к управляющим входам счетчиков импульсов. Входы элементов НЕ подключены соответственно к счетным входам 1-3 счетчиков импульсов, выходы элементов НЕ объединены и подключены параллельно к управляющим входам счетчиков импульсов. Блок 102 выделения кадровых синхроимпульсов КСИ включает /фиг.19/ первый 148 и второй 149 счетчики импульсов, первый 150 и второй 151 элементы И, первый 152 и второй 153 элементы НЕ, выходы которых объединены и подключены к управляющим входам счетчиков импульсов, счетные входы которых являются первым и вторым входами блока 102, входы элементов НЕ подключены к счетным входам соответственно первого и второго счетчиков импульсов, выходы которых подключены к входам первого элемента И 150, выход которого и третий вход блока 102 подключены к входам второго элемента И 151, выход которого является выходом блока 102 и через диод подключен к управляющим входам обоих счетчиков импульсов.

Фотоэлектрический преобразователь 1 матрицей ПЗИ 3 формирует три аналоговых видеосигнала основных цветов R, G, В. Объектив 2 создает изображение в фокальной плоскости, в которой расположена фоточувствительная сторона матрицы ПЗИ 3, оптическое разрешение которой не менее 2000×1000. Матрица ПЗИ выполнена трехслойной по технологии ХЗ. В первом периоде кадра "40 мс" на каждый из трех слоев матрицы ПЗИ /вход 1/ с ключа 21 поступают импульсы 25 кГц частоты строк для считывания сигналов пикселов по вертикали, на второй вход матрицы ПЗИ с ключа 22 поступают импульсы 25 МГц для считывания сигналов R, G, В пикселов по горизонтали [4, с.832]. Аналоговые сигналы с матрицы ПЗИ 3 поступают на входы предварительных усилителей 4 /R/, 5 /G/, /6 /В/, с выходов которых поступают на входы АЦП соответственно 7, 8, 9, с выходов которых 8-разрядные коды цветовых сигналов с дискретизацией 25 МГц поступают на входы своих кодеров 14, 15, 16. Синхронизация считывания сигналов с матрицы ПЗИ выполняется сигналом частоты кадров 25 Гц открытием ключей 21, 22 на длительность кадра 40 мс. Синтезатор 13 частот выдает с первого выхода импульсы 25 МГц дискретизации кодов в АЦП видеосигналов, со второго - импульсы 6,25 МГц выдачи кодов из кодеров 14-16, с третьего - импульсы 75 кГц дискретизации сигнала звука, с четвертого - тактовые импульсы 56,25 МГц для формирователей 17, 18 кодов, с пятого - импульсы 25 кГц частоты отрок на первый вход матрицы ПЗИ 3 и блоки 17, 18, с шестого выхода - импульсы 25 Гц частоты кадров для открытия ключей 21, 22 длительностью, равной длительности кадра 40 мс, с седьмого - синусоидальные колебания несущей частоты 843,75 МГц в передатчик 23 со стабильностью 10-7. Задающий генератор 12 генерирует синусоидальные колебания со стабильностью 10-7. АЦП 7, 8, 9 преобразуют аналоговые видеосигналы R, G, В в 8-разрядные коды, поступающие в кодеры 14, 15, 16.

Работа кодеров представлена на фиг.3.

8-разрядные коды в параллельном виде поступают на 1-8 входы регистра 29, на первые входы схемы сравнения 30 и на входы блока 33 элементов задержек. Исходное состояние ключей в блоке 34 открытое.

Код в блоке 33 задерживается на время срабатывания схемы сравнения 18 нс и поступает через открытые ключи блока 34 на 1-8 входы буферного накопителя 35 кодов кадра емкостью 250×103 9-разрядных кодов. Схема сравнения 30 выполняет сравнение по величине каждого предыдущего и последующего кодов с целью выявления их равенства или неравенства. При следовании неравных кодов они проходят через блок 33, ключи блока 34 и поступают на первый-восьмой входы буферного накопителя 35 кодов. Выдача кодов из блока 35 выполняется сигналом

Uвыд 6,25 МГц с выхода 2 блока 13. Поступление кодов в блок 35 при следовании неравных кодов идет с частотой 25 МГц. В общем потоке кодов имеется большое число равных по величине кодов, причем, чем выше частота дискретизации, тем равных кодов будет больше. Кодер выполняет сжатие потока кодов с плавающим коэффициентом сжатия от 1 до 255. Средний общий коэффициент сжатия принимается равным 4, поэтому частота выдачи кодов с блока 35 принимается 6,25 МГц  При коэффициентах выше 4 эта частота выдачи будет тем более удовлетворять. Схема 30 сравнения выполняет сравнение кодов по величине, представляется двумя микросхемами 530СП1 с временем срабатывания 16 нс [7, с.279]. При неравенстве А>В появляется сигнал на выходе 2 блока 30 /в микросхеме выход 5 [7, с.272, рис.2. 190]/, при равенстве кодов А=В сигнал с выхода 3 /в микросхеме выход 7/. При равенстве кодов сигнал с выхода 1 блока 30 закрывает ключи в блоке 34, поступает счетным импульсом в счетчик 31 и как сигнал Uвыд на первый управляющий вход регистра 29. Счетчик 31 производит счет импульсов с выхода 1 блока 30 пока идут коды, равные по величине. Счетчик 31 8-разрядный, максимальный код в нем 11111111 /255/, отсюда и максимальный коэффициент сжатия 255. С применением счетчика с большей разрядностью коэффициент сжатия будет больше: при 9-разрядном коэффициент будет с 1 по 511. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [7 c.428]. При появлении неравных кодов со схемы 30 следует сигнал с выхода 2 или 3 /А<В/, которые объединены, сигнал с них используется для выдачи Uвыд кода числа равных кодов из счетчика 31 черев диоды в первый-восьмой входы блока 35 и для заполнения в блоке 35 девятого разряда, с которого сигнал используется для опознания по нему кода числа равных кодов при декодировании. Этот же сигнал открывает ключи в блоке 34 /вход 1/ и обнуляет регистр 29 /вход 2/. Выданный перед этим с блока 35 код является первым кодом последовательности, на диаграмме 1 фиг.4 они помечены крестиками. Коды, равные по по величине и подсчитанные счетчиком 31, исключаются из потока, диаграмма 111. Емкость буферного накопителя 35 кодов соответствует числу 9-разрядных кодов в кадре /250×103/ для обеспечения темпа следования с частотой 6,25 МГц. При следовании подряд кодов, равных по величине, более 255 в работу вступает дешифратор 32. При коде 11111111 дешифратор 32 выдает сигнал, который одновременно открывает ключи в блоке 34 /вход 1/, обнуляет регистр 29, сингалом Uвыд выдает код из счетчика 31 /вход 1/ и обнуляет счетчик /вход 2/, а в девятый разряд блока 35 поступает сигнал опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы сравнения 30 /18 нс/ и составляет до 50 Мбайт/с. С выходов кодеров 14 и 15 коды в параллельном виде поступают на первый и второй информационные входы формирователя 17 кодов, с кодера 16 - на первый информационный вход формирователя 18 кодов. Первый формирователь 17 кодов первым в строке выдает /фиг.2/ код строчного синхроимпульса /ССИ/, из сжатого потока кодов формирует и выдает со второго по 247 коды сигналов R и G и затем три кода звука 248, 249, 250 /фиг.2/. Второй формирователь 18 кодов первыми в строке выдает коды ССИ и КСИ /фиг.2/, код КСИ в первой строке каждого кадра, из сжатого потока выдает со второго по 247 коды сигнала В и три кода Зв2 звука 248, 249, 250. Единицы в кодах R и В представляются на выходе блоков 27, 18 положительными полусинусоидами моночастоты 56,25 МГц, единицы в кодах сигнала G и КСИ представляются отрицательными полусинусоидами той же моночастоты.

При коэффициентах выше 4 эта частота выдачи будет тем более удовлетворять. Схема 30 сравнения выполняет сравнение кодов по величине, представляется двумя микросхемами 530СП1 с временем срабатывания 16 нс [7, с.279]. При неравенстве А>В появляется сигнал на выходе 2 блока 30 /в микросхеме выход 5 [7, с.272, рис.2. 190]/, при равенстве кодов А=В сигнал с выхода 3 /в микросхеме выход 7/. При равенстве кодов сигнал с выхода 1 блока 30 закрывает ключи в блоке 34, поступает счетным импульсом в счетчик 31 и как сигнал Uвыд на первый управляющий вход регистра 29. Счетчик 31 производит счет импульсов с выхода 1 блока 30 пока идут коды, равные по величине. Счетчик 31 8-разрядный, максимальный код в нем 11111111 /255/, отсюда и максимальный коэффициент сжатия 255. С применением счетчика с большей разрядностью коэффициент сжатия будет больше: при 9-разрядном коэффициент будет с 1 по 511. Счетчик из микросхем К531ИЕ160 с временем срабатывания 8 нс [7 c.428]. При появлении неравных кодов со схемы 30 следует сигнал с выхода 2 или 3 /А<В/, которые объединены, сигнал с них используется для выдачи Uвыд кода числа равных кодов из счетчика 31 черев диоды в первый-восьмой входы блока 35 и для заполнения в блоке 35 девятого разряда, с которого сигнал используется для опознания по нему кода числа равных кодов при декодировании. Этот же сигнал открывает ключи в блоке 34 /вход 1/ и обнуляет регистр 29 /вход 2/. Выданный перед этим с блока 35 код является первым кодом последовательности, на диаграмме 1 фиг.4 они помечены крестиками. Коды, равные по по величине и подсчитанные счетчиком 31, исключаются из потока, диаграмма 111. Емкость буферного накопителя 35 кодов соответствует числу 9-разрядных кодов в кадре /250×103/ для обеспечения темпа следования с частотой 6,25 МГц. При следовании подряд кодов, равных по величине, более 255 в работу вступает дешифратор 32. При коде 11111111 дешифратор 32 выдает сигнал, который одновременно открывает ключи в блоке 34 /вход 1/, обнуляет регистр 29, сингалом Uвыд выдает код из счетчика 31 /вход 1/ и обнуляет счетчик /вход 2/, а в девятый разряд блока 35 поступает сигнал опознания кода числа равных кодов. Пропускная способность кодера определяется временем срабатывания схемы сравнения 30 /18 нс/ и составляет до 50 Мбайт/с. С выходов кодеров 14 и 15 коды в параллельном виде поступают на первый и второй информационные входы формирователя 17 кодов, с кодера 16 - на первый информационный вход формирователя 18 кодов. Первый формирователь 17 кодов первым в строке выдает /фиг.2/ код строчного синхроимпульса /ССИ/, из сжатого потока кодов формирует и выдает со второго по 247 коды сигналов R и G и затем три кода звука 248, 249, 250 /фиг.2/. Второй формирователь 18 кодов первыми в строке выдает коды ССИ и КСИ /фиг.2/, код КСИ в первой строке каждого кадра, из сжатого потока выдает со второго по 247 коды сигнала В и три кода Зв2 звука 248, 249, 250. Единицы в кодах R и В представляются на выходе блоков 27, 18 положительными полусинусоидами моночастоты 56,25 МГц, единицы в кодах сигнала G и КСИ представляются отрицательными полусинусоидами той же моночастоты.

Работа формирователей 17, 18 кодов представлена на фиг.5, 6.

Временные диаграммы работы блоков - на фиг.21. Блоки 17, 18 преобразуют коды с параллельных в последовательные с заменой в них представление единиц с импульсов на положительные и отрицательные полисинусоиды. На первый вход формирователя 17 кодов поступают коды с АЦП 14, на второй с АЦП 15, на третий с АЦП 10 коды звука и на четвертый вход код сигнала ССИ с блока 19. 9-разрядные коды поступают на первые входы элементов И блоков 36, 41, на вторые входы которых поступают последовательно 9 импульсов с выходов СРИ 40 и 45, сигнал Uп пуска на которые поступает с первого ключа 52. С выходов блоков 36, 41 импульсы кодов последовательно через элементы ИЛИ 37, 38 и 42, 43 поступают на управляющие входы выходных ключей соответственно 39, 44 и открывают их на время своей длительности 18 нс  Выходной ключ 39 в открытом состоянии пропускает одну положительную полусинусоиду на выход, выходной ключ 44 в открытом состоянии пропускает на выход одну отрицательную полусинусоиду. Выходы ключей объединены, являются выходом /первым/ блока 17, на выходе которого выходной сигнал представляется полными или неполными синусоидами моночастоты 56,25 МГц со стабильностью 10-7. Сигналы с первого выхода блока 17 модулируют несущую частоту в блоке 25 /фиг.1/. Очередность формирования сигналов ССИ, кодов строки и звука 3в1 определяют сигналы с дешифратора 55. Счетчик 54 8-разрядный, ведет счет с 1-го по 250 импульсы строки частоты 6,25 МГц. При коде 00000001 импульс с первого выхода дешифратора 55 открывает ключ 52 и закрывает ключ 53. При этом идет формирование кодов строки со второго отсчета по 247-й. С приходом на вход счетчика 54 247-го импульса сигнал со второго выхода дешифратора 55 закрывает ключ 52, открывает ключ 53, при этом формируются три кода звука 248, 249, 250. Сигналы разрядов с 1 по 8 кода звука поступают на первые входы блока 46, с него через элементы ИЛИ 47 и 38 на управляющий вход выходного ключа 39. Сигналы разрядов с 9 по 16 кода звука поступают на первые входы блока 49, с него через элементы ИЛИ 50, 43 на управляющий вход выходного ключа 44. С приходом в счетчик 54 250-го импульса строки с третьего выхода дешифратора 55 следует сигнал, являющийся вторым выходом блока 17, поступает как сигнал Uп пуска на вход первого СРИ 19 и запускает его в работу, с выхода которого 9-разрядный код ССИ поступает на третьи входы элементов ИЛИ 38, 43. На первый вход второго формирователя 18 кодов поступают 9-разрядные коды сигнала В на первые входы блока 56, на вторые входы которого поступают девять импульсов с СРИ 60. С выхода блока 58 импульсы кода последовательно поступают на вход выходного ключа 59, который в открытом состоянии пропускает одну положительную полусинусоиду. Коды сигнала В формируются аналогично, как и в формирователе 17 со второго по 247 отсчеты строки. С приходом в счетчик 71 247-го импульса сигнал со второго выхода дешифратора 72 закрывает ключ 69, открывает ключ 70: формируются три кода 3в2 звука 248, 249, 250. По окончании периода кадра в СРИ 20 /фиг.1/ поступает сигнал 25 Гц Uп, запускающий его в работу. С блока 20 на второй вход элемента ИЛИ 63 и на третий вход элемента ИЛИ 58 синхронно поступают коды КСИ и ССИ. Код КСИ является первым кодом только в первой строке каждого кадра, код ССИ является первым кодом в каждой строке. С приходом в счетчик 71 /54/ первого импульса следующей строки дешифратор 72 /55/ с первого выхода закрывает ключ 70 /63/ и открывает ключ 69 /52/, следует формирование кодов строки. Далее процессы повторяются. Сигналы с второго формирователя 18 кодов модулируют несущую чистоту в блоке 27 /фиг.1/. Спектр амплитудно-модулированного сигнала передатчика 23 состоит из несущей частоты и двух боковых частот: верхней 900 МГц и нижней 787,5 МГц. Сама несущая частота и одна из боковых частот являются избыточными, поэтому в каждом из формирователей 25, 27 однополосного сигнала подавляется несущая и отфильтровывается ненужная боковая /фиг.20/. Блок 25 выдает в выходной усилитель 26 верхнюю боковую частоту 900 МГц с информацией кодов сигналов R и G и при стабильности несущей 10-7 занимает в эфире полосу ±90 Гц или 180 Гц.

Выходной ключ 39 в открытом состоянии пропускает одну положительную полусинусоиду на выход, выходной ключ 44 в открытом состоянии пропускает на выход одну отрицательную полусинусоиду. Выходы ключей объединены, являются выходом /первым/ блока 17, на выходе которого выходной сигнал представляется полными или неполными синусоидами моночастоты 56,25 МГц со стабильностью 10-7. Сигналы с первого выхода блока 17 модулируют несущую частоту в блоке 25 /фиг.1/. Очередность формирования сигналов ССИ, кодов строки и звука 3в1 определяют сигналы с дешифратора 55. Счетчик 54 8-разрядный, ведет счет с 1-го по 250 импульсы строки частоты 6,25 МГц. При коде 00000001 импульс с первого выхода дешифратора 55 открывает ключ 52 и закрывает ключ 53. При этом идет формирование кодов строки со второго отсчета по 247-й. С приходом на вход счетчика 54 247-го импульса сигнал со второго выхода дешифратора 55 закрывает ключ 52, открывает ключ 53, при этом формируются три кода звука 248, 249, 250. Сигналы разрядов с 1 по 8 кода звука поступают на первые входы блока 46, с него через элементы ИЛИ 47 и 38 на управляющий вход выходного ключа 39. Сигналы разрядов с 9 по 16 кода звука поступают на первые входы блока 49, с него через элементы ИЛИ 50, 43 на управляющий вход выходного ключа 44. С приходом в счетчик 54 250-го импульса строки с третьего выхода дешифратора 55 следует сигнал, являющийся вторым выходом блока 17, поступает как сигнал Uп пуска на вход первого СРИ 19 и запускает его в работу, с выхода которого 9-разрядный код ССИ поступает на третьи входы элементов ИЛИ 38, 43. На первый вход второго формирователя 18 кодов поступают 9-разрядные коды сигнала В на первые входы блока 56, на вторые входы которого поступают девять импульсов с СРИ 60. С выхода блока 58 импульсы кода последовательно поступают на вход выходного ключа 59, который в открытом состоянии пропускает одну положительную полусинусоиду. Коды сигнала В формируются аналогично, как и в формирователе 17 со второго по 247 отсчеты строки. С приходом в счетчик 71 247-го импульса сигнал со второго выхода дешифратора 72 закрывает ключ 69, открывает ключ 70: формируются три кода 3в2 звука 248, 249, 250. По окончании периода кадра в СРИ 20 /фиг.1/ поступает сигнал 25 Гц Uп, запускающий его в работу. С блока 20 на второй вход элемента ИЛИ 63 и на третий вход элемента ИЛИ 58 синхронно поступают коды КСИ и ССИ. Код КСИ является первым кодом только в первой строке каждого кадра, код ССИ является первым кодом в каждой строке. С приходом в счетчик 71 /54/ первого импульса следующей строки дешифратор 72 /55/ с первого выхода закрывает ключ 70 /63/ и открывает ключ 69 /52/, следует формирование кодов строки. Далее процессы повторяются. Сигналы с второго формирователя 18 кодов модулируют несущую чистоту в блоке 27 /фиг.1/. Спектр амплитудно-модулированного сигнала передатчика 23 состоит из несущей частоты и двух боковых частот: верхней 900 МГц и нижней 787,5 МГц. Сама несущая частота и одна из боковых частот являются избыточными, поэтому в каждом из формирователей 25, 27 однополосного сигнала подавляется несущая и отфильтровывается ненужная боковая /фиг.20/. Блок 25 выдает в выходной усилитель 26 верхнюю боковую частоту 900 МГц с информацией кодов сигналов R и G и при стабильности несущей 10-7 занимает в эфире полосу ±90 Гц или 180 Гц.

Блок 27 выдает в выходной усилитель 28 нижнюю боковую частоту 787,5 МГц с информацией кодов сигнала В и КСИ и занимает в эфире полосу ±79 Гц или 158 Гц. Применяемый способ передачи выполняет высокую помехозащищенность сигнала: энергия помех в таких таких полосах окажется мизерной, применяемый гармонический /синусоидальный/ сигнал менее всего подвержен искажениям. На приемной стороне принимаются два радиосигнала блоками 74, 87 /фиг.7/, являющихся селекторами каналов соответствующих диапазонов с электронной настройкой. Каждый блок включает входную цепь, усилитель радиочастоты и смеситель [6, с.132]. Полосовой фильтр усилителя радиочастоты перестраивается напряжением смещения с блока 73 управления /выбора каналов/. Радиочастотный сигнал в блоке 74 /87/ через петлю связи поступает на смеситель, сюда же с синтезатора 98 частот /выход 3/ подается частота, равная несущей частоте передатчика 23, необходимая при детектировании однополосного сигнала [9, с.146]. Сигнал со смесителя, являющийся выходным сигналом блока 74 /87/, поступает на вход усилителя 75 /88/ радиочастоты, где усиливается до необходимой величины и поступает на вход двухполярного амплитудного детектора 76 /89/, выполненного по схеме на фиг.8. Диод Д1 выделяет положительную огибающую модулирующего сигнала /фиг.21 диаграмма 9/. Диод Д2 из модулирующей выделяет огибающие положительных полусинусоид - символы единиц сигнала R /диаграмма 10/, диод Д3 из модулирующей выделяет огибающие отрицательных полусинусоид - символы единиц сигнала G /диаграмма 11/. Аналогично и в блоке 89 для сигнала В. С первого выхода блока 76 продетектированные положительные полусинусоиды частоты 56,25 МГц поступают на вход первого формирователя 77 импульсов, со второго выхода блока 76 продетектированные отрицательные полусинусоиды 56,25 МГц поступают на вход второго формирователя 82 импульсов.

Формирователи 77, 82, 90, 91 импульсов выполнены по схеме несимметричного триггера с эмиттерной связью [10 с.209], формирующего прямоугольные импульсы из гармонически изменяющихся сигналов. Импульсы имеют одну полярность и длительность, равную длительности импульсов на передающей стороне. Единицы в кодах теперь представляются наличием импульсов, нули - их отсутствием. При включении питания ключ 99 в закрытом состоянии. Порядок работы приемной стороны определяется сигналами управления с канала формирования управляющих сигналов, задающая роль принадлежит блоку 97 выделения ССИ. При каждом приходе на три входа блока 97 трех кодов из 9-и единиц ССИ на выходе блока 97 появляется строчный синхроимпульс ССИ, поступающий на первый вход синтезатора частот 98, по которым выполняется точная подстройка частоты в синтезаторе 98 частот, собственная стабильность частоты которого 10-6. Вторые входы синтезатора 98 частот подключены к второй группе выходов блока 73, при включении в котором выбранного канала передачи сигнал с соответствующего выхода блока 73 поступает в синтезатор 98 частот и определяет выход требуемой несущей частоты на третьи входы блоков 74, 87. Синтезатор 98 частот выдает: с первого выхода импульсы 6,25 МГц на сигнальный вход ключа 99 и на вторые управляющие входы декодеров 78, 83, 92, со второго выхода импульсы дискретизации 75 кГц сигнала звука, с третьего - синусоидальные колебания соответствующей несущей частоты, с четвертого - импульсы двойной частоты дискретизации 50 МГц на третьи управляющие входы входы накопителей 80, 85, 94 кодов кадра, с пятого - импульсы 25 МГц дискретизации на третьи входы декодеров 78, 83, 92 и на управляющие входы блоков 79, 84, 93 обработки кодов, с шестого - импульсы тактовой частоты 56,25 МГц на первые управляющие входы декодеров. С формирователей 77, 82, 91 импульсов коды поступают на информационные входы декодеров.

Работа декодеров 78, 83, 92 представлена на фиг.9.

Коды в последовательном виде поступают с частотой 6,25 МГц на информационный вход первого регистра 105, на первый /тактовый/ управляющий вход которого поступают импульсы 56,25 МГц, на второй оправляющий вход поступают сигналы Uвыд 6,25 МГц, на третий оправляющий вход поступают импульсы дискретизации 25 МГц. Заполняя девять разрядов регистра 105, код приобретает параллельный вид, в котором в дальнейшем и используется. С регистра 105 коды выдаются с частотой 6,25 МГц в накопитель 106 кодов кадра, который емкостью в 250×103 9-разрядных кодов. Накопитель принимает коды кадра, которые из него выдаются сигналами с ключа 115 с частотой 6,25 МГц. При закрытом состоянии ключа 115 накопитель 106 накапливает коды. Исходное состояние ключей в декодере: в блоке 110 закрытое, в блоке 108 открытое, ключей 113, 115, 116 открытое, ключа 114 закрытое. В 1-8 разряды второго регистра 107 поступают с первого по восьмой информационные сигналы кода, а при наличии в девятом разряде сигнала опознания кода числа равных кодов он поступает в 9-ый разряд регистра 107. С регистра 107 код выдается сигналом Uвыд с ключа 116 уже с частотой 25 МГц. Пока в регистр 107 поступают коды без сигнала, в девятом разряде они поступают через открытые ключи блока 108 в третий регистр 109, а с него выдаются Uвыд1 с ключа 113 на выход декодера. Сигнал Uвыд1 при выдаче кода обнуляет разряды регистра 109. При поступлении в регистр 107 кода с сигналом в девятом разряде сигнал с девятого разряда регистра 107 закрывает ключи в блоке 108 /вход 2/, закрывает ключи 113, 115, 116, открывает ключ 114 и ключи в блоке 110. Выдача кодов с регистра 107 прерывается, а накопитель 106 производит накопление кодов кадра, так как в него продолжают поступать коды. Код числа равных кодов через открытые ключи блока 110 поступает в вычитающий счетчик 111 импульсов, на счетный вход которого с ключа 114 поступают импульсы 25 МГц. Импульс с ключа 114 поступает и как сигнал Uвыд2 на второй управляющий вход регистра 109 и выдает содержащийся в нем код, но при этом не обнуляет его. Поэтому пока идет работа счетчика 111 на вычитание из регистра 109 выдается один и тот же код, эти коды являются изъятыми кодами при сжатии потока в кодере на передающей стороне. С выхода регистра 109 идет восстановленный на 100% поток кодов. С регистра 109 идут только 8-разрядные коды с дискретизацией уже 25 МГц в блок 79. По окончании вычитания в счетчике 111 в дешифратор 112 поступает код из нулей. С выхода дешифратора 112 сигнал одновременно: закрывает ключи в блоке 110, закрывает ключ 114, открывает ключи в блоке 108 и ключи 113, 115, 116. С накопителя 106 опять выдаются коды в регистр 107, с него через ключи в блоке 108 в регистр 109, процессы повторяются. Пропускная способность декодера определяется временем срабатывания 10,5 нс счетчика 111, который состоит из микросхем 100ИЕ137 [7, с.428], плюс время срабатывания дешифратора 112 6 нс из микросхемы 100ИД161 [7, с.433]. Скорость восстановления потока кодов до 50 Мбайт/с. Восставновленный поток кодов с частотой 25 МГц и числом отсчетов в строке 1000 штук /250×4/ поступает на вход блока 79 /84, 93/ обработки кодов, выполняющего удвоение числа отсчетов в строке /1000×2/. Удвоение выполняется получением промежуточных /средних/ кодов между каждым прошедшим и следующим за ним кодами. Блоки выполняют сложение предыдущего и последующего кодов и деление кода суммы на два. Причем деление выполняется без временных затрат: отбрасыванием младшего разряда в коде суммы /как это делается при делении десятичного числа на десять/ путем соответствующего подключения выходов сумматора 124 /фиг.10/ и выходов блоков 125, 126 регистров.

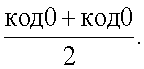

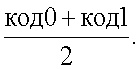

Разряд 0 означает перенос в старший разряд при сумме кодов. Удвоение отсчетов в строке сокращает период следования кодов в два раза, который равен 20 нс  т.е. 50 МГц. Процесс сложения двух 8-разрядных кодов должен занимать 20 нс. После включения питания в регистрах 120-123 нули. С приходом первого импульса 25 МГц в триггер 117 с его первого выхода сигнал Uвыд1 одновременно выдает "код 0" с регистра 121 на первые входы сумматора 124, из регистра 122 "код 0" в регистр 126 для хранения на 40 нс и через диоды на вторые входы сумматора 124, сигналы выдачи и обнуляют регистры, открывает ключи в блоке 118 на время прохода следующего кода через ключи, регистры 120, 121 заполняются кодом "код 1". В сумматоре идет сложение "код 0 + код 0". Сумматор из микросхем с временем сложения 20 нс. По окончании сложения код суммы идет на выход сумматора при этом делится на два, код №1

т.е. 50 МГц. Процесс сложения двух 8-разрядных кодов должен занимать 20 нс. После включения питания в регистрах 120-123 нули. С приходом первого импульса 25 МГц в триггер 117 с его первого выхода сигнал Uвыд1 одновременно выдает "код 0" с регистра 121 на первые входы сумматора 124, из регистра 122 "код 0" в регистр 126 для хранения на 40 нс и через диоды на вторые входы сумматора 124, сигналы выдачи и обнуляют регистры, открывает ключи в блоке 118 на время прохода следующего кода через ключи, регистры 120, 121 заполняются кодом "код 1". В сумматоре идет сложение "код 0 + код 0". Сумматор из микросхем с временем сложения 20 нс. По окончании сложения код суммы идет на выход сумматора при этом делится на два, код №1  Регистры 125, 126 хранят /задерживают/ коды на 40 нс, причем первая половина хранения приходится (20 нс) на процесс сложения в сумматоре 124. С приходом второго импульса в триггер 117 он обнуляет сумматор 124, а сигнал Uвыд2 со второго выхода триггера одновременно выдает с регистра 126 код №2 "код 0", с регистра 120 "код 1" в регистр 125 и через диоды в сумматор 124, с регистра 123 "код 0" в сумматор, открывает ключи в блоке 119, и регистры 122, 123 заполняются следующим кодом "код 2". В сумматоре идет сложение "код 0 + код 1", по окончания которого код суммы идет на выход сумматора с делением на два: код №3

Регистры 125, 126 хранят /задерживают/ коды на 40 нс, причем первая половина хранения приходится (20 нс) на процесс сложения в сумматоре 124. С приходом второго импульса в триггер 117 он обнуляет сумматор 124, а сигнал Uвыд2 со второго выхода триггера одновременно выдает с регистра 126 код №2 "код 0", с регистра 120 "код 1" в регистр 125 и через диоды в сумматор 124, с регистра 123 "код 0" в сумматор, открывает ключи в блоке 119, и регистры 122, 123 заполняются следующим кодом "код 2". В сумматоре идет сложение "код 0 + код 1", по окончания которого код суммы идет на выход сумматора с делением на два: код №3  С приходом третьего импульса на вход триггера 117 он обнуляет сумматор 124, а сигнал с его первого выхода Uвыд3 одновременно выдает из регистра 125 код №4 "код 1", выдает из регистра 121 "код 1" в сумматор, из регистра 122 выдает код "код 2" в регистр 126 на хранение и через диоды в сумматор 124, открывает ключи в блоке 118, и регистры 120, 121 заполняются кодом "код 3". В сумматоре идет сложение "код 1 + код 2", код суммы идет на выход сумматора с делением его на два: код №5

С приходом третьего импульса на вход триггера 117 он обнуляет сумматор 124, а сигнал с его первого выхода Uвыд3 одновременно выдает из регистра 125 код №4 "код 1", выдает из регистра 121 "код 1" в сумматор, из регистра 122 выдает код "код 2" в регистр 126 на хранение и через диоды в сумматор 124, открывает ключи в блоке 118, и регистры 120, 121 заполняются кодом "код 3". В сумматоре идет сложение "код 1 + код 2", код суммы идет на выход сумматора с делением его на два: код №5

С приходом четвертого импульса на вход триггера 117 он обнуляет сумматор, а сигнал со второго выхода триггера Uвыд4 одновременно выдает код №6 "код 2" из регистра 126, с регистра 120 "код 3" в регистр 125 и через диоды в сумматор 124, с регистра 123 "код 2" в сумматор 124, открывает ключи в блоке 119, регистры 122, 123 заполняются следующим кодом "код 4". В сумматоре идет сложение "код 3 + код 4”, затем код суммы идет на выход с делением его на два: код №7  С приходом пятого импульса в триггер 117 он обнуляет сумматор 124, а сигнал Uвыд5 с первого выхода триггера одновременно выдает с регистра 125 код №8 "код 3", выдает о регистра 121 "код 3" в сумматор, с регистра 122 "код 4" в регистр 126 на хранение и через диоды в сумматор, открывает ключи в блоке 118, регистры 120 и 121 заполняются кодом "код 5". Сумматор 124 выполняет сложение "код 3 + код 4", код суммы следует на выход с делением на два: код №9

С приходом пятого импульса в триггер 117 он обнуляет сумматор 124, а сигнал Uвыд5 с первого выхода триггера одновременно выдает с регистра 125 код №8 "код 3", выдает о регистра 121 "код 3" в сумматор, с регистра 122 "код 4" в регистр 126 на хранение и через диоды в сумматор, открывает ключи в блоке 118, регистры 120 и 121 заполняются кодом "код 5". Сумматор 124 выполняет сложение "код 3 + код 4", код суммы следует на выход с делением на два: код №9  С приходом шестого и следующих импульсов в триггер 117 протесы повторяются. Выходы 0-7 сумматора 124 и выходы 1-8 регистров 125, 126 поразрядно объединены и являются выходами блока 79. Коды с блоков 79, 84, 93 о частотой 50 МГц в параллельном виде поступают на информационные входы накопителей 80, 85, 94 кодов кадра.

С приходом шестого и следующих импульсов в триггер 117 протесы повторяются. Выходы 0-7 сумматора 124 и выходы 1-8 регистров 125, 126 поразрядно объединены и являются выходами блока 79. Коды с блоков 79, 84, 93 о частотой 50 МГц в параллельном виде поступают на информационные входы накопителей 80, 85, 94 кодов кадра.

Работа блоков 127 регистров представлена на фиг.11, 12.

Сигналы кодов в параллельном виде поступают на третьи входы разрядов регистров 1311-8 /фиг.12/. Заполнение регистров кодами строки начинаются с открытием сигналом кадра Uк 25 Гц первого ключа в первом блоке 1271 регистров. Импульсы частоты кадров Uк 25 Гц поступают в блоки 80, 85, 94 с выхода блоха 102 выделения КСИ.

Ключ 128 /фиг.12/ пропускает импульсы дискретизации 50 МГц на вход распределителя 130 импульсов, тактовые импульсы с которого последовательно поступают на первые входы разрядов восьми регистров 1311-8. По заполнению регистров 131 с последнего 2000-го выхода блока 130 сигнал Uз закрывает ключ 128 и в качестве управляющего выходного сигнала открывает ключ 128 в следующем блоке 1272 регистров, регистры которого заполняются кодами второй строки. За период кадра 40 мс заполняются последовательно регистры 131 всех блоков 127 регистров. С блока 1271000 регистров выходной сигнал поступает параллельно на четвертые управляющее входы блоков 127 /фиг.11/ и открывает в них синхронно вторые ключи 129, которые пропускают по одному сигналу Uвыд, который выдает из всех блоков 1271-1000 регистров коды кадра в свои формирователи 81, 86, 95 управляющих сигналов. Каждый накопитель 80, 85, 94 кодов кадра имеет 16×106 выходов /2000×8×1000/, которые подключены к стольким же входам в каждом из блоков 81, 86, 95, каждый из которых имеет в своем составе 2×106 преобразователей /2000×1000/ "код - число импульсов излучения". Выходы 6×106 от трех блоков 81, 86, 95 подключены к стольким же входам в СД-экране 96. Ввиду большого числа соединений лучшим вариантом для надежной работы приемной стороны будет исполнение накопителей кодов кадра и формирователей управляющих сигналов на тыльной стороне СД-экрана в единой с ним неразборной конструкции.

Работа системы

ФЭП 1 формирует матрицей ПЗИ 3 /фиг.1/ аналоговые видеосигналы R, G, В кадра, которые преобразуются АЦП 7, 8, 9 с частотой 25 МГц в 8-разрядные коды. Коды поступают в кодеры 14, 15, 16, выполняющие сжатие потока кодов в кадре с общим коэффициентом за период кадра 4. С кодеров сжатые потоки кодов сигналов R и G поступают в первый формирователь 17 кодов, сигнала В во второй формирователь 18 кодов, преобразующие параллельные коды в последовательные с заменой в них представления единиц с импульсов на положительные и отрицательные полусинусоиды моночастоты 56,25 МГц. Информация кодов сигналов R и G передается верхней боковой несущей, информация кодов сигнала В передается нижней боковой несущей. Приемная сторона принимает два радиосигнала двумя трактами приема и обработки кодов, производит детектирование, выделяет синхроимпульсы строк ССИ и кадров КСИ, представление единиц в кодах возвращает к импульсам. Декодеры 78, 83, 92 /фиг.7/ восстанавливают потоки кодов на 100%, затем следует удвоение отсчетов в каждой строке. За первый период кадра накопители 80, 85, 94 сосредотачивают все коды кадра, сигнал КСИ следующего кадра выдает из накопителей все коды кадра в формирователи 81, 86, 95 управляющих сигналов, которые преобразуют коды цветовых сигналов в число импульсов излучения светодиодов за период кадра. На СД-экране 96 воспроизводится видеорежим 2000×1000×25 Гц. В системе отсутствуют строчная и кадровая развертки. Два канала звукового сопровождения воспроизводят стереозвук. Заявляемая система выполняет разрешение формата НДТУ. Технические ее характеристики представлены в таблице 2.

Литература

1. "Домашний компьютер" №12, 2006, с.26-28, 32.

2. Патент №2214693 кл. H04N 11/11/24, бюл. 29 от 20.10.03, прототип.

3. В.И.Мураховсхий. Устройство компьютера. М, 2003, с.552.

4. Колесниченко О.В. Шишигин И.В. Аппаратные средства PC 5-е изд, СПб, 2004, с.832, 833, 835.

5. Радиопередающие устройства. М.С.Шумилин. М, 1981, с.234-235.

6. "Радио" №9, 2004, с.47.

7. Цифровые интегральные микросхемы. Минск, 1991, с.279, 272, 428, 433.

8. Бродский М.А. Телевизоры цветного изображения, Минск, 1988, с.132 рис.4.2

9. Радиосвязь, вещание, телевидение. Под ред. А.Д.Фортушенко, М, 1981, с.146.

| название | год | авторы | номер документа |

|---|---|---|---|

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2375841C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2384012C1 |

| СИСТЕМА ТЕЛЕВИДЕНИЯ | 2008 |

|

RU2368097C1 |

| ДВУХКАНАЛЬНАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2009 |

|

RU2413387C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2008 |

|

RU2369041C1 |

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2009 |

|

RU2402806C1 |

| СИСТЕМА СТЕРЕОТЕЛЕВИДЕНИЯ | 2010 |

|

RU2420025C1 |

| СПОСОБ ФОРМИРОВАНИЯ ОБЪЕМНОГО ИЗОБРАЖЕНИЯ И СИСТЕМА ТЕЛЕВИДЕНИЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2008 |

|

RU2384011C1 |

| УНИВЕРСАЛЬНАЯ СИСТЕМА ТЕЛЕВИДЕНИЯ | 2009 |

|

RU2410846C1 |

| ПЕРСОНАЛЬНЫЙ КОМПЬЮТЕР | 2009 |

|

RU2421771C1 |

Изобретение относится к технике радиосвязи и может быть использовано для цифрового телевещания в формате НДТУ. Техническими результатами являются упрощение фотоэлектрического преобразователя, снижение энергоемкости системы и увеличение яркости изображения, достигаемые тем, что в систему телевидения на передающей стороне вводятся три кодера, в фотоэлектрический преобразователь вводится матрица ПЗИ и передатчик выполняется двухканальным, на приемной стороне вводятся три декодера, три накопителя кодов кадра, три формирователя управляющих сигналов и устройство отображения видеоинформации представлено плоскопанельным светодиодным экраном. 21 ил., 2 табл.