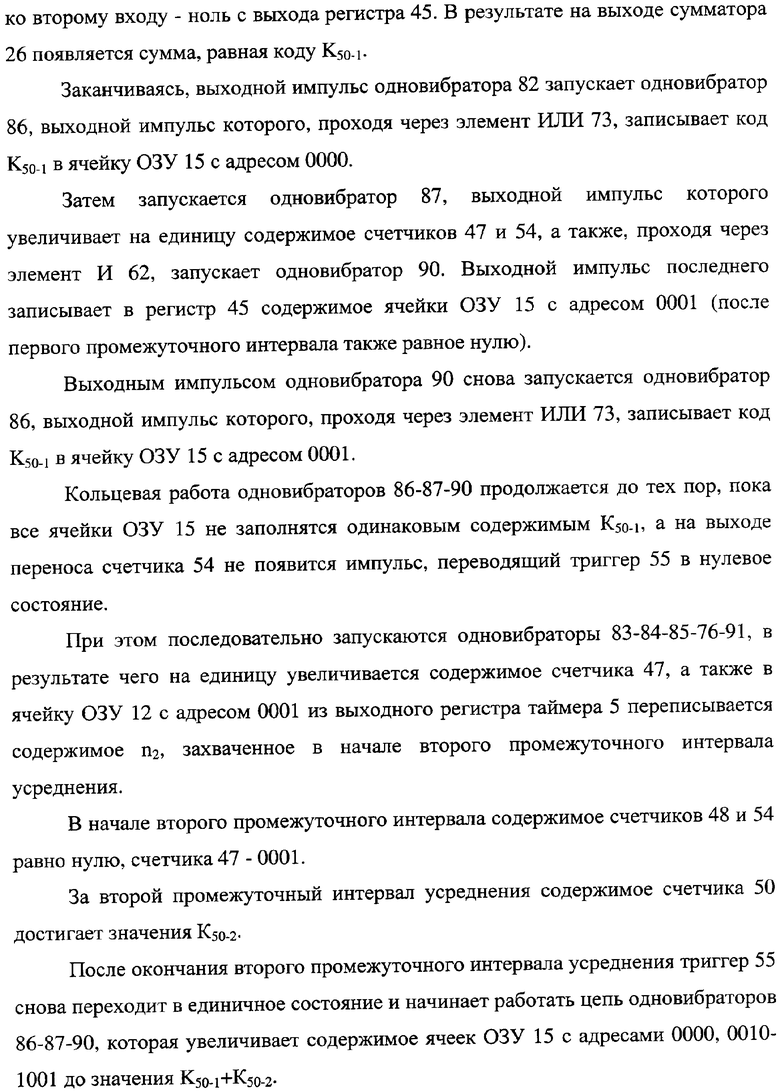

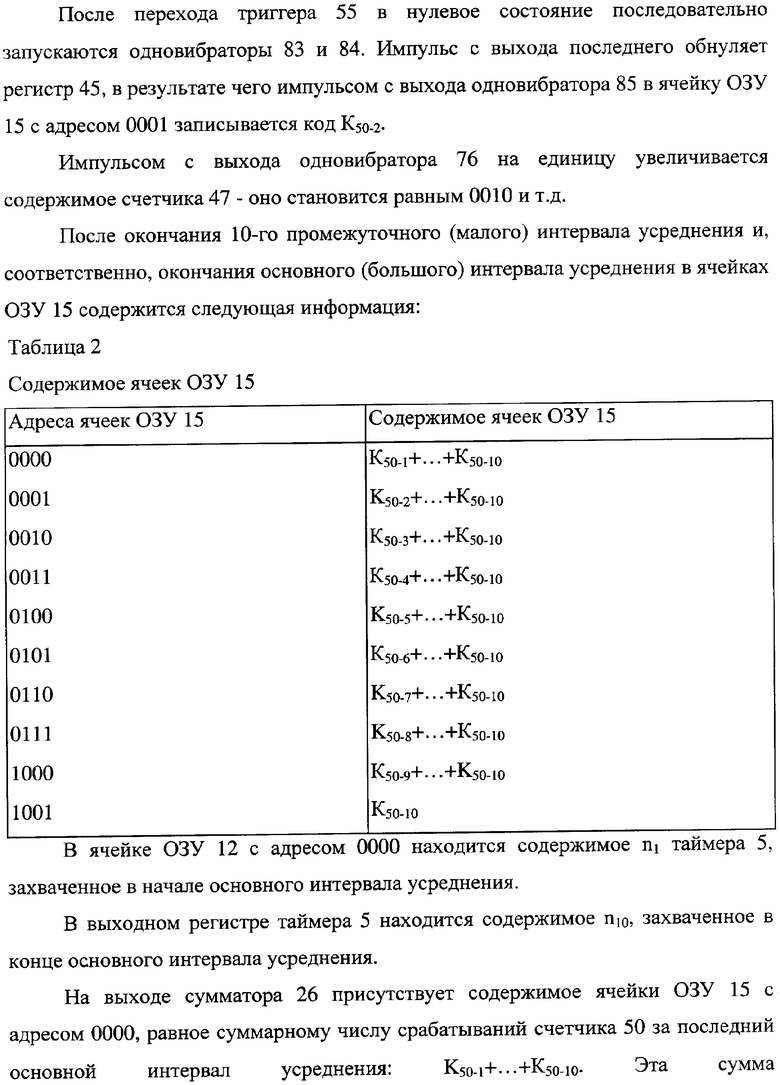

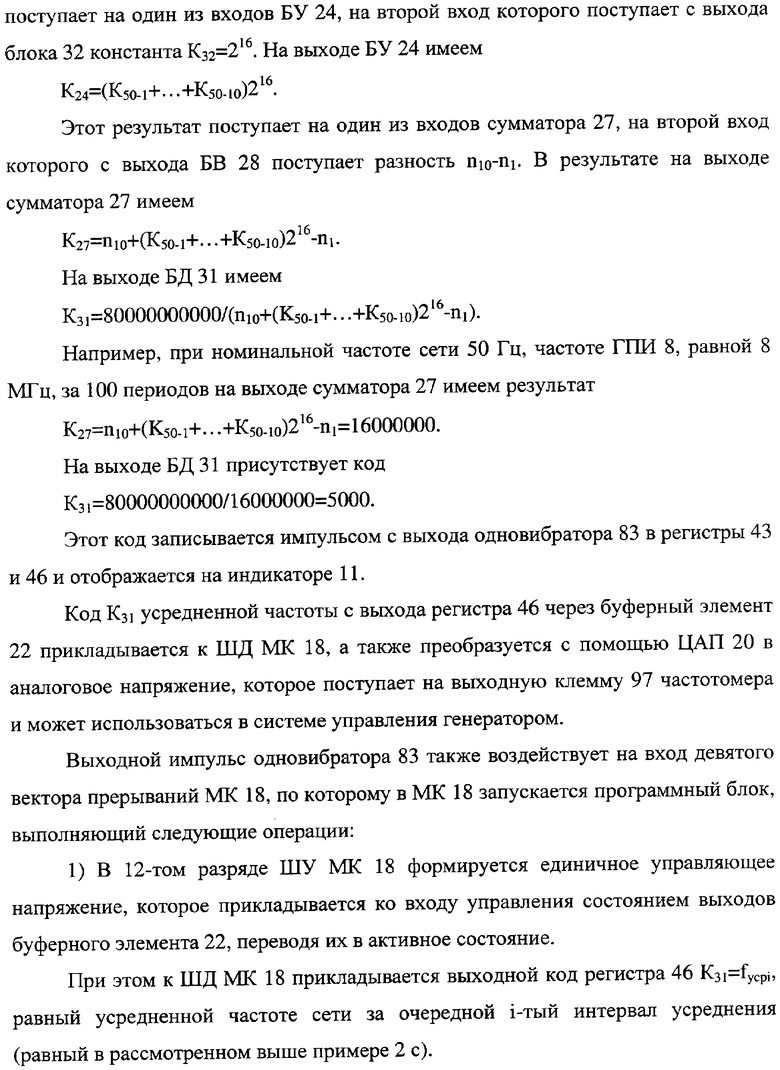

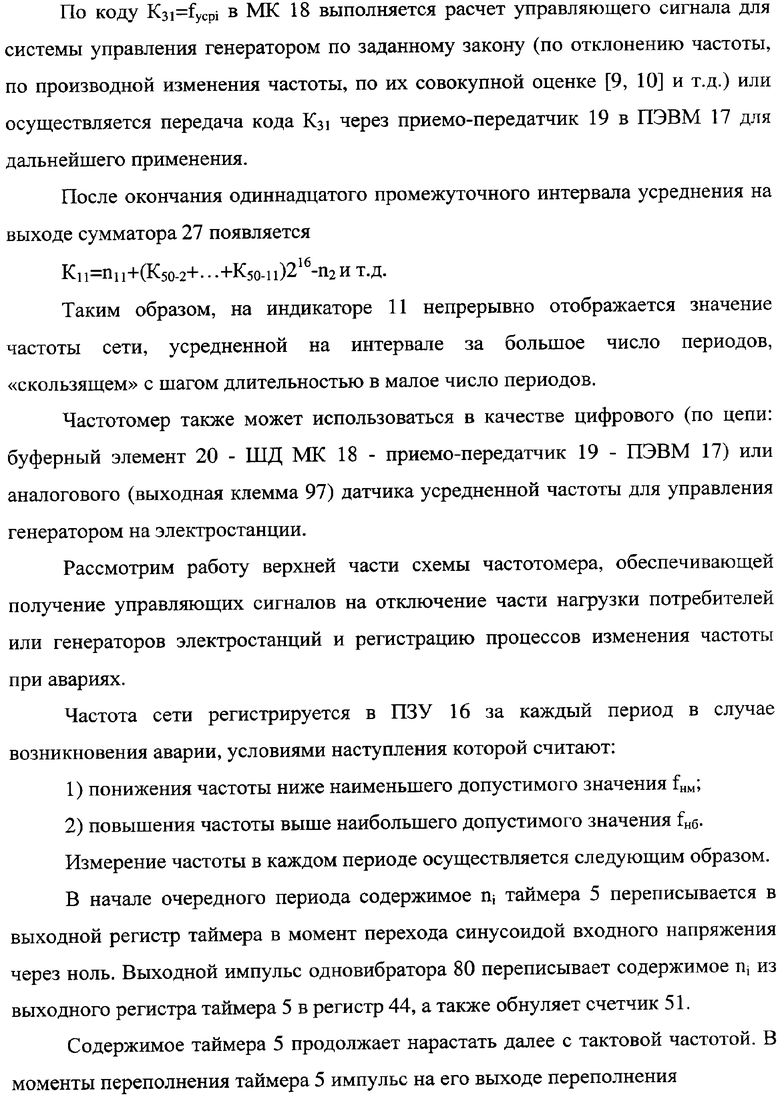

Текст описания приведен в факсимильном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362175C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2008 |

|

RU2380716C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

| ЧАСТОТОМЕР ДЛЯ ПРОМЫШЛЕННЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ | 2006 |

|

RU2326390C1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2326391C1 |

| РЕГИСТРАТОР АВАРИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ЭНЕРГОСИСТЕМ | 2009 |

|

RU2402067C1 |

| УСТРОЙСТВО ДЛЯ ПОВЕРКИ ИЗМЕРИТЕЛЕЙ ЧАСТОТЫ И ПЕРИОДА | 2009 |

|

RU2392633C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| СЧЕТЧИК РЕСУРСА СИЛОВОГО ТРАНСФОРМАТОРА | 2008 |

|

RU2384879C1 |

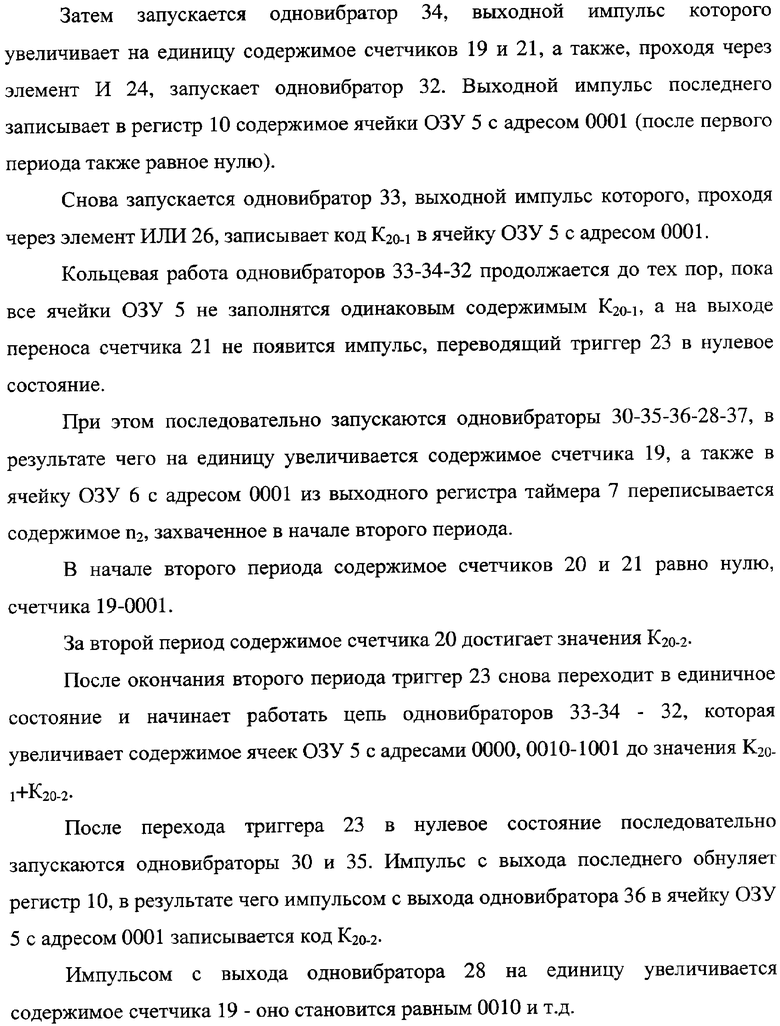

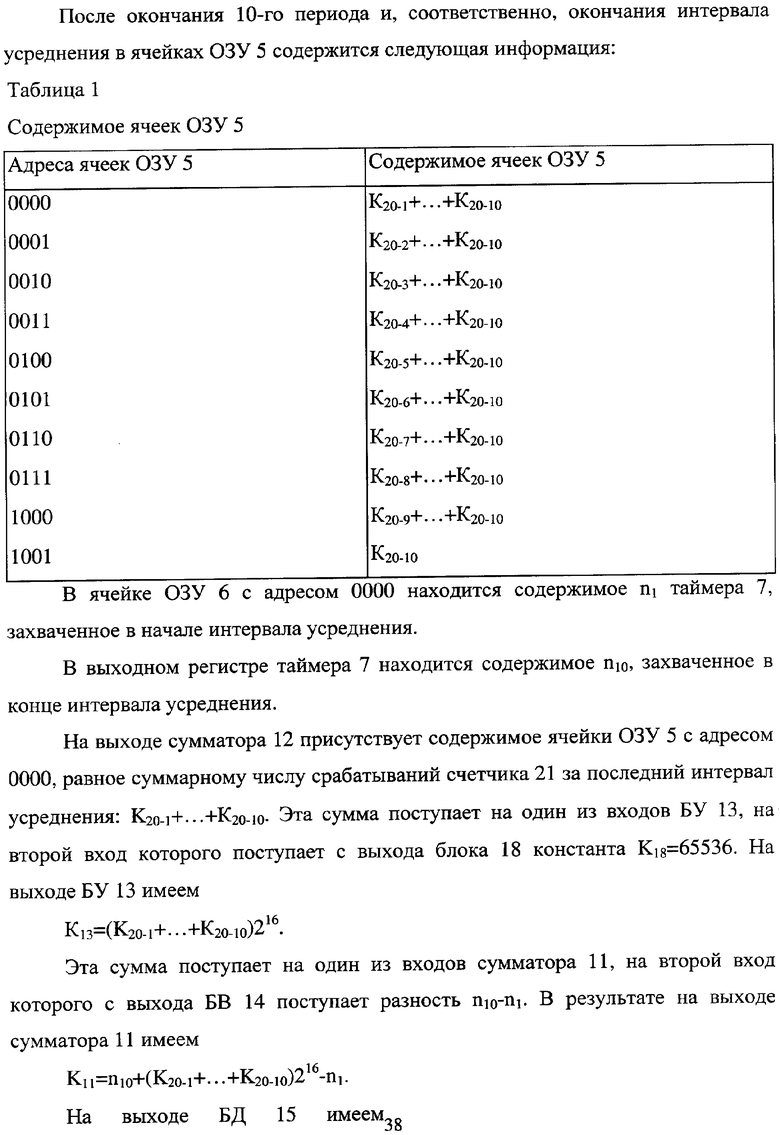

Группа заявленных изобретений (варианты) относится к области информационно-измерительной и вычислительной техники и может быть использована в электроэнергетике для контроля и регистрации значений частоты за каждый период, среднего значения и стандарта частоты за сутки и усредненных значений частоты в промышленных электрических сетях переменного тока с номинальной частотой 50 или 60 Гц, а также получения сигналов, управляющих системами управления генераторов, устройствами автоматической частотной разгрузки (АЧР) и автоматического ограничения частоты (АОЧ). 1) Первый вариант реализации частотомера содержит входную клемму (ВК), фильтр нижних частот (ФНЧ), аналоговый компаратор (АК), источник опорного напряжения (ИОН), одновибратор, счетчик, таймер, генератор прямоугольных импульсов (ГПИ), регистр, блок умножения (БУ), сумматор, блок вычитания (БВ), блок деления (БД), постоянное запоминающее устройство (ПЗУ), первый и второй блоки множителя (БМ), персональную электронную вычислительную машину (ПЭВМ), микроконтроллер (МК), приемопередатчик, таймер-часы; 2) второй вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, одновибратор, счетчик, таймер, ГПИ, регистр, БУ, сумматор, БВ, БД, ПЗУ, первый и второй БМ, ПЭВМ, МК, приемопередатчик, таймер-часы; 3) третий вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первое и второе ОЗУ, таймер, ГПИ, первый и второй регистры, первый и второй сумматоры, БУ, БВ, БД, индикатор, первый и второй БМ, первый - третий счетчики, шифратор из двоичного кода в двоично-десятичный (ШДКДД), триггер, элемент И, первый - третий элементы ИЛИ, первый - десятый одновибраторы, цифроаналоговый преобразователь (ЦАП), выходную клемму; 4) четвертый вариант реализации частотомера содержит первую и вторую ВК, ФНЧ, АК, ИОН, первое и второе ОЗУ, таймер, ГПИ, первый и второй регистры, первый и второй сумматоры, БУ, БВ, БД, индикатор, первый и второй БМ, первый - третий счетчики, ШДКДД, триггер, элемент И, первый - третий элементы ИЛИ, первый - десятый одновибраторы, ЦАП, буферный элемент (БЭ), выходную одноразрядную клемму, выходную многоразрядную клемму; 5) пятый вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый - третий таймеры, ГПИ, таймер-часы, ШДКДД, индикатор, первое - четвертое ОЗУ, ПЗУ, ПЭВМ, МК, приемопередатчик, ЦАП, первый и второй БЭ, первый и второй БУ, первый - третий сумматоры, первый и второй БВ, первый и второй БД, первый - третий БМ, первый и второй блоки задания кодов наибольшей частоты, первый и второй блоки задания кодов наименьшей частоты, первый - четвертый числовые компараторы, первый - четвертый регистры, первый - восьмой счетчики, первый - третий триггеры, первый - четвертый усилители мощности, первый - седьмой элементы И, первый - седьмой элементы ИЛИ, первый - семнадцатый одновибраторы, первую - пятую выходные клеммы; 6) шестой вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый - третий одновибраторы, ГПИ, таймер, первый и второй регистры, первый и второй БМ, БУ, сумматор, БВ, БД, первый и второй счетчики, индикатор, D-триггер, элементы И и НЕ, двухпозиционный переключатель. Технический результат - расширение функциональных возможностей за счет возможности текущего контроля частоты в промышленных электрических сетях, регистрации среднего значения и стандарта частоты за сутки, процессов изменения частоты при авариях и на интервалах времени, предшествующих аварии, а также получения сигналов, управляющих устройствами автоматической частотной разгрузки, автоматического ограничения частоты и системами управления генераторов, упрощение схемы устройства, повышение его быстродействия и точности. 6 н.п. ф-лы, 6 ил.

1. Частотомер для энергосистем и электростанций, предназначенный для регистрации частоты за каждый период контролируемого напряжения ответственных производителей и потребителей электроэнергии, содержащий входную клемму, аналоговый компаратор, одновибратор, генератор прямоугольных импульсов, счетчик, регистр, отличающийся тем, что в него дополнительно введены персональная электронная вычислительная машина, микроконтроллер, приемопередатчик, постоянное запоминающее устройство, источник опорного напряжения, таймер, таймер-часы, сумматор, блок умножения, блок вычитания, блок деления, первый и второй блоки множителя, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом одновибратора, выход которого соединен с входом первого вектора прерываний микроконтроллера и входом захвата таймера, тактовый вход которого объединен с тактовыми входами микроконтроллера и таймера-часов и подключен к выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через регистр с входом вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с шиной данных микроконтроллера, с которой также связаны информационный выход таймера-часов, а также информационные вход и выход постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, к которой также подключены вход управления записью регистра, вход установки нуля счетчика и входы управления состоянием выходов постоянного запоминающего устройства и таймера-часов, выход суточных импульсов которого соединен с входом второго вектора прерываний микроконтроллера, информационный выход которого через шину данных связан с входом приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины.

2. Частотомер для энергосистем и электростанций, предназначенный для регистрации частоты за каждый период контролируемого напряжения ответственных производителей и потребителей электроэнергии, содержащий входную клемму, аналоговый компаратор, одновибратор, генератор прямоугольных импульсов, счетчик, регистр, отличающийся тем, что в него дополнительно введены персональная электронная вычислительная машина, микроконтроллер, приемопередатчик, постоянное запоминающее устройство, источник опорного напряжения, таймер, таймер-часы, сумматор, блок умножения, блок вычитания, блок деления, первый и второй блоки множителя, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом одновибратора, выход которого соединен с входом первого вектора прерываний микроконтроллера и входом захвата таймера, тактовый вход которого объединен с тактовыми входами микроконтроллера и таймера-часов и подключен к выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через регистр с входом вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с шиной данных микроконтроллера, с которой также связаны информационный выход таймера-часов, а также информационные вход и выход постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, к которой также подключены вход управления записью регистра, вход установки нуля счетчика и входы управления состоянием выходов постоянного запоминающего устройства и таймера-часов, выходы суточных, часовых, минутных и секундных импульсов которого соединены соответственно с входами второго-пятого векторов прерываний микроконтроллера, информационный выход которого через шину данных связан с входом приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины.

3. Частотомер для энергосистем и электростанций, предназначенный для контроля частоты, усредненной на интервале, «скользящем» с шагом длительностью в один период, а также получения управляющих сигналов системами управления генераторов, содержащий входную клемму, аналоговый компаратор, генератор прямоугольных импульсов, первый-третий счетчики, первый регистр, первое и второе оперативные запоминающие устройства, триггер, первый-пятый одновибраторы, элемент И, первый-третий элементы ИЛИ, первый вход которого подключен к выходу первого одновибратора, а выход соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, вход управления записью которого подключен к выходу второго элемента ИЛИ, выход переноса третьего счетчика соединен с входом установки нуля триггера, прямой выход которого соединен с первым входом элемента И, отличающийся тем, что в него дополнительно введены цифроаналоговый преобразователь, шифратор из двоичного кода в двоично-десятичный, выходная клемма, таймер, второй регистр, блок вычитания, блок умножения, блок деления, первый и второй сумматоры, первый и второй блоки множителя, источник опорного напряжения, шестой-десятый одновибраторы, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом второго одновибратора, выход которого соединен с входом установки единицы триггера и входом захвата таймера, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, а информационный выход соединен с объединенными входом уменьшаемого блока вычитания и информационным входом второго оперативного запоминающего устройства, адресный вход которого подключен к информационному выходу первого счетчика, а информационный выход соединен с входом вычитаемого блока вычитания, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к выходу блока умножения, а выход соединен с входом делителя блока деления, вход делимого которого подключен к выходу первого блока множителя, а выход соединен с информационным входом первого регистра, информационный выход которого соединен с объединенными информационными входами цифроаналогового преобразователя и шифратора из двоичного кода в двоично-десятичный, выход которого соединен с информационным входом индикатора, аналоговый выход цифроаналогового преобразователя соединен с выходной клеммой, выход переполнения таймера соединен с тактовым входом второго счетчика, вход установки нуля которого подключен к выходу первого одновибратора, а информационный выход соединен с первым входом второго сумматора, второй вход которого через второй регистр подключен к информационному выходу первого оперативного запоминающего устройства, а выход соединен с объединенными информационным входом первого оперативного запоминающего устройства и первым входом блока умножения, второй вход которого подключен к выходу второго блока множителя, выходы триггера соединены инверсный - с входом третьего одновибратора, прямой - с входом четвертого одновибратора, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу пятого одновибратора, инверсный вход которого подключен к выходу элемента И, выход первого элемента ИЛИ соединен с входом управления записью второго регистра и инверсным входом шестого одновибратора, выход которого соединен с первым входом второго элемента ИЛИ и инверсным входом седьмого одновибратора, выход которого соединен с объединенными вторыми входами элемента И и третьего элемента ИЛИ, а также тактовым входом третьего счетчика, выход третьего одновибратора соединен с входом управления записью первого регистра и инверсным входом восьмого одновибратора, выход которого соединен с входом установки нуля второго регистра и инверсным входом девятого одновибратора, выход которого соединен с объединенными вторым входом второго элемента ИЛИ и инверсным входом первого одновибратора, выход которого через десятый одновибратор соединен с входом управления записью второго оперативного запоминающего устройства.

4. Частотомер для энергосистем и электростанций, предназначенный для контроля частоты, усредненной на интервале, «скользящем» с шагом длительностью в один период, а также получения управляющих сигналов системами управления генераторов, содержащий первую входную клемму, аналоговый компаратор, генератор прямоугольных импульсов, первый-третий счетчики, первый регистр, первое и второе оперативные запоминающие устройства, триггер, первый-пятый одновибраторы, элемент И, первый-третий элементы ИЛИ, первый вход которого подключен к выходу первого одновибратора, а выход соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, вход управления записью которого подключен к выходу второго элемента ИЛИ, выход переноса третьего счетчика соединен с входом установки нуля триггера, прямой выход которого соединен с первым входом элемента И, отличающийся тем, что в него дополнительно введены цифроаналоговый преобразователь, шифратор из двоичного кода в двоично-десятичный, буферный элемент, вторая входная клемма, одноразрядная и многоразрядная выходные клеммы, таймер, второй регистр, блок вычитания, блок умножения, блок деления, первый и второй сумматоры, первый и второй блоки множителя, источник опорного напряжения, шестой-десятый одновибраторы, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом второго одновибратора, выход которого соединен с входом установки единицы триггера и входом захвата таймера, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, а информационный выход соединен с объединенными входом уменьшаемого блока вычитания и информационным входом второго оперативного запоминающего устройства, адресный вход которого подключен к информационному выходу первого счетчика, а информационный выход соединен с входом вычитаемого блока вычитания, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к выходу блока умножения, а выход соединен с входом делителя блока деления, вход делимого которого подключен к выходу первого блока множителя, а выход соединен с информационным входом первого регистра, информационный выход которого соединен с объединенными информационными входами цифроаналогового преобразователя, буферного элемента и шифратора из двоичного кода в двоично-десятичный, выход которого соединен с информационным входом индикатора, аналоговый выход цифроаналогового преобразователя соединен с одноразрядной выходной клеммой, выход буферного элемента соединен с многоразрядной выходной клеммой, вход управления состоянием выходов буферного элемента подключен ко второй входной клемме, выход переполнения таймера соединен с тактовым входом второго счетчика, вход установки нуля которого подключен к выходу первого одновибратора, а информационный выход соединен с первым входом второго сумматора, второй вход которого через второй регистр подключен к информационному выходу первого оперативного запоминающего устройства, а выход соединен с объединенными информационным входом первого оперативного запоминающего устройства и первым входом блока умножения, второй вход которого подключен к выходу второго блока множителя, выходы триггера соединены инверсный - с входом третьего одновибратора, прямой - с входом четвертого одновибратора, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу пятого одновибратора, инверсный вход которого подключен к выходу элемента И, выход первого элемента ИЛИ соединен с входом управления записью второго регистра и инверсным входом шестого одновибратора, выход которого соединен с первым входом второго элемента ИЛИ и инверсным входом седьмого одновибратора, выход которого соединен с объединенными вторыми входами элемента И и третьего элемента ИЛИ, а также тактовым входом третьего счетчика, выход третьего одновибратора соединен с входом управления записью первого регистра и инверсным входом восьмого одновибратора, выход которого соединен с входом установки нуля второго регистра и инверсным входом девятого одновибратора, выход которого соединен с объединенными вторым входом второго элемента ИЛИ и инверсным входом первого одновибратора, выход которого через десятый одновибратор соединен с входом управления записью второго оперативного запоминающего устройства.

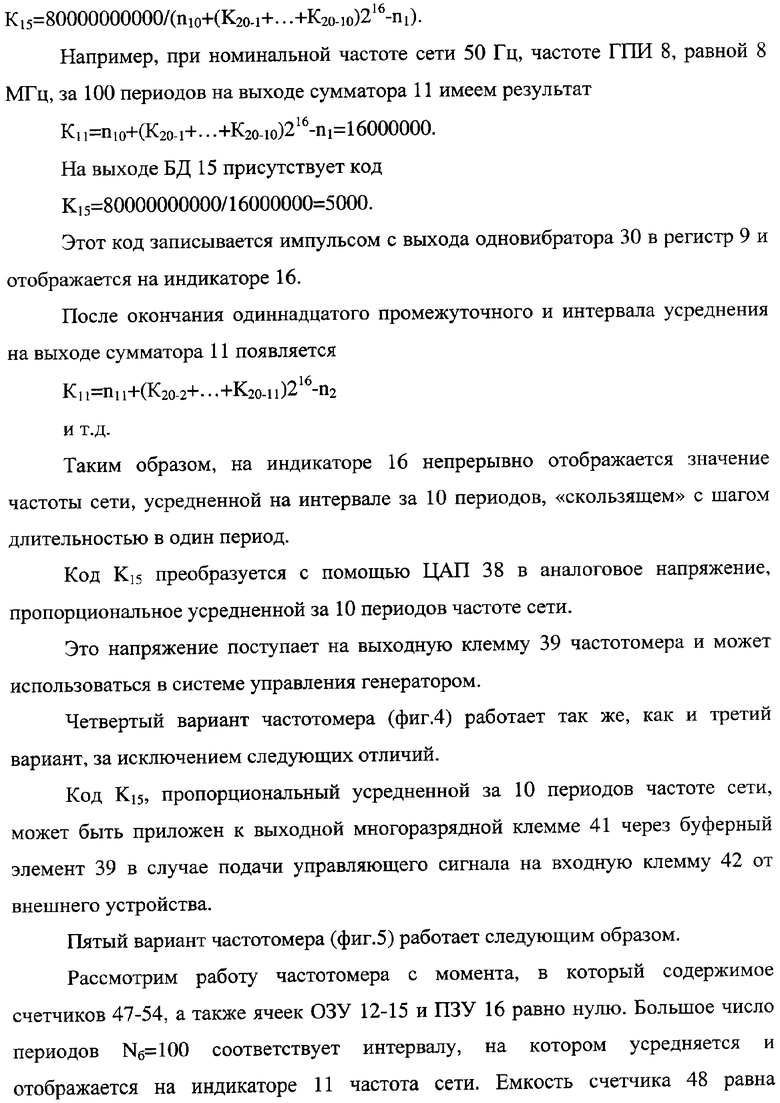

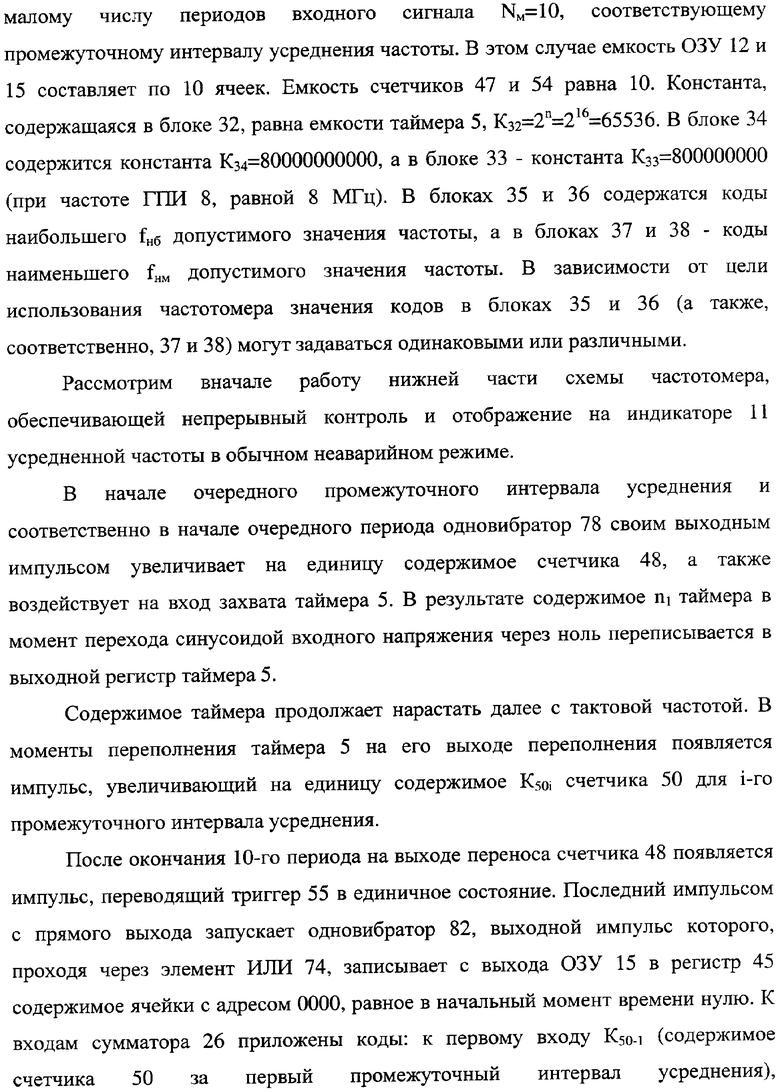

5. Частотомер для энергосистем и электростанций, предназначенный для получения управляющих сигналов системами управления генераторов и на отключение части нагрузки потребителей или генераторов электростанций, регистрации среднего значения и стандарта частоты за сутки, процессов изменения частоты при авариях, а также контроля частоты, усредненной на интервале за большое число периодов, «скользящем» с шагом длительностью в малое число периодов, содержащий входную клемму, первый-третий триггеры, аналоговый компаратор, первый регистр, генератор прямоугольных импульсов, первое и второе оперативные запоминающие устройства, первый-четвертый счетчики, индикатор, первый-пятый одновибраторы, первый-пятый элементы И, первый-четвертый элементы ИЛИ, первый регистр, информационный выход которого соединен с информационным входом индикатора, выход первого одновибратора через первый элемент ИЛИ соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, выход переноса второго счетчика соединен с входом установки единицы первого триггера, прямой выход которого соединен с первым входом первого элемента И, вход установки нуля второго триггера подключен к инверсному выходу второго одновибратора, инверсный вход которого подключен к выходу переноса третьего счетчика, информационный выход первого регистра соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены третье и четвертое оперативные запоминающие устройства, постоянное запоминающее устройство, источник опорного напряжения, персональная электронная вычислительная машина, микроконтроллер, приемопередатчик, первый-третий таймеры, таймер-часы, первый-третий сумматоры, первый и второй блоки умножения, первый и второй блоки вычитания, первый и второй блоки деления, первый-третий блоки множителя, первый-четвертый числовые компараторы, первый и второй блоки задания кодов наибольшей частоты, первый и второй блоки задания кодов наименьшей частоты, второй-четвертый регистры, шестой-семнадцатый одновибраторы, пятый-восьмой счетчики, пятый-седьмой элементы ИЛИ, первый-четвертый усилители мощности, первая-пятая выходные клеммы, шестой и седьмой элементы И, шифратор из двоичного кода в двоично-десятичный, первый и второй буферные элементы, цифроаналоговый преобразователь, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом третьего одновибратора, выход которого соединен с инверсным входом четвертого одновибратора и входом захвата первого таймера, тактовый вход которого объединен с тактовыми входами микроконтроллера и таймера-часов и подключен к первому выходу генератора прямоугольных импульсов, третий выход которого соединен с первым входом второго элемента И, информационный выход первого таймера соединен с объединенными входом уменьшаемого первого блока вычитания, информационным входом первого оперативного запоминающего устройства, первым входом первого сумматора и через второй регистр с входом вычитаемого второго блока вычитания, выход переполнения первого таймера соединен с тактовыми входами четвертого и пятого счетчиков, информационный выход последнего соединен с первым входом первого блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом первого сумматора, выход которого соединен с входом уменьшаемого второго блока вычитания, выход которого соединен с входом делителя первого блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с объединенными информационными входами второго оперативного запоминающего устройства и первого буферного элемента и первыми входами первого и второго числовых компараторов, вторые входы которых подключены соответственно к выходам первых блоков задания кодов наибольшей и наименьшей частот, выход "А>В" первого числового компаратора и выход "А<В" второго числового компаратора (где А и В - соответственно коды двоичных чисел на первом и втором входах числовых компараторов) соединены через второй элемент ИЛИ с объединенными входами захвата таймера-часов, первого вектора прерываний микроконтроллера, установки нуля третьего и шестого счетчиков, выход четвертого одновибратора соединен с объединенными входом седьмого вектора прерываний микроконтроллера, входом управления записью второго оперативного запоминающего устройства, первым входом четвертого элемента ИЛИ и инверсным входом пятого одновибратора, выход которого соединен с объединенными входом установки нуля пятого счетчика, входом управления записью второго регистра и первым входом третьего элемента ИЛИ, второй вход которого связан с тактовым входом третьего счетчика и выходом шестого одновибратора, а выход соединен с объединенными тактовыми входами шестого и седьмого счетчиков, информационный выход которого соединен с адресным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, к которой также подключены объединенные информационные вход и выход постоянного запоминающего устройства, информационные выходы первого и второго буферных элементов, выход таймера-часов, выход микроконтроллера и вход приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины, информационный выход первого счетчика соединен с адресным входом четвертого оперативного запоминающего устройства, информационный вход которого подключен к выходу второго сумматора, а информационный выход через третий регистр соединен с первым входом второго сумматора, второй вход которого подключен к выходу четвертого счетчика, а выход соединен с первым входом второго блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с первым входом третьего сумматора, информационный выход первого оперативного запоминающего устройства соединен с входом вычитаемого первого блока вычитания, выход которого через третий сумматор соединен с входом делителя второго блока деления, вход делимого которого подключен к выходу третьего блока множителя, а выход соединен с объединенными первыми входами третьего и четвертого числовых компараторов, информационным входом четвертого регистра и входом шифратора из двоичного кода в двоично-десятичный, выход которого через первый регистр соединен с информационным входом индикатора, информационный выход четвертого регистра соединен с объединенными информационными входами второго буферного элемента и цифроаналогового преобразователя, аналоговый выход которого соединен с пятой выходной клеммой, выходы первого триггера соединены прямой - с входом седьмого одновибратора, инверсный - через восьмой одновибратор с объединенными входами управления записью первого и четвертого регистров, входом девятого вектора прерываний микроконтроллера и инверсным входом девятого одновибратора, выход которого соединен с входом установки нуля третьего регистра и инверсным входом десятого одновибратора, выход которого соединен с первым входом пятого элемента ИЛИ и инверсным входом первого одновибратора, выход которого соединен с входом установки нуля четвертого счетчика и инверсным входом шестнадцатого одновибратора, выход которого соединен с входом управления записью первого оперативного запоминающего устройства, выход седьмого одновибратора через шестой элемент ИЛИ соединен с входом управления записью третьего регистра и инверсным входом одиннадцатого одновибратора, выход которого соединен с вторым входом пятого элемента ИЛИ и инверсным входом двенадцатого одновибратора, выход которого соединен с объединенными вторыми входами первого элемента И и первого элемента ИЛИ, а также с тактовым входом восьмого счетчика, выход переноса которого соединен с входом установки нуля первого триггера, выход пятого элемента ИЛИ соединен с входом управления записью четвертого оперативного запоминающего устройства, второй выход генератора прямоугольных импульсов соединен с вторым входом седьмого элемента И, выход которого соединен с тактовым входом третьего триггера, выходы которого соединены соответственно с входами шестого и тринадцатого одновибраторов, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого через четырнадцатый одновибратор соединен с входом управления записью третьего оперативного запоминающего устройства, выход переноса шестого счетчика соединен с входом второго вектора прерываний микроконтроллера, адресная шина которого соединена с объединенными адресными входами третьего оперативного запоминающего устройства и постоянного запоминающего устройства, вход управления записью которого подключен к шине управления микроконтроллера, к которой также подключены вход установки единицы второго триггера и входы управления состоянием выходов первого и второго буферных элементов, постоянного запоминающего устройства, таймера-часов, шестого счетчика и третьего оперативного запоминающего устройства, входы первого-четвертого усилителей мощности, выходы которых соединены соответственно с первой-четвертой выходными клеммами, выход суточных импульсов таймера-часов соединен с входом восьмого вектора прерываний микроконтроллера, выход первого элемента И через пятнадцатый одновибратор соединен с вторым входом шестого элемента ИЛИ, вторые входы третьего и четвертого числовых компараторов подключены соответственно к выходам вторых блоков задания кодов наибольшей и наименьшей частот, выход "А>В" третьего числового компаратора и выход "А<В" четвертого числового компаратора соединены через седьмой элемент ИЛИ с объединенными инверсным входом семнадцатого одновибратора и вторым входом второго элемента И, выход которого соединен с объединенными тактовыми входами второго и третьего таймеров, выходы переполнения которых соединены соответственно попарно с первыми входами третьего и четвертого элементов И, а также пятого и шестого элементов И, выход семнадцатого одновибратора соединен с объединенными входами установки нуля второго и третьего таймеров, выход "А>В" третьего числового компаратора соединен с вторыми входами пятого и четвертого элементов И, выход которого соединен с входом четвертого вектора прерываний микроконтроллера, вход шестого вектора прерываний которого подключен к выходу пятого элемента И, выход "А<В" четвертого числового компаратора соединен с вторыми входами шестого и третьего элементов И, выход которого соединен с входом третьего вектора прерываний микроконтроллера, вход пятого вектора прерываний которого подключен к выходу шестого элемента И.

6. Частотомер для энергосистем и электростанций, предназначенный для контроля частоты, усредненной на примыкающих интервалах времени за фиксированное число периодов, содержащий входную клемму, генератор прямоугольных импульсов, аналоговый компаратор, индикатор, первый и второй счетчики, первый-третий одновибраторы, первый регистр, информационный выход которого соединен с информационным входом индикатора, выход переноса первого счетчика соединен с инверсным входом второго одновибратора, отличающийся тем, что в него дополнительно введены таймер, D-триггер, элементы И и НЕ, двухпозиционный переключатель, сумматор, блок умножения, блок вычитания, блок деления, первый и второй блоки множителя, источник опорного напряжения, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом первого одновибратора, выход которого соединен с тактовым входом первого счетчика и входом захвата таймера, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через второй регистр с входов вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом второго счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с объединенными информационным входом второго блока множителя и входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с информационным входом первого регистра, вход управления записью которого объединен с первым входом элемента И и подключен к выходу переноса первого счетчика, выход второго одновибратора соединен с объединенными входом управления записью второго регистра, входом установки нуля второго счетчика и тактовым входом D-триггера, информационный вход которого подключен к шине единичного потенциала, а прямой выход соединен с вторым входом элемента И, третий вход которого объединен с входам третьего одновибратора и подключен к выходу элемента НЕ, вход которого через контакты двухпозиционного переключателя соединен с шинами нулевого и единичного потенциала, выход элемента И соединен с вводом управления записью второго блока множителя, инверсный выход третьего одновибратора соединен с входом установки нуля D-триггера.

| АЛЕКСЕЕВ В.С., ВАРГАНОВ Г.П., ПАНФИЛОВ Б.И., РОЗЕНБЛЮМ Ф.М | |||

| Реле защиты | |||

| - М.: Энергия, 1976 | |||

| Цифровой измеритель частоты | 1983 |

|

SU1290190A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ СИНУСОИДАЛЬНОГО СИГНАЛА | 1999 |

|

RU2169927C1 |

| Способ определения угла естественного откоса сыпучих материалов и устройство для его осуществления | 1986 |

|

SU1401250A1 |

Авторы

Даты

2009-07-20—Публикация

2007-10-12—Подача