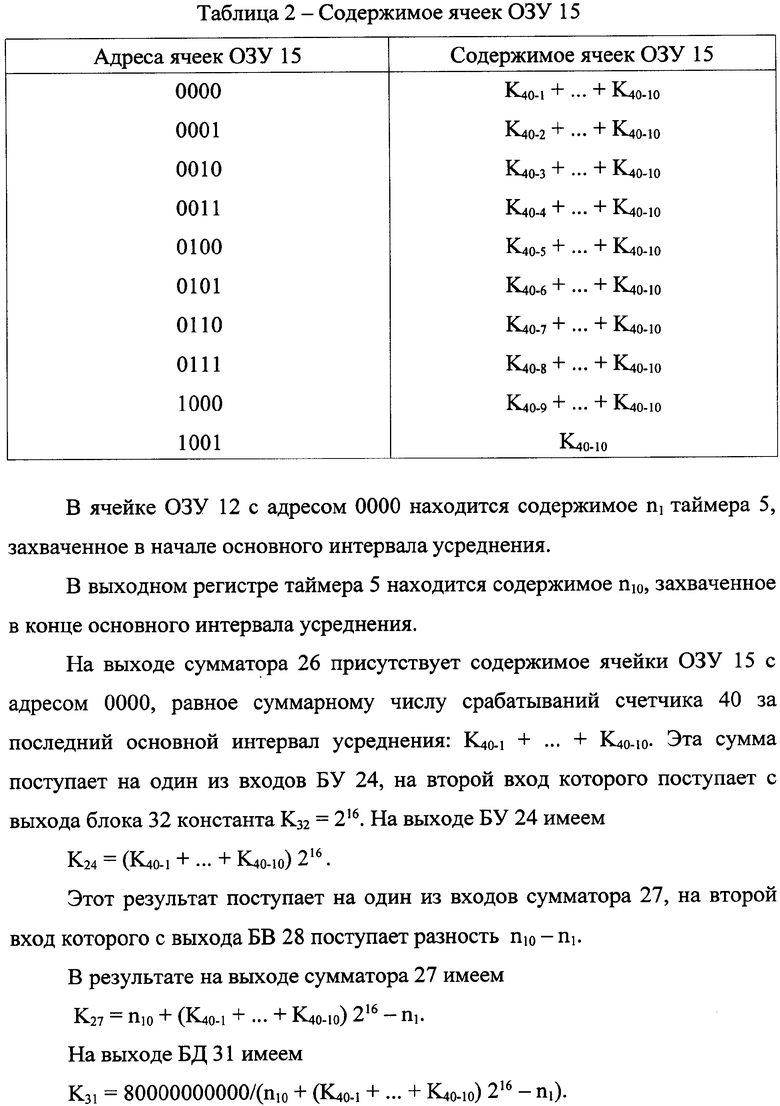

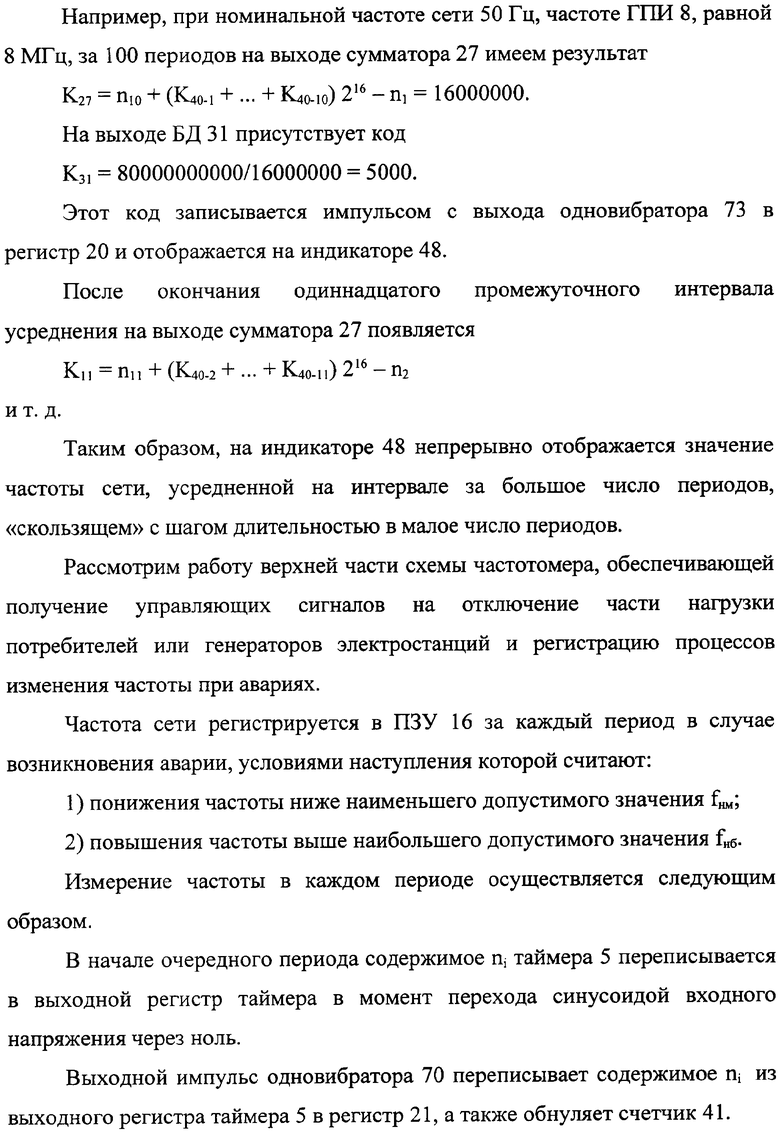

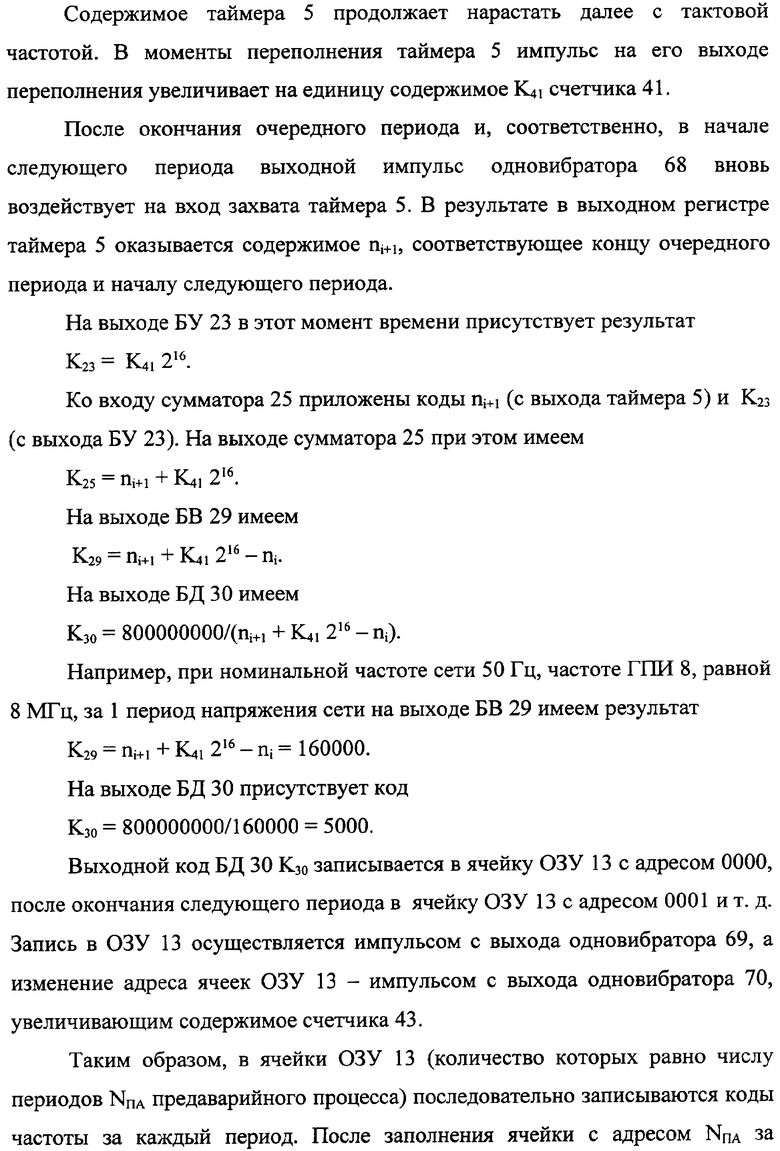

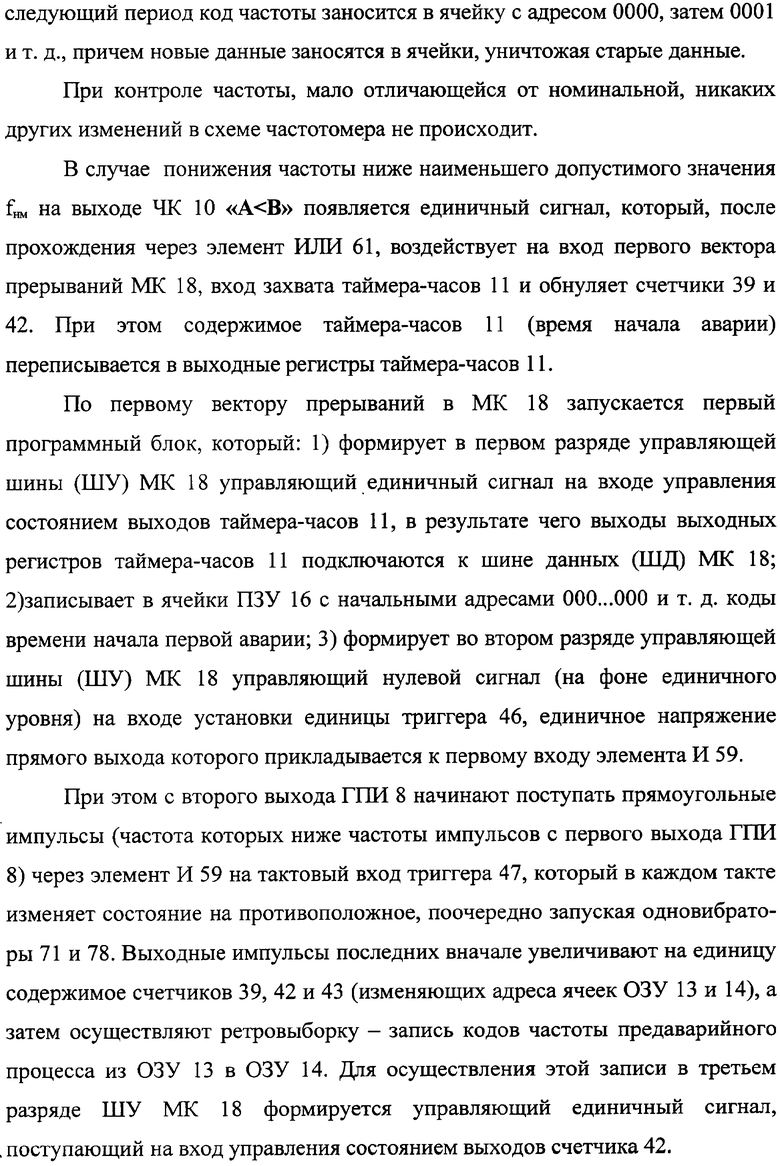

Текст описания приведен в факсимильном виде.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЧАСТОТОМЕР ДЛЯ ЭНЕРГОСИСТЕМ И ЭЛЕКТРОСТАНЦИЙ ЕРМАКОВА-ФЕДОРОВА (ВАРИАНТЫ) | 2007 |

|

RU2362174C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ КОРРЕКЦИИ ПОГРЕШНОСТИ ЧАСТОТЫ ТАКТОВОГО ГЕНЕРАТОРА МИКРОКОНТРОЛЛЕРА (ВАРИАНТЫ) | 2008 |

|

RU2390786C1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2008 |

|

RU2380716C1 |

| ЧАСТОТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2326391C1 |

| ЧАСТОТОМЕР ДЛЯ ПРОМЫШЛЕННЫХ ЭЛЕКТРИЧЕСКИХ СЕТЕЙ | 2006 |

|

RU2326390C1 |

| РЕГИСТРАТОР АВАРИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ЭНЕРГОСИСТЕМ | 2009 |

|

RU2402067C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| УСТРОЙСТВО ДЛЯ ПОВЕРКИ ИЗМЕРИТЕЛЕЙ ЧАСТОТЫ И ПЕРИОДА | 2009 |

|

RU2392633C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ | 2008 |

|

RU2381549C2 |

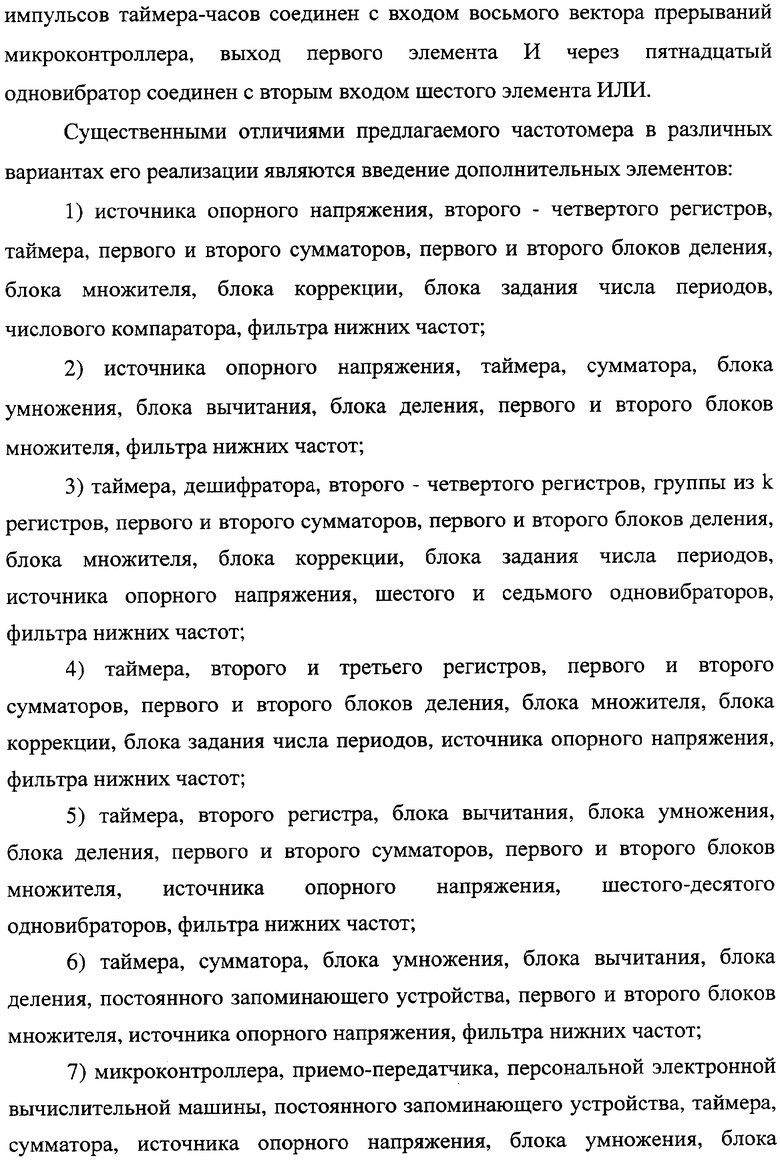

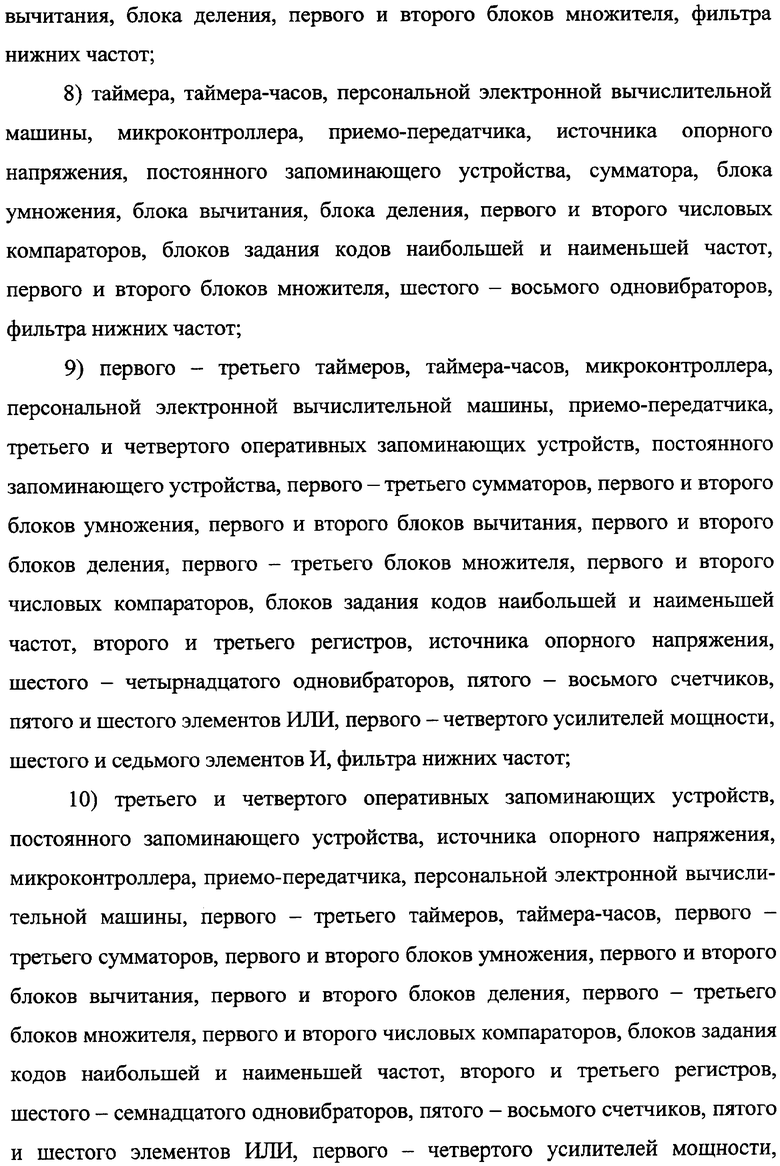

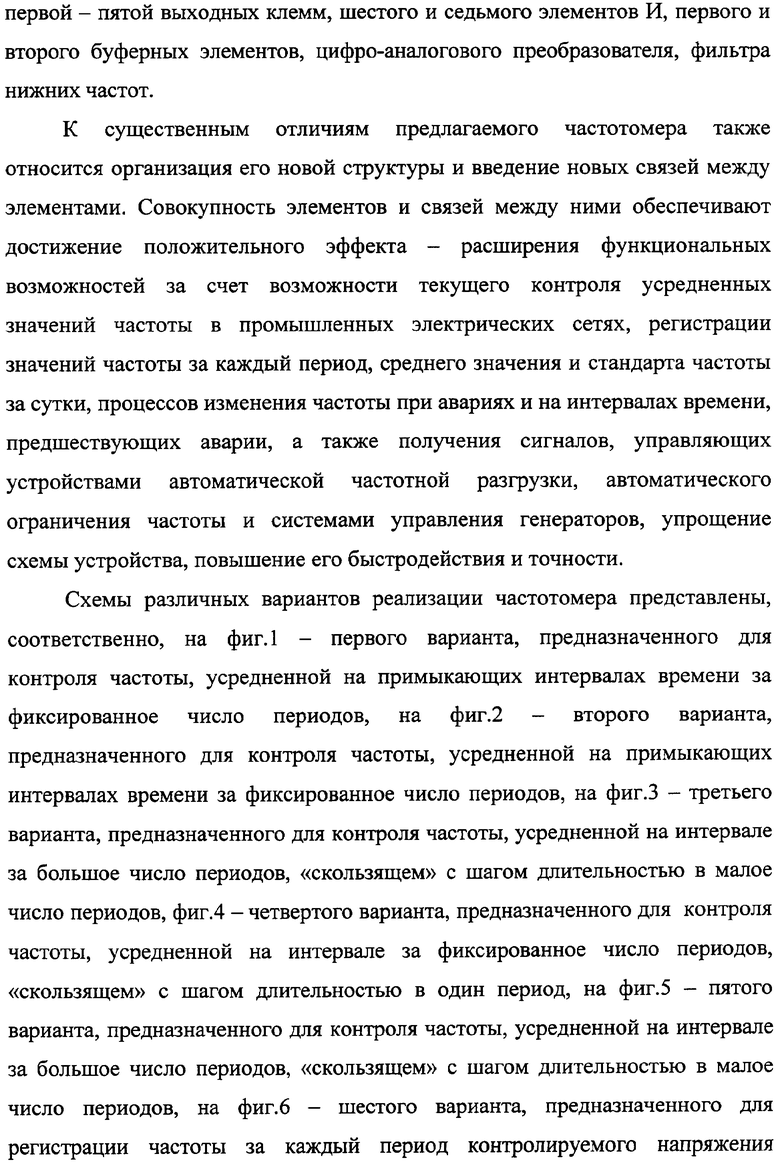

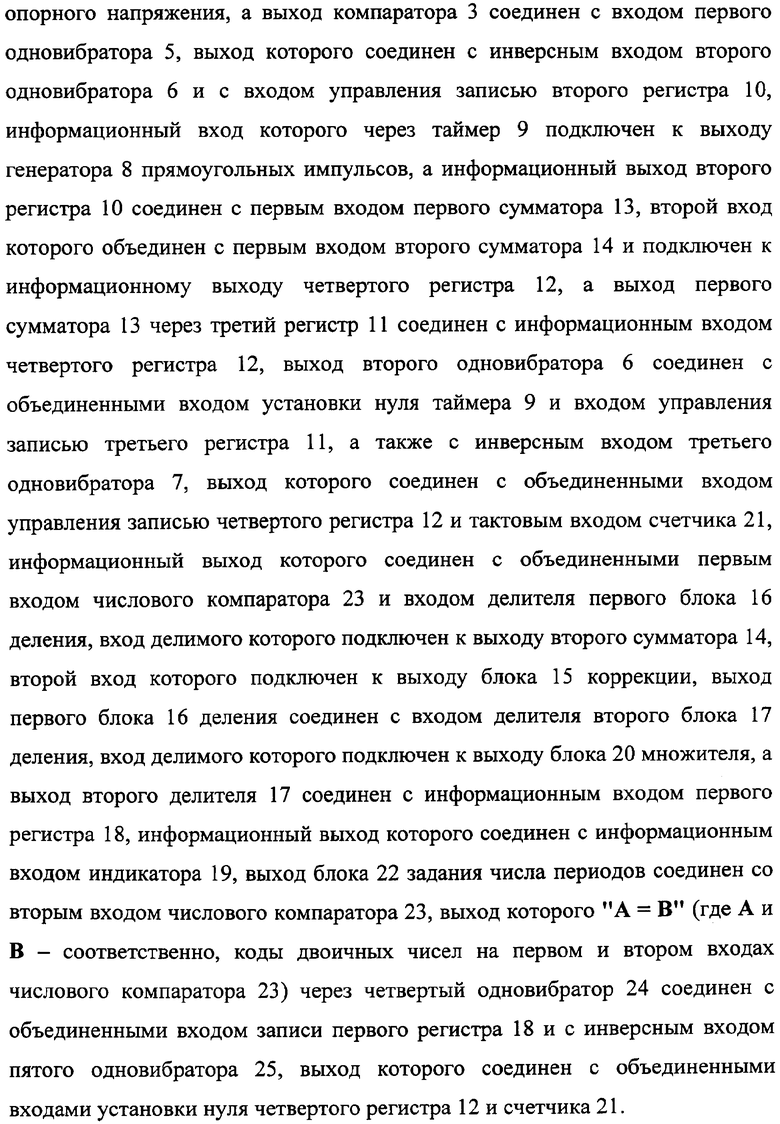

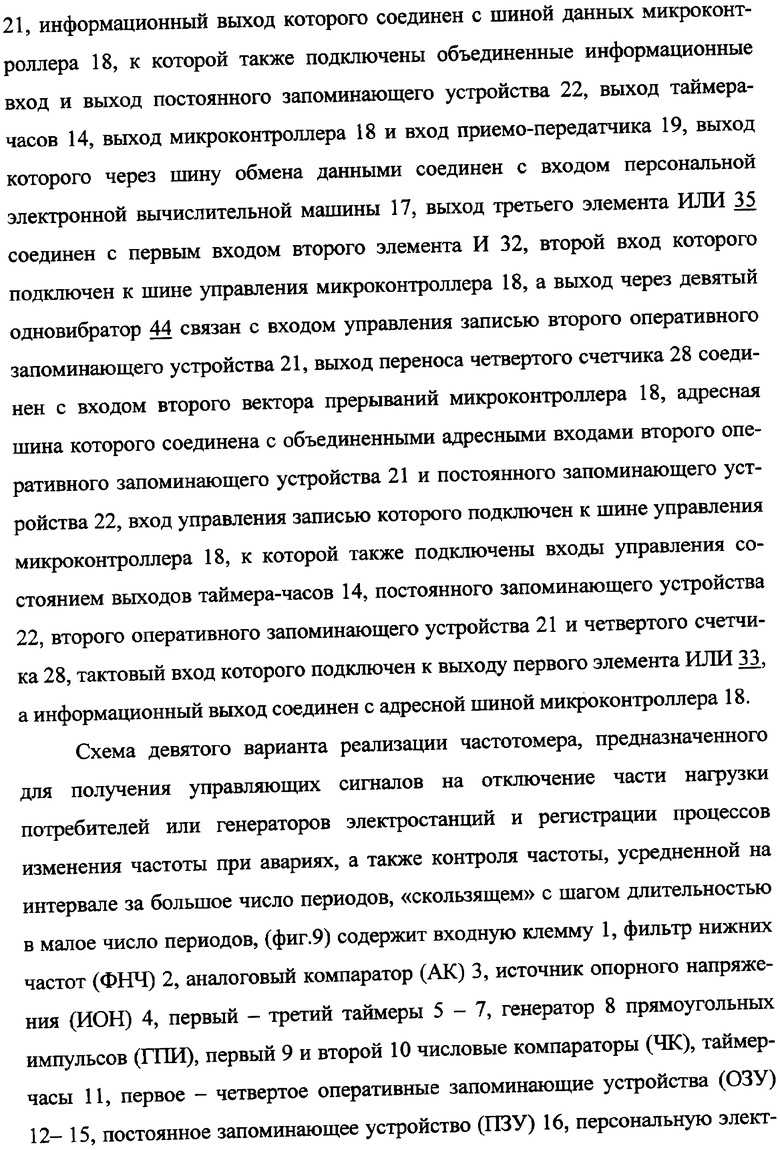

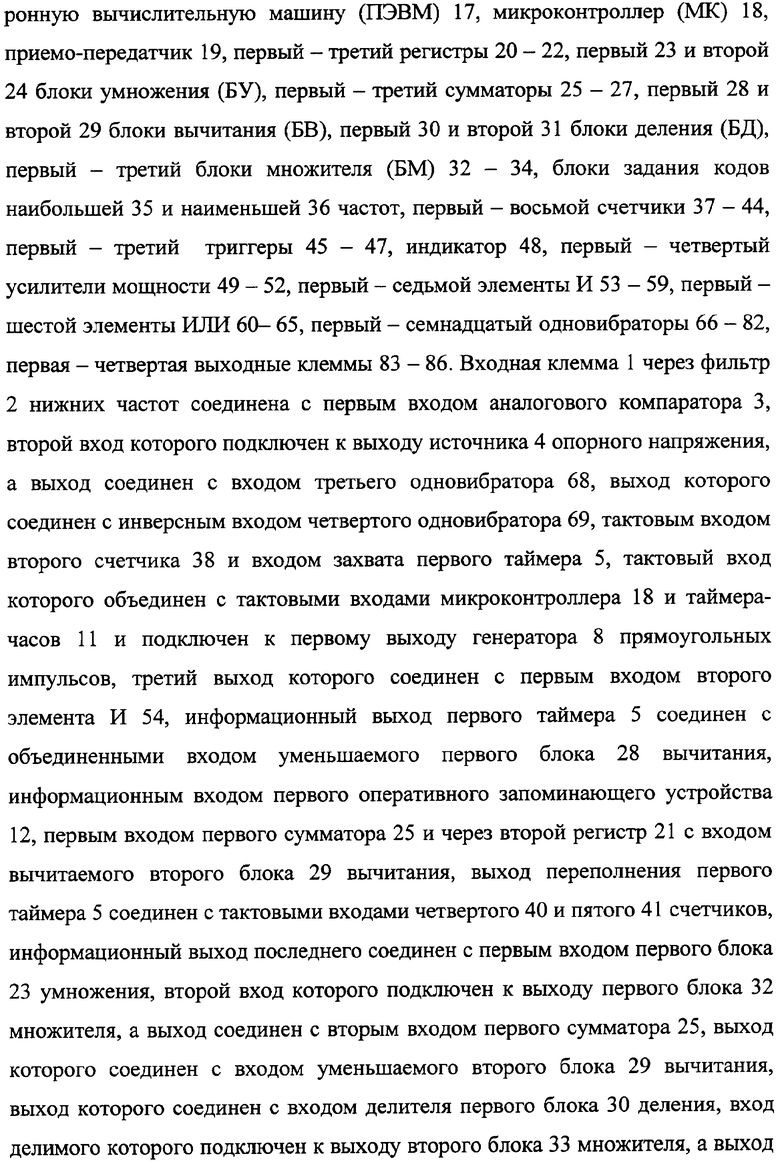

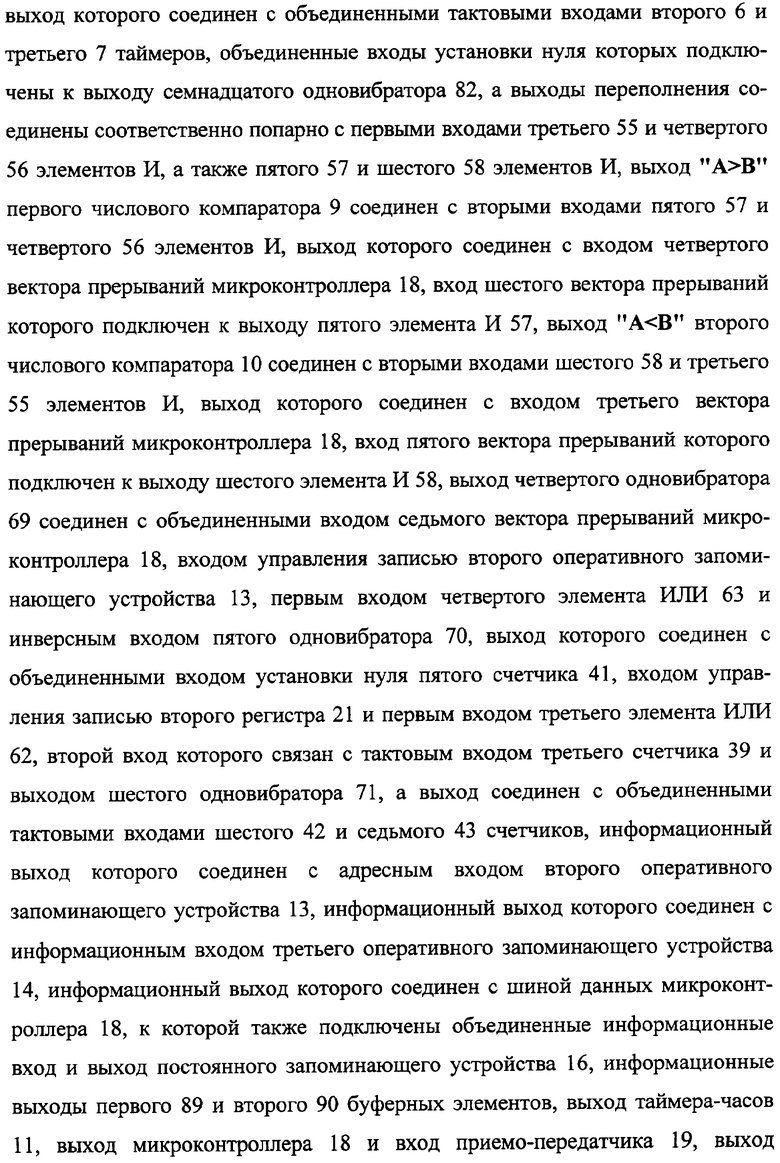

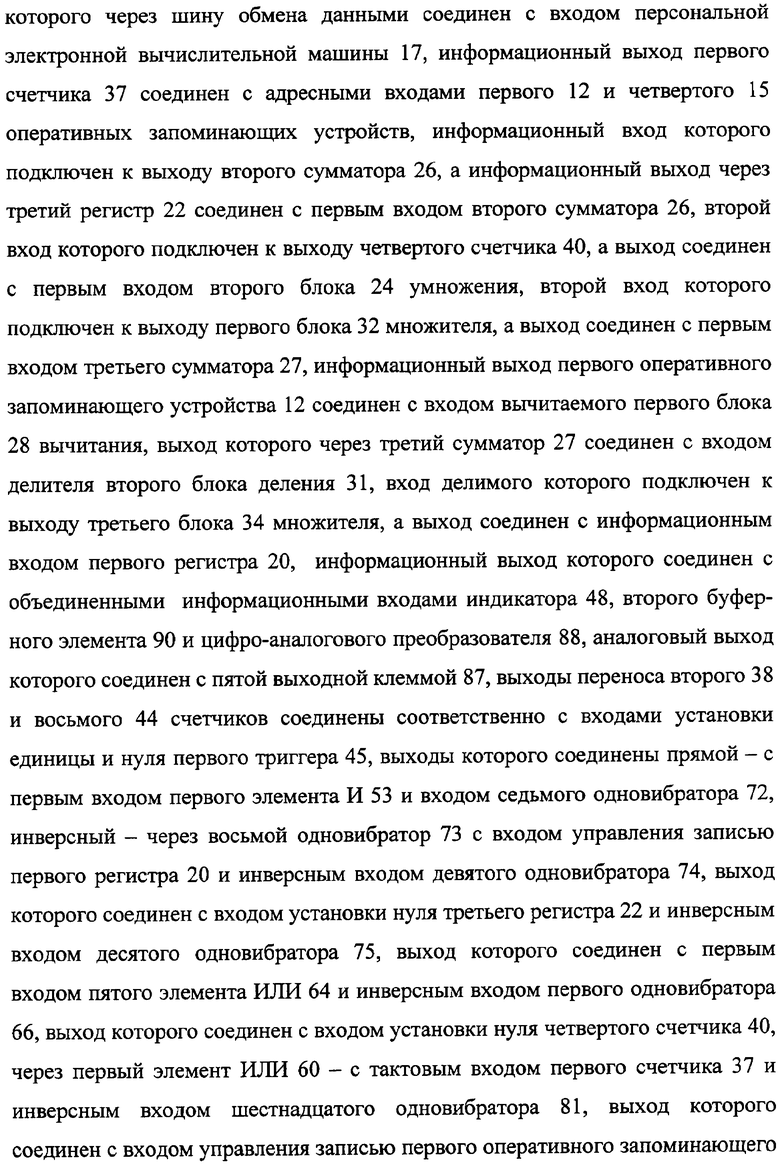

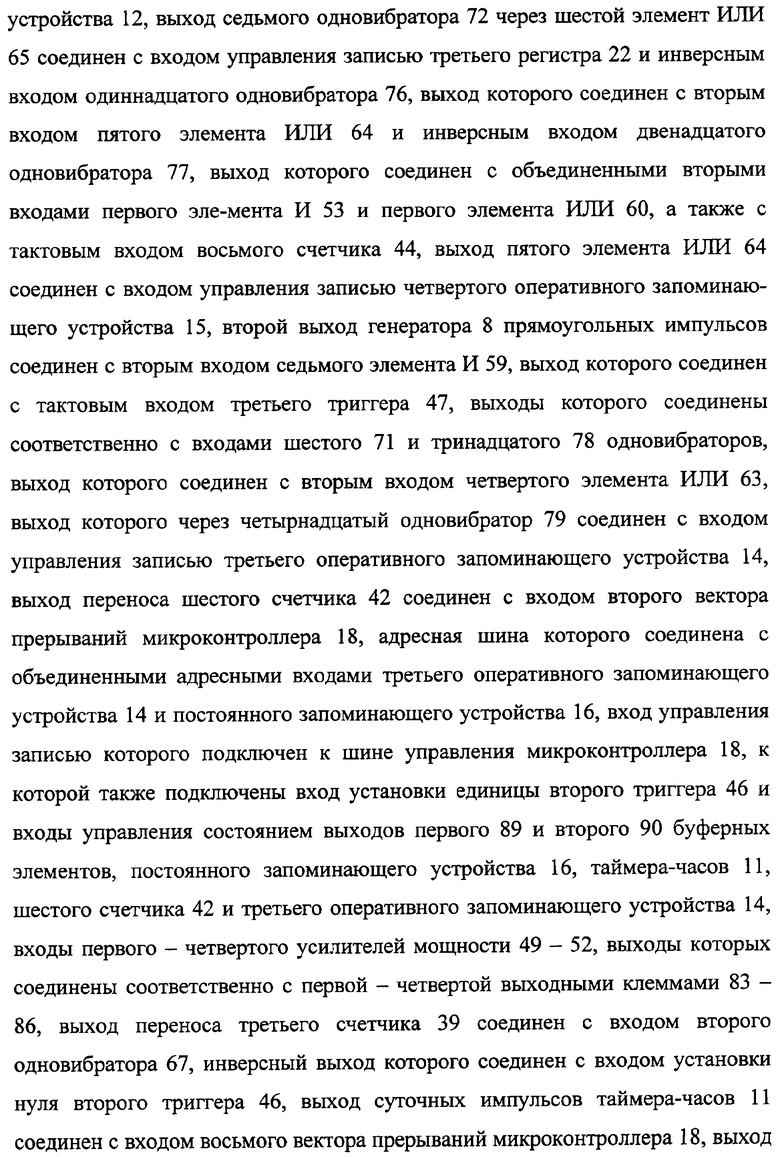

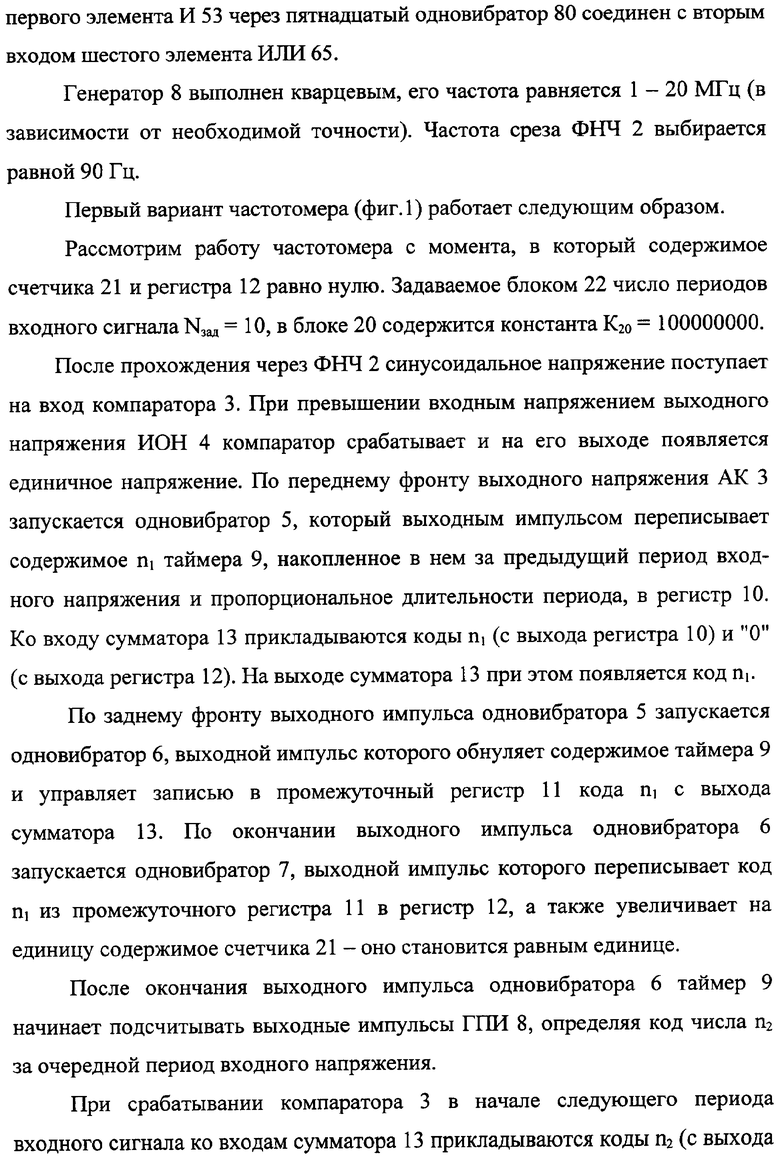

Группа заявленных изобретений относится к области информационно-измерительной и вычислительной техники и может быть использована в электроэнергетике для контроля и регистрации значений частоты за каждый период, среднего значения и стандарта частоты за сутки и усредненных значений частоты в промышленных электрических сетях переменного тока с номинальной частотой 50 или 60 Гц, а также получения сигналов, управляющих системами управления генераторов, устройствами автоматической частотной разгрузки (АЧР) и автоматического ограничения частоты (АОЧ). 1) Первый вариант реализации частотомера содержит входную клемму (ВК), фильтр нижних частот (ФНЧ), аналоговый компаратор (АК), источник опорного напряжения (ИОН), первый, второй и третий одновибраторы, генератор прямоугольных импульсов (ГПИ), таймер, второй, третий и четвертый регистры, первый и второй сумматоры, блок коррекции (БК), первый и второй блоки деления (БД), первый регистр, индикатор, блок множителя (БМ), счетчик, блок задания числа периодов (БЗЧП), числовой компаратор (ЧК), четвертый и пятый одновибраторы; 2) второй вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый и второй одновибраторы, таймер, ГПИ, первый и второй регистры, индикатор, первый и второй БМ, БУ, сумматор, БВ, БД, первый и второй счетчики; 3) третий вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый - третий одновибраторы, ГПИ, таймер, второй - четвертый регистры, первый и второй сумматоры, БК, первый и второй БД, первый регистр, индикатор, БМ, первый и второй счетчики, дешифратор, группу из k регистров, БЗЧП, четвертый - седьмой одновибраторы; 4) четвертый вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый - третий одновибраторы, ГПИ, таймер, оперативное запоминающее устройство (ОЗУ), второй и третий регистры, первый и второй сумматоры, БК, первый и второй БД, первый регистр, индикатор, БМ, первый и второй счетчики, распределитель импульсов (РИ), элемент ИЛИ, триггер, БЗЧП, четвертый одновибратор; 5) пятый вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первое и второе ОЗУ, таймер, ГПИ, первый и второй регистры, первый и второй сумматоры, БУ, БВ, БД, индикатор, первый и второй БМ, первый - четвертый счетчики, триггер, элемент И, первый - третий элементы ИЛИ, первый - десятый одновибраторы; 6) шестой вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый и второй счетчики, таймер, ГПИ, регистр, БУ, сумматор, БВ, БД, постоянное запоминающее устройство (ПЗУ), первый и второй БМ, первый - третий одновибраторы; 7) седьмой вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, одновибратор, счетчик, таймер, ГПИ, регистр, БУ, сумматор, БВ, БД, ПЗУ, первый и второй БМ, ПЭВМ, микроконтроллер (МК), приемопередатчик; 8) восьмой вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый и второй ЧК, таймер, ГПИ, регистр, БУ, сумматор, БВ, БД, таймер-часы, первый и второй БМ, ПЭВМ, МК, приемопередатчик, первое и второе ОЗУ, ПЗУ, блоки задания кодов наибольшей (БЗКБЧ) и наименьшей (БЗКМЧ) частот, первый - четвертый счетчики, первый и второй триггеры, первый и второй элементы И, первый - третий элементы ИЛИ, первый - девятый одновибраторы; 9) девятый вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый - третий таймеры, ГПИ, первый и второй ЧК, таймер-часы, первое - четвертое ОЗУ, ПЗУ, ПЭВМ, МК, приемопередатчик, первый - третий регистры, первый и второй БУ, первый - третий сумматоры, первый и второй БВ, первый и второй БД, первый - третий БМ, БЗКБЧ и БЗКМЧ, первый - восьмой счетчики, первый - третий триггеры, индикатор, первый - четвертый усилители мощности (УМ), первый - седьмой элементы И, первый - шестой элементы ИЛИ, первый - семнадцатый одновибраторы, первая - четвертая выходные клеммы; 10) десятый вариант реализации частотомера содержит ВК, ФНЧ, АК, ИОН, первый - третий таймеры, ГПИ, первый и второй ЧК, таймер-часы, первое - четвертое ОЗУ, ПЗУ, ПЭВМ, МК, приемопередатчик, первый - третий регистры, первый и второй БУ, первый - третий сумматоры, первый и второй БВ, первый и второй БД, первый - третий БМ, БЗКБЧ и БЗКМЧ, первый - восьмой счетчики, первый - третий триггеры, индикатор, первый - четвертый УМ, первый - седьмой элементы И, первый - шестой элементы ИЛИ, первый - семнадцатый одновибраторы, первую - пятую выходные клеммы, цифроаналоговый преобразователь, первый и второй буферные элементы. Технический результат - расширение функциональных возможностей за счет возможности текущего контроля частоты в промышленных электрических сетях, регистрации среднего значения и стандарта частоты за сутки, процессов изменения частоты при авариях и на интервалах времени, предшествующих аварии, а также получения сигналов, управляющих устройствами автоматической частотной разгрузки, автоматического ограничения частоты и системами управления генераторов, упрощение схемы устройства, повышение его быстродействия и точности. 10 н.п. ф-лы, 10 ил.

1. Частотомер промышленного напряжения, предназначенный для контроля частоты, усредненной на примыкающих интервалах времени за фиксированное число периодов, содержащий входную клемму, аналоговый компаратор, первый-пятый одновибраторы, генератор прямоугольных импульсов, счетчик, первый регистр, информационный выход которого соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены таймер, второй-четвертый регистры, первый и второй сумматоры, первый и второй блоки деления, блок множителя, блок коррекции, блок задания числа периодов, числовой компаратор, источник опорного напряжения, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход компаратора соединен с входом первого одновибратора, выход которого соединен с инверсным входом второго одновибратора и с входом управления записью второго регистра, информационный вход которого через таймер подключен к выходу генератора прямоугольных импульсов, а информационный выход второго регистра соединен с первым входом первого сумматора, второй вход которого объединен с первым входом второго сумматора и подключен к информационному выходу четвертого регистра, а выход первого сумматора через третий регистр соединен с информационным входом четвертого регистра, выход второго одновибратора соединен с объединенными входом установки нуля таймера и входом управления записью третьего регистра, а также с инверсным входом третьего одновибратора, выход которого соединен с объединенными входом управления записью четвертого регистра и тактовым входом счетчика, информационный выход которого соединен с объединенными первым входом числового компаратора и входом делителя первого блока деления, вход делимого которого подключен к выходу второго сумматора, второй вход которого подключен к выходу блока коррекции, выход первого блока деления соединен с входом делителя второго блока деления, вход делимого которого подключен к выходу блока множителя, а выход второго блока деления соединен с информационным входом первого регистра, выход блока задания числа периодов соединен со вторым входом числового компаратора, выход которого "А=В" (где А и В - соответственно коды двоичных чисел на первом и втором входах числового компаратора) через четвертый одновибратор соединен с объединенными входом записи первого регистра и с инверсным входом пятого одновибратора, выход которого соединен с объединенными входами установки нуля четвертого регистра и счетчика.

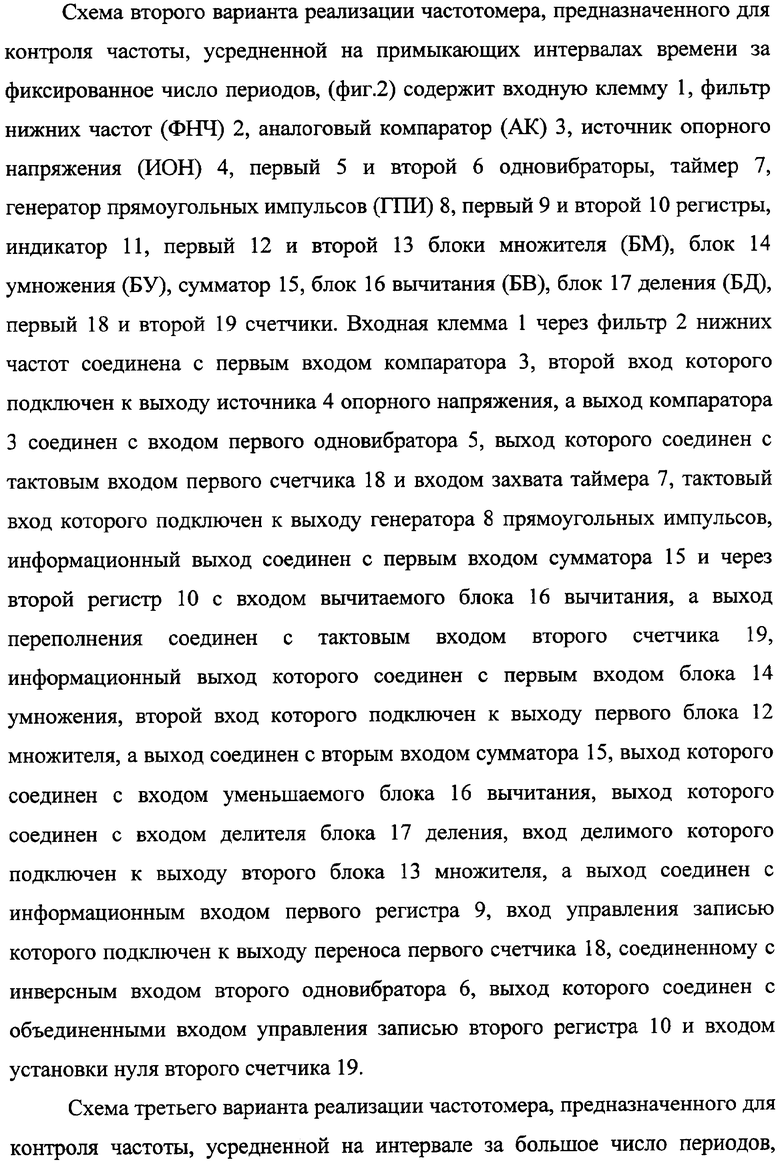

2. Частотомер промышленного напряжения, предназначенный для контроля частоты, усредненной на примыкающих интервалах времени за фиксированное число периодов, содержащий входную клемму, генератор прямоугольных импульсов, аналоговый компаратор, индикатор, первый и второй счетчики, первый и второй одновибраторы, первый регистр, информационный выход которого соединен с информационным входом индикатора, выход переноса первого счетчика соединен с инверсным входом второго одновибратора, отличающийся тем, что в него дополнительно введены таймер, сумматор, блок умножения, блок вычитания, блок деления, первый и второй блоки множителя, источник опорного напряжения, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом первого одновибратора, выход которого соединен с тактовым входом первого счетчика и входом захвата таймера, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через второй регистр с входом вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом второго счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с информационным входом первого регистра, вход управления записью которого подключен к выходу переноса первого счетчика, выход второго одновибратора соединен с объединенными входом управления записью второго регистра и входом установки нуля второго счетчика.

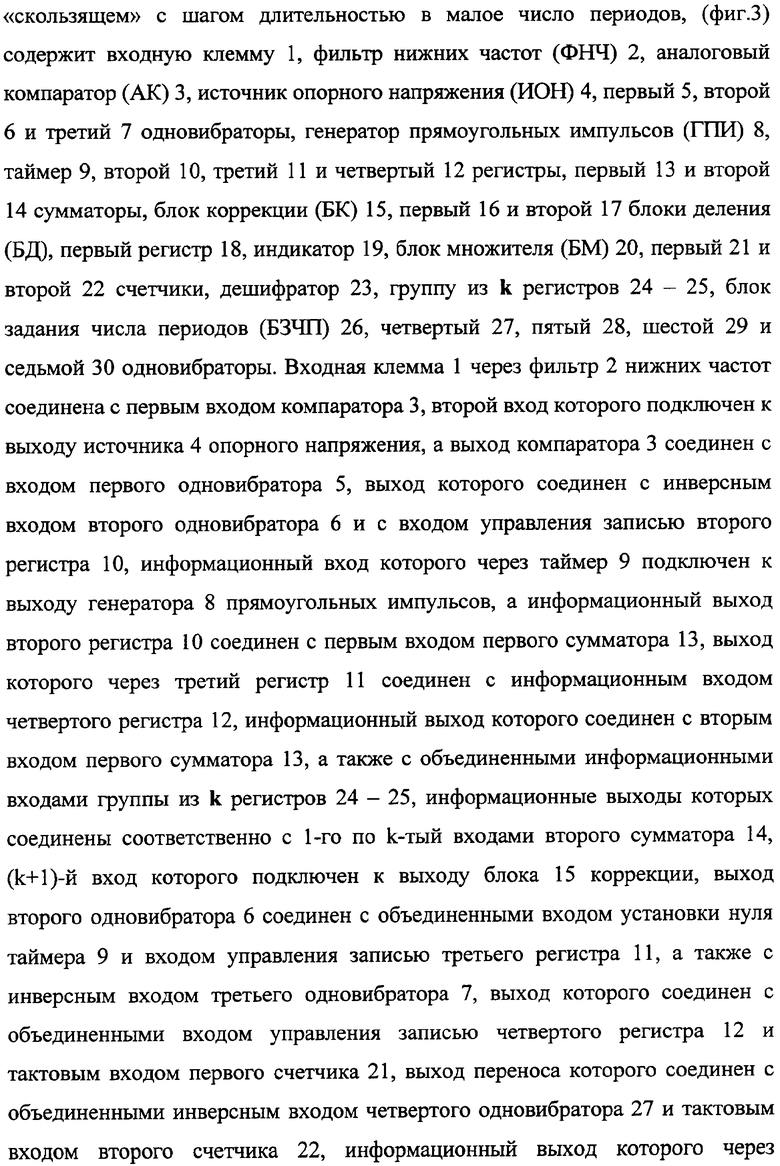

3. Частотомер промышленного напряжения, предназначенный для контроля частоты, усредненной на интервале за большое число периодов, «скользящем» с шагом длительностью в малое число периодов, содержащий входную клемму, аналоговый компаратор, первый-пятый одновибраторы, генератор прямоугольных импульсов, первый и второй счетчики, первый регистр, информационный выход которого соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены таймер, дешифратор, второй-четвертый регистры, группа из k регистров, первый и второй сумматоры, первый и второй блоки деления, блок множителя, блок коррекции, блок задания числа периодов, источник опорного напряжения, шестой и седьмой одновибраторы, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход компаратора соединен с входом первого одновибратора, выход которого соединен с инверсным входом второго одновибратора и с входом управления записью второго регистра, информационный вход которого через таймер подключен к выходу генератора прямоугольных импульсов, а информационный выход второго регистра соединен с первым входом первого сумматора, выход которого через третий регистр соединен с информационным входом четвертого регистра, информационный выход которого соединен с вторым входом первого сумматора, а также с объединенными информационными входами группы из k регистров, информационные выходы которых соединены соответственно с 1-го по k-й входами второго сумматора, (k+1)-й вход которого подключен к выходу блока коррекции, выход второго одновибратора соединен с объединенными входом установки нуля таймера и входом управления записью третьего регистра, а также с инверсным входом третьего одновибратора, выход которого соединен с объединенными входом управления записью четвертого регистра и тактовым входом первого счетчика, выход старшего разряда которого соединен с объединенными инверсным входом четвертого одновибратора и тактовым входом второго счетчика, информационный выход которого через дешифратор соединен соответственно с входами управления записью группы из k регистров, выход второго сумматора соединен с входом делимого первого блока деления, вход делителя которого подключен к выходу блока задания числа периодов, а выход первого блока деления соединен с входом делителя второго блока деления, вход делимого которого подключен к выходу блока множителя, а выход второго делителя соединен с информационным входом первого регистра, выход четвертого одновибратора соединен с инверсным входом пятого одновибратора, выход которого соединен с объединенными входом стробирования дешифратора и инверсным входом шестого одновибратора, выход которого соединен с объединенными входом управления записью первого регистра и с инверсным входом седьмого одновибратора, выход которого соединен с входом установки нуля четвертого регистра.

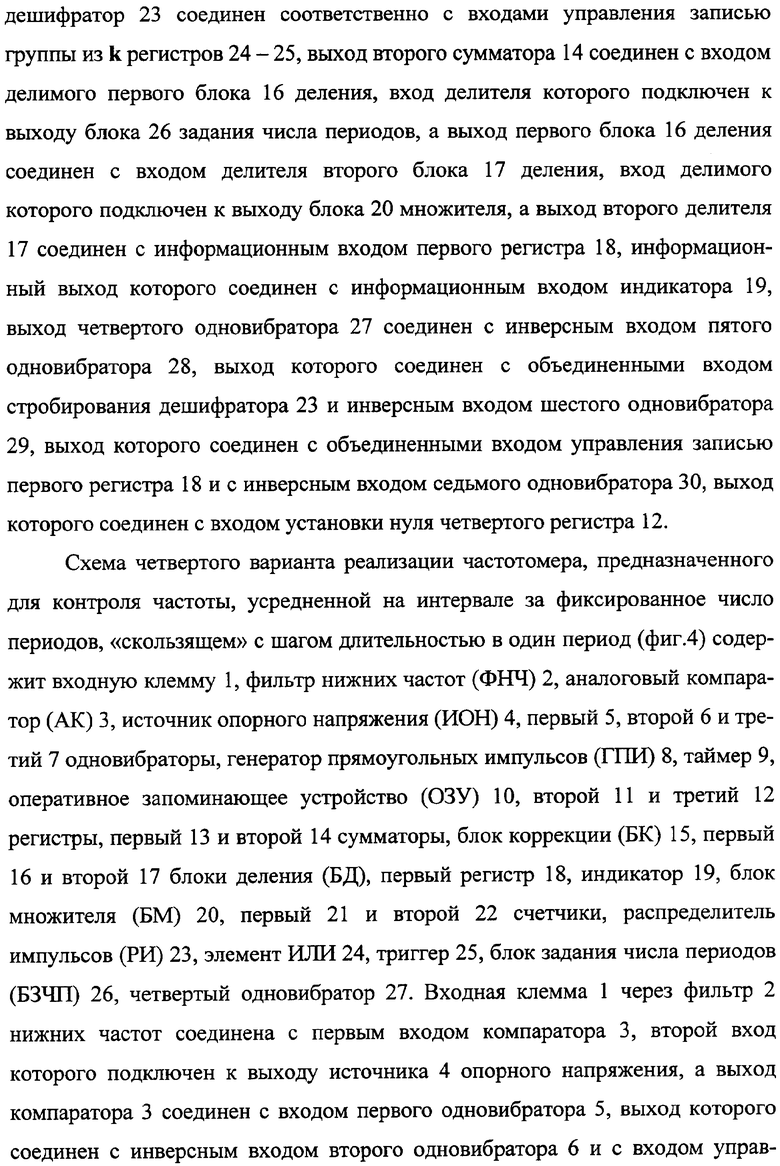

4. Частотомер промышленного напряжения, предназначенный для контроля частоты, усредненной на интервале за фиксированное число периодов, «скользящем» с шагом длительностью в один период, содержащий входную клемму, аналоговый компаратор, генератор прямоугольных импульсов, первый и второй счетчики, первый регистр, распределитель импульсов, оперативное запоминающее устройство, первый-четвертый одновибраторы, элемент ИЛИ, триггер, инверсный выход которого соединен с входом установки нуля распределителя импульсов, вход установки единицы подключен к инверсному выходу второго одновибратора, а вход установки нуля подключен к инверсному выходу третьего одновибратора, инверсный вход которого подключен к выходу старшего разряда второго счетчика, выход элемента ИЛИ соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом оперативного запоминающего устройства, информационный выход первого регистра соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены таймер, второй и третий регистры, первый и второй сумматоры, первый и второй блоки деления, блок множителя, блок коррекции, блок задания числа периодов, источник опорного напряжения, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход компаратора соединен с входом первого одновибратора, выход которого соединен с инверсным входом второго одновибратора и с входом управления записью оперативного запоминающего устройства, информационный вход которого через таймер подключен к выходу генератора прямоугольных импульсов, а информационный выход соединен с первым входом первого сумматора, выход которого через второй регистр соединен с информационным входом третьего регистра, информационный выход которого соединен с объединенными вторым входом первого сумматора и первым входом второго сумматора, второй вход которого подключен к выходу блока коррекции, выход второго сумматора соединен с входом делимого первого блока деления, вход делителя которого подключен к выходу блока задания числа периодов, а выход первого блока деления соединен с входом делителя второго блока деления, вход делимого которого подключен к выходу блока множителя, а выход второго делителя соединен с информационным входом первого регистра, выход генератора прямоугольных импульсов соединен с тактовым входом распределителя импульсов, выходы которого соответственно соединены второй - с входом управления записью второго регистра, третий - с входом управления записью третьего регистра, четвертый - с первым входом элемента ИЛИ, пятый - с тактовым входом второго счетчика, выход старшего разряда которого соединен с инверсным входом третьего одновибратора, прямой выход которого соединен с объединенными вторым входом элемента ИЛИ, входом управления записью первого регистра и с инверсным входом четвертого одновибратора, выход которого соединен с входом установки нуля третьего регистра, прямой выход второго одновибратора соединен с входом установки нуля таймера.

5. Частотомер промышленного напряжения, предназначенный для контроля частоты, усредненной на интервале за большое число периодов, «скользящем» с шагом длительностью в малое число периодов, содержащий входную клемму, аналоговый компаратор, генератор прямоугольных импульсов, первый-четвертый счетчики, первый регистр, первое и второе оперативные запоминающие устройства, триггер, первый-пятый одновибраторы, элемент И, первый-третий элементы ИЛИ, первый вход которого подключен к выходу первого одновибратора, а выход соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, вход управления записью которого подключен к выходу второго элемента ИЛИ, выход переноса второго счетчика соединен с входом установки единицы триггера, прямой выход которого соединен с первым входом элемента И, информационный выход первого регистра соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены таймер, второй регистр, блок вычитания, блок умножения, блок деления, первый и второй сумматоры, первый и второй блоки множителя, источник опорного напряжения, шестой-десятый одновибраторы, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом второго одновибратора, выход которого соединен с тактовым входом второго счетчика и входом захвата таймера, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, а информационный выход соединен с объединенными входом уменьшаемого блока вычитания и информационным входом второго оперативного запоминающего устройства, адресный вход которого подключен к информационному выходу первого счетчика, а информационный выход соединен с входом вычитаемого блока вычитания, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к выходу блока умножения, а выход соединен с входом делителя блока деления, вход делимого которого подключен к выходу первого блока множителя, а выход соединен с информационным входом первого регистра, выход переполнения таймера соединен с тактовым входом третьего счетчика, вход установки нуля которого подключен к выходу первого одновибратора, а информационный выход соединен с первым входом второго сумматора, второй вход которого через второй регистр подключен к информационному выходу первого оперативного запоминающего устройства, а выход соединен с объединенными информационным входом первого оперативного запоминающего устройства и первым входом блока умножения, второй вход которого подключен к выходу второго блока множителя, выходы триггера соединены инверсный - с входом третьего одновибратора, прямой - с входом четвертого одновибратора, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого подключен к выходу пятого одновибратора, инверсный вход которого подключен к выходу элемента И, выход первого элемента ИЛИ соединен с входом управления записью второго регистра и инверсным входом шестого одновибратора, выход которого соединен с первым входом второго элемента ИЛИ и инверсным входом седьмого одновибратора, выход которого соединен с объединенными вторыми входами элемента И и третьего элемента ИЛИ, а также тактовым входом четвертого счетчика, выход переноса которого соединен с входом установки нуля триггера, выход третьего одновибратора соединен с входом управления записью первого регистра и инверсным входом восьмого одновибратора, выход которого соединен с входом установки нуля второго регистра и инверсным входом девятого одновибратора, выход которого соединен с объединенными вторым входом второго элемента ИЛИ и инверсным входом первого одновибратора, выход которого через десятый одновибратор соединен с входом управления записью второго оперативного запоминающего устройства.

6. Частотомер промышленного напряжения, предназначенный для регистрации частоты за каждый период контролируемого напряжения ответственных производителей и потребителей электроэнергии, содержащий генератор прямоугольных импульсов, входную клемму, аналоговый компаратор, первый - третий одновибраторы, первый и второй счетчики, регистр, отличающийся тем, что в него дополнительно введены таймер, сумматор, блок умножения, блок вычитания, блок деления, постоянное запоминающее устройство, первый и второй блоки множителя, источник опорного напряжения, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом первого одновибратора, выход которого соединен с инверсным входом второго одновибратора и входом захвата таймера, тактовый вход которого подключен к выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через регистр с входом вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом первого счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к информационному выходу второго счетчика, а вход управления записью подключен к выходу второго одновибратора, соединенному с инверсным входом третьего одновибратора, выход которого соединен с объединенными входом управления записью регистра, тактовым входом второго счетчика и входом установки нуля первого счетчика.

7. Частотомер промышленного напряжения, предназначенный для регистрации частоты за каждый период контролируемого напряжения ответственных производителей и потребителей электроэнергии, содержащий входную клемму, аналоговый компаратор, одновибратор, генератор прямоугольных импульсов, счетчик, регистр, отличающийся тем, что в него дополнительно введены источник опорного напряжения, таймер, сумматор, блок умножения, блок вычитания, блок деления, постоянное запоминающее устройство, микроконтроллер, приемопередатчик, персональная электронная вычислительная машина, первый и второй блоки множителя, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом одновибратора, выход которого соединен с входом вектора прерываний микроконтроллера и входом захвата таймера, тактовый вход которого объединен с тактовым входом микроконтроллера и подключен к выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через регистр с входом вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с информационным входом постоянного запоминающего устройства, адресный вход которого подключен к адресной шине микроконтроллера, а вход управления записью подключен к шине управления микроконтроллера, к которой также подключены вход управления записью регистра и вход установки нуля счетчика, информационный выход микроконтроллера через шину данных связан с информационным выходом постоянного запоминающего устройства и входом приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины.

8. Частотомер промышленного напряжения, предназначенный для регистрации процессов изменения частоты при авариях, содержащий входную клемму, аналоговый компаратор, первый-четвертый счетчики, первый и второй триггеры, генератор прямоугольных импульсов, первое и второе оперативные запоминающие устройства, первый и второй элементы И, первый-третий элементы ИЛИ, первый-пятый одновибраторы, выход первого одновибратора через первый элемент ИЛИ соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, входы установки единицы и нуля первого триггера подключены соответственно к инверсным выходам второго и третьего одновибраторов, инверсный вход которого подключен к выходу переноса второго счетчика, отличающийся тем, что в него дополнительно введены таймер-часы, таймер, источник опорного напряжения, персональная электронная вычислительная машина, микроконтроллер, приемопередатчик, сумматор, блок умножения, блок вычитания, блок деления, шестой-девятый одновибраторы, первый и второй числовые компараторы, блоки задания кодов наибольшей и наименьшей частот, первый и второй блоки множителя, постоянное запоминающее устройство, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом аналогового компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом четвертого одновибратора, выход которого соединен с инверсным входом пятого одновибратора и входом захвата таймера, тактовый вход которого объединен с тактовыми входами микроконтроллера и таймера-часов и подключен к первому выходу генератора прямоугольных импульсов, информационный выход соединен с первым входом сумматора и через регистр с входом вычитаемого блока вычитания, а выход переполнения соединен с тактовым входом третьего счетчика, информационный выход которого соединен с первым входом блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом сумматора, выход которого соединен с входом уменьшаемого блока вычитания, выход которого соединен с входом делителя блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с объединенными информационным входом первого оперативного запоминающего устройства и первыми входами первого и второго числовых компараторов, вторые входы которых подключены соответственно к выходам блоков задания кодов наибольшей и наименьшей частот, выход "А>В" первого числового компаратора и выход "А<В" второго числового компаратора (где А и В - соответственно коды двоичных чисел на первом и втором входах числовых компараторов) соединены через второй элемент ИЛИ с входом шестого одновибратора, выход которого соединен с объединенными входами захвата таймера-часов, первого вектора прерываний микроконтроллера, установки нуля второго и четвертого счетчиков и инверсным входом второго одновибратора, прямой выход первого триггера соединен с первым входом первого элемента И, второй вход которого подключен к второму выходу генератора прямоугольных импульсов, а выход соединен с тактовым входом второго триггера, выходы которого соединены соответственно с входами седьмого и восьмого одновибраторов, выход последнего соединен с первым входом третьего элемента ИЛИ, второй вход которого объединен с входом управления записью первого оперативного запоминающего устройства и подключен к выходу пятого одновибратора, соединенному с инверсным входом первого одновибратора, выход которого соединен с объединенными входами управления записью регистра и установки нуля третьего счетчика, выход седьмого одновибратора соединен с объединенными вторым входом первого элемента ИЛИ и тактовым входом второго счетчика, информационный выход первого оперативного запоминающего устройства соединен с информационным входом второго оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, к которой также подключены объединенные информационные вход и выход постоянного запоминающего устройства, выход таймера-часов, выход микроконтроллера и вход приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины, выход третьего элемента ИЛИ соединен с первым входом второго элемента И, второй вход которого подключен к шине управления микроконтроллера, а выход через девятый одновибратор связан с входом управления записью второго оперативного запоминающего устройства, выход переноса четвертого счетчика соединен с входом второго вектора прерываний микроконтроллера, адресная шина которого соединена с объединенными адресными входами второго оперативного запоминающего устройства и постоянного запоминающего устройства, вход управления записью которого подключен к шине управления микроконтроллера, к которой также подключены входы управления состоянием выходов таймера-часов, постоянного запоминающего устройства, второго оперативного запоминающего устройства и четвертого счетчика, тактовый вход которого подключен к выходу первого элемента ИЛИ, а информационный выход соединен с адресной шиной микроконтроллера.

9. Частотомер промышленного напряжения, предназначенный для получения управляющих сигналов на отключение части нагрузки потребителей или генераторов электростанций и регистрации процессов изменения частоты при авариях, а также контроля частоты, усредненной на интервале за большое число периодов, «скользящем» с шагом длительностью в малое число периодов, содержащий входную клемму, аналоговый компаратор, первый-третий триггеры, первый регистр, генератор прямоугольных импульсов, первое и второе оперативные запоминающие устройства, первый-четвертый счетчики, индикатор, первый-пятый одновибраторы, первый-пятый элементы И, первый-четвертый элементы ИЛИ, выход первого одновибратора через первый элемент ИЛИ соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, выход переноса второго счетчика соединен с входом установки единицы первого триггера, прямой выход которого соединен с первым входом первого элемента И, вход установки нуля второго триггера подключен к инверсному выходу второго одновибратора, инверсный вход которого подключен к выходу переноса третьего счетчика, информационный выход первого регистра соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены третье и четвертое оперативные запоминающие устройства, постоянное запоминающее устройство, источник опорного напряжения, персональная электронная вычислительная машина, микроконтроллер, приемопередатчик, первый-третий таймеры, таймер-часы, первый-третий сумматоры, первый и второй блоки умножения, первый и второй блоки вычитания, первый и второй блоки деления, первый-третий блоки множителя, первый и второй числовые компараторы, блоки задания кодов наибольшей и наименьшей частот, второй и третий регистры, шестой-пятнадцатый одновибраторы, пятый-восьмой счетчики, пятый и шестой элементы ИЛИ, первый-четвертый усилители мощности, шестой и седьмой элементы И, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом третьего одновибратора, выход которого соединен с инверсным входом четвертого одновибратора и входом захвата первого таймера, тактовый вход которого объединен с тактовыми входами микроконтроллера и таймера-часов и подключен к первому выходу генератора прямоугольных импульсов, третий выход которого соединен с первым входом второго элемента И, информационный выход первого таймера соединен с объединенными входом уменьшаемого первого блока вычитания, информационным входом первого оперативного запоминающего устройства, первым входом первого сумматора и через второй регистр с входом вычитаемого второго блока вычитания, выход переполнения первого таймера соединен с тактовыми входами четвертого и пятого счетчиков, информационный выход последнего соединен с первым входом первого блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом первого сумматора, выход которого соединен с входом уменьшаемого второго блока вычитания, выход которого соединен с входом делителя первого блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с объединенными информационным входом второго оперативного запоминающего устройства и первыми входами первого и второго числовых компараторов, вторые входы которых подключены соответственно к выходам блоков задания кодов наибольшей и наименьшей частот, выход "А>В" первого числового компаратора и выход "А<В" второго числового компаратора (где А и В - соответственно коды двоичных чисел на первом и втором входах числовых компараторов) соединены через второй элемент ИЛИ с объединенными входами захвата таймера-часов, первого вектора прерываний микроконтроллера, установки нуля третьего и шестого счетчиков, инверсным входом семнадцатого одновибратора и вторым входом второго элемента И, выход которого соединен с объединенными тактовыми входами второго и третьего таймеров, объединенные входы установки нуля которых подключены к выходу семнадцатого одновибратора, а выходы переполнения соединены соответственно попарно с первыми входами третьего и четвертого элементов И, а также пятого и шестого элементов И, выход "А>В" первого числового компаратора соединен с вторыми входами пятого и четвертого элементов И, выход которого соединен с входом четвертого вектора прерываний микроконтроллера, вход шестого вектора прерываний которого подключен к выходу пятого элемента И, выход "А<В" второго числового компаратора соединен с вторыми входами шестого и третьего элементов И, выход которого соединен с входом третьего вектора прерываний микроконтроллера, вход пятого вектора прерываний которого подключен к выходу шестого элемента И, выход четвертого одновибратора соединен с объединенными входом управления записью второго оперативного запоминающего устройства, первым входом четвертого элемента ИЛИ и инверсным входом пятого одновибратора, выход которого соединен с объединенными входом установки нуля пятого счетчика, входом управления записью второго регистра и первым входом третьего элемента ИЛИ, второй вход которого связан с тактовым входом третьего счетчика и выходом шестого одновибратора, а выход соединен с объединенными тактовыми входами шестого и седьмого счетчиков, информационный выход которого соединен с адресным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, к которой также подключены объединенные информационные вход и выход постоянного запоминающего устройства, выход таймера-часов, выход микроконтроллера и вход приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины, информационный выход первого счетчика соединен с адресным входом четвертого оперативного запоминающего устройства, информационный вход которого подключен к выходу второго сумматора, а информационный выход через третий регистр соединен с первым входом второго сумматора, второй вход которого подключен к выходу четвертого счетчика, а выход соединен с первым входом второго блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с первым входом третьего сумматора, информационный выход первого оперативного запоминающего устройства соединен с входом вычитаемого первого блока вычитания, выход которого через третий сумматор соединен с входом делителя второго блока деления, вход делимого которого подключен к выходу третьего блока множителя, а выход соединен с информационным входом первого регистра, выходы первого триггера соединены прямой с входом седьмого одновибратора, инверсный - через восьмой одновибратор с входом управления записью первого регистра и инверсным входом девятого одновибратора, выход которого соединен с входом установки нуля третьего регистра и инверсным входом десятого одновибратора, выход которого соединен с первым входом пятого элемента ИЛИ и инверсным входом первого одновибратора, выход которого соединен с входом установки нуля четвертого счетчика и инверсным входом шестнадцатого одновибратора, выход которого соединен с входом управления записью первого оперативного запоминающего устройства, выход седьмого одновибратора через шестой элемент ИЛИ соединен с входом управления записью третьего регистра и инверсным входом одиннадцатого одновибратора, выход которого соединен с вторым входом пятого элемента ИЛИ и инверсным входом двенадцатого одновибратора, выход которого соединен с объединенными вторыми входами первого элемента И и первого элемента ИЛИ, а также с тактовым входом восьмого счетчика, выход переноса которого соединен с входом установки нуля первого триггера, выход пятого элемента ИЛИ соединен с входом управления записью четвертого оперативного запоминающего устройства, второй выход генератора прямоугольных импульсов соединен с вторым входом седьмого элемента И, выход которого соединен с тактовым входом третьего триггера, выходы которого соединены соответственно с входами шестого и тринадцатого одновибраторов, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого через четырнадцатый одновибратор соединен с входом управления записью третьего оперативного запоминающего устройства, выход переноса шестого счетчика соединен с входом второго вектора прерываний микроконтроллера, адресная шина которого соединена с объединенными адресными входами третьего оперативного запоминающего устройства и постоянного запоминающего устройства, вход управления записью которого подключен к шине управления микроконтроллера, к которой также подключены вход установки единицы второго триггера и входы управления состоянием выходов постоянного запоминающего устройства, таймера-часов, шестого счетчика и третьего оперативного запоминающего устройства, входы первого-четвертого усилителей мощности, выходы которых соединены соответственно с первой-четвертой выходными клеммами, выход первого элемента И через пятнадцатый одновибратор соединен с вторым входом шестого элемента ИЛИ.

10. Частотомер промышленного напряжения, предназначенный для получения управляющих сигналов системами управления генераторов и на отключение части нагрузки потребителей или генераторов электростанций, регистрации среднего значения и стандарта частоты за сутки, процессов изменения частоты при авариях, а также контроля частоты, усредненной на интервале за большое число периодов, «скользящем» с шагом длительностью в малое число периодов, содержащий входную клемму, первый-третий триггеры, аналоговый компаратор, первый регистр, генератор прямоугольных импульсов, первое и второе оперативные запоминающие устройства, первый-четвертый счетчики, индикатор, первый-пятый одновибраторы, первый-пятый элементы И, первый-четвертый элементы ИЛИ, выход первого одновибратора через первый элемент ИЛИ соединен с тактовым входом первого счетчика, информационный выход которого соединен с адресным входом первого оперативного запоминающего устройства, выход переноса второго счетчика соединен с входом установки единицы первого триггера, прямой выход которого соединен с первым входом первого элемента И, вход установки нуля второго триггера подключен к инверсному выходу второго одновибратора, инверсный вход которого подключен к выходу переноса третьего счетчика, информационный выход первого регистра соединен с информационным входом индикатора, отличающийся тем, что в него дополнительно введены третье и четвертое оперативные запоминающие устройства, постоянное запоминающее устройство, источник опорного напряжения, персональная электронная вычислительная машина, микроконтроллер, приемопередатчик, первый-третий таймеры, таймер-часы, первый-третий сумматоры, первый и второй блоки умножения, первый и второй блоки вычитания, первый и второй блоки деления, первый-третий блоки множителя, первый и второй числовые компараторы, блоки задания кодов наибольшей и наименьшей частот, второй и третий регистры, шестой-семнадцатый одновибраторы, пятый-восьмой счетчики, пятый и шестой элементы ИЛИ, первый-четвертый усилители мощности, первая-пятая выходные клеммы, шестой и седьмой элементы И, первый и второй буферные элементы, цифроаналоговый преобразователь, фильтр нижних частот, вход которого подключен к входной клемме, а выход соединен с первым входом компаратора, второй вход которого подключен к выходу источника опорного напряжения, а выход соединен с входом третьего одновибратора, выход которого соединен с инверсным входом четвертого одновибратора и входом захвата первого таймера, тактовый вход которого объединен с тактовыми входами микроконтроллера и таймера-часов и подключен к первому выходу генератора прямоугольных импульсов, третий выход которого соединен с первым входом второго элемента И, информационный выход первого таймера соединен с объединенными входом уменьшаемого первого блока вычитания, информационным входом первого оперативного запоминающего устройства, первым входом первого сумматора и через второй регистр с входом вычитаемого второго блока вычитания, выход переполнения первого таймера соединен с тактовыми входами четвертого и пятого счетчиков, информационный выход последнего соединен с первым входом первого блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с вторым входом первого сумматора, выход которого соединен с входом уменьшаемого второго блока вычитания, выход которого соединен с входом делителя первого блока деления, вход делимого которого подключен к выходу второго блока множителя, а выход соединен с объединенными информационными входами второго оперативного запоминающего устройства и первого буферного элемента и первыми входами первого и второго числовых компараторов, вторые входы которых подключены соответственно к выходам блоков задания кодов наибольшей и наименьшей частот, выход "А>В" первого числового компаратора и выход "А<В" второго числового компаратора (где А и В - соответственно коды двоичных чисел на первом и втором входах числовых компараторов) соединены через второй элемент ИЛИ с объединенными входами захвата таймера-часов, первого вектора прерываний микроконтроллера, установки нуля третьего и шестого счетчиков, инверсным входом семнадцатого одновибратора и вторым входом второго элемента И, выход которого соединен с объединенными тактовыми входами второго и третьего таймеров, выходы переполнения которых соединены соответственно попарно с первыми входами третьего и четвертого элементов И, а также пятого и шестого элементов И, выход семнадцатого одновибратора соединен с объединенными входами установки нуля второго и третьего таймеров, выход "А>В" первого числового компаратора соединен с вторыми входами пятого и четвертого элементов И, выход которого соединен с входом четвертого вектора прерываний микроконтроллера, вход шестого вектора прерываний которого подключен к выходу пятого элемента И, выход "А<В" второго числового компаратора соединен с вторыми входами шестого и третьего элементов И, выход которого соединен с входом третьего вектора прерываний микроконтроллера, вход пятого вектора прерываний которого подключен к выходу шестого элемента И, выход четвертого одновибратора соединен с объединенными входом седьмого вектора прерываний микроконтроллера, входом управления записью второго оперативного запоминающего устройства, первым входом четвертого элемента ИЛИ и инверсным входом пятого одновибратора, выход которого соединен с объединенными входом установки нуля пятого счетчика, входом управления записью второго регистра и первым входом третьего элемента ИЛИ, второй вход которого связан с тактовым входом третьего счетчика и выходом шестого одновибратора, а выход соединен с объединенными тактовыми входами шестого и седьмого счетчиков, информационный выход которого соединен с адресным входом второго оперативного запоминающего устройства, информационный выход которого соединен с информационным входом третьего оперативного запоминающего устройства, информационный выход которого соединен с шиной данных микроконтроллера, к которой также подключены объединенные информационные вход и выход постоянного запоминающего устройства, информационные выходы первого и второго буферных элементов, выход таймера-часов, выход микроконтроллера и вход приемопередатчика, выход которого через шину обмена данными соединен с входом персональной электронной вычислительной машины, информационный выход первого счетчика соединен с адресным входом четвертого оперативного запоминающего устройства, информационный вход которого подключен к выходу второго сумматора, а информационный выход через третий регистр соединен с первым входом второго сумматора, второй вход которого подключен к выходу четвертого счетчика, а выход соединен с первым входом второго блока умножения, второй вход которого подключен к выходу первого блока множителя, а выход соединен с первым входом третьего сумматора, информационный выход первого оперативного запоминающего устройства соединен с входом вычитаемого первого блока вычитания, выход которого через третий сумматор соединен с входом делителя второго блока деления, вход делимого которого подключен к выходу третьего блока множителя, а выход соединен с информационным входом первого регистра, информационный выход которого соединен с объединенными информационными входами второго буферного элемента и цифроаналогового преобразователя, аналоговый выход которого соединен с пятой выходной клеммой, выходы первого триггера соединены прямой с входом седьмого одновибратора, инверсный - через восьмой одновибратор с входом управления записью первого регистра и инверсным входом девятого одновибратора, выход которого соединен с входом установки нуля третьего регистра и инверсным входом десятого одновибратора, выход которого соединен с первым входом пятого элемента ИЛИ и инверсным входом первого одновибратора, выход которого соединен с входом установки нуля четвертого счетчика и инверсным входом шестнадцатого одновибратора, выход которого соединен с входом управления записью первого оперативного запоминающего устройства, выход седьмого одновибратора через шестой элемент ИЛИ соединен с входом управления записью третьего регистра и инверсным входом одиннадцатого одновибратора, выход которого соединен с вторым входом пятого элемента ИЛИ и инверсным входом двенадцатого одновибратора, выход которого соединен с объединенными вторыми входами первого элемента И и первого элемента ИЛИ, а также с тактовым входом восьмого счетчика, выход переноса которого соединен с входом установки нуля первого триггера, выход пятого элемента ИЛИ соединен с входом управления записью четвертого оперативного запоминающего устройства, второй выход генератора прямоугольных импульсов соединен с вторым входом седьмого элемента И, выход которого соединен с тактовым входом третьего триггера, выходы которого соединены соответственно с входами шестого и тринадцатого одновибраторов, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого через четырнадцатый одновибратор соединен с входом управления записью третьего оперативного запоминающего устройства, выход переноса шестого счетчика соединен с входом второго вектора прерываний микроконтроллера, адресная шина которого соединена с объединенными адресными входами третьего оперативного запоминающего устройства и постоянного запоминающего устройства, вход управления записью которого подключен к шине управления микроконтроллера, к которой также подключены вход установки единицы второго триггера и входы управления состоянием выходов первого и второго буферных элементов, постоянного запоминающего устройства, таймера-часов, шестого счетчика и третьего оперативного запоминающего устройства, входы первого-четвертого усилителей мощности, выходы которых соединены соответственно с первой-четвертой выходными клеммами, выход суточных импульсов таймера-часов соединен с входом восьмого вектора прерываний микроконтроллера, выход первого элемента И через пятнадцатый одновибратор соединен с вторым входом шестого элемента ИЛИ.

| SU 1485145 A1, 19.01.1987 | |||

| АЛЕКСЕЕВ В.С., ВАРГАНОВ Г.П., ПАНФИЛОВ Б.И., РОЗЕНБЛЮМ Ф.М | |||

| Реле защиты | |||

| - М.: Энергия, 1976 | |||

| Цифровой измеритель частоты | 1983 |

|

SU1290190A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЧАСТОТЫ СИНУСОИДАЛЬНОГО СИГНАЛА | 1999 |

|

RU2169927C1 |

| Способ определения угла естественного откоса сыпучих материалов и устройство для его осуществления | 1986 |

|

SU1401250A1 |

Авторы

Даты

2009-07-20—Публикация

2007-09-14—Подача