Область техники, к которой относится изобретение

Настоящее изобретение относится к системам и техническим решениям для калибровки интегральной схемы к электронному компоненту.

Уровень техники

Интегральные схемы произвели революцию в электронной промышленности, дав начало новым применениям, которые были невозможны на основе дискретных устройств. Интеграция позволяет размещать сложные схемы, состоящие из миллионов электронных компонентов на одном кристалле полупроводникового материала. Кроме того, интеграция обеспечивает преимущества изготовления сотен микросхем на одной кремниевой пластине, что значительно снижает стоимость и повышает надежность окончательных схем.

В настоящее время интегральные схемы широко используются в электронных устройствах для реализации сложных схем, например, процессоров общего и специального назначения. Контроллер, внедренный в микросхему, можно использовать для сопряжения различных процессоров с компонентами вне кристалла, например внешней памятью и пр. Тактовые сигналы, генерируемые контроллером, можно использовать для доступа к этим компонентам вне кристалла. Эти тактовые сигналы должны действовать на конкретной номинальной скорости с определенным допуском, чтобы контроллер мог осуществлять связь с компонентами вне кристалла в наихудших условиях температуры и напряжения.

Вследствие процессов, характерных для процесса изготовления кремниевой пластины, набор микросхем, созданных из одной пластины, могут относиться к разным классам скорости процесса. В зависимости от применения, некоторые производители вынуждены отбраковывать медленные микросхемы и быстрые микросхемы, которые выходят за пределы номинальных допусков. Это приводит к большому объему отходов, что может сильно повышать затраты.

Пытаясь сохранить участки пластины, из которых не получаются номинальные микросхемы, некоторые производители применяют метод классификации по скорости, согласно которому различные микросхемы, созданные из одной пластины, тестируются и группируются согласно сортировке по скорости процесса. Этот метод группирования микросхем согласно их скорости требует много времени и затрат. Дополнительные убытки обусловлены продажей медленных микросхем и быстрых микросхем со скидкой.

Задержки используются для реализации хронирования, необходимого для обеспечения безошибочной связи между интегральной схемой и внешним компонентом, которые образуют электронное устройство. Они зависят от многих факторов, включая скорость и напряжение интегральной схемы, и скорость внешнего компонента. Эти задержки можно определять, например, с использованием процесса калибровки, который тестирует такие связи и затем выводит задержки из результатов тестирования. Различия в таких параметрах по большому количеству интегральных схем и внешних компонентов могут приводить к заданной задержке, которая не является оптимальной для данного электронного устройства. Кроме того, с практической точки зрения нецелесообразно заранее знать фактические скорость и напряжение каждой интегральной схемы или скорость внешнего компонента. Поэтому в лучшем случае производители микросхем должны принимать решение для определения программной задержки, которая будет работать без ошибок в предполагаемых диапазонах таких параметров, несмотря на то, что известно, что заданные задержки не являются оптимальными для многих электронных устройств.

Сущность изобретения

Согласно одному аспекту изобретения электронное устройство содержит электронный компонент и интегральную схему, сконфигурированную с возможностью генерации системного тактового сигнала и внешнего тактового сигнала, имеющего программируемую задержку относительно системного тактового сигнала, причем интегральная схема дополнительно сконфигурирована с возможностью выдачи внешнего тактового сигнала на электронный компонент, определения диапазона задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании диапазона задержки.

Согласно другому аспекту изобретения, способ калибровки интегральной схемы к электронному компоненту, причем интегральная схема имеет системный тактовый сигнал, содержит этапы, на которых генерируют внешний тактовый сигнал на интегральной схеме, причем внешний тактовый сигнал имеет программируемую задержку относительно системного тактового сигнала, способ дополнительно содержит этапы, на которых обеспечивают внешний тактовый сигнал от интегральной схемы на электронный компонент для поддержки связи с ним, определяют диапазон задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и программируют внешний тактовый сигнал одним из совокупности заданных значений задержки на основании диапазона задержки.

Согласно еще одному аспекту изобретения электронное устройство содержит электронный компонент и интегральную схему, причем интегральная схема включает в себя средство для генерации системного тактового сигнала, содержащее средство для генерации внешнего тактового сигнала на интегральной схеме, причем внешний тактовый сигнал имеет программируемую задержку относительно системного тактового сигнала, средство для обеспечения внешнего тактового сигнала от интегральной схемы на электронный компонент для поддержки связи с ним, средство для определения диапазона задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и средство для программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании диапазона задержки.

Согласно еще одному аспекту изобретения компьютерно-считываемый носитель информации реализует программу из команд, выполняемых процессором для осуществления способа калибровки интегральной схемы к электронному компоненту, причем интегральная схема включает в себя системный тактовый сигнал и внешний тактовый сигнал, имеющий программируемую задержку относительно системного тактового сигнала, причем внешний тактовый сигнал поступает на электронный компонент для поддержки связи с ним, при этом способ содержит этапы, на которых определяют диапазон задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и программируют внешний тактовый сигнал одним из совокупности заданных значений задержки на основании диапазона задержки.

Следует понимать, что специалисты в данной области техники, изучив нижеследующее подробное описание, в котором различные варианты осуществления изобретения показаны и описаны в порядке иллюстрации, смогут предложить другие варианты осуществления настоящего изобретения. Очевидно, что изобретение предусматривает другие и отличные варианты осуществления, и некоторые его детали допускают модификацию в различных других отношениях без отклонения от сущности и объема настоящего изобретения. Соответственно, чертежи и подробное описание следует рассматривать в порядке иллюстрации, но не ограничения.

Краткое описание чертежей

Аспекты настоящего изобретения проиллюстрированы в порядке примера, но не ограничения на прилагаемых чертежах, на которых:

фиг.1 - общая блок-схема, иллюстрирующая пример электронного устройства, в котором используется интегральная схема;

фиг.2 - временная диаграмма, иллюстрирующая пример параметров хронирования для записи в память вне кристалла;

фиг.3 - временная диаграмма, иллюстрирующая пример параметров хронирования для чтения из памяти вне кристалла;

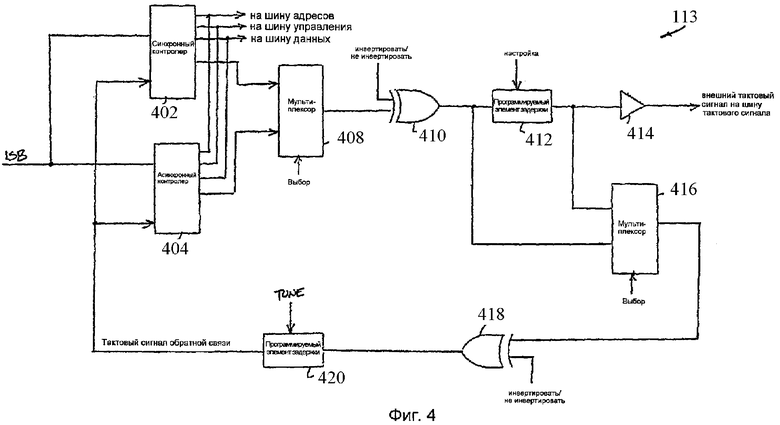

фиг.4 - функциональная блок-схема, иллюстрирующая пример работы контроллера;

фиг.5A и фиг.5B - гистограммы, демонстрирующие иллюстративные диапазоны задержки для интегральной схемы при разных напряжениях и скоростях;

фиг.5C - гистограмма, демонстрирующая диапазон задержки, разделенный на бункеры согласно настоящему изобретению;

фиг.6 - логическая блок-схема, иллюстрирующая пример алгоритма калибровки, который может играть роль предшественника адаптивного алгоритма калибровки, показанного на фиг.7; и

фиг.7 - логическая блок-схема, иллюстрирующая пример адаптивного алгоритма калибровки согласно настоящему изобретению.

Подробное описание

Подробное описание, приведенное ниже со ссылками на прилагаемые чертежи, призвано иллюстрировать различные варианты осуществления настоящего изобретения и не призвано представлять только варианты осуществления, в которых настоящее изобретение может быть реализовано на практике. Подробное описание включает в себя конкретные детали в целях обеспечения полного понимания настоящего изобретения. Однако специалисту в данной области техники очевидно, что настоящее изобретение можно использовать на практике без этих конкретных деталей. В некоторых случаях общеизвестные структуры и устройства показаны в виде блок-схемы во избежание затемнения принципов настоящего изобретения. Акронимы и другие описательные термины могут использоваться исключительно для удобства и упрощения и не призваны ограничивать объем изобретения.

В нижеследующем подробном описании различные аспекты настоящего изобретения могут быть описаны применительно к интегральной схеме, сконфигурированной с возможностью подключения к электронному компоненту, например запоминающему устройству. Интегральная схема может представлять собой, например, специализированную интегральную схему (СИС), содержащую, по меньшей мере, один процессор. Запоминающее устройство может представлять собой, например, синхронную динамическую оперативную память (SDRAM) или аналогичное устройство. Хотя эти аспекты изобретения могут быть пригодны для использования с этими компонентами, специалистам в данной области техники очевидно, что эти аспекты изобретения аналогично применимы для использования в различных других электронных устройствах. Соответственно, любая ссылка на конкретный тип интегральной схемы или электронного компонента (например, внешнюю память или память вне кристалла) призвана лишь иллюстрировать аспекты изобретения, и следует понимать, что такие аспекты изобретения имеют широкую сферу применения.

На фиг.1 показана общая блок-схема электронного устройства 100, в котором применяется интегральная схема 102, например СИС. Интегральная схема 102 может включать в себя микропроцессор 104, цифровой сигнальный процессор (ЦСП) 106, приемопередатчик 108, интерфейс 110 ввода/вывода (I/O) и интерфейс внешней шины (EBI) 112. Все эти компоненты могут соединяться друг с другом посредством интерфейса внутренней шины (ISB) 114. Тактовый генератор 116 можно использовать для генерации системного тактового сигнала для системного хронирования. Фиг.1 не следует рассматривать как предписание какого-либо конкретного физического формата электронного устройства 100 или его компонентов.

Микропроцессор 104 можно использовать как платформу для выполнения прикладных программ, которая, помимо прочего, обеспечивает функции пользовательского управления и общего системного администрирования для электронного устройства 100. ЦСП 106 может быть реализован со встроенным уровнем программного обеспечения связи, на котором выполняются специализированные алгоритмы, для снижения обработочной нагрузки на микропроцессор 104. Микропроцессор 104 и/или ЦСП 106 также можно использовать для выполнения описанных здесь алгоритмов. Приемопередатчик 108 можно использовать для обеспечения доступа к внешней среде, например линии радиосвязи, применительно к беспроводному телефону, терминалу, устройству электронной почты или доступа в Интернет, например карманному персональному компьютеру (КПК), или другому аналогичному устройству. В некоторых вариантах осуществления приемопередатчик 108 может обеспечивать доступ к Эзернет (Ethernet) кабельной модемной линии, волоконной оптике, цифровой абонентской линии (DSL), коммутируемой телефонной сети общего пользования (PSTN) или любой другой среде связи. В других вариантах осуществления электронное устройство может самостоятельно без помощи приемопередатчика поддерживать внешнюю связь. Интерфейс I/O 110 можно использовать для поддержки различных пользовательских интерфейсов. Пользовательские интерфейсы могут включать в себя клавиатуру, мышь, сенсорный экран, громкоговоритель или наушники, микрофон, камеру и пр.

EBI 112 можно использовать для обеспечения доступа между компонентами на ISB 114. EBI 112 может включать в себя контроллер 113, который обеспечивает интерфейс между ISB 114 и компонентами, внешними по отношению к интегральной схеме 102, например одним или несколькими компонентами вне кристалла, например внешним компонентом 118. Интерфейс может включать в себя шину тактового сигнала, шину 122 адресов, шину 120, 124 управления и шину 126 данных. Хотя это не показано, EBI 112 также может обеспечивать интерфейс к жидкокристаллическим дисплеем (ЖКД) и/или другими устройствами пользовательского интерфейса.

Согласно, по меньшей мере, одному варианту осуществления электронного устройства 100 внешний компонент 118 может представлять собой память, например SDRAM. Альтернативно, внешний компонент может представлять собой Burst NOR, Burst PSRAM, RAM, ROM, EPROM, EEPROM, VRAM или любой(е) другой(е) компонент или устройство памяти или матрицу памяти. В любом из вышеперечисленных случаев контроллер 113 можно использовать для генерации внешнего тактового сигнала и тактового сигнала обратной связи как функции системного тактового сигнала от тактового генератора 116. Внешний тактовый сигнал может поступать на внешний компонент 118 по шине тактового сигнала 120 для считывания из внешнего компонента 118, далее SDRAM 118 и записи в него. Контроллер 113 может использовать тактовый сигнал обратной связи для дискретизации данных, считываемых из SDRAM 118.

Пример требований к хронированию для записи в SDRAM 118 показан на фиг.2. Внешний тактовый сигнал, представленный внешним тактовым сигналом 204, может иметь задержку относительно системного тактового сигнала, представленного системным тактовым сигналом 202. Данные, подлежащие записи в SDRAM 118, представлены данными (или сигналом данных) 206 и могут выводиться в шину 120 данных (см. фиг.1) из контроллера 113 вскоре после перехода системного тактового сигнала, в момент времени t0. Короткая задержка 210 между переходом системного тактового сигнала и t0 обусловлена задержкой на распространение контроллера 113. Шина 120 данных (см. фиг.1) добавляет дополнительную задержку на распространение, в результате чего данные 206 поступают на вход SDRAM в момент времени t1. Данные на входе SDRAM показаны на фиг.2 перекрестной штриховкой данных 206.

Для обеспечения надежной работы данные 206 должны быть стабильными на входе SDRAM 118 в течение короткого периода времени до перехода внешнего тактового сигнала. Это называется "минимальным временем установления" и обозначено на фиг.2 как tset-up. Также существует период времени, в течение которого данные 206 должны оставаться стабильными после перехода внешнего тактового сигнала, т.е. после tset-up. Это называется "минимальным временем удержания" и обозначено на фиг.2 как thold. Если минимальные времена установления и удержания не согласованы, то операцию записи в SDRAM нельзя гарантировать. Таким образом, согласно фиг.2 существует необходимая минимальная задержка между системным тактовым сигналом 202 и внешним тактовым сигналом 204 для согласования минимального времени установления и максимальной задержки между ними для согласования минимального времени удержания. Задержка может быть программируемой и может быть установлена где угодно между этими границами, как показано на фиг.2 заштрихованным участком 208 внешнего тактового сигнала 204.

Пример требований к хронированию для чтения из SDRAM 118 показан на фиг.3. Как было объяснено ранее со ссылкой на фиг.2, внешний тактовый сигнал 204 может иметь задержку относительно системного тактового сигнала 202. Тактовый сигнал 302 обратной связи также может иметь задержку относительно системного тактового сигнала 202, как показано на фиг.3. Тактовый сигнал 302 обратной связи можно использовать для считывания данных из SDRAM 118 в контроллер 113. Данные 206 могут выводиться из SDRAM 118 в шину 120 данных (см. фиг.1) вскоре после перехода внешнего тактового сигнала 204, в момент времени t0. В силу задержки на распространение SDRAM 118 и шины 120 данных (см. фиг.1), данные 206 поступают на вход контроллера 113 в момент времени t1. Данные на входе контроллера 113 (которые показаны перекрестной штриховкой данных 206) должны оставаться стабильными в течение короткого периода времени до перехода тактового сигнала обратной связи. Этот период времени определяется как минимальное время установления tset-up контроллера 113. Данные 206 также должны оставаться стабильными после перехода тактового сигнала 302 обратной связи в течение периода времени, определяемого как минимальное время удержания thold контроллера 113. После считывания данных в контроллер 113 с переходом тактового сигнала 302 обратной связи они могут повторно дискретизироваться системным тактовым сигналом. Процесс повторной дискретизации имеет свои собственные требования, включающие в себя минимальное время установления, в течение которого дискретизированные данные должны оставаться стабильными до следующего перехода системного тактового сигнала 202. Таким образом, согласно фиг.3, существует необходимая минимальная задержка между системным тактовым сигналом 202 и тактовым сигналом 302 обратной связи для согласования минимального времени установления и максимальной задержки между ними для согласования минимального времени удержания и времени установления повторной дискретизации. Задержка может быть программируемой в контроллере 113 и может быть установлена где угодно между этими границами, как показано на фиг.3 заштрихованным участком 304.

На фиг.4 показана функциональная блок-схема варианта осуществления контроллера 113. Согласно показанному варианту осуществления контроллер 113 может делиться на синхронный контроллер 402 и асинхронный контроллер 404. Это деление носит характер исключительно конструкционного предпочтения, и специалистам в данной области техники очевидно, что для осуществления различных функций, описанных в этом раскрытии, можно использовать любую конфигурацию. Контроллеры 402 и 404 могут быть сконфигурированы с возможностью сопряжения шины 122 адресов, шины 124 управления и шины 126 данных с ISB 114 общеизвестным в технике способом.

Контроллер 113 можно использовать для генерации внешнего тактового сигнала 204 и тактового сигнала 302 обратной связи. Мультиплексор 408 можно использовать для выбора надлежащего системного тактового сигнала 202 в зависимости от того, тактируются ли данные 206 из синхронного или асинхронного контроллера. В показанном варианте осуществления можно установить мультиплексор 408 для выбора системного тактового сигнала, используемого синхронным контроллером 402 для сопряжения с SDRAM 118. Для обеспечения гибкости можно использовать вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ 410, выдающий инвертированный или неинвертированный системный тактовый сигнал 202. Для задания задержки внешнего тактового сигнала 204 можно использовать программируемый элемент задержки 412. Управление мультиплексором и вентилем ИСКЛЮЧАЮЩЕЕ ИЛИ, а также задержку внешний тактовый сигнал можно программировать посредством, например, программного обеспечения, выполняющегося на микропроцессоре 104, или любыми другими средствами, для подачи внешнего тактового сигнала 204 на SDRAM 118 можно использовать драйвер 414 шины.

Тактовый сигнал 302 обратной связи можно генерировать из системного тактового сигнала 202 или из внешнего тактового сигнала 204. Оба тактовых сигнала можно подавать на мультиплексор 416 для предоставления некоторой гибкости разработчику программного обеспечения. В описанном варианте осуществления выбранный системный тактовый сигнал может поступать на вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ 418. Вентиль ИСКЛЮЧАЮЩЕЕ ИЛИ 418 позволяет использовать либо инвертированный, либо неинвертированный тактовый сигнал. Программируемый элемент задержки 420 можно использовать для задержки тактового сигнала обратной связи. Тактовый сигнал 302 обратной связи может затем возвращаться на контроллеры 402 и 404. Управление мультиплексором и вентилем ИСКЛЮЧАЮЩЕЕ ИЛИ, а также задержку тактового сигнала обратной связи можно программировать посредством программного обеспечения, выполняющегося на микропроцессоре 104, или любыми другими средствами.

Согласно рассмотренному выше определенные ограничения на хронирование, налагаемые контроллером 113 и SDRAM 118, могут ограничивать возможные настройки задержки для внешнего тактового сигнала и тактового сигнала обратной связи. Настройка задержки для внешнего тактового сигнала, например, может ограничиваться минимальными временами установления и удержания для SDRAM 118. Аналогично, настройка задержки для тактового сигнала обратной связи может ограничиваться минимальными временами установления, удержания и установления повторной дискретизации для контроллера 113. Эти ограничения на хронирование могут изменяться в зависимости от процесса, напряжения и температуры (PVT).

Алгоритм калибровки, запрограммированный в интегральную схему, можно использовать для программирования элементов задержки для каждого устройства в отдельности. Этот подход позволяет обеспечивать оптимальные настройки тактового сигнала для каждого электронного устройства в отдельности. Алгоритм калибровки можно использовать в условиях эксплуатации, при запуске электронного устройства или периодически в ходе его работы. Алгоритм калибровки может частично опираться на статистическую информацию, записанную в памяти. Статистическую информацию можно выводить из совокупности данных, полученных при тестировании достаточной выборки электронных устройств на фабрике. Этот процесс называется "процессом снятия характеристик".

Процесс снятия характеристик может начинаться с вычисления задержки ("K") между тактовым сигналом обратной связи и внешним тактовым сигналом для выборки электронных устройств. Из фиг.3 следует, что время установления tset-up для контроллера 113 определяется задержкой от перехода внешнего тактового сигнала до перехода тактового сигнала обратной связи, для операции чтения. Также можно видеть, что время удержания thold определяется задержкой от перехода тактового сигнала обратной связи до следующего перехода внешнего тактового сигнала. Соответственно, если задержка между внешним тактовым сигналом и тактовым сигналом обратной связи сокращается, то время установления tset-up уменьшается и время удержания thold увеличивается. Напротив, если задержка между внешним тактовым сигналом и тактовым сигналом обратной связи возрастает, то время установления tset-up увеличивается и время удержания thold уменьшается. Таким образом, начальный этап процесса снятия характеристик может состоять в вычислении задержки между тактовым сигналом обратной связи и внешним тактовым сигналом, которая удовлетворяет минимальным временам установления и удержания в наихудшем случае для контроллера 113 применительно к выборке электронных устройств.

Исходя из того, что задержка между внешним тактовым сигналом и тактовым сигналом обратной связи задана таким образом, чтобы удовлетворять минимальным временам установления и удержания контроллера при операции чтения, неудачное или успешное завершение операции чтения будет целиком зависеть от того, удовлетворяется ли минимальное время установления повторной дискретизации tset-up. Согласно фиг.3 время установления повторной дискретизации tset-up очень велико, когда задержка между системным тактовым сигналом и тактовым сигналом обратной связи мала. Однако при увеличении задержки между двумя тактовыми сигналами время установления повторной дискретизации tset-up сокращается, пока не достигнет минимального времени установления повторной дискретизации tset-up. Это "максимальная задержка" между системным тактовым сигналом и тактовым сигналом обратной связи, при которой можно гарантировать операцию чтения.

Согласно фиг.2 успешное или неудачное завершение операции записи будет зависеть от двух параметров: минимального времени установления tset-up и минимального времени удержания thold для записи в SDRAM 118. Однако на практике минимальное время удержания thold обычно не является ограничительным фактором. Дело в том, что время удержания приблизительно равно периоду тактового сигнала минус время установления tset-up, что гораздо больше, чем минимальное время удержания thold. Соответственно, минимальное время установления tset-up SDRAM 118 будет определять "минимальную задержку" между системным тактовым сигналом и внешним тактовым сигналом (или таковым сигналом обратной связи), при которой можно гарантировать операцию записи.

В ходе процесса снятия характеристик процедуру тестирования можно осуществлять на каждом электронном устройстве в выборке для определения диапазона значений задержки между системным тактовым сигналом и тактовым сигналом обратной связи, в котором контроллер 113 может записывать в SDRAM 118 или читать из нее. Этот диапазон является непрерывным диапазоном, ограниченным "максимальной задержкой", заданной минимальным временем установления повторной дискретизации tset-up контроллера 113 и "минимальной задержкой", заданной минимальным временем установления tset-up SDRAM 118. Процедура тестирования может предусматривать программирование вычисленной задержки между тактовым сигналом обратной связи и внешним тактовым сигналом в программируемые элементы задержки контроллера 113 для каждого тестируемого электронного устройства. Затем диапазон настройки программируемых элементов задержки для каждого электронного устройства можно варьировать по всему диапазону настройки, в то же время поддерживая задержку между внешним тактовым сигналом и тактовым сигналом обратной связи. В частности, для каждого электронного устройства программируемый элемент задержки 420 для тактового сигнала обратной связи можно устанавливать на нулевую задержку и программируемый элемент задержки 412 для внешнего тактового сигнала можно устанавливать на K. Затем задержку программируемых элементов задержки можно постепенно совместно увеличивать. Для каждой возрастающей задержки контроллер 113 производит чтение из SDRAM 118 и запись в нее, после чего классифицирует каждую попытку чтения и записи как успешную или неудачную в зависимости от исхода.

На практике возможны вариации по скорости конкретных интегральных схем и по скорости устройств SDRAM, которые могут влиять на оптимальные задержки тактового сигнала обратной связи и внешнего тактового сигнала для конкретного электронного устройства. Например, на фиг.5A и 5B показаны результаты процедуры тестирования для двух разных электронных устройств из выборки в ходе процесса снятия характеристик. На каждой из фиг.5A и фиг.5B каждая гистограмма представляет диапазон задержки тактового сигнала обратной связи, в котором может работать соответствующее электронное устройство. Можно видеть, что различия в частоте (т.е. тактовой частоте) интегральной схемы могут порождать существенно отличающиеся требования к задержке тактового сигнала обратной связи. Хотя на каждой из фиг.5A и фиг.5B показана задержка внешнего тактового сигнала, результаты в равной степени применимы к задержке внешнего тактового сигнала ввиду известного соотношения между внешним тактовым сигналом и тактовым сигналом обратной связи в иллюстративном варианте осуществления.

Согласно фиг.5A процедура тестирования для электронного устройства в ходе процесса снятия характеристик может начинаться с задания оптимального напряжения для электронного устройства. Затем задержка тактового сигнала обратной связи задается равной нулю (nfb=0), где nfb это численное значение, запрограммированное в элемент задержки для тактового сигнала обратной связи, и задержка внешнего тактового сигнала задается равной K (next=K), где next это численное значение, запрограммированное в элемент задержки для внешнего тактового сигнала. При этих условиях данные записываются в SDRAM и затем считываются из SDRAM. Если считанные данные верны, т.е. ошибки не произошло, в качестве значения n записывается «прошел». В противном случае, в качестве значения n записывается "не прошел" n. Затем значение n получает приращение, например, n=1, тогда как напряжение и частота остаются неизменными. Этапы записи, чтения и записи «прошел/не прошел» затем осуществляются для нового n. Это продолжается до n=31, которое является максимальным значением. Результаты, например, показаны на гистограмме, изображенной на фиг.5A. Заштрихованный участок гистограммы представляет значения прохождения и проходит от около n=1 до около n=28. Значения непрохождения попадают либо ниже n=1, либо выше n=28. "Минимальную задержку" между системным тактовым сигналом и тактовым сигналом обратной связи можно соотнести с наименьшим значением прохождения (LPV) и "максимальную задержку" между системным тактовым сигналом и тактовым сигналом обратной связи можно соотнести с наибольшим значением прохождения (HPV).

Такую же процедуру тестирования можно осуществлять на втором электронном устройстве при оптимальном напряжении. В этом случае интегральная схема во втором электронном устройстве быстрее, чем в первом. Результаты показаны на гистограмме, изображенной на фиг.5B. Заштрихованный участок гистограммы представляет значения прохождения и проходит от около n=4 до около n=31. Значения непрохождения попадают либо ниже n=4, либо выше n=31. Сравнивая результаты для первого и второго электронных устройств, показанные на фиг.5A и фиг.5B, можно видеть, что различные настройки задержки тактового сигнала между системным тактовым сигналом и тактовым сигналом обратной связи для второго электронного устройства, имеющего более быструю интегральную схему, не будут работать для первого электронного устройства, имеющего более медленную интегральную схему.

Процесс снятия характеристик можно осуществлять для большого количества электронных устройств для получения более обширной статистики решений задержки тактового сигнала обратной связи. Эти данные можно использовать для определения диапазона значений задержки для разных классификаций электронных устройств. Эти классификации называются "бункерами" и опираются на скорость интегральной схемы и SDRAM для электронных устройств. Каждый бункер может представлять комбинацию тестируемых устройств. В иллюстративном варианте осуществления, задано четыре бункера, которые представляют комбинации интегральной схемы и SDRAM, а именно: (1) медленная интегральная схема, быстрая SDRAM; (2) медленная/номинальная интегральная схема, медленная SDRAM; (3) быстрая/номинальная интегральная схема, быстрая SDRAM; и (4) быстрая/номинальная интегральная схема, медленная SDRAM. Конечно, можно задать и другие комбинации или задать больше или меньше бункеров.

Тестирование достаточно большой выборки электронных устройств в ходе процесса снятия характеристик может привести к созданию распределения значений задержки для каждой комбинации интегральной схемы и SDRAM. На основании таких распределений можно задавать бункеры. Конечно, известны многочисленные статистические подходы, которые можно применять к данным тестирования для определения ширины бункеров (т.е. диапазона значений задержки между системным тактовым сигналом и тактовым сигналом обратной связи). При наличии недостаточных данных тестирования можно использовать экстраполяцию для оценивания ширины бункера и соответствующих задержек.

На фиг.5C показана гистограмма 550, где изображены бункеры 1, 2, 3 и 4, причем каждый бункер имеет определенную ширину бункера. Ширина бункера 1 равна около 4-8, ширина бункера 2 равна около 8-12, ширина бункера 3 равна около 12-16, и ширина бункера 4 равна около 16-20. Ширину каждого бункера, настройку задержки между системным тактовым сигналом и тактовым сигналом обратной связи можно выбирать. Настройку задержки можно выбирать из центра бункера. Например, электронное устройство, которое характеризуется как имеющее медленную интегральную схему и быструю SDRAM, можно отправить в бункер 1, и если задержка между системным тактовым сигналом и тактовым сигналом обратной связи задана равной 6 (т.е. значению задержки в центре бункера 1), то электронное устройство должно работать правильно. В этом случае задержка между системным тактовым сигналом и внешним тактовым сигналом будет равна 6+K. Если K задана равной 4 для получения приближенного времени установления 2 нс и времени удержания 1 нс, то для каждого бункера можно установить следующие настройки задержки:

Бункер 1 → медленная интегральная схема, быстрая SDRAM:

задержка тактового сигнала обратной связи = 6, задержка внешнего тактового сигнала = 10

Бункер 2 → медленная/номинальная интегральная схема, медленная SDRAM:

задержка тактового сигнала обратной связи = 10, задержка внешнего тактового сигнала = 14

Бункер 3 → номинальная/быстрая интегральная схема, быстрая SDRAM:

задержка тактового сигнала обратной связи = 14, задержка внешнего тактового сигнала = 18

Бункер 4 → номинальная/быстрая интегральная схема, медленная SDRAM:

задержка тактового сигнала обратной связи = 18, задержка внешнего тактового сигнала = 22.

Настройки тактового сигнала, определенные в ходе процесса снятия характеристик, могут использоваться адаптивным алгоритмом калибровки, запрограммированным в электронное устройство, для задания задержки внешнего тактового сигнала и тактового сигнала обратной связи для каждого устройства в отдельности в условиях эксплуатации. Эти настройки тактового сигнала и определения бункеров могут храниться в памяти электронного устройства или быть включены в адаптивный алгоритм калибровки.

На фиг.6 представлена логическая блок-схема 600, изображающая адаптивный алгоритм калибровки, используемый для конкретного электронного устройства в условиях эксплуатации. Как и другие описанные здесь алгоритмы, процессы и способы, адаптивный алгоритм 700 калибровки может быть реализован программными, аппаратными, программно-аппаратными средствами или посредством любой их комбинации. Адаптивный алгоритм 600 калибровки аналогичен описанному выше для определения гистограмм на фиг.5A и 5B. Адаптивный алгоритм 600 калибровки может выполняться при первом запуске электронного устройства 100. Адаптивный алгоритм 600 калибровки также может выполняться при последующих запусках, произвольно, периодически или в соответствии с изменениями измеряемых условий, например напряжения, температуры или скорости.

В этом примере адаптивный алгоритм калибровки первоначально устанавливает задержку между системным тактовым сигналом и тактовым сигналом обратной связи, равной нулю (nfb=0), и задержку между системным тактовым сигналом и внешним тактовым сигналом равной K (next=K) на этапе 604. На этапе 606 проводится проверка, был ли тактовый сигнал обратной связи проварьирован по всему диапазону настройки. Для этого можно определять, превышает ли nfb 31. Если на этапе 606 определено, что задержка тактового сигнала обратной связи не была проварьирована по всему диапазону настройки, процесс 600 переходит к этапу 608, на котором интегральная схема 102 записывает данные тестирования в SDRAM 118. Затем процесс 600 переходит к этапу 610, на котором интегральная схема 102 считывает данные тестирования из SDRAM 118.

Считанные данные тестирования сравниваются с записанными данными. Если на этапе 612 определено, что считанные данные верны (т.е. точны), то процесс 600 переходит к этапу 614, и в настройках внешнего тактового сигнала и тактового сигнала обратной связи регистрируется состояние "прошел" для операции. Если считанные данные не совпадают с записанными данными, значит тест не пройден, и на этапе 616 в настройках внешнего тактового сигнала и тактового сигнала обратной связи регистрируется состояние "не прошел". В любом случае значения задержки внешнего тактового сигнала и тактового сигнала обратной связи затем получают приращение на этапе 618, и процесс 600 возвращается к этапу 606. Таким образом адаптивный алгоритм калибровки 600 охватывает весь диапазон задержки. В конце концов, процесс 600 переходит к этапу 620, на котором определяются результирующие LPV и HPV для электронного устройства 100.

Когда LPV и HPV известны, адаптивный алгоритм 700 калибровки можно использовать для определения окончательных настроек тактового сигнала. Адаптивный алгоритм 700 калибровки проводит тесты, базирующиеся на известных принципах соотношений между HPV, LPV и скоростями интегральных схем и запоминающих устройств, которые отражены в рассмотренных выше определениях бункеров.

На этапе 702 получают LPV и HPV для электронного устройства 100. Хотя иллюстративный вариант осуществления предусматривает определение LPV и HPV с использованием процесса, показанного на фиг.6, адаптивный алгоритм калибровки не требует, чтобы LPV и HPV для электронного устройства 100 определялись посредством процесса, показанного на фиг.6. Значения LPV и HPV можно определять и другими способами. LPV и HPV используются для определения, какой бункер пригоден для электронного устройства 100 и соответственно какая настройка задержки пригодна для электронного устройства 100. Для этого производится тестирование LPV и HPV по всему диапазону настройки (т.е. nfb пробегает от 0 до 31).

На этапе 704 производится определение, действительно ли HPV больше или равно 31. Если проверка на этапе 704 не проходит, процесс переходит к этапу 706, на котором производится определение, действительно ли LPV меньше или равно 0. Если LPV больше или равно 0, то на этапе 708 электронное устройство 100 заносится в бункер 1. Если LPV не меньше или равно 0, то на этапе 710 электронное устройство 100 заносится в бункер 2. Если на этапе 704 определено, что HPV больше или равно 31, то алгоритм переходит к этапу 712, на котором производится определение в отношении LPV. Если LPV меньше или равно 0, то на этапе 714 электронное устройство 100 заносится в бункер 3. Иначе на этапе 716 электронное устройство 100 заносится в бункер 4.

После определения правильного бункера интегральная схема 102 устанавливает задержки тактовых сигналов с помощью заданных настроек для этого бункера. В этом примере настройка задержки соответствует центру бункера. На этапе 720 получают задержку тактового сигнала обратной связи, и на этапе 722 внешний тактовый сигнал определяют из задержки тактового сигнала обратной связи и смещения K. На этапе 724 программируемый элемент 412 задержки внешнего тактового сигнала и программируемый элемент 420 задержки тактового сигнала обратной связи настраивают с использованием значений, полученных на этапе 722.

Очевидно, что вышеописанные алгоритмы можно представить как определяющие задержку внешнего тактового сигнала, и на основании задержки внешнего тактового сигнала определяющие задержку тактового сигнала обратной связи, в которых задержка тактового сигнала обратной связи = задержке внешнего тактового сигнала K. Любой подход будет приемлемым, поскольку, если задано определенное соотношение между тактовым сигналом обратной связи и внешним тактовым сигналом, из него можно получить другое.

Согласно фиг.7 и с использованием определений бункеров, рассмотренных выше со ссылкой на фиг.5C, если электронное устройство 100 попадает в бункер 1, то задержка тактового сигнала обратной связи = 6 и задержка внешнего тактового сигнала = 10; если электронное устройство 100 попадает в бункер 2, то задержка тактового сигнала обратной связи = 10 и задержка внешнего тактового сигнала = 14; если электронное устройство 100 попадает в бункер 3, то задержка тактового сигнала обратной связи = 14 и задержка внешнего тактового сигнала = 18; и если электронное устройство 100 попадает в бункер 4, то задержка тактового сигнала обратной связи = 18 и задержка тактового сигнала обратной связи = 22.

Согласно вышесказанному этот процесс может выполняться не только при первом запуске, но и в последующее время. Например, адаптивный алгоритм калибровки может выполняться при каждом запуске произвольно, периодически или в соответствии с изменениями измеряемых условий. Каждое измеряемое условие может представлять собой измерение напряжения, температуры, скорости интегральной схемы или внешнего компонента или ошибку связи между интегральной схемой и внешним компонентом.

Различные иллюстративные логические блоки, модули и схемы, описанные в связи с раскрытыми здесь вариантами осуществления, можно реализовать или осуществлять посредством процессора общего назначения, цифрового сигнального процессора (ЦСП), специализированной интегральной схемы (СИС), программируемой пользователем вентильной матрицы (ППВМ) или другого программируемого логического устройства, дискретной вентильной или транзисторной логики, дискретных аппаратных компонентов или любой их комбинации, предназначенных для осуществления описанных здесь функций. Процессор общего назначения может представлять собой микропроцессор, но, альтернативно, процессор может представлять собой любой традиционный процессор, контроллер, микроконтроллер или конечный автомат. Процессор также может быть реализован как комбинация вычислительных устройств, например комбинация ЦСП и микропроцессора, совокупность микропроцессоров, один или несколько микропроцессоров в сочетании с ядром ЦСП или любая другая подобная комбинация.

Способы или алгоритмы, описанные в связи с раскрытыми здесь вариантами осуществления, могут быть реализованы непосредственно в оборудовании, в программном модуле, выполняемом процессором, или в их комбинации. Программный модуль может размещаться в ОЗУ, флэш-памяти, ПЗУ, ЭППЗУ, ЭСППЗУ, на жестком диске, сменном диске, CD-ROM или носителе информации любого другого типа, известного в технике. Носитель информации может быть подключен к процессору, в результате чего процессор может считывать с него информацию и записывать на него информацию. Альтернативно, носитель данных может образовывать с процессором единое целое. Процессор и носитель данных могут размещаться в СИС.

Вышеприведенное описание раскрытых вариантов осуществления предоставлено, чтобы специалист в данной области мог использовать настоящее изобретение. Специалисту в данной области должны быть очевидны различные модификации этих вариантов осуществления, и раскрытые здесь общие принципы можно применять к другим вариантам осуществления, не выходя за рамки сущности и объема изобретения. Таким образом, настоящее изобретение не ограничивается показанными здесь вариантами осуществления, но подлежит рассмотрению в широчайшем объеме, согласующемся с раскрытыми здесь принципами и новыми признаками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ИНТЕГРАЛЬНАЯ СХЕМА С АДАПТИВНЫМ ОТБОРОМ ПО СКОРОСТИ | 2005 |

|

RU2381543C2 |

| СПОСОБ (ВАРИАНТЫ) И СИСТЕМА ДЛЯ УПРАВЛЕНИЯ КАТАЛИТИЧЕСКИМ НЕЙТРАЛИЗАТОРОМ С ОБРАТНОЙ СВЯЗЬЮ | 2017 |

|

RU2704902C2 |

| Электронная офтальмологическая линза с отслеживанием сна | 2016 |

|

RU2663492C2 |

| СПОСОБ ЭЛЕКТРОННОЙ ОБРАБОТКИ СИГНАЛОВ ФОТОПРИЕМНИКА ПРИ ФОРМИРОВАНИИ ИЗОБРАЖЕНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2423016C1 |

| СИСТЕМА И СПОСОБ ДЛЯ ОФТАЛЬМОЛОГИЧЕСКОЙ ЛИНЗЫ С ПРОЦЕССОРНЫМ УПРАВЛЕНИЕМ | 2014 |

|

RU2633307C2 |

| СПОСОБ И СИСТЕМА ДЛЯ КОРРЕКЦИИ DC И AGC | 2009 |

|

RU2458457C2 |

| ПРИВОД ЛИНЗЫ ДЛЯ ЭЛЕКТРОННОЙ ОФТАЛЬМОЛОГИЧЕСКОЙ ЛИНЗЫ С ИЗМЕРЯЕМЫМИ ОПТИЧЕСКИМИ СВОЙСТВАМИ | 2013 |

|

RU2577461C2 |

| УДАЛЕННАЯ СИСТЕМА СБОРА И ОБРАБОТКИ ДАННЫХ ДЛЯ БОРТОВОЙ РЕГИСТРИРУЮЩЕЙ АППАРАТУРЫ | 2012 |

|

RU2493592C1 |

| ИСПАРИТЕЛЬНОЕ УСТРОЙСТВО И СПОСОБ ЕГО ФУНКЦИОНИРОВАНИЯ | 2019 |

|

RU2790191C2 |

| КАЛИБРОВКА АНТЕННОЙ РЕШЕТКИ ДЛЯ СИСТЕМ БЕСПРОВОДНОЙ СВЯЗИ | 2006 |

|

RU2390942C2 |

Изобретение относится к системам для калибровки интегральной схемы к электронному компоненту. Сущность: электронное устройство содержит электронный компонент и интегральную схему. Итегральная схема сконфигурирована с возможностью генерации системного тактового сигнала и внешнего тактового сигнала, имеющего программируемую задержку относительно системного тактового сигнала. Интегральная схема имеет возможность определения диапазона задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании диапазона задержки. 4 н. и 31 з.п. ф-лы, 9 ил.

1. Электронное устройство, содержащее

электронный компонент, и

интегральную схему, сконфигурированную с возможностью генерации системного тактового сигнала и внешнего тактового сигнала, имеющего программируемую задержку относительно системного тактового сигнала, причем интегральная схема дополнительно сконфигурирована с возможностью выдачи внешнего тактового сигнала на электронный компонент, определения диапазона задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании диапазона задержки.

2. Электронное устройство по п.1, в котором интегральная схема дополнительно сконфигурирована с возможностью сохранения заданных значений задержки.

3. Электронное устройство по п.1, в котором электронный компонент содержит, по меньшей мере, одно запоминающее устройство.

4. Электронное устройство по п.3, в котором электронный компонент содержит, по меньшей мере, одно из следующего: SDRAM, Burst NOR, Burst PSRAM, RAM, ROM, EPROM, EEPROM или VRAM.

5. Электронное устройство по п.3, в котором интегральная схема дополнительно сконфигурирована с возможностью определения диапазона задержки посредством совокупности операций чтения/записи на электронном компоненте.

6. Электронное устройство по п.5, в котором интегральная схема дополнительно сконфигурирована с возможностью определения диапазона задержки посредством оценки каждой из операций чтения как состояние «прошел» или состояние «не прошел».

7. Электронное устройство по п.1, в котором диапазон задержки содержит верхнюю и нижнюю границы, и в котором интегральная схема дополнительно сконфигурирована с возможностью программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании границ диапазона задержки.

8. Электронное устройство по п.7, в котором интегральная схема дополнительно сконфигурирована с возможностью определения одного из совокупности заданных значений задержки в зависимости от того, выше ли верхняя граница диапазона задержки максимальной программируемой задержки между системным тактовым сигналом и внешним тактовым сигналом.

9. Электронное устройство по п.7, в котором интегральная схема дополнительно сконфигурирована с возможностью определения одного из совокупности заданных значений задержки в зависимости от того, ниже ли нижняя граница диапазона задержки минимальной программируемой задержки между системным тактовым сигналом и внешним тактовым сигналом.

10. Электронное устройство по п.1, в котором каждое из заданных значений задержки связано с диапазоном скоростей, характеризующим интегральную схему, и диапазоном скоростей, характеризующим электронный компонент.

11. Электронное устройство по п.1, в котором электронное устройство содержит беспроводной телефон, карманный персональный компьютер, устройство электронной почты или устройство доступа в Интернет.

12. Способ калибровки интегральной схемы к электронному компоненту, причем интегральная схема имеет системный тактовый сигнал, содержащий этапы, на которых

генерируют внешний тактовый сигнал на интегральной схеме, причем внешний тактовый сигнал имеет программируемую задержку относительно системного тактового сигнала,

обеспечивают внешний тактовый сигнал от интегральной схемы на электронный компонент для поддержки связи с ним,

определяют диапазон задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и

программируют внешний тактовый сигнал одним из совокупности заданных значений задержки на основании диапазона задержки.

13. Способ по п.12, дополнительно содержащий этап, на котором сохраняют заданные значения задержки.

14. Способ по п.12, в котором электронный компонент содержит, по меньшей мере, одно запоминающее устройство.

15. Способ по п.14, в котором электронный компонент содержит, по меньшей мере, одно из следующего: SDRAM, Burst NOR, Burst PSRAM, RAM, ROM, EPROM, EEPROM или VRAM.

16. Способ по п.14, дополнительно содержащий этап, на котором определяют диапазон задержки посредством совокупности операций чтения/записи на электронном компоненте.

17. Способ по п.16, дополнительно содержащий этап, на котором определяют диапазон задержки, оценивая каждую из операций чтения как состояние «прошел» или состояние «не прошел».

18. Способ по п.12, дополнительно содержащий этап, на котором определяют верхнюю и нижнюю границы диапазона задержки, и программируют внешний тактовый сигнал одним из совокупности заданных значений задержки на основании границ диапазона задержки.

19. Способ по п.18, дополнительно содержащий этап, на котором определяют одно из совокупности заданных значений задержки в зависимости от того, выше ли верхняя граница диапазона задержки максимальной программируемой задержки между системным тактовым сигналом и внешним тактовым сигналом.

20. Способ по п.18, дополнительно содержащий этап, на котором определяют одно из совокупности заданных значений задержки в зависимости от того, ниже ли нижняя граница диапазона задержки минимальной программируемой задержки между системным тактовым сигналом и внешним тактовым сигналом.

21. Способ по п.12, в котором каждое из заданных значений задержки связано с диапазоном скоростей, характеризующим интегральную схему, и диапазоном скоростей, характеризующим электронный компонент.

22. Способ по п.12, в котором электронное устройство содержит беспроводной телефон, карманный персональный компьютер, устройство электронной почты или устройство доступа в Интернет.

23. Электронное устройство, содержащее

электронный компонент, и

интегральную схему, содержащую

средство для генерации системного тактового сигнала,

средство для генерации внешнего тактового сигнала на интегральной схеме, причем внешний тактовый сигнал имеет программируемую задержку относительно системного тактового сигнала,

средство для обеспечения внешнего тактового сигнала от интегральной схемы на электронный компонент для поддержки связи с ним,

средство для определения диапазона задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и

средство для программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании диапазона задержки.

24. Электронное устройство по п.23, дополнительно содержащее средство для сохранения заданных значений задержки.

25. Электронное устройство по п.23, в котором электронный компонент содержит, по меньшей мере, одно запоминающее устройство.

26. Электронное устройство по п.25, в котором электронный компонент содержит, по меньшей мере, одно из следующего: SDRAM, Burst NOR, Burst PSRAM, RAM, ROM, EPROM, EEPROM или VRAM.

27. Электронное устройство по п.25, дополнительно содержащее средство для определения диапазона задержки посредством совокупности операций чтения/записи на электронном компоненте.

28. Электронное устройство по п.27, дополнительно содержащее средство для определения диапазона задержки, оценивающее каждую операцию чтения как состояние «прошел» или состояние «не прошел».

29. Электронное устройство по п.23, дополнительно содержащее средство для определения верхней и нижней границ диапазона задержки, и средство для программирования внешнего тактового сигнала одним из совокупности заданных значений задержки на основании границ диапазона задержки.

30. Электронное устройство по п.29, дополнительно содержащее средство для определения одного из совокупности заданных значений задержки в зависимости от того, выше ли верхняя граница диапазона задержки максимальной программируемой задержки между системным тактовым сигналом и внешним тактовым сигналом.

31. Электронное устройство по п.29, дополнительно содержащее средство для определения одного из совокупности заданных значений задержки в зависимости от того, ниже ли нижняя граница диапазона задержки минимальной программируемой задержки между системным тактовым сигналом и внешним тактовым сигналом.

32. Электронное устройство по п.23, в котором каждое из заданных значений задержки связано с диапазоном скоростей, характеризующим интегральную схему, и диапазоном скоростей, характеризующим электронный компонент.

33. Электронное устройство по п.23, в котором электронное устройство содержит беспроводной телефон, карманный персональный компьютер, устройство электронной почты или устройство доступа в Интернет.

34. Компьютерно-считываемый носитель информации, реализующий программу из команд, выполняемых процессором для осуществления способа калибровки интегральной схемы к электронному компоненту, причем интегральная схема включает в себя системный тактовый сигнал и внешний тактовый сигнал, имеющий программируемую задержку относительно системного тактового сигнала, причем внешний тактовый сигнал поступает на электронный компонент для поддержки связи с ним, при этом способ содержит этапы, на которых определяют диапазон задержки между системным тактовым сигналом и внешним тактовым сигналом, в котором интегральная схема и электронный компонент могут осуществлять связь, и программируют внешний тактовый сигнал одним из совокупности заданных значений задержки на основании диапазона задержки.

35. Компьютерно-считываемый носитель информации по п.34, в котором электронный компонент содержит память, и при этом интегральная схема дополнительно включает в себя тактовый сигнал обратной связи, имеющий программируемую задержку относительно системного тактового сигнала, причем связь между интегральной схемой и памятью осуществляется с использованием внешнего тактового сигнала для записи в память и чтения из нее и с использованием тактового сигнала обратной связи для дискретизации данных на интегральной схеме, считанных из памяти, и способ дополнительно содержит калибровку задержки тактового сигнала обратной связи на основании диапазона задержки.

| Перекатываемый затвор для водоемов | 1922 |

|

SU2001A1 |

| Топчак-трактор для канатной вспашки | 1923 |

|

SU2002A1 |

| Устройство для контроля параметров электронных блоков | 1987 |

|

SU1471156A1 |

| Устройство для автоматического контроля больших интегральных схем | 1986 |

|

SU1529220A1 |

Авторы

Даты

2009-07-27—Публикация

2005-11-07—Подача